#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

## **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

AT-MIO-16D

## AT-MIO-16X User Manual

Multifunction I/O Board for the PC AT/EISA

October 1997 Edition Part Number 320640B-01

© Copyright 1992, 1997 National Instruments Corporation. All rights reserved.

#### **Internet Support**

support@natinst.com

E-mail: info@natinst.com

FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

#### **Bulletin Board Support**

BBS United States: (512) 794-5422 BBS United Kingdom: 01635 551422

BBS France: 01 48 65 15 59

Fax-on-Demand Support

(512) 418-1111

Telephone Support (U.S.)

Tel: (512) 795-8248 Fax: (512) 794-5678

#### **International Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 5734815, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, United Kingdom 01635 523545

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 Tel: (512) 794-0100

## **Important Information**

#### Warranty

The AT-MIO-16X is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

$ComponentWorks^{TM}, LabVIEW^{TM}, Measure^{TM}, NI-DAQ^{TM}, RTSI^{TM}, and\ VirtualBench^{TM}\ are\ trademarks\ of\ National\ Instruments\ Corporation.$

Product and company names listed are trademarks or trade names of their respective companies.

#### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

Table of Contents

| About  | This Manual                               |      |

|--------|-------------------------------------------|------|

|        | Organization of This Manual               | ΧV   |

|        | Conventions Used in This Manual           |      |

|        | Related Documentation                     | xvii |

|        | Customer Communication                    | xvii |

| Chapt  | er 1                                      |      |

| •      | uction                                    |      |

|        | About the AT-MIO-16X                      | 1-1  |

|        | Analog Input                              |      |

|        | Analog Output                             |      |

|        | Digital and Timing I/O                    |      |

|        | What You Need to Get Started              |      |

|        | Software Programming Choices              | 1-4  |

|        | National Instruments Application Software | 1-4  |

|        | NI-DAQ Driver Software                    | 1-5  |

|        | Register-Level Programming                | 1-6  |

|        | Optional Equipment                        | 1-7  |

|        | Unpacking                                 | 1-7  |

| Chant  | OH 0                                      |      |

| Chapt  |                                           |      |

| Config | guration and Installation                 |      |

|        | Board Configuration                       | 2-2  |

|        | AT Bus Interface                          |      |

|        | Base I/O Address Selection                | 2-3  |

|        | Interrupt and DMA Channel Selection       | 2-7  |

|        | Analog Input Configuration                | 2-7  |

|        | Input Mode                                | 2-7  |

|        | DIFF Input (Eight Channels)               | 2-8  |

|        | RSE Input (16 Channels)                   | 2-9  |

|        | NRSE Input (16 Channels)                  | 2-9  |

|        | Input Polarity and Input Range            |      |

|        | Considerations for Selecting Input Ranges |      |

|        | Analog Output Configuration               | 2-11 |

| Analog Output Reference Selection                                   | 2-11 |

|---------------------------------------------------------------------|------|

| Analog Output Polarity Selection                                    | 2-12 |

| Digital I/O Configuration                                           | 2-12 |

| Board and RTSI Clock Configuration                                  | 2-12 |

| Hardware Installation                                               | 2-13 |

| Signal Connections                                                  | 2-14 |

| Signal Connection Descriptions                                      | 2-17 |

| Analog Input Signal Connections                                     | 2-19 |

| Types of Signal Sources                                             | 2-21 |

| Floating Signal Sources                                             | 2-21 |

| Ground-Referenced Signal Sources                                    | 2-21 |

| Input Configurations                                                | 2-21 |

| Differential Connection Considerations (DIFF Input                  |      |

| Configuration)                                                      | 2-22 |

| Differential Connections for Ground-Referenced Signal               |      |

| Sources                                                             | 2-23 |

| Differential Connections for Nonreferenced or Floating              |      |

| Signal Sources                                                      | 2-24 |

| Single-Ended Connection Considerations                              | 2-26 |

| Single-Ended Connections for Floating Signal Sources                |      |

| (RSE Configuration)                                                 | 2-27 |

| Single-Ended Connections for Grounded Signal Sources                |      |

| (NRSE Configuration)                                                | 2-28 |

| Common-Mode Signal Rejection Considerations                         |      |

| Analog Output Signal Connections                                    |      |

| Digital I/O Signal Connections                                      |      |

| Power Connections                                                   | 2-32 |

| Timing Connections for Data Acquisition and Analog Output           |      |

| SCANCLK Signal                                                      |      |

| EXTSTROBE* Signal                                                   |      |

| EXTCONV* Signal                                                     |      |

| EXTTRIG* Signal                                                     |      |

| EXTGATE* Signal                                                     |      |

| EXTTMRTRIG* Signal                                                  |      |

| Counter Signal Connections                                          |      |

| Field Wiring Considerations                                         |      |

| Cabling Considerations for the AT-MIO-16X with 50-Pin I/O Connector |      |

| Cabling Considerations for the AT-MIO-16X with 68-Pin I/O Connector |      |

## Chapter 3 Theory of Operation

| Functional Overview                         | 3-1  |

|---------------------------------------------|------|

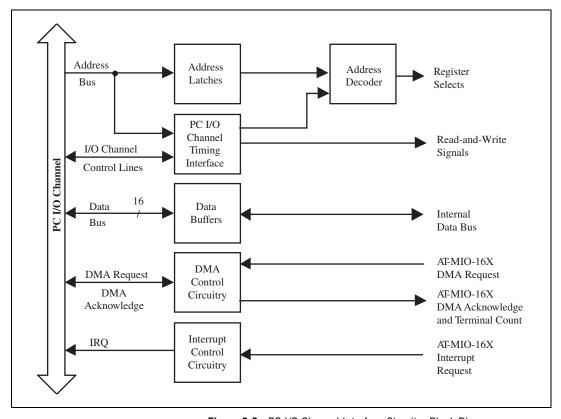

| PC I/O Channel Interface Circuitry          | 3-2  |

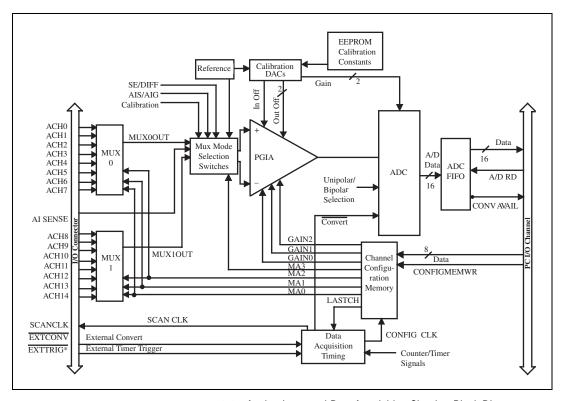

| Analog Input and Data Acquisition Circuitry | 3-5  |

| Analog Input Circuitry                      | 3-6  |

| A/D Converter                               | 3-6  |

| Analog Input Multiplexers                   |      |

| Analog Input Configuration                  | 3-6  |

| PGIA                                        |      |

| ADC FIFO Buffer                             | 3-7  |

| Analog Input Calibration                    | 3-7  |

| Data Acquisition Timing Circuitry           |      |

| Single-Read Timing                          |      |

| Single-Channel Data Acquisition Timing      |      |

| Multiple-Channel Data Acquisition           |      |

| Continuous Scanning Data Acquisition Timing |      |

| Interval Scanning Data Acquisition Timing   |      |

| Data Acquisition Rates                      |      |

| Analog Output and Timing Circuitry          |      |

| Analog Output Circuitry                     |      |

| Analog Output Configuration                 |      |

| Analog Output Calibration                   |      |

| DAC Waveform Circuitry and Timing           |      |

| DAC Waveform Circuitry                      |      |

| DAC Waveform Timing Circuitry               |      |

| FIFO Continuous Cyclic Waveform Generation  |      |

| FIFO Programmed Cyclic Waveform Generation  |      |

| FIFO Pulsed Waveform Generation             |      |

| Digital I/O Circuitry                       |      |

| Timing I/O Circuitry                        |      |

| RTSI Bus Interface Circuitry                | 3-29 |

|                                             |      |

| Chapter 4                                   |      |

| Register Map and Descriptions               |      |

| Register Map                                | 4-1  |

| Register Sizes                              | 4-3  |

| Register Description Format                 | 4-3  |

| Configuration and Status Register Group     | 4-4  |

| Command Register 1                          |      |

| Command Register 2                          | 4-9  |

| Command Register 3                   | 4-13 |

|--------------------------------------|------|

| Command Register 4                   | 4-20 |

| Status Register 1                    |      |

| Status Register 2                    | 4-30 |

| Analog Input Register Group          | 4-31 |

| ADC FIFO Register                    | 4-32 |

| CONFIGMEM Register                   |      |

| Analog Output Register Group         | 4-41 |

| DAC0 Register                        | 4-44 |

| DAC1 Register                        | 4-45 |

| ADC Event Strobe Register Group      | 4-46 |

| CONFIGMEMCLR Register                | 4-47 |

| CONFIGMEMLD Register                 | 4-48 |

| DAQ Clear Register                   | 4-49 |

| DAQ Start Register                   | 4-50 |

| Single Conversion Register           | 4-51 |

| ADC Calibration Register             | 4-52 |

| DAC Event Strobe Register Group      | 4-53 |

| TMRREQ Clear Register                | 4-54 |

| DAC Update Register                  | 4-55 |

| DAC Clear Register                   | 4-56 |

| General Event Strobe Register Group  | 4-57 |

| DMA Channel Clear Register           | 4-58 |

| DMATCA Clear Register                | 4-59 |

| DMATCB Clear Register                | 4-60 |

| External Strobe Register             | 4-61 |

| Calibration DAC 0 Load Register      | 4-62 |

| Calibration DAC 1 Load Register      | 4-63 |

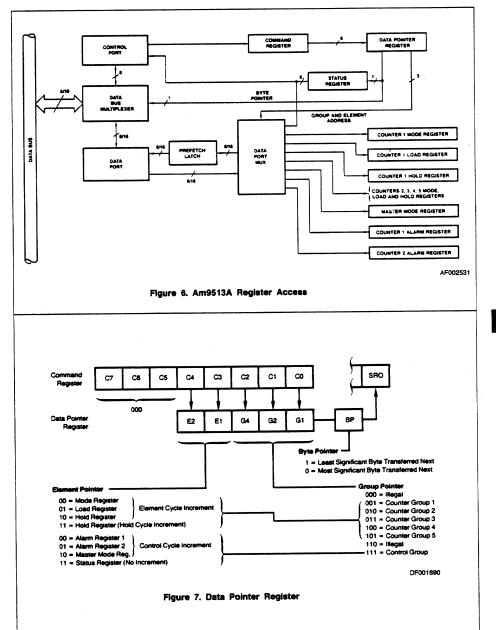

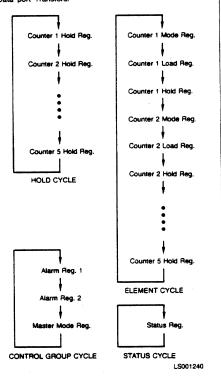

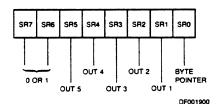

| Am9513A Counter/Timer Register Group | 4-64 |

| Am9513A Data Register                |      |

| Am9513A Command Register             | 4-66 |

| Am9513A Status Register              |      |

| Digital I/O Register Group           |      |

| Digital Input Register               | 4-69 |

| Digital Output Register              |      |

| RTSI Switch Register Group           |      |

| RTSI Switch Shift Register           |      |

| RTSI Switch Strobe Register          |      |

## Chapter 5 Programming

| Register Programming Considerations                          |      |

|--------------------------------------------------------------|------|

| Resource Allocation Considerations                           | 5-1  |

| Initializing the AT-MIO-16X                                  | 5-2  |

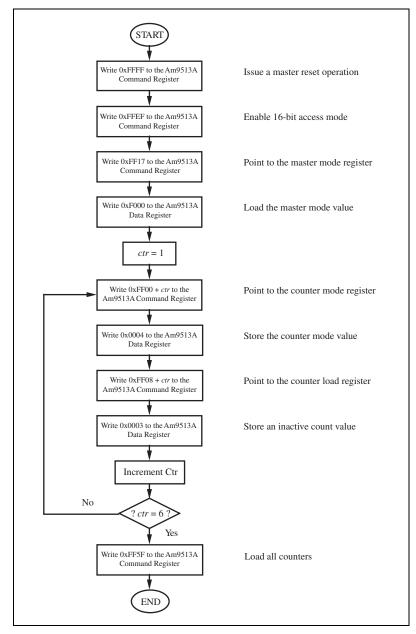

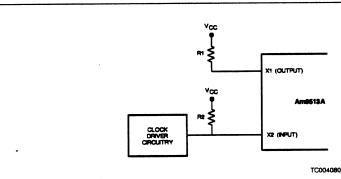

| Initializing the Am9513A                                     | 5-3  |

| Programming the Analog Input Circuitry                       | 5-5  |

| Single Conversions Using the SCONVERT or                     |      |

| EXTCONV* Signal                                              | 5-5  |

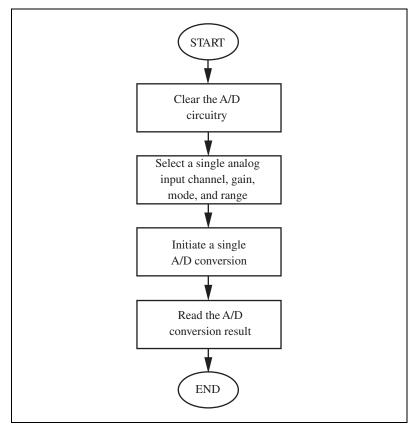

| Generating a Single Conversion                               |      |

| Reading a Single Conversion Result                           |      |

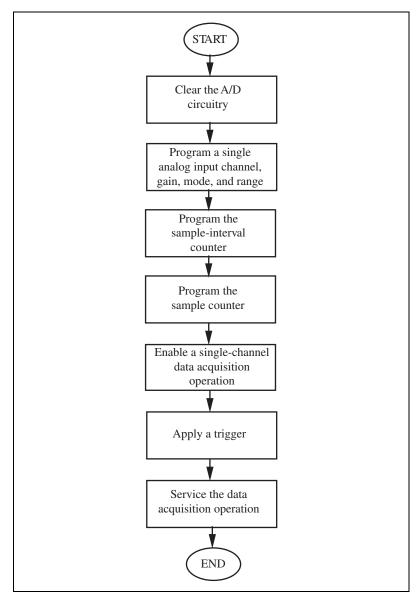

| Programming Single-Channel Data Acquisition Sequence         | 5-7  |

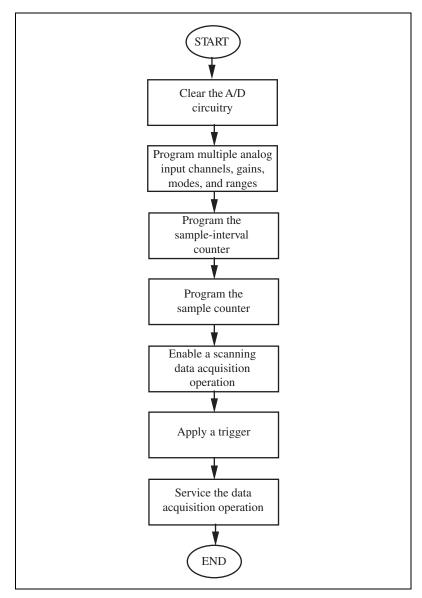

| Programming Data Acquisition Sequences with Channel Scanning | 5-10 |

| Continuous Channel Scanning Data Acquisition                 | 5-10 |

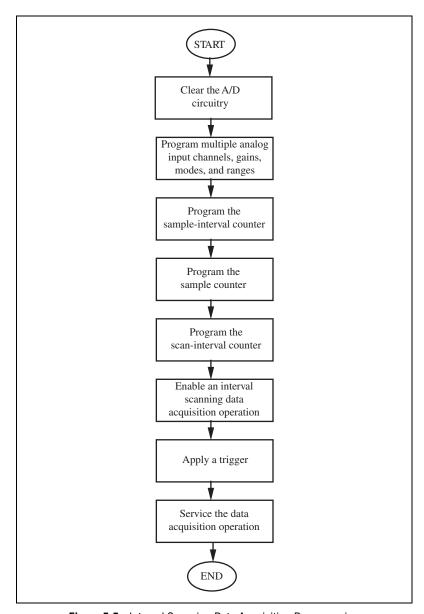

| Interval-Channel Scanning Data Acquisition                   | 5-12 |

| Data Acquisition Programming Functions                       | 5-14 |

| Clearing the Analog Input Circuitry                          | 5-14 |

| Programming Single-Analog Input Channel Configurations       | 5-15 |

| Programming Multiple-Analog Input Channel Configurations     | 5-15 |

| Programming the Sample-Interval Counter                      | 5-16 |

| Programming the Sample Counter(s)                            | 5-17 |

| Sample Counts 2 through 65,536                               | 5-18 |

| Sample Counts Greater than 65,536                            | 5-18 |

| Programming the Scan-Interval Counter                        | 5-20 |

| Applying a Trigger                                           | 5-21 |

| Servicing the Data Acquisition Operation                     | 5-22 |

| Resetting the Hardware after a Data Acquisition Operation    | 5-22 |

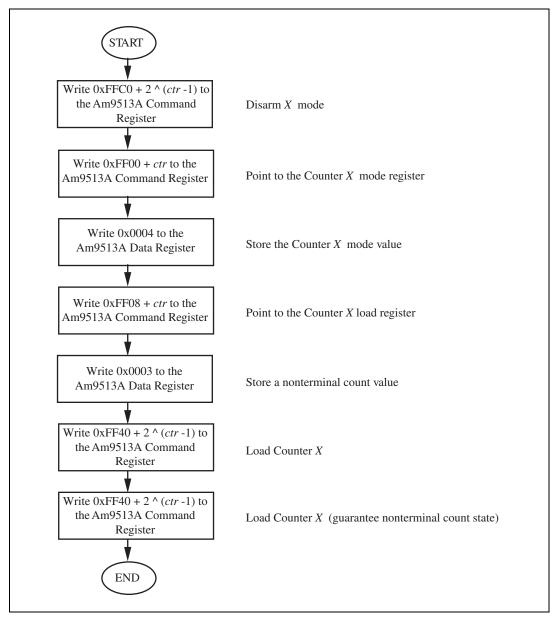

| Resetting a Single Am9513A Counter/Timer                     | 5-23 |

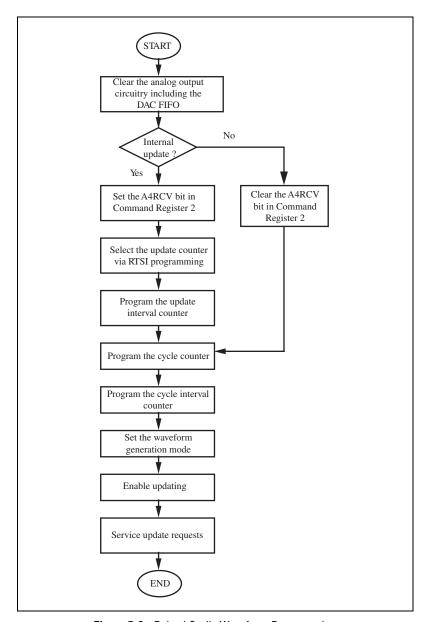

| Programming the Analog Output Circuitry                      | 5-25 |

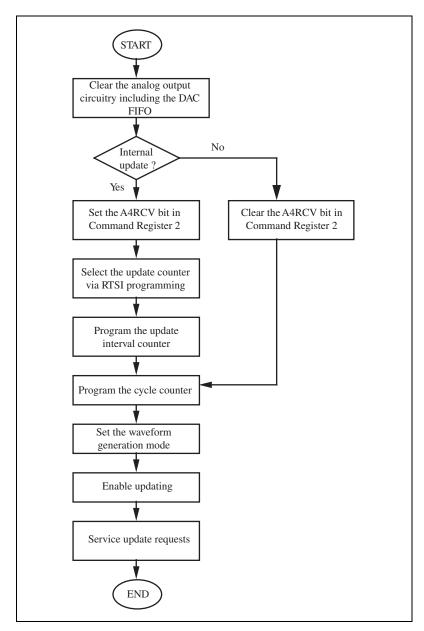

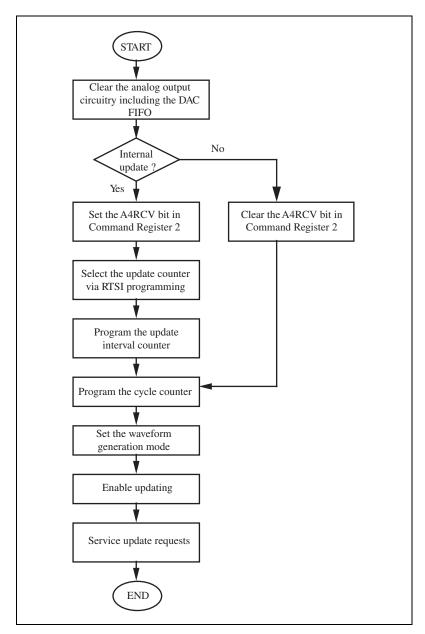

| Cyclic Waveform Generation                                   | 5-26 |

| Programmed Cycle Waveform Generation                         | 5-28 |

| Pulsed Cyclic Waveform Generation                            | 5-30 |

| Waveform Generation Programming Functions                    | 5-32 |

| Clearing the Analog Output Circuitry                         | 5-32 |

| Selecting the Internal Update Counter                        | 5-32 |

| Programming the Update-Interval Counter                      | 5-32 |

| Programming the Waveform Cycle Counter                       | 5-34 |

| Programming the Waveform Cycle Interval Counter              | 5-34 |

| Servicing Update Requests                                    |      |

| Programming the Digital I/O Circuitry                        | 5-36 |

| Programming the Am9513A Counter/Timer                        | 5-37 |

| RTSI Bus Trigger Line Programming Considerations             | 5-37 |

|                | Programming<br>Prog                                            | Signal Connection Considerations. 5-38 g the RTSI Switch 5-39 gramming DMA Operations 5-41 rrupt Programming 5-43                                                                                               |

|----------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapt<br>Calib | ter 6<br>ration Pro                                            | cedures                                                                                                                                                                                                         |

|                | Calibration I<br>Calibration I<br>Reference Ca<br>Analog Input | Equipment Requirements       6-7         DACs       6-8         alibration       6-8         t Calibration       6-9         ut Calibration       6-10                                                          |

|                | ndix A<br>fications                                            |                                                                                                                                                                                                                 |

|                | ndix B<br>onnector                                             |                                                                                                                                                                                                                 |

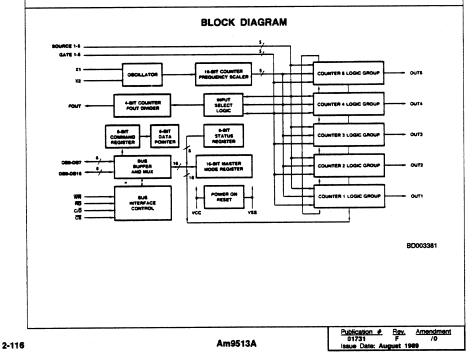

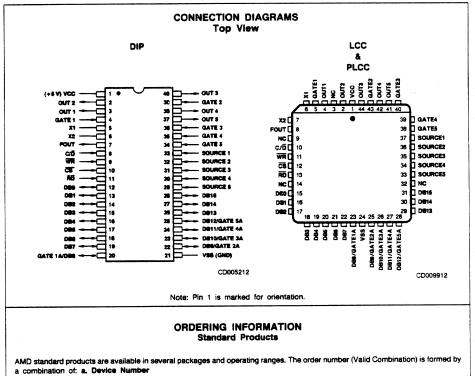

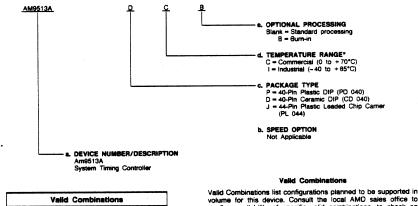

|                | ndix C<br>Am9513A                                              | Data Sheet                                                                                                                                                                                                      |

|                | ndix D<br>mer Comr                                             | nunication                                                                                                                                                                                                      |

| Gloss          | ary                                                            |                                                                                                                                                                                                                 |

| Index          |                                                                |                                                                                                                                                                                                                 |

| Figur          | es                                                             |                                                                                                                                                                                                                 |

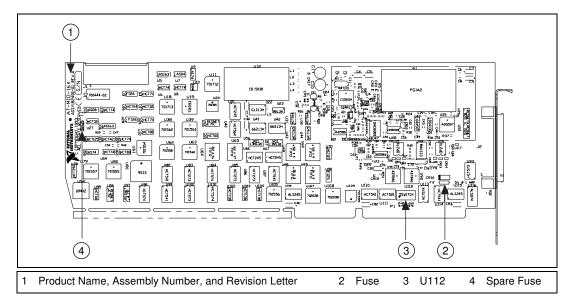

|                | Figure 1-1.                                                    | The Relationship between the Programming Environment, NI-DAQ, and Your Hardware                                                                                                                                 |

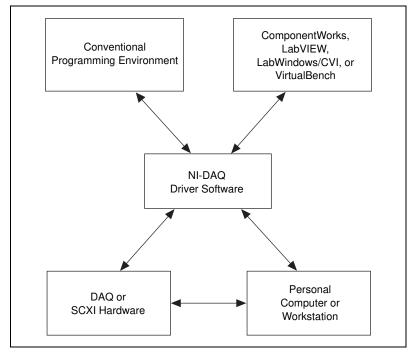

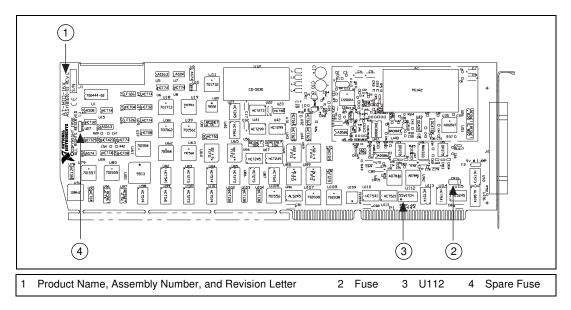

|                | Figure 2-1.<br>Figure 2-2.<br>Figure 2-3.<br>Figure 2-4.       | AT-MIO-16X with 50-Pin I/O Connector Parts Locator Diagram 2-1 AT-MIO-16X with 68-Pin I/O Connector Parts Locator Diagram 2-2 Example Base I/O Address Switch Settings 2-3 AT-MIO-16X 50-Pin I/O Connector 2-15 |

| Figure 2-5.  | AT-MIO-16X 68-Pin I/O Connector                              | 2-16 |

|--------------|--------------------------------------------------------------|------|

| Figure 2-6.  | AT-MIO-16X PGIA                                              | 2-20 |

| Figure 2-7.  | Differential Input Connections for Ground-Referenced Signals | 2-23 |

| Figure 2-8.  | Differential Input Connections for Nonreferenced Signals     | 2-24 |

| Figure 2-9.  | Single-Ended Input Connections for Nonreferenced or          |      |

|              | Floating Signals                                             | 2-27 |

| Figure 2-10. | Single-Ended Input Connections for Ground-Referenced Signals | 2-28 |

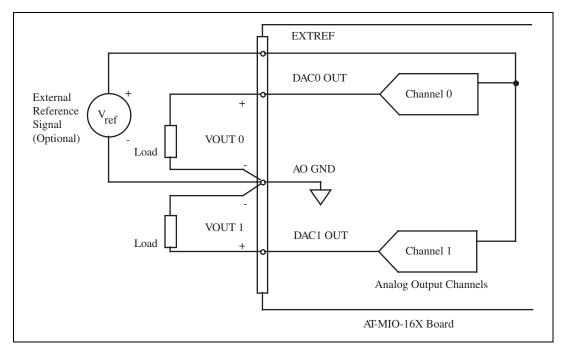

| Figure 2-11. | Analog Output Connections                                    | 2-30 |

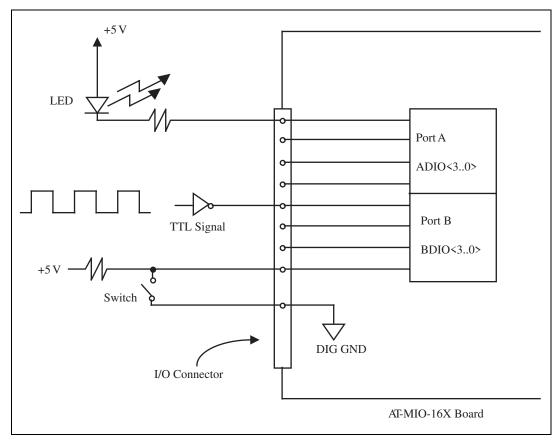

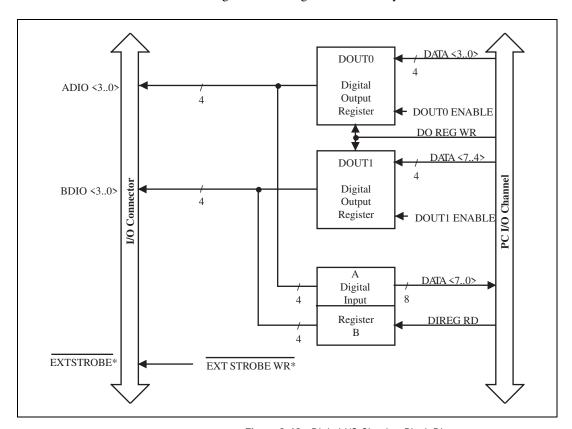

| Figure 2-12. | Digital I/O Connections                                      | 2-32 |

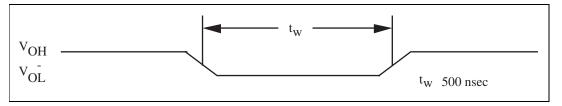

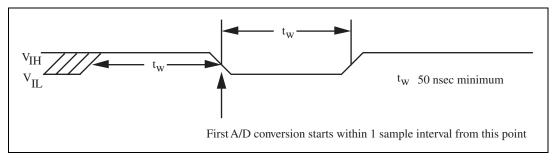

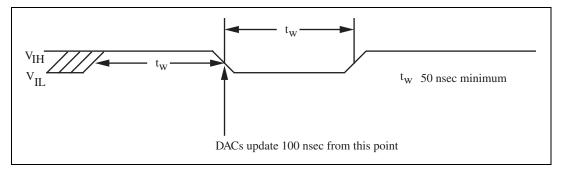

| Figure 2-13. | EXTSTROBE* Signal Timing                                     | 2-33 |

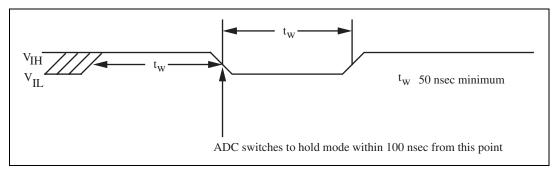

| Figure 2-14. | EXTCONV* Signal Timing                                       | 2-34 |

| Figure 2-15. | EXTTRIG* Signal Timing                                       | 2-35 |

| Figure 2-16. | EXTTMRTRIG* Signal Timing                                    | 2-36 |

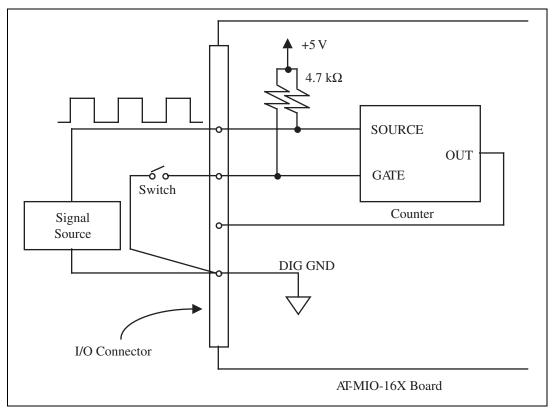

| Figure 2-17. | Event-Counting Application with External Switch Gating       | 2-38 |

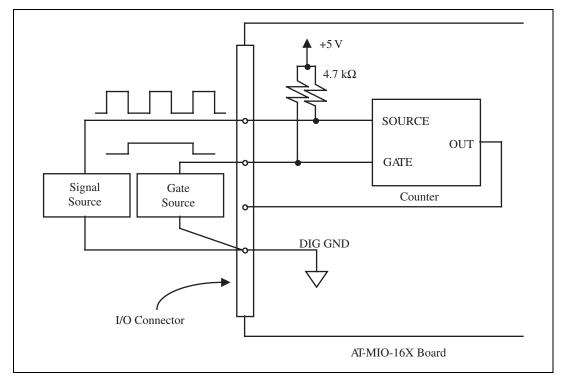

| Figure 2-18. | Frequency Measurement Application                            | 2-39 |

| Figure 2-19. | General-Purpose Timing Signals                               |      |

|              |                                                              |      |

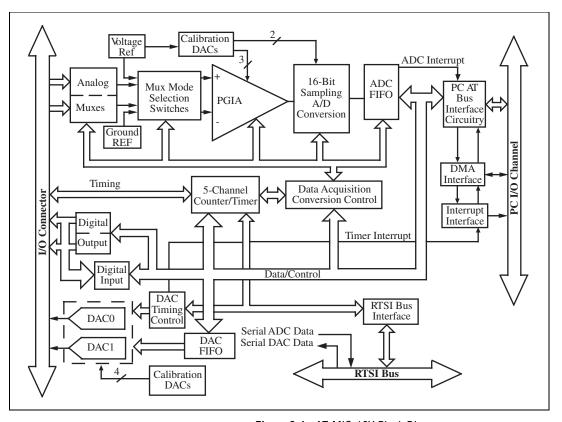

| Figure 3-1.  | AT-MIO-16X Block Diagram                                     | 3-1  |

| Figure 3-2.  | PC I/O Channel Interface Circuitry Block Diagram             | 3-3  |

| Figure 3-3.  | Analog Input and Data Acquisition Circuitry Block Diagram    | 3-5  |

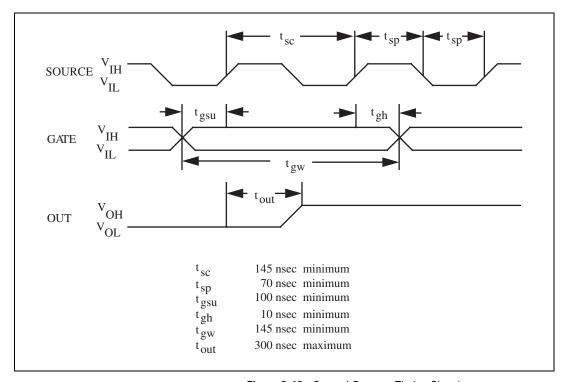

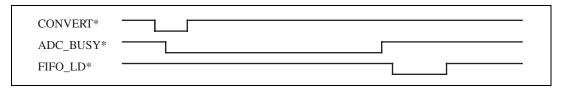

| Figure 3-4.  | ADC Conversion Timing                                        | 3-8  |

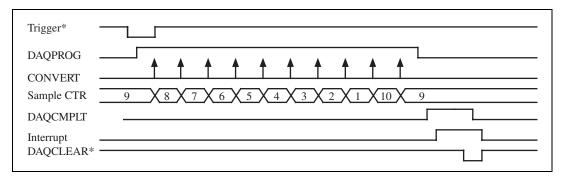

| Figure 3-5.  | Single-Channel Posttrigger Data Acquisition Timing           | 3-10 |

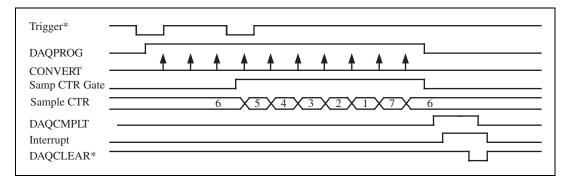

| Figure 3-6.  | Single-Channel Pretrigger Data Acquisition Timing            | 3-11 |

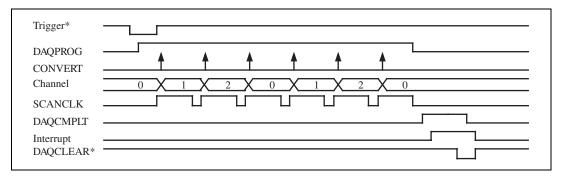

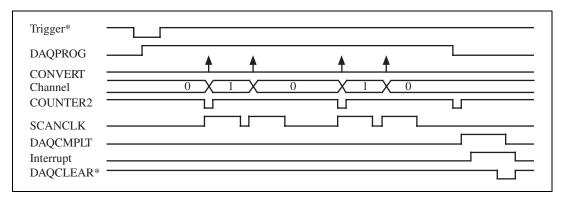

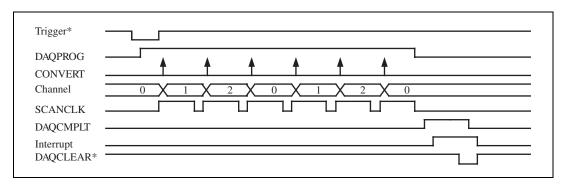

| Figure 3-7.  | Scanning Posttrigger Data Acquisition Timing                 | 3-13 |

| Figure 3-8.  | Interval Scanning Posttrigger Data Acquisition Timing        | 3-14 |

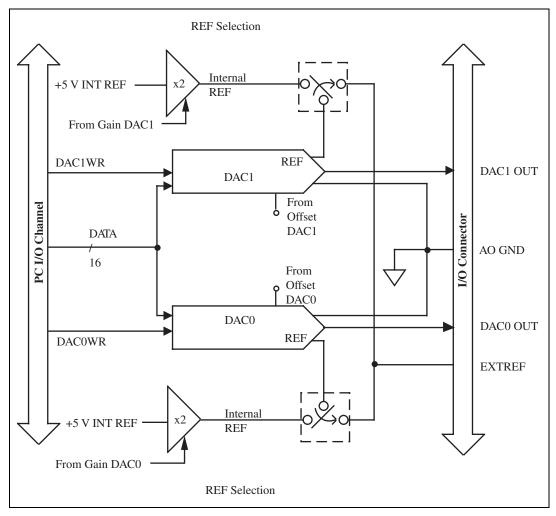

| Figure 3-9.  | Analog Output Circuitry Block Diagram                        | 3-16 |

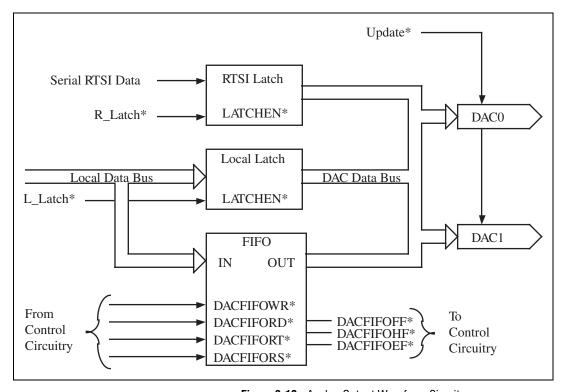

| Figure 3-10. | Analog Output Waveform Circuitry                             | 3-19 |

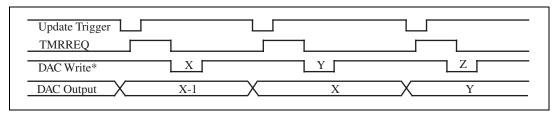

| Figure 3-11. | Posted DAC Update Timing                                     | 3-20 |

| Figure 3-12. | Analog Output Waveform Circuitry                             | 3-21 |

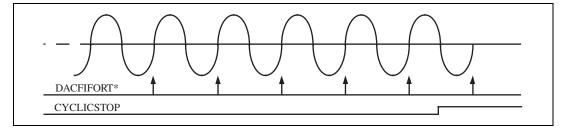

| Figure 3-13. | FIFO Cyclic Waveform Generation with Disable                 | 3-22 |

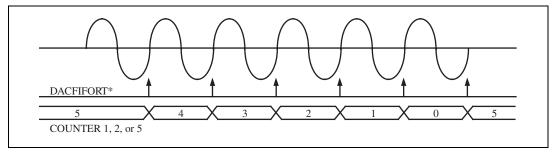

| Figure 3-14. | FIFO Programmed Cyclic Waveform Timing                       | 3-23 |

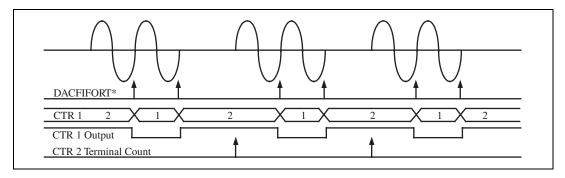

| Figure 3-15. | FIFO Pulsed Waveform Generation Timing                       | 3-23 |

| Figure 3-16. | Digital I/O Circuitry Block Diagram                          | 3-24 |

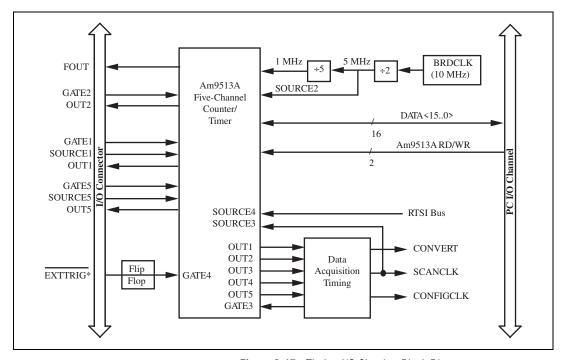

| Figure 3-17. | Timing I/O Circuitry Block Diagram                           | 3-26 |

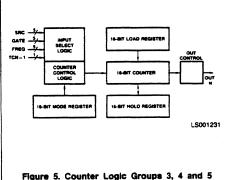

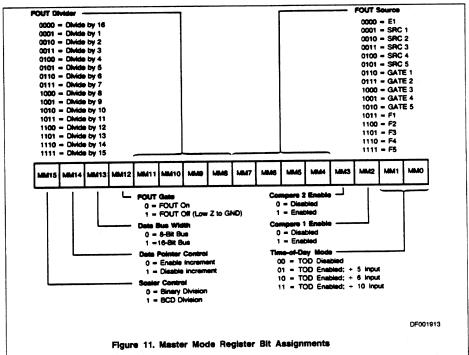

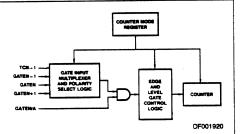

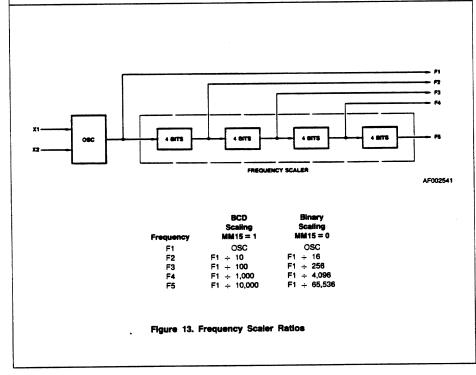

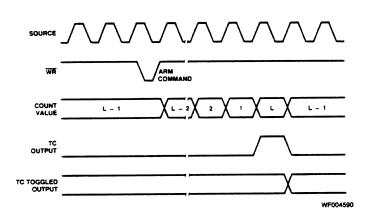

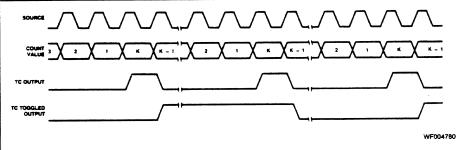

| Figure 3-18. | Counter Block Diagram                                        | 3-27 |

| Figure 3-19. | RTSI Bus Interface Circuitry Block Diagram                   | 3-29 |

| Figure 5-1.  | Initializing the Am9513A Counter/Timer                       |      |

| Figure 5-2.  | Single Conversion Programming                                |      |

| Figure 5-3.  | Single-Channel Data Acquisition Programming                  |      |

| Figure 5-4.  | Scanning Data Acquisition Programming                        | 5-11 |

| Figure 5-5.  | Interval Scanning Data Acquisition Programming               |      |

| Figure 5-6.  | Resetting an Am9513A Counter/Timer                           | 5-24 |

|      | Figure 5-7.  | Cyclic Waveform Programming                                  | 5-27 |

|------|--------------|--------------------------------------------------------------|------|

|      | Figure 5-8.  | Programmed Cycle Waveform Programming                        |      |

|      | Figure 5-9.  | Pulsed Cyclic Waveform Programming                           |      |

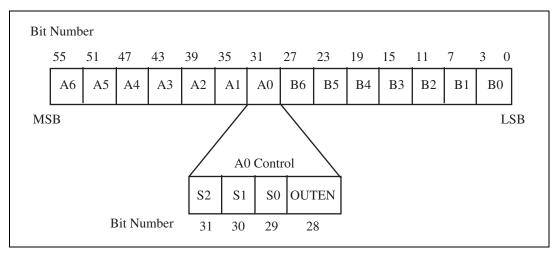

|      | Figure 5-10. | RTSI Switch Control Pattern                                  |      |

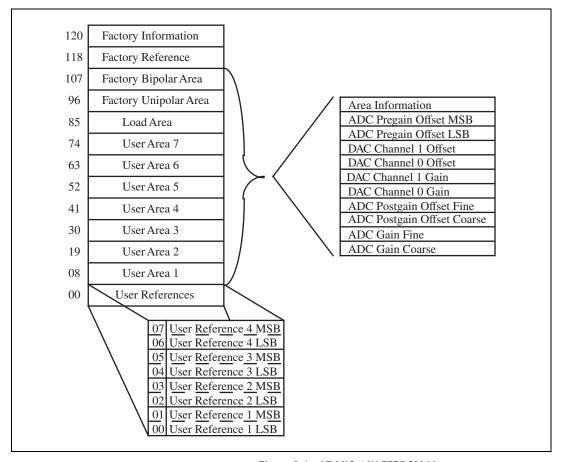

|      | Figure 6-1.  | AT-MIO-16X EEPROM Map                                        | 6-2  |

|      | Figure 6-2.  | Revision and Subrevision Field                               | 6-5  |

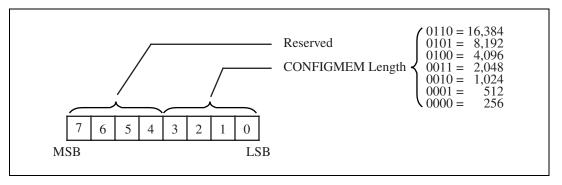

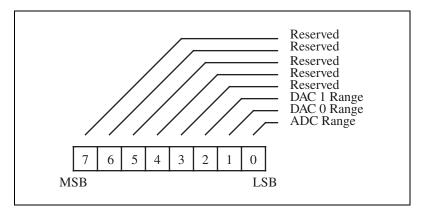

|      | Figure 6-3.  | Configuration Memory Depth Field                             | 6-5  |

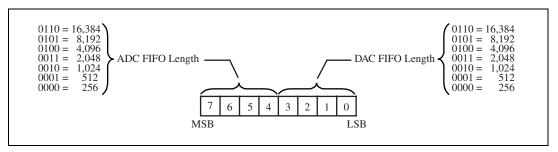

|      | Figure 6-4.  | ADC and DAC FIFO Depth Field                                 | 6-6  |

|      | Figure 6-5.  | Area Information Field                                       | 6-6  |

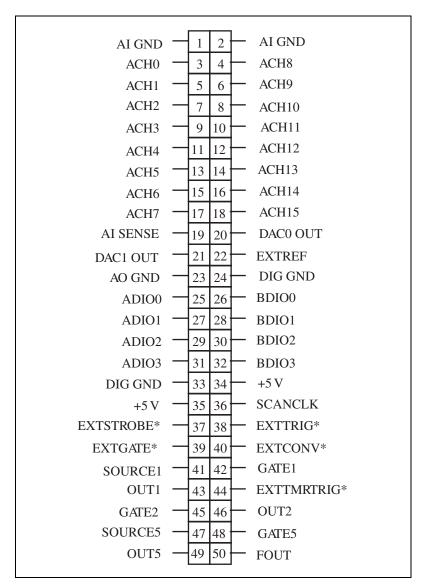

|      | Figure B-1.  | AT-MIO-16X 50-Pin I/O Connector                              | B-2  |

|      | Figure B-2.  | AT-MIO-16X 68-Pin I/O Connector                              | B-3  |

| Tabl | es           |                                                              |      |

|      | Table 2-1.   | Default Settings of National Instruments Products for the PC | 2-4  |

|      | Table 2-2.   | Switch Settings with Corresponding Base I/O Address and      |      |

|      |              | Base I/O Address Space                                       |      |

|      | Table 2-3.   | Available Input Configurations for the AT-MIO-16X            | 2-8  |

|      | Table 2-4.   | Actual Range and Measurement Precision Versus Input Range    |      |

|      |              | Selection and Gain                                           | 2-11 |

|      | Table 2-5.   | Recommended Input Configurations for Ground-Referenced and   |      |

|      |              | Floating Signal Sources                                      | 2-22 |

|      | Table 4-1.   | AT-MIO-16X Register Map                                      |      |

|      | Table 4-2.   | DMA Channel Selection                                        |      |

|      | Table 4-3.   | DMA and Interrupt Modes                                      |      |

|      | Table 4-4.   | Interrupt Level Selection                                    |      |

|      | Table 4-5.   | Board and RTSI Clock Selection                               |      |

|      | Table 4-6.   | Analog Output Waveform Modes                                 |      |

|      | Table 4-7.   | Straight Binary Mode A/D Conversion Values                   |      |

|      | Table 4-8.   | Two's Complement Mode A/D Conversion Values                  |      |

|      | Table 4-9.   | Input Configuration                                          |      |

|      | Table 4-10.  | Analog Output Voltage Versus Digital Code (Unipolar Mode)    |      |

|      | Table 4-11.  | Analog Output Voltage Versus Digital Code (Bipolar Mode)     | 4-42 |

|      | Table 5-1.   | Am9513A Counter/Timer Allocations                            |      |

|      | Table 5-2.   | RTSI Switch Signal Connections                               | 5-38 |

|      | Table 6-1.   | EEPROM Factory Area Information                              |      |

|      | Table 6-2    | Calibration DACs                                             | 6-8  |

| Table A-1. | Equivalent Offset Errors in 16-Bit Systems       | A-3 |

|------------|--------------------------------------------------|-----|

| Table A-2. | Equivalent Gain Errors in 16-Bit Systems         | A-4 |

|            | Typical Multiple-Channel Scanning Settling Times |     |

| Table B-1. | Signal Connection Descriptions                   | B-4 |

About This Manual

This manual describes the mechanical and electrical aspects of the AT-MIO-16X board and contains information concerning its operation and programming. The AT-MIO-16X is a high-performance, multifunction analog, digital, and timing I/O board for the IBM PC AT and compatibles and EISA personal computers (PCs).

## **Organization of This Manual**

The AT-MIO-16X User Manual is organized as follows:

- Chapter 1, Introduction, describes the AT-MIO-16X, lists the

contents of your AT-MIO-16X kit, the optional software, and

optional equipment, and explains how to unpack the AT-MIO-16X.

- Chapter 2, *Configuration and Installation*, explains board configuration, installation of the AT-MIO-16X into the PC, signal connections to the AT-MIO-16X, and cable considerations.

- Chapter 3, *Theory of Operation*, contains a functional overview of the AT-MIO-16X and explains the operation of each functional unit making up the AT-MIO-16X.

- Chapter 4, Register Map and Descriptions, describes in detail the address and function of each of the AT-MIO-16X control and status registers.

- Chapter 5, *Programming*, contains programming instructions for operating the circuitry on the AT-MIO-16X.

- Chapter 6, *Calibration Procedures*, discusses the calibration resources and procedures for the AT-MIO-16X analog input and analog output circuitry.

- Appendix A, Specifications, lists the specifications of the AT-MIO-16X.

- Appendix B, I/O Connector, describes the pinout and signal names for the AT-MIO-16X 50-pin I/O connector and the 68-pin I/O connector.

<>

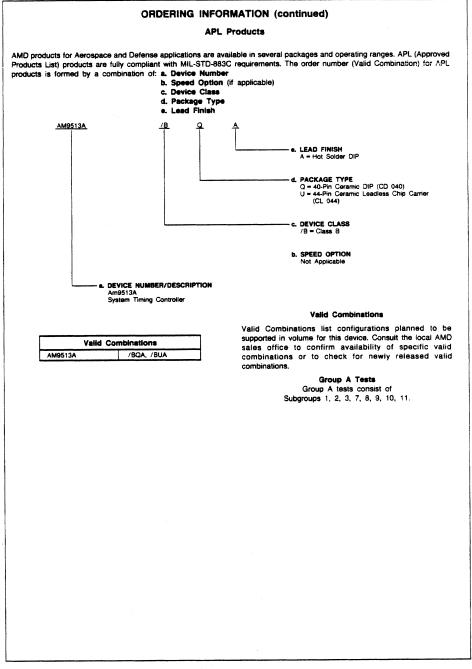

- Appendix C, AMD Am9513A Data Sheet, contains the manufacturer data sheet for the AMD Am9513A System Timing Controller integrated circuit (Advanced Micro Devices, Inc.). This controller is used on the AT-MIO-16X.

- Appendix D, Customer Communication, contains forms you can use to request help from National Instruments or to comment on our products.

- The Glossary contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, and symbols.

- The *Index* contains an alphabetical list of key terms and topics used in this manual, including the page where you can find each one.

## Conventions Used in This Manual

The following conventions are used in this manual:

Angle brackets containing numbers separated by an ellipsis represent a

range of values associated with a bit or signal name (for example,

DBIO<3..0>).

This icon to the left of bold italicized text denotes a note, which alerts

you to important information.

advises you of precautions to take to avoid injury, data loss, or a

This icon to the left of bold italicized text denotes a caution, which

system crash.

bold italic Bold italic text denotes a note, caution, or warning.

italic Italic text denotes emphasis, a cross reference, or an introduction to a

key concept.

NI-DAO NI-DAQ is used throughout this manual to refer to the NI-DAQ

software for DOS/Windows/LabWindows unless otherwise noted.

PC PC refers to the IBM PC AT and compatibles, and to EISA personal

computers.

The Glossary lists abbreviations, acronyms, metric prefixes,

mnemonics, symbols, and terms.

## **Related Documentation**

The following document contains information that you may find helpful as you read this manual:

• IBM Personal Computer AT Technical Reference

You may also want to consult the following Advanced Micro Devices information if you plan to program the Am9513A Counter/Timer used on the AT-MIO-16X:

Am9513A/Am9513 System Timing Controller

## **Customer Communication**

National Instruments want to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix D, *Customer Communication*, at the end of this manual.

Introduction

This chapter describes the AT-MIO-16X, lists the contents of your AT-MIO-16X kit, the optional software, and optional equipment, and explains how to unpack the AT-MIO-16X.

## About the AT-MIO-16X

Congratulations on your purchase of the National Instruments AT-MIO-16X. The AT-MIO-16X is a high-performance, software-configurable 16-bit DAQ board for laboratory, test and measurement, and data acquisition and control applications. The board performs *high-accuracy* measurements with self-calibration, high-speed settling to 16 bits, noise as low as 0.8 LSBrms, and a maximum DNL of ±0.5 LSB. Because of its large FIFOs and dual-channel DMA, the AT-MIO-16X can achieve *high performance*, even when used in environments that may have long interrupt latencies, such as Windows.

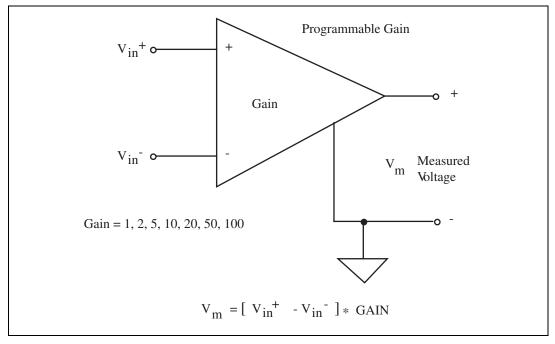

Because off-the-shelf instrumentation amplifiers require 500  $\mu$ sec and more to settle to 16-bit accuracy at high gains when sampling multiple channels, National Instruments developed the *NI-PGIA*. The NI-PGIA, which is used on the AT-MIO-16X, is an instrumentation amplifier that settles to 16 bits in 40  $\mu$ s, even when the board is used at its highest gain of 100.

A common problem with DAQ boards is that you cannot easily synchronize several measurement functions to a common trigger or timing event. The AT-MIO-16X has the Real-Time System Integration (RTSI) bus to solve this problem. The *RTSIbus* consists of our custom RTSI bus interface chip and a ribbon cable to route timing and trigger signals between several functions on one or more DAQ boards in your PC.

The AT-MIO-16X can interface to the Signal Conditioning eXtensions for Instrumentation (*SCXI*) system so that you can acquire over 3,000 analog signals from thermocouples, RTDs, strain gauges, voltage sources, and current sources. You can also acquire or generate digital

signals for communication and control. SCXI is the instrumentation front end for plug-in DAQ boards.

## **Analog Input**

The AT-MIO-16X is a high-performance multifunction analog, digital, and timing I/O board for the PC. The AT-MIO-16X has a 10 µsec, 16-bit, sampling ADC that can monitor a single input channel, or scan through the 16 single-ended or 8 differential channels (expandable with National Instruments multiplexing products) at a programmable gain of 1, 2, 5, 10, 20, 50, or 100 for unipolar or bipolar input ranges. A 512-word ADC FIFO buffer can perform seamless data acquisition at the maximum rate without data loss. Internal or external triggering and sampling are supported. If signal conditioning or additional analog inputs are required, you can use the SCXI signal conditioning modules, SCXI multiplexer products, or the AMUX-64T multiplexer board.

You can use the NI-DAQ software included with the AT-MIO-16X to calibrate the analog input circuitry. This software adjusts the offset and gain errors to zero by means of board-level calibration DACs. You can store calibration DAC constants resulting from the calibration procedure in the onboard EEPROM for later use. See Chapter 6, *Calibration Procedures*, for additional information on calibration procedures for the AT-MIO-16X.

## **Analog Output**

The AT-MIO-16X also has two deglitched, double-buffered, multiplying, 16-bit DACs that may be configured for a unipolar or bipolar voltage output range. An onboard, +10-V reference is the internal reference to the circuitry of the DAC. A 2,048-word DAC FIFO buffer allows seamless waveform generation at the maximum rate without data loss. The DAC FIFO can perform cyclic waveform generation directly from the FIFO, independent of the PC interface. You can use the analog output circuitry for internal timer and external signal update capability for waveform generation.

You calibrate the analog output circuitry through the NI-DAQ software provided with the board. This software adjusts the DAC offset and gain errors of each channel to zero by means of board-level calibration DACs. Calibration DAC constants resulting from the calibration procedure may be stored in the onboard EEPROM for later use. See Chapter 6, *Calibration Procedures*, for additional information on calibration procedures for the AT-MIO-16X.

## Digital and Timing I/O

In addition to the analog input and analog output capabilities of the AT-MIO-16X, the AT-MIO-16X also has eight digital I/O lines that can sink up to 24 mA of current, and three independent 16-bit counter/timers for frequency counting, event counting, and pulse output applications. The AT-MIO-16X has timer-generated interrupts, a high-performance RTSI bus interface, and four triggers for system-level timing.

You can use the AT-MIO-16X, with its multifunction analog, digital, and timing I/O, in many applications, including machine and process control automation, level monitoring and control, instrumentation, electronic testing, and many others. You can use the multichannel analog input for signal and transient analysis, data logging, and chromatography. The two analog output channels are useful for machine and process control, analog function generation, 16-bit resolution voltage source, and programmable signal attenuation. You can use the eight TTL-compatible digital I/O lines for machine and process control, intermachine communication, and relay switching control. The three 16-bit counter/timers are useful for such functions as pulse and clock generation, timed control of laboratory equipment, and frequency, event, and pulse-width measurement. With all these functions on one board, you can automatically monitor and control laboratory processes.

The AT-MIO-16X is interfaced to the National Instruments RTSI bus. With this bus, National Instruments AT Series boards can send timing signals to each other. The AT-MIO-16X can send signals from the onboard counter/timer to another board, or another board can control single and multiple A/D conversions on the AT-MIO-16X.

Detailed specifications for the AT-MIO-16X are listed in Appendix A, *Specifications*.

## What You Need to Get Started

To set up and use your AT-MIO-16X Series board, you will need the following:

• One of the following boards:

AT-MIO-16X 50-pin AT-MIO-16X 68-pin

| AT-MIO-16X User Manual                                    |

|-----------------------------------------------------------|

| One of the following software packages and documentation: |

| ComponentWorks                                            |

| LabVIEW for Windows                                       |

| LabWindows/CVI for Windows                                |

| Measure                                                   |

| NI-DAQ for PC Compatibles                                 |

| VirtualBench                                              |

☐ Your computer

## **Software Programming Choices**

You have several options to choose from when programming your National Instruments DAQ and SCXI hardware. You can use National Instruments application software, NI-DAQ, or register-level programming.

#### **National Instruments Application Software**

ComponentWorks contains tools for data acquisition and instrument control built on NI-DAQ driver software. ComponentWorks provides a higher-level programming interface for building virtual instruments through standard OLE controls and DLLs. With ComponentWorks, you can use all of the configuration tools, resource management utilities, and interactive control utilities included with NI-DAQ.

LabVIEW features interactive graphics, a state-of-the-art user interface, and a powerful graphical programming language. The LabVIEW Data Acquisition VI Library, a series of VIs for using LabVIEW with National Instruments DAQ hardware, is included with LabVIEW. The LabVIEW Data Acquisition VI Library is functionally equivalent to NI-DAQ software.

LabWindows/CVI features interactive graphics, state-of-the-art user interface, and uses the ANSI standard C programming language. The LabWindows/CVI Data Acquisition Library, a series of functions for using LabWindows/CVI with National Instruments DAQ hardware, is included with the NI-DAQ software kit. The LabWindows/CVI Data Acquisition Library is functionally equivalent to the NI-DAQ software.

VirtualBench features virtual instruments that combine DAQ products, software, and your computer to create a stand-alone instrument with the added benefit of the processing, display, and storage capabilities of your computer. VirtualBench instruments load and save waveform data to disk in the same forms that can be used in popular spreadsheet programs and word processors.

Using ComponentWorks, LabVIEW, LabWindows/CVI, or VirtualBench software will greatly reduce the development time for your data acquisition and control application.

#### NI-DAQ Driver Software

The NI-DAQ driver software is included at no charge with all National Instruments DAQ hardware. NI-DAQ is not packaged with SCXI or accessory products, except for the SCXI-1200. NI-DAQ has an extensive library of functions that you can call from your application programming environment. These functions include routines for analog input (A/D conversion), buffered data acquisition (high-speed A/D conversion), analog output (D/A conversion), waveform generation (timed D/A conversion), digital I/O, counter/timer operations, SCXI, RTSI, self-calibration, messaging, and acquiring data to extended memory.

NI-DAQ has both high-level DAQ I/O functions for maximum ease of use and low-level DAQ I/O functions for maximum flexibility and performance. Examples of high-level functions are streaming data to disk or acquiring a certain number of data points. An example of a low-level function is writing directly to registers on the DAQ device. NI-DAQ does not sacrifice the performance of National Instruments DAQ devices because it lets multiple devices operate at their peak.

NI-DAQ also internally addresses many of the complex issues between the computer and the DAQ hardware such as programming interrupts and DMA controllers. NI-DAQ maintains a consistent software interface among its different versions so that you can change platforms with minimal modifications to your code. Whether you are using conventional programming languages or National Instruments application software, your application uses the NI-DAQ driver software, as illustrated in Figure 1-1.

Figure 1-1. The Relationship between the Programming Environment, NI-DAQ, and Your Hardware

## **Register-Level Programming**

The final option for programming any National Instruments DAQ hardware is to write register-level software. Writing register-level programming software can be very time-consuming and inefficient, and is not recommended for most users.

Even if you are an experienced register-level programmer, using NI-DAQ or application software to program your National Instruments DAQ hardware is easier than, and as flexible as, register-level programming, and can save weeks of development time.

## **Optional Equipment**

National Instruments offers a variety of products to use with your AT-MIO-16X board, including cables, connector blocks, and other accessories, as follows:

- Cables and cable assemblies, shielded and ribbon

- Connector blocks, shielded and unshielded 50 and 68-pin screw terminals

- Real Time System Integration (RTSI) bus cables

- SCXI modules and accessories for isolating, amplifying, exciting, and multiplexing signals for relays and analog output. With SCXI you can condition and acquire up to 3,072 channels.

- Low channel count signal conditioning modules, boards, and accessories, including conditioning for strain gauges and RTDs, simultaneous sample and hold, and relays

For more specific information about these products, refer to your National Instruments catalogue or call the office nearest you.

## Unpacking

Your AT-MIO-16X board is shipped in an antistatic package to prevent electrostatic damage to the board. Electrostatic discharge can damage several components on the board. To avoid such damage in handling the board, take the following precautions:

- Ground yourself via a grounding strap or by holding a grounded object.

- Touch the antistatic package to a metal part of your computer chassis before removing the board from the package.

- Remove the board from the package and inspect the board for loose components or any other sign of damage. Notify National Instruments if the board appears damaged in any way. *Do not* install a damaged board into your computer.

- *Never* touch the exposed pins of connectors.

# Configuration and Installation

This chapter explains board configuration, installation of the AT-MIO-16X into the PC, signal connections to the AT-MIO-16X, and cable considerations.

Figure 2-1. AT-MIO-16X with 50-Pin I/O Connector Parts Locator Diagram

Figure 2-2. AT-MIO-16X with 68-Pin I/O Connector Parts Locator Diagram

## **Board Configuration**

The AT-MIO-16X contains one DIP switch to configure the base address selection for the AT bus interface. The remaining resource selections, such as DMA and interrupt channel selections, are determined by programming the individual registers in the AT-MIO-16X register set. The general location of the registers in the I/O space of the PC is determined by the base address selection, whereas the specific location of the registers within the register set is determined by the AT-MIO-16X decode circuitry.

#### **AT Bus Interface**

Operation of the AT-MIO-16X multifunction I/O board is controlled through accesses to registers within the board register set. Some of the registers in the register set retain data written to them to determine board operation. Other registers in the register set contain important status information necessary for proper sequencing of events. Still other registers perform functions by accessing them either by reading from or writing to their location. However, these registers do not retain pertinent data when written to, nor do they provide pertinent status information when read.

The PC defines accesses to plug-in boards to be I/O mapped accesses within the I/O space of the computer. Locations are either written to or read from as bytes or words. Each register in the register set is mapped to a certain offset from the base address selection of the board as read or write, and as a word or byte location as defined by the decode circuitry.

#### Base I/O Address Selection

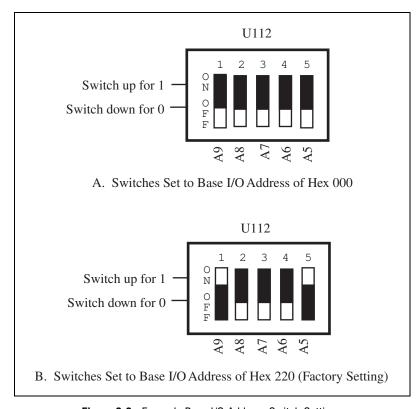

The AT-MIO-16X is configured at the factory to a base I/O address of 220 hex. This base address setting is suitable for most systems. However, if your system has other hardware at this base I/O address, you must change either the AT-MIO-16X base address DIP switch or the other hardware base address to avoid a conflict. Figure 2-3 shows a graphical representation of the base address selection DIP switch, and also shows how to reconfigure the selected base address.

Figure 2-3. Example Base I/O Address Switch Settings

The base address DIP switch is arranged so that a logical 1 or *true* state for the associated address selection bit is selected by pushing the toggle switch up, or toward the top of the board. Alternately, a logical 0 or *false* state is selected by pushing the toggle switch down, or toward the bottom of the board. In Figure 2-3B, A9 is up (true), A8 through A6 are low (false), and A5 is up (true). This represents a binary value of 10001XXXXX, or hex 220. The Xs indicate don't care bits and are the five least significant bits (LSBs) of the address (A4 through A0) used by the AT-MIO-16X circuitry to decode the individual register selections. The don't care bits indicate the size of the register space. In this case, the AT-MIO-16X uses I/O address hex 220 through hex 23F in the factory-default setting.

Note:

If you change the AT-MIO-16X base I/O address, you must make a corresponding change to any software packages you use with the AT-MIO-16X. Table 2-1 lists the default settings of other National Instruments products for the PC. Table 2-2 lists the possible switch settings, the corresponding base I/O address, and the base I/O address space used for that setting. For more information about the I/O address of your PC, refer to the technical reference manual for your computer.

**Table 2-1.** Default Settings of National Instruments Products for the PC

| Board        | DMA<br>Channel | Interrupt<br>Level | Base I/O<br>Address |

|--------------|----------------|--------------------|---------------------|

| AT-A2150     | None*          | None*              | 120 hex             |

| AT-AO-6/10   | Channel 5      | Lines 11, 12       | 1C0 hex             |

| AT-DIO-32F   | Channels 5, 6  | Lines 11, 12       | 240 hex             |

| AT-DSP2200   | None*          | None*              | 120 hex             |

| AT-GPIB      | Channel 5      | Line 11            | 2C0 hex             |

| AT-MIO-16    | Channels 6, 7  | Line 10            | 220 hex             |

| AT-MIO-16D   | Channels 6, 7  | Lines 5, 10        | 220 hex             |

| AT-MIO-16F-5 | Channels 6, 7  | Line 10            | 220 hex             |

| AT-MIO-16X   | None*          | None*              | 220 hex             |

Table 2-1. Default Settings of National Instruments Products for the PC (Continued)

| Board                                                                        | DMA<br>Channel | Interrupt<br>Level | Base I/O<br>Address |

|------------------------------------------------------------------------------|----------------|--------------------|---------------------|

| AT-MIO-64F-5                                                                 | None*          | None*              | 220 hex             |

| GPIB-PCII                                                                    | Channel 1      | Line 7             | 2B8 hex             |

| GPIB-PCIIA                                                                   | Channel 1      | Line 7             | 02E1 hex            |

| GPIB-PCIII                                                                   | Channel 1      | Line 7             | 280 hex             |

| Lab-PC                                                                       | Channel 3      | Line 5             | 260 hex             |

| PC-DIO-24                                                                    | None           | Line 5             | 210 hex             |

| PC-DIO-96                                                                    | None           | Line 5             | 180 hex             |

| PC-LPM-16                                                                    | None           | Line 5             | 260 hex             |

| PC-TIO-10                                                                    | None           | Line 5             | 1A0 hex             |

| * These settings are software configurable and are disabled at startup time. |                |                    |                     |

Table 2-2. Switch Settings with Corresponding Base I/O Address and

| Switch Setting |    |    |    |    | Page I/O  | Base I/O                    |

|----------------|----|----|----|----|-----------|-----------------------------|

| A9             | A8 | A7 | A6 | A5 | _         | Address Space<br>Used (hex) |

| 0              | 0  | X  | X  | X  | 000 - E00 | Reserved                    |

| 0              | 1  | 0  | 0  | 0  | 100       | 100 - 11F                   |

| 0              | 1  | 0  | 0  | 1  | 120       | 120 - 13F                   |

| 0              | 1  | 0  | 1  | 0  | 140       | 140 - 15F                   |

| 0              | 1  | 0  | 1  | 1  | 160       | 160 - 17F                   |

| 0              | 1  | 1  | 0  | 0  | 180       | 180 - 19F                   |

| 0              | 1  | 1  | 0  | 1  | 1A0       | 1A0 - 1BF                   |

**Table 2-2.** Switch Settings with Corresponding Base I/O Address and Base I/O Address Space (Continued)

| Switch Setting |    |    |           |           | Page I/O                  | Base I/O                    |

|----------------|----|----|-----------|-----------|---------------------------|-----------------------------|

| A9             | A8 | A7 | <b>A6</b> | <b>A5</b> | Base I/O<br>Address (hex) | Address Space<br>Used (hex) |

| 0              | 1  | 1  | 1         | 0         | 1C0                       | 1C0 - 1DF                   |

| 0              | 1  | 1  | 1         | 1         | 1E0                       | 1E0 - 1FF                   |

| 1              | 0  | 0  | 0         | 0         | 200                       | 200 - 21F                   |

| 1              | 0  | 0  | 0         | 1         | 220                       | 220 - 23F                   |

| 1              | 0  | 0  | 1         | 0         | 240                       | 240 - 25F                   |

| 1              | 0  | 0  | 1         | 1         | 260                       | 260 - 27F                   |

| 1              | 0  | 1  | 0         | 0         | 280                       | 280 - 29F                   |

| 1              | 0  | 1  | 0         | 1         | 2A0                       | 2A0 - 2BF                   |

| 1              | 0  | 1  | 1         | 0         | 2C0                       | 2C0 - 2DF                   |

| 1              | 0  | 1  | 1         | 1         | 2E0                       | 2E0 - 2FF                   |

| 1              | 1  | 0  | 0         | 0         | 300                       | 300 - 31F                   |

| 1              | 1  | 0  | 0         | 1         | 320                       | 320 - 33F                   |

| 1              | 1  | 0  | 1         | 0         | 340                       | 340 - 35F                   |

| 1              | 1  | 0  | 1         | 1         | 360                       | 360 - 37F                   |

| 1              | 1  | 1  | 0         | 0         | 380                       | 380 - 39F                   |

| 1              | 1  | 1  | 0         | 1         | 3A0                       | 3A0 - 3BF                   |

| 1              | 1  | 1  | 1         | 0         | 3C0                       | 3C0 - 3DF                   |

| 1              | 1  | 1  | 1         | 1         | 3E0                       | 3E0 - 3FF                   |

## **Interrupt and DMA Channel Selection**

The base I/O address selection is the only resource on the AT-MIO-16X board that must be set manually before the board is placed into the PC. The interrupt level and DMA channels used by the AT-MIO-16X are selected via registers in the AT-MIO-16X register set. The AT-MIO-16X powers up with all interrupt and DMA requests disabled. To use the interrupt capability of the AT-MIO-16X, an interrupt level must first be selected via register programming, then the specific interrupt mode must be enabled. The same method holds for DMA channel selection. To use the DMA capability of the board, one or two DMA channels must be selected through the appropriate register, then the specific DMA mode must be enabled. It is possible to have interrupt and DMA resources concurrently enabled.

The interrupt lines supported by the AT-MIO-16X hardware are IRQ3, IRQ4, IRQ5, IRQ7, IRQ10, IRQ11, IRQ12, and IRQ15. The DMA channels supported are Channels 0 through 3, and Channels 5 through 7. If you use the AT-MIO-16X in an AT-type computer, you should only use DMA Channels 5 through 7 because these are the only 16-bit channels available. If you use the board in an EISA computer, all channels are capable of 16-bit transfers and you can use them. The AT-MIO-16X *does not* use and *cannot* be configured to use the 8-bit DMA Channels 0 through 3 on the PC I/O channel for 16-bit transfers.

## **Analog Input Configuration**

The analog input section of the AT-MIO-16X is software configurable. You can select different analog input configurations by programming the appropriate register in the AT-MIO-16X register set. The following paragraphs describe in detail each of the analog input categories.

#### **Input Mode**

The AT-MIO-16X offers three different input modesSE) input, referenced single-ended (RSE) input, and differential (DIFF) input. The single-ended input configurations use up to 16 channels. The DIFF input configuration uses up to eight channels. Input modes are programmed on a per channel basis for multimode scanning. For example, the circuitry can be configured to effectively scan 12 channels, four differentially configured channels and eight single-ended channels. The input configurations are described in Table 2-3.

| Configuration | Description                                                                                                              |

|---------------|--------------------------------------------------------------------------------------------------------------------------|

| DIFF          | Differential configurationnput of the PGIA tied to the multiplexer output of Channels 8 through 15.                      |

| RSE           | Referenced single-ended configurationve (–) input of the PGIA referenced to analog ground.                               |

| NRSE          | Nonreferenced single-ended configurationative (–) input of the PGIA tied to AI SENSE and <i>not</i> connected to ground. |

**Table 2-3.** Available Input Configurations for the AT-MIO-16X

While reading the following paragraphs, you may find it helpful to refer to the *Analog Input Signal Connections* section later in this chapter, which contains diagrams showing the signal paths for the three configurations.

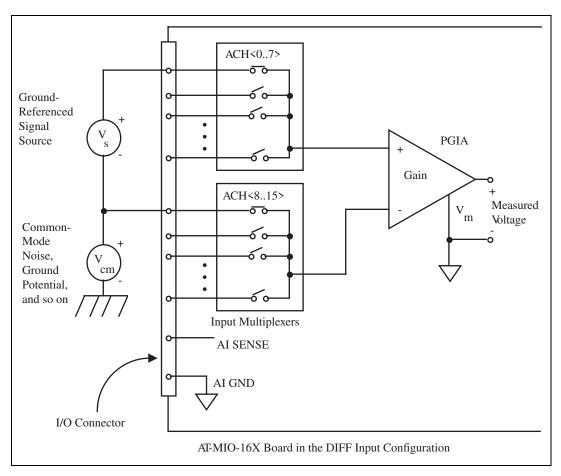

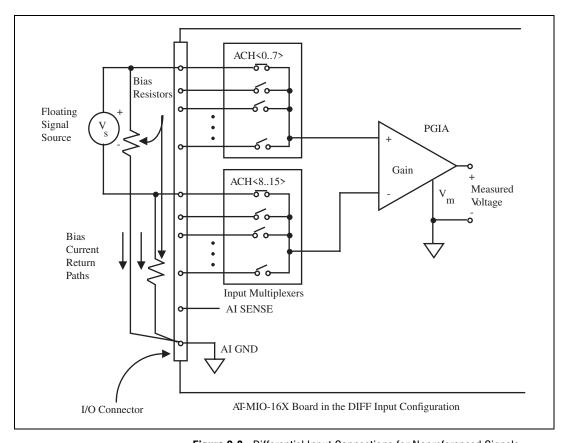

## **DIFF Input (Eight Channels)**

DIFF input means that each input signal has its own reference, and the difference between each signal and its reference is measured. The signal and its reference are assigned an input channel. This is the recommended configuration. With this input configuration, the AT-MIO-16X can monitor up to eight different analog input signals. This configuration is selected via software. See the configuration memory register and Table 4-9 in Chapter 4, *Register Map and Descriptions*. The results of this configuration are as follows:

- One of Channels 0 through 7 is tied to the positive (+) input of the PGIA.

- One of Channels 8 through 15 is tied to the negative (–) input of the PGIA.

- Multiplexer control is configured to control up to eight input channels.

- AI SENSE may be driven by the board analog input ground or left unconnected.

Considerations for using the DIFF input configuration are discussed in the *Signal Connections* section later in this chapter. Figure 2-8 shows a schematic diagram of this configuration.

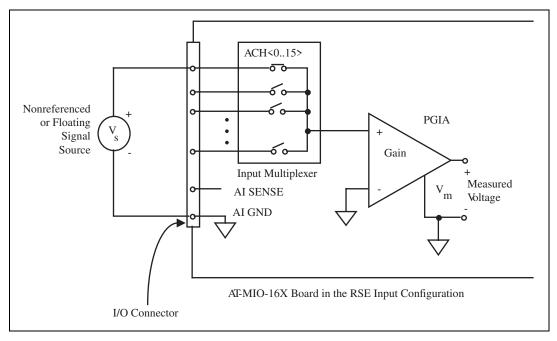

## **RSE Input (16 Channels)**

RSE input means that all input signals are referenced to a common ground point that is also tied to the analog input ground of the AT-MIO-16X board. The negative (–) input of the differential input amplifier is tied to the analog ground. This configuration is useful when measuring floating signal sources. See the *Types of Signal Sources* section later in this chapter for more information. With this input configuration, the AT-MIO-16X can monitor up to 16 different analog input signals. This configuration is selected via software. See the configuration memory register and Table 4-9 in Chapter 4, *Register Map and Descriptions*. The results of this configuration are as follows:

- The negative (–) input of the PGIA is tied to the PGIA signal ground.

- Multiplexer outputs are tied together into the positive (+) input of the PGIA.

- Multiplexer control is configured to control up to 16 input channels.

- AI SENSE may be driven by the board analog input ground or left unconnected.

Considerations for using the RSE configuration are discussed in the *Signal Connections* section later in this chapter. Figure 2-18 shows a schematic diagram of this configuration.

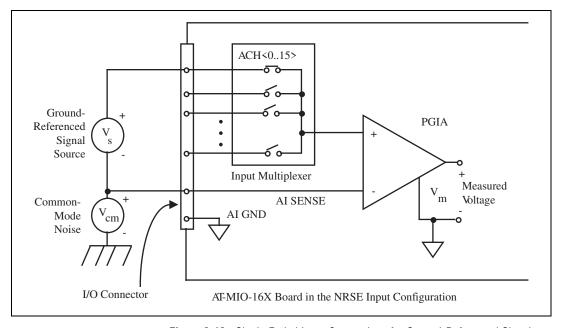

#### NRSE Input (16 Channels)

NRSE input means that all input signals are referenced to the same common-mode voltage, but this common-mode voltage can float with respect to the analog ground of the AT-MIO-16X board. This common-mode voltage is subsequently subtracted from the signals by the input PGIA. This configuration is useful when measuring ground-referenced signal sources. See the *Types of Signal Sources* section later in this chapter for more information. With this input configuration, the AT-MIO-16X can measure up to 16 different analog input signals. This configuration is selected via software. See the configuration memory register and Table 4-9 in Chapter 4, *Register Map and Descriptions*, for additional information. The results of this configuration are as follows:

- AI SENSE is tied into the negative (–) input of the PGIA.

- Multiplexer outputs are tied together into the positive (+) input of the PGIA.

Multiplexer control is configured to control up to 16 input channels.

Note:

The NRSE input mode is the only mode in which the AI SENSE signal from the I/O connector is used as an input. In all other modes, AI SENSE is either programmed to be unused or driven with the board analog input ground.

Considerations for using the NRSE input configuration are discussed in the *Signal Connections* section later in this chapter. Figure 2-8 shows a schematic diagram of this configuration.

## **Input Polarity and Input Range**

The AT-MIO-16X has two polarities: unipolar input and bipolar input. Unipolar input means that the input voltage range is between 0 and  $V_{ref}$  where  $V_{ref}$  is a positive reference voltage. Bipolar input means that the input voltage range is between  $-V_{ref}$  and  $+V_{ref}$ . The AT-MIO-16X has a maximum unipolar input range of 10 V, and a maximum bipolar input range of 20 V ( $\pm$ 10 V). Polarity and range settings are programmed on a per channel basis through the configuration memory register.

## **Considerations for Selecting Input Ranges**

Input polarity and range selection depend on the expected input range of the incoming signal. A large input range can accommodate a large signal variation but lowers the voltage resolution. Choosing a smaller input range increases the voltage resolution but may result in the input signal going out of range. For best results, the input range should be matched as closely as possible to the expected range of the input signal. For example, if the input signal is certain not to be negative (below 0 V), a unipolar input is best. However, if the signal is ever negative, inaccurate readings will occur if unipolar input polarity is used.

The software-programmable gain on the AT-MIO-16X increases its overall flexibility by matching the input signal ranges to those that the AT-MIO-16X analog-to-digital converter (ADC) can accommodate. The AT-MIO-16X board has gains of 1, 2, 5, 10, 20, 50, and 100 and is suited for a wide variety of signal levels. With the proper gain setting, the full resolution of the ADC can be used to measure the input signal. Table 2-4 shows the overall input range and precision according to the input range configuration and gain used.

Range Gain Actual Precision\* **Input Range** Configuration 0 to +10 V1.0  $152.59 \mu V$ 0 to +10.0 V2.0 0 to +5.0 V $76.29 \, \mu V$  $30.52 \,\mu V$ 5.0 0 to +2.0 V10.0 0 to +1.0 V15.26 uV 20.0 0 to +0.5 V $7.63 \, \mu V$ 50.0 0 to +0.2 V $3.05 \,\mu\text{V}$ 100.0 0 to 100.0 mV  $1.53 \,\mu\text{V}$ -10 to +10 V1.0 -10.0 to +10.0 V 305.18 uV 2.0 -5.0 to +5.0 V 152.59 uV 5.0 -2.0 to +2.0 V  $61.04 \, \mu V$ 10.0 -1.0 to +1.0 V  $30.52 \, \mu V$ -0.5 to +0.5 V 20.0 15.26 uV 50.0 -0.2 to +0.2 V  $6.10 \,\mu\text{V}$ 100.0 -100.0 to +100.0 mV  $3.05 \,\mu\text{V}$

**Table 2-4.** Actual Range and Measurement Precision Versus Input Range Selection and Gain

**Note:** See Appendix A, *Specifications*, for absolute maximum ratings.

## **Analog Output Configuration**

The AT-MIO-16X supplies two channels of analog output voltage at the I/O connector. The analog output circuitry is configurable through programming of a register in the board register set. The reference and range for the analog output circuitry can be selected through software. The reference can be either internal or external, whereas the range can be either bipolar or unipolar.

#### **Analog Output Reference Selection**

Each DAC can be connected to the AT-MIO-16X internal reference of 10 V or to the external reference signal connected to the EXTREF pin on the I/O connector. This signal applied to EXTREF must be between -18 and +18 V. Both channels need not be configured for the same mode.

<sup>\*</sup> The value of 1 LSB of the 16-bit ADC; that is, the voltage increment corresponding to a change of 1 count in the ADC 16-bit count.

## **Analog Output Polarity Selection**

Each analog output channel can be configured for either unipolar or bipolar output. A unipolar configuration has a range of 0 to  $V_{ref}$  at the analog output. A bipolar configuration has a range of  $-V_{ref}$  to  $+V_{ref}$  at the analog output.  $V_{ref}$  is the voltage reference used by the DACs in the analog output circuitry and can be either the 10-V onboard reference or an externally supplied reference between -18 and +18 V. Both channels need not be configured for the same range.

Selecting a bipolar range for a particular DAC means that any data written to that DAC will be interpreted as two's complement format. In two's complement mode, data values written to the analog output channel range from –32,768 to +32,767 decimal (8000 to 7FFF hex). If unipolar range is selected, data is interpreted in straight binary format. In straight binary mode, data values written to the analog output channel range from 0 to 65,535 decimal (0 to FFFF hex).

## **Digital I/O Configuration**

The AT-MIO-16X contains eight lines of digital I/O for general-purpose use. The eight digital I/O lines supplied are configured as two 4-bit ports. Each port can be individually configured through programming of a register in the board register set as either input or output. At system startup and reset, the digital I/O ports are both configured for input.

## **Board and RTSI Clock Configuration**

When multiple AT Series boards are connected via the RTSI bus, you may want all of the boards to use the same 10-MHz clock. This arrangement is useful for applications that require counter/timer synchronization between boards. Each AT Series board with a RTSI bus interface has an onboard 10-MHz oscillator. Thus, one board can drive the RTSI bus clock signal, and the other boards can receive this signal or disconnect from it.

Many functions performed by the AT-MIO-16X board require a frequency timebase to generate the necessary timing signals for controlling ADC conversions, DAC updates, or general-purpose signals at the I/O connector. You select this timebase through programming one of the registers in the AT-MIO-16X register set.

The AT-MIO-16X can use either its internal 10-MHz timebase, or it can use a timebase received over the RTSI bus. In addition, if the board is configured to use the internal timebase, it can also be programmed to drive its internal timebase over the RTSI bus to another board that is programmed to receive this timebase signal. This clock source, whether local or from the RTSI bus, is then divided by 10 and used as the Am9513A frequency source. The default configuration at startup is to use the internal timebase without driving the RTSI bus timebase signal.

## **Hardware Installation**

You can install the AT-MIO-16X in any available 16-bit expansion slot in your AT Series computer. However, to achieve best noise performance, you should leave as much room as possible between the AT-MIO-16X and other boards and hardware. The AT-MIO-16X *does not* work if installed in an 8-bit expansion slot (PC Series). After you have made any necessary changes, verified, and recorded the switches and jumper settings (a form is included for this purpose in Appendix D, *Customer Communication*), you are ready to install the AT-MIO-16X. The following are general installation instructions, but consult your PC user manual or technical reference manual for specific instructions and warnings.

- 1. Turn off your computer.

- 2. Remove the top cover or access port to the I/O channel.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Insert the AT-MIO-16X into a 16-bit slot. Do not force the board into place. Verify that there are no extended components on the circuit board of the computer that may touch or be in the way of any part of the AT-MIO-16X.

- 5. Attach a RTSI cable to the RTSI connectors to connect AT Series boards to each other.

- 6. Screw the AT-MIO-16X mounting bracket to the back panel rail of the computer.

- 7. Check the installation.

- 8. Replace the cover.

The AT-MIO-16X board is installed and ready for operation.

## **Signal Connections**

This section describes input and output signal connections to the AT-MIO-16X board via the AT-MIO-16X I/O connector. This section also includes specifications and connection instructions for the signals given on the AT-MIO-16X I/O connector.

Caution:

Connections that exceed any of the maximum ratings of input or output signals on the AT-MIO-16X can result in damage to the AT-MIO-16X board and to the PC. Maximum input ratings for each signal are given in this chapter under the discussion of that signal. National Instruments is not liable for any damages resulting from such signal connections.

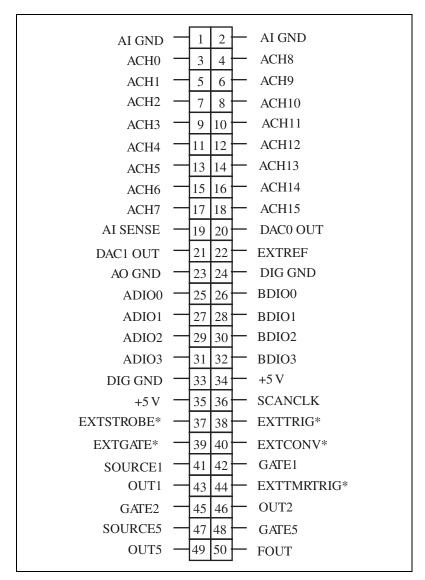

Figure 2-4 shows the pin assignments for the AT-MIO-16X 50-pin I/O connector.

Figure 2-4. AT-MIO-16X 50-Pin I/O Connector

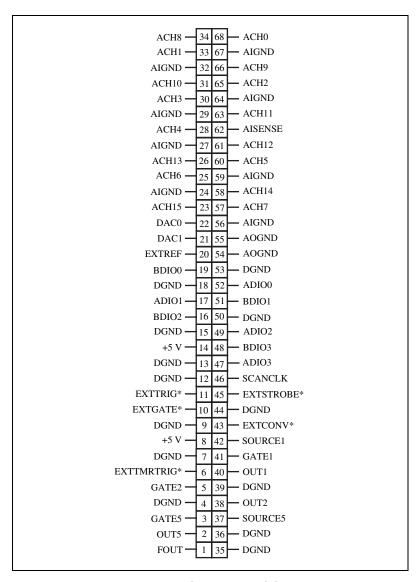

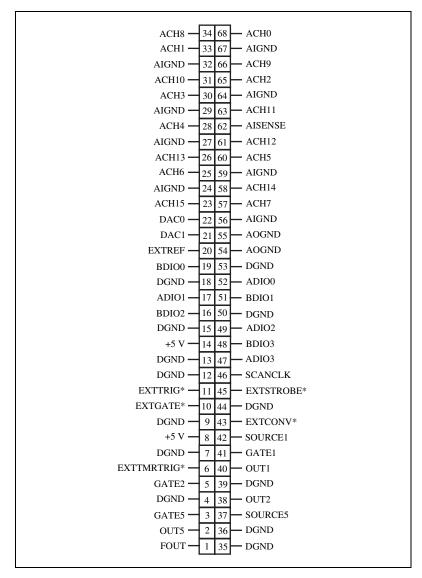

Figure 2-5 shows the pin assignments for the AT-MIO-16X 68-pin I/O connector.

Figure 2-5. AT-MIO-16X 68-Pin I/O Connector

## **Signal Connection Descriptions**

| Signal Names | Reference | Descriptions                                                                                                                                                                                                                      |

|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI GND       | N/A       | Analog Input Ground—These pins are the reference point for single-ended measurements and the bias current return point for differential measurements.                                                                             |

| ACH<015>     | AI GND    | Analog Input Channels 0 through 15—In differential mode, the input is configured for up to eight channels. In single-ended mode, the input is configured for up to 16 channels.                                                   |

| AI SENSE     | AI GND    | Analog Input Sense—This pin serves as the reference node when the board is in NRSE configuration. If desired, this signal can be programmed to be driven by the board analog input ground in the DIFF and RSE analog input modes. |

| DAC0 OUT     | AO GND    | Analog Channel 0 Output—This pin supplies the voltage output of analog output Channel 0.                                                                                                                                          |

| DAC1 OUT     | AO GND    | Analog Channel 1 Output—This pin supplies the voltage output of analog output Channel 1.                                                                                                                                          |

| EXTREF       | AO GND    | External Reference—This is the external reference input for the analog output circuitry.                                                                                                                                          |

| AO GND       | N/A       | Analog Output Ground—The analog output voltages are referenced to this node.                                                                                                                                                      |

| DIG GND      | N/A       | Digital Ground—This pin supplies the reference for the digital signals at the I/O connector as well as the +5 VDC supply.                                                                                                         |

| ADIO<03>     | DIG GND   | Digital I/O port A signals.                                                                                                                                                                                                       |

| BDIO<03>     | DIG GND   | Digital I/O port B signals.                                                                                                                                                                                                       |

| +5 V         | DIG GND   | +5 VDC Source—These pins are fused for up to 1 A of +5 V supply.                                                                                                                                                                  |

| Signal Names | Reference | Descriptions                                                                                                                                                                                                                                                                                 |  |

|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SCANCLK      | DIG GND   | Scan Clock—This pin pulses once for each A/D conversion in the scanning modes. The low-to-high edge indicates when the input signal can be removed from the input or switched to another signal.                                                                                             |  |