#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

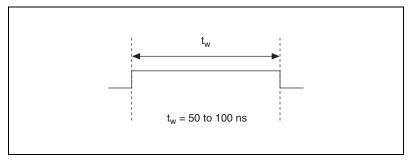

#### SELL YOUR SURPLUS

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs. We Sell For Cash We Get Credit We Receive a Trade-In Deal

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE CA-1000

# **DAQ E Series**

**E Series User Manual**

#### Worldwide Technical Support and Product Information

ni.com

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 787593504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 1800 300 800, Austria 43 662 457990-0, Belgium 32 (0) 2 757 0020, Brazil 55 11 3262 3599, Canada 800 433 3488, China 86 21 5050 9800, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 385 (0) 9 725 72511, France 33 (0) 1 48 14 24 24, Germany 49 89 7413130, India 91 80 41190000, Israel 972 3 6393737, Italy 39 02 413091, Japan 81 3 5472 2970, Korea 82 02 3451 3400, Lebanon 961 (0) 1 33 28 28, Malaysia 1800 887710, Mexico 01 800 010 0793, Netherlands 31 (0) 348 433 466, New Zealand 0800 553 322, Norway 47 (0) 66 90 76 60, Poland 48 22 3390150, Portugal 351 210 311 210, Russia 7 495 783 6851, Singapore 1800 226 5886, Slovenia 386 3 425 42 00, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 (0) 8 587 895 00, Switzerland 41 56 2005151, Taiwan 886 02 2377 2222, Thailand 662 278 6777, Turkey 90 212 279 3031, United Kingdom 44 (0) 1635 523545

For further support information, refer to the *Technical Support and Professional Services* appendix. To comment on National Instruments documentation, refer to the National Instruments Web site at ni.com/info and enter the info code feedback.

© 1997–2007 National Instruments Corporation. All rights reserved.

#### Warranty

The E Series devices are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### Trademarks

National Instruments, NI, ni.com, and LabVIEW are trademarks of National Instruments Corporation. Refer to the *Terms of Use* section on ni.com/legal for more information about National Instruments trademarks.

FireWire<sup>®</sup> is the registered trademark of Apple Computer, Inc. Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents

For patents covering National Instruments products, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your CD, or ni.com/patents.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

# Compliance

# Compliance with FCC/Canada Radio Frequency Interference Regulations

#### **Determining FCC Class**

The Federal Communications Commission (FCC) has rules to protect wireless communications from interference. The FCC places digital electronics into two classes. These classes are known as Class A (for use in industrial commercial locations only) or Class B (for use in residential or commercial locations). All National Instruments (NI) products are FCC Class A products.

Depending on where it is operated, this Class A product could be subject to restrictions in the FCC rules. (In Canada, the Department of Communications (DOC), of Industry Canada, regulates wireless interference in much the same way.) Digital electronics emit weak signals during normal operation that can affect radio, television, or other wireless products.

All Class A products display a simple warning statement of one paragraph in length regarding interference and undesired operation. The FCC rules have restrictions regarding the locations where FCC Class A products can be operated.

Consult the FCC Web site at www.fcc.gov for more information.

#### FCC/DOC Warnings

This equipment generates and uses radio frequency energy and, if not installed and used in strict accordance with the instructions in this manual and the CE marking Declaration of Conformity\*, may cause interference to radio and television reception. Classification requirements are the same for the Federal Communications Commission (FCC) and the Canadian Department of Communications (DOC).

Changes or modifications not expressly approved by NI could void the user's authority to operate the equipment under the FCC Rules.

#### Class A

#### Federal Communications Commission

This equipment has been tested and found to comply with the limits for a Class A digital device, pursuant to part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the instruction manual, may cause harmful interference to radio communications. Operation of this equipment in a residential area is likely to cause harmful interference in which case the user is required to correct the interference at their own expense.

#### **Canadian Department of Communications**

This Class A digital apparatus meets all requirements of the Canadian InterferenceCausing Equipment Regulations.

Cet appareil numérique de la classe A respecte toutes les exigences du Règlement sur le matériel brouilleur du Canada.

#### **Compliance with EU Directives**

Users in the European Union (EU) should refer to the Declaration of Conformity (DoC) for information\* pertaining to the CE marking. Refer to the Declaration of Conformity (DoC) for this product for any additional regulatory compliance information. To obtain the DoC for this product, visit ni.com/certification, search by model number or product line, and click the appropriate link in the Certification column.

\* The CE marking Declaration of Conformity contains important supplementary information and instructions for the user or installer.

#### **About This Manual**

| Conventions                                    | XV    |

|------------------------------------------------|-------|

| Related Documentation                          | xvi   |

| NI-DAQ for Windows                             | xvi   |

| NI-DAQmx for Linux                             | xvi   |

| NI-DAQmx Base                                  | xvii  |

| LabVIEW                                        | xvii  |

| LabWindows/CVI                                 | xviii |

| Measurement Studio                             | xviii |

| ANSI C without NI Application Software         | xix   |

| .NET Languages without NI Application Software | xix   |

| Device Documentation and Specifications        | XX    |

| Training Courses                               | XX    |

| Technical Support on the Web                   | xx    |

## Chapter 1 DAQ System Overview

| DAQ Hardware                      | 1-2  |

|-----------------------------------|------|

| DAQ-STC                           |      |

| Calibration Circuitry             | 1-3  |

| Internal or Self-Calibration      | 1-4  |

| External Calibration              | 1-4  |

| Signal Conditioning               | 1-4  |

| Sensors and Transducers           | 1-4  |

| Signal Conditioning Options       | 1-5  |

| SCXI                              | 1-5  |

| SCC                               | 1-6  |

| 5B Series                         | 1-6  |

| Cables and Accessories            | 1-6  |

| Using Accessories with Devices    | 1-7  |

| Custom Cabling                    | 1-9  |

| Programming Devices in Software   | 1-10 |

| I/O Connector Signal Descriptions | 1-11 |

| Terminal Name Equivalents         | 1-14 |

| +5 V Power Source                 |      |

## Chapter 2 Analog Input

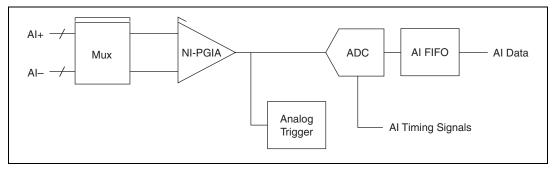

| Analog Input Circuitry                              | 2-1  |

|-----------------------------------------------------|------|

| Mux                                                 |      |

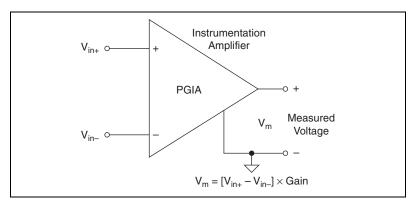

| Instrumentation Amplifier (NI-PGIA)                 | 2-2  |

| A/D Converter                                       |      |

| AI FIFO                                             | 2-2  |

| Analog Trigger                                      | 2-2  |

| AI Timing Signals                                   | 2-2  |

| Input Polarity and Range                            | 2-2  |

| Analog Input Terminal Configuration                 | 2-5  |

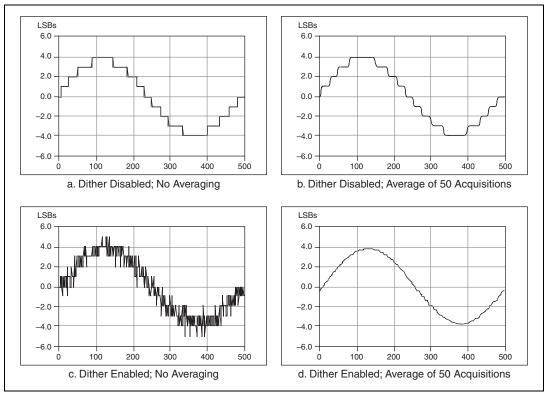

| Dither                                              | 2-8  |

| Multichannel Scanning Considerations                | 2-9  |

| Use Low Impedance Sources                           | 2-10 |

| Use Short High-Quality Cabling                      |      |

| Carefully Choose the Channel Scanning Order         |      |

| Avoid Switching from a Large to a Small Input Range | 2-11 |

| Insert Grounded Channel between Signal Channels     |      |

| Minimize Voltage Step between Adjacent Channels     |      |

| Avoid Scanning Faster than Necessary                |      |

| Example 1                                           |      |

| Example 2                                           | 2-13 |

| AI Data Acquisition Methods                         | 2-13 |

| Software-Timed Acquisitions                         |      |

| Hardware-Timed Acquisitions                         |      |

| Analog Input Triggering                             | 2-14 |

| AI Start Trigger Signal                             | 2-15 |

| Using a Digital Source                              | 2-15 |

| Using an Analog Source                              | 2-15 |

| Outputting the AI Start Trigger Signal              | 2-16 |

| AI Reference Trigger Signal                         |      |

| Using a Digital Source                              | 2-18 |

| Using an Analog Source                              | 2-18 |

| Outputting the AI Reference Trigger Signal          | 2-18 |

| AI Pause Trigger Signal                             |      |

| Using a Digital Source                              |      |

| Using an Analog Source                              | 2-19 |

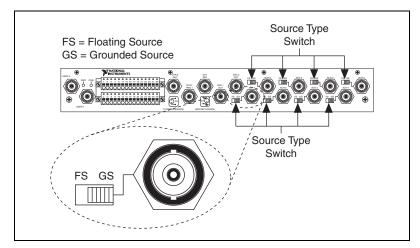

| Connecting Analog Input Signals                     |      |

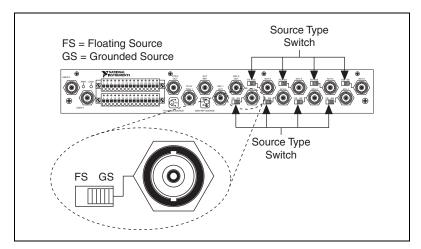

| Types of Signal Sources                             |      |

| Floating Signal Sources                             |      |

| Ground-Referenced Signal Sources                    |      |

|                                                     |      |

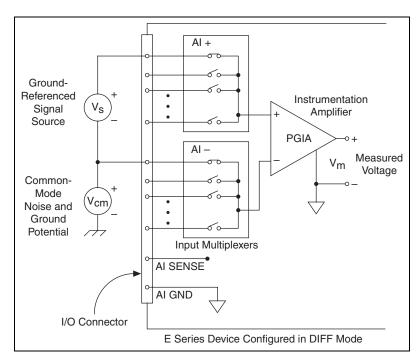

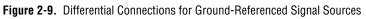

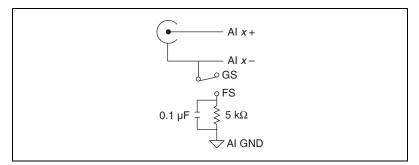

| Differential Connection Considerations                        | 2-22 |

|---------------------------------------------------------------|------|

| Differential Connections for Ground-Referenced Signal Sources | 2-23 |

| Common-Mode Signal Rejection Considerations                   | 2-24 |

| Differential Connections for Non-Referenced or                |      |

| Floating Signal Sources                                       | 2-24 |

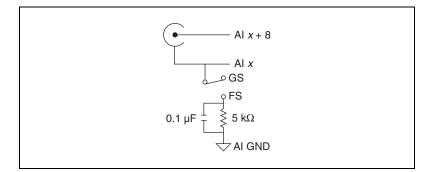

| Single-Ended Connection Considerations                        | 2-26 |

| Common-Mode Signal Rejection Considerations                   | 2-26 |

| Single-Ended Connections for Floating Signal Sources          |      |

| (RSE Configuration)                                           | 2-27 |

| Single-Ended Connections for Grounded Signal Sources          |      |

| (NRSE Configuration)                                          |      |

| Field Wiring Considerations                                   |      |

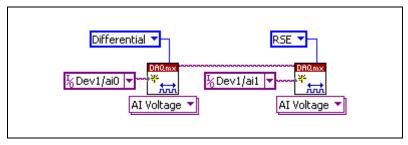

| Configuring AI Modes in Software                              |      |

| Traditional NI-DAQ (Legacy)                                   | 2-29 |

| NI-DAQmx                                                      | 2-29 |

| Analog Input Timing Signals                                   | 2-30 |

| AI Start Trigger Signal                                       | 2-32 |

| Using a Digital Source                                        | 2-33 |

| Using an Analog Source                                        | 2-33 |

| Outputting the AI Start Trigger Signal                        | 2-33 |

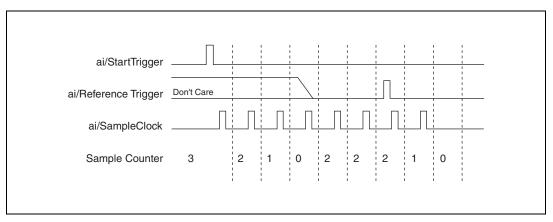

| AI Reference Trigger Signal                                   | 2-34 |

| Using a Digital Source                                        | 2-35 |

| Using an Analog Source                                        | 2-36 |

| Outputting the AI Reference Trigger Signal                    | 2-36 |

| AI Pause Trigger Signal                                       | 2-36 |

| Using a Digital Source                                        | 2-36 |

| Using an Analog Source                                        | 2-37 |

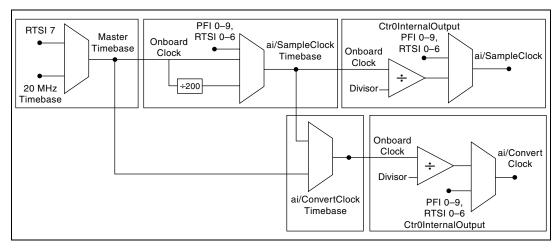

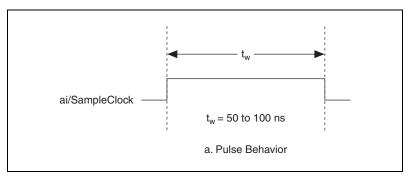

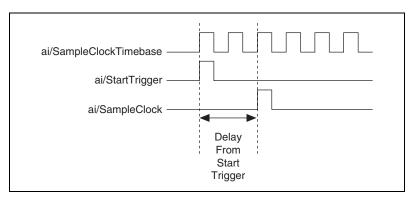

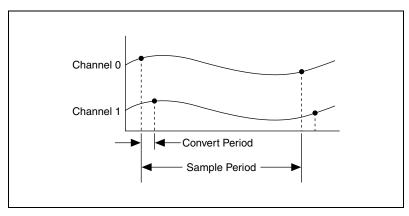

| AI Sample Clock Signal                                        | 2-37 |

| Using an Internal Source                                      | 2-37 |

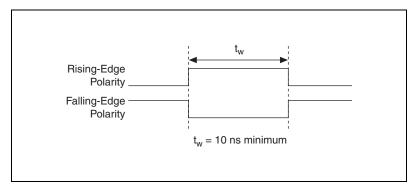

| Using an External Source                                      | 2-37 |

| Outputting the AI Sample Clock Signal                         | 2-38 |

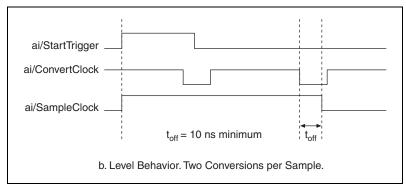

| Other Timing Requirements                                     | 2-39 |

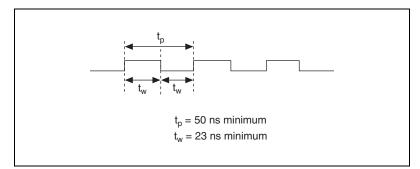

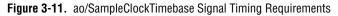

| AI Sample Clock Timebase Signal                               | 2-40 |

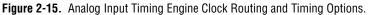

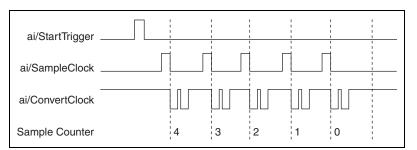

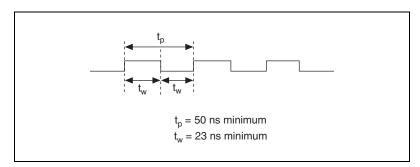

| AI Convert Clock Signal                                       | 2-41 |

| Using an Internal Source                                      | 2-41 |

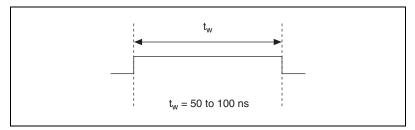

| Using an External Source                                      | 2-42 |

| Outputting the AI Convert Clock Signal                        |      |

| Using a Delay from Sample Clock to Convert Clock              | 2-43 |

| Other Timing Requirements                                     | 2-43 |

| AI Convert Clock Timebase Signal                              | 2-45 |

| Master Timebase Signal                                        |      |

| AI Hold Complete Event Signal                                 |      |

| External Strobe Signal                                        |      |

| Getting Started with AI Applications in Software              | 2-47 |

## Chapter 3 Analog Output

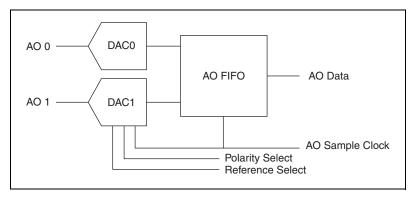

| Analog Output Circuitry                          | 3-1  |

|--------------------------------------------------|------|

| DACs                                             | 3-1  |

| DAC FIFO                                         | 3-1  |

| AO Sample Clock                                  | 3-2  |

| Polarity and Reference Selection                 | 3-2  |

| Reference Selection                              | 3-2  |

| Polarity Selection                               | 3-3  |

| Reglitch Selection                               | 3-3  |

| Minimizing Glitches on the Output Signal         | 3-3  |

| AO Data Generation Methods                       |      |

| Software-Timed Generations                       | 3-4  |

| Hardware-Timed Generations                       | 3-4  |

| Buffered                                         | 3-4  |

| Non-Buffered                                     | 3-5  |

| Analog Output Triggering                         | 3-5  |

| AO Start Trigger Signal                          | 3-6  |

| Using a Digital Source                           | 3-6  |

| Using an Analog Source                           |      |

| Outputting the AO Start Trigger Signal           | 3-6  |

| AO Pause Trigger Signal                          |      |

| Using a Digital Source                           |      |

| Using an Analog Source                           |      |

| Connecting Analog Output Signals                 |      |

| Waveform Generation Timing Signals               |      |

| AO Start Trigger Signal                          |      |

| Using a Digital Source                           |      |

| Using an Analog Source                           |      |

| Outputting the AO Start Trigger Signal           |      |

| AO Pause Trigger Signal                          |      |

| Using a Digital Source                           |      |

| Using an Analog Source                           |      |

| AO Sample Clock Signal                           |      |

| Using an Internal Source                         |      |

| Using an External Source                         |      |

| Outputting the AO Sample Clock Signal            |      |

| Other Timing Requirements                        |      |

| AO Sample Clock Timebase Signal                  |      |

| Master Timebase Signal                           |      |

| Getting Started with AO Applications in Software | 3-15 |

## Chapter 4 Digital I/O

| Extended Digital I/O                              | 4-2  |

|---------------------------------------------------|------|

| Port 3 Signal Assignments                         |      |

| Power-On State                                    | 4-3  |

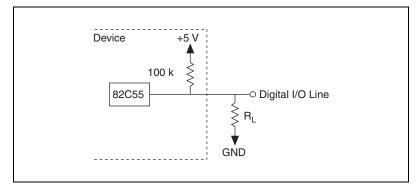

| Changing DIO Power-On State to Pulled Low         | 4-3  |

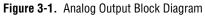

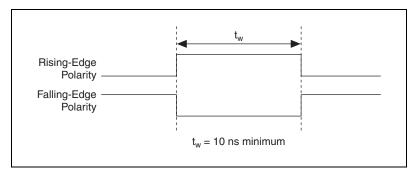

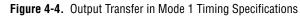

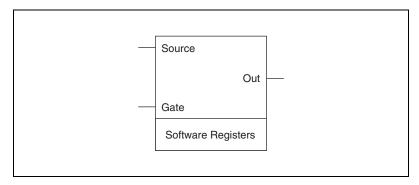

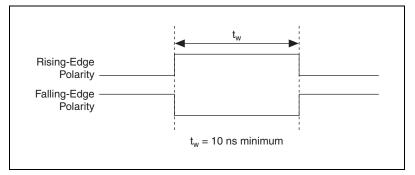

| Timing Specifications                             | 4-4  |

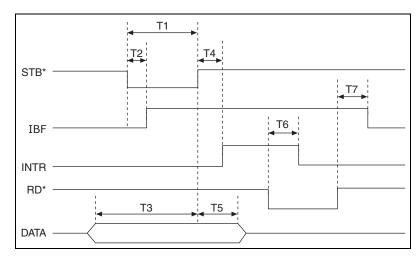

| Mode 1 Input Timing                               | 4-6  |

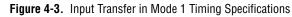

| Mode 1 Output Timing                              | 4-7  |

| Mode 2 Bidirectional Timing                       | 4-8  |

| Power-On States of the PFI and DIO Lines          | 4-9  |

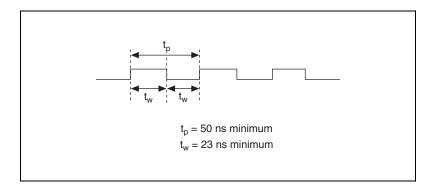

| Connecting Digital I/O Signals                    | 4-9  |

| Getting Started with DIO Applications in Software | 4-10 |

#### Chapter 5 Counters

| Counter Triggering                                    |     |

|-------------------------------------------------------|-----|

| Start Trigger                                         | 5-1 |

| Pause Trigger                                         | 5-2 |

| Counter Timing Signals                                | 5-2 |

| Counter 0 Source Signal                               | 5-3 |

| Counter 0 Gate Signal                                 | 5-4 |

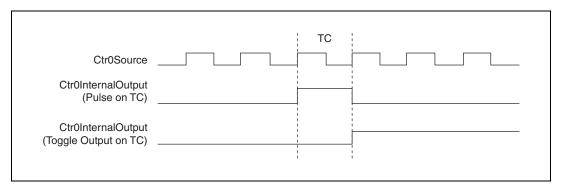

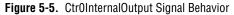

| Counter 0 Internal Output Signal                      | 5-5 |

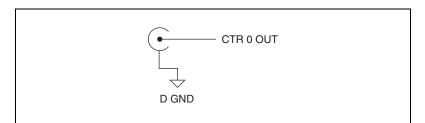

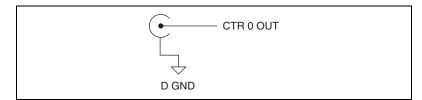

| CTR 0 OUT Pin                                         | 5-6 |

| Counter 0 Up/Down Signal                              | 5-6 |

| Counter 1 Source Signal                               | 5-6 |

| Counter 1 Gate Signal                                 | 5-7 |

| Counter 1 Internal Output Signal                      | 5-8 |

| Counter 1 Up/Down Signal                              | 5-9 |

| Frequency Output Signal                               | 5-9 |

| Master Timebase Signal                                | 5-9 |

| Getting Started with Counter Applications in Software |     |

|                                                       |     |

## Chapter 6 Programmable Function Interfaces (PFI)

| Inputs  | 6-1 |

|---------|-----|

| Outputs | 6-1 |

### Chapter 7 Digital Routing

| Timing Signal Routing       |  |

|-----------------------------|--|

| Connecting Timing Signals   |  |

| Routing Signals in Software |  |

## Chapter 8 Real-Time System Integration Bus (RTSI)

| -1 |

|----|

| -1 |

| -2 |

| -4 |

| -4 |

|    |

#### Chapter 9 Bus Interface

| MITE and DAQPnP                                    |  |

|----------------------------------------------------|--|

| Using PXI with CompactPCI                          |  |

| Data Transfer Methods                              |  |

| Direct Memory Access (DMA)                         |  |

| Interrupt Request (IRQ)                            |  |

| Programmed I/O                                     |  |

| Changing Data Transfer Methods between DMA and IRQ |  |

## Chapter 10 Triggering

| Triggering with a Digital Source |  |

|----------------------------------|--|

| Triggering with an Analog Source |  |

| PFI 0/AI START TRIG Pin          |  |

| Analog Input Channel             |  |

| Analog Trigger Actions           |  |

| Analog Trigger Types             |  |

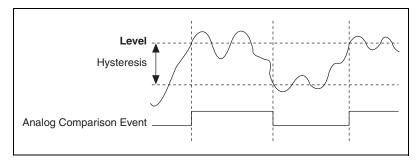

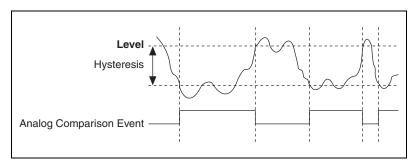

| Level Triggering                 |  |

| Level Triggering with Hysteresis |  |

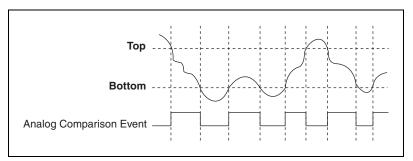

| Window Triggering                |  |

| Analog Trigger Accuracy          |  |

| 66 6                             |  |

### Appendix A Device-Specific Information

Appendix B I/O Connector Pinouts

Appendix C Troubleshooting

Appendix D Technical Support and Professional Services

Glossary

Index

The *E Series User Manual* contains information about using the National Instruments E Series and several B Series data acquisition (DAQ) devices with NI-DAQ 8.0 or later. E Series devices feature up to 64 analog input (AI) channels, two counters, eight or 32 lines of digital input/output (DIO), and up to two analog output (AO) channels. The B Series devices discussed in this document are similar to E Series devices, but do not support SCXI, RTSI, or referenced single-ended AI mode.

## Conventions

|           | The following conventions are used in this manual:                                                                                                                                                                                                                                                    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <>        | Angle brackets indicate function keys. Angle brackets that contain numbers separated by an ellipsis represent a range of values associated with a bit or signal name—for example, P0.<30>.                                                                                                            |

| »         | The » symbol leads you through nested menu items and dialog box options to a final action. The sequence <b>File</b> » <b>Page Setup</b> » <b>Options</b> directs you to pull down the <b>File</b> menu, select the <b>Page Setup</b> item, and select <b>Options</b> from the last dialog box.        |

|           | This icon denotes a note, which alerts you to important information.                                                                                                                                                                                                                                  |

|           | This icon denotes a caution, which advises you of precautions to take to avoid injury, data loss, or a system crash. When this symbol is marked on the product, refer to the <i>Read Me First: Safety and Radio-Frequency Interference</i> document shipped with the product for precautions to take. |

| bold      | Bold text denotes items that you must select or click in the software, such<br>as menu items and dialog box options. Bold text also denotes parameter<br>names.                                                                                                                                       |

| italic    | Italic text denotes variables, emphasis, a cross-reference, or an introduction<br>to a key concept. Italic text also denotes text that is a placeholder for a word<br>or value that you must supply.                                                                                                  |

| monospace | Text in this font denotes text or characters you should enter from the keyboard, the proper names of disk drives, paths, directories, programs, functions filenames and extensions                                                                                                                    |

| monospace italic | Italic text in this font denotes text that is a placeholder for a word or value that you must supply.                 |

|------------------|-----------------------------------------------------------------------------------------------------------------------|

| Platform         | Text in this font denotes a specific platform and indicates that the text following it applies only to that platform. |

## **Related Documentation**

Each application software package and driver includes information about writing applications for taking measurements and controlling measurement devices. The following references to documents assume you have NI-DAQ 8.0 or later, and where applicable, version 7.0 or later of the NI application software.

#### **NI-DAQ** for Windows

The DAQ Getting Started Guide describes how to install your NI-DAQmx for Windows software, how to install your NI-DAQmx-supported DAQ device, and how to confirm that your device is operating properly. Select Start>All Programs>National Instruments>NI-DAQ>DAQ Getting Started Guide.

The *NI-DAQ Readme* lists which devices are supported by this version of NI-DAQ. Select **Start**»**All Programs**»**National Instruments**»**NI-DAQ**» **NI-DAQ Readme**.

The *NI-DAQmx Help* contains general information about measurement concepts, key NI-DAQmx concepts, and common applications that are applicable to all programming environments. Select **Start**»**All Programs**» **National Instruments**»**NI-DAQ**»**NI-DAQmx Help**.

The *Traditional NI-DAQ (Legacy) User Manual* contains an API overview and general information about measurement concepts. Select **Start**»All **Programs**»National Instruments»NI-DAQ»Traditional NI-DAQ (Legacy) User Manual.

#### **NI-DAQmx** for Linux

The *DAQ Getting Started Guide* describes how to install your NI-DAQmx-supported DAQ device and confirm that your device is operating properly.

The *NI-DAQ Readme for Linux* lists supported devices and includes software installation instructions, frequently asked questions, and known issues.

The C Function Reference Help describes functions and attributes.

The *NI-DAQmx for Linux Configuration Guide* provides configuration instructions, templates, and instructions for using test panels.

**Note** All NI-DAQmx documentation for Linux is installed at /usr/local/natinst/ NI-DAQmx/docs.

#### **NI-DAQmx Base**

The *NI-DAQmx Base Getting Started Guide* describes how to install your NI-DAQmx Base software, your NI-DAQmx Base-supported DAQ device, and how to confirm that your device is operating properly. Select **Start**»All **Programs**»National Instruments»NI-DAQmx Base»Documentation» Getting Started Guide.

The *NI-DAQmx Base Readme* lists which devices are supported by this version of NI-DAQmx Base. Select **Start**»All **Programs**»National **Instruments**»NI-DAQmx Base»DAQmx Base Readme.

The *NI-DAQmx Base VI Reference Help* contains VI reference and general information about measurement concepts. In LabVIEW, select **Help**» **NI-DAQmx Base VI Reference Help**.

The *NI-DAQmx Base C Reference Help* contains C reference and general information about measurement concepts. Select **Start**»**All Programs**» **National Instruments**»**NI-DAQmx Base**»**Documentation**»**C Function Reference Help**.

#### LabVIEW

If you are a new user, use the *Getting Started with LabVIEW* manual to familiarize yourself with the LabVIEW graphical programming environment and the basic LabVIEW features you use to build data acquisition and instrument control applications. Open the *Getting Started with LabVIEW* manual by selecting **Start-All Programs-National Instruments-LabVIEW-LabVIEW Manuals** or by navigating to the labview\manuals directory and opening LV\_Getting\_Started.pdf.

Use the *LabVIEW Help*, available by selecting **Help**»**Search the LabVIEW Help** in LabVIEW, to access information about LabVIEW programming concepts, step-by-step instructions for using LabVIEW, and reference information about LabVIEW VIs, functions, palettes, menus, and tools. Refer to the following locations on the **Contents** tab of the *LabVIEW Help* for information about NI-DAQmx:

- Getting Started »Getting Started with DAQ—Includes overview information and a tutorial to learn how to take an NI-DAQmx measurement in LabVIEW using the DAQ Assistant.

- VI and Function Reference»Measurement I/O VIs and Functions—Describes the LabVIEW NI-DAQmx VIs and properties.

- **Taking Measurements**—Contains the conceptual and how-to information you need to acquire and analyze measurement data in LabVIEW, including common measurements, measurement fundamentals, NI-DAQmx key concepts, and device considerations.

#### LabWindows/CVI

The **Data Acquisition** book of the *LabWindows/CVI Help* contains measurement concepts for NI-DAQmx. This book also contains *Taking an NI-DAQmx Measurement in LabWindows/CVI*, which includes step-by-step instructions about creating a measurement task using the DAQ Assistant. In LabWindows<sup>™</sup>/CVI<sup>™</sup>, select **HelpContents**, then select **Using LabWindows/CVI>Data Acquisition**.

The NI-DAQmx Library book of the *LabWindows/CVI Help* contains API overviews and function reference for NI-DAQmx. Select Library Reference»NI-DAQmx Library in the *LabWindows/CVI Help*.

#### **Measurement Studio**

If you program your NI-DAQmx-supported device in Measurement Studio using Visual C++, Visual C#, or Visual Basic .NET, you can interactively create channels and tasks by launching the DAQ Assistant from MAX or from within Visual Studio .NET. You can generate the configuration code based on your task or channel in Measurement Studio. Refer to the *DAQ Assistant Help* for additional information about generating code. You also can create channels and tasks, and write your own applications in your ADE using the NI-DAQmx API.

For help with NI-DAQmx methods and properties, refer to the NI-DAQmx .NET Class Library or the NI-DAQmx Visual C++ Class Library included in the *NI Measurement Studio Help*. For general help with programming in Measurement Studio, refer to the *NI Measurement Studio Help*, which is fully integrated with the Microsoft Visual Studio .NET help. To view

# this help file in Visual Studio. NET, select **Measurement Studio**» **NI Measurement Studio Help**.

To create an application in Visual C++, Visual C#, or Visual Basic .NET, follow these general steps:

- 1. In Visual Studio .NET, select **File**»**New**»**Project** to launch the New Project dialog box.

- 2. Find the Measurement Studio folder for the language you want to create a program in.

- 3. Choose a project type. You add DAQ tasks as a part of this step.

The *Measurement Studio Reference* contains the Traditional NI-DAQ (Legacy) API overview, measurement concepts, and function reference. In Visual Studio .NET, select **Measurement Studio**»Measurement Studio Reference.

#### **ANSI C without NI Application Software**

*The Traditional NI-DAQ (Legacy) User Manual* and the *NI-DAQmx Help* contain API overviews. The NI-DAQmx Help also contains general information about measurement concepts. Traditional NI-DAQ (Legacy) Function Reference Help and NI-DAQmx C Reference Help describe the C functions and attributes. Select **Start>All Programs>National Instruments>NI-DAQ** and the document title for the NI-DAQ API you are using.

#### .NET Languages without NI Application Software

With the Microsoft .NET Framework version 1.1 or later, you can use NI-DAQmx to create applications using Visual C# and Visual Basic .NET without Measurement Studio. You need Microsoft Visual Studio .NET 2003 or Microsoft Visual Studio 2005 for the API documentation to be installed.

The installed documentation contains the NI-DAQmx API overview, measurement tasks and concepts, and function reference. This help is fully integrated into the Visual Studio .NET documentation. To view the NI-DAQmx .NET documentation, go to **Start»Programs»National Instruments»NI-DAQ»NI-DAQmx .NET Reference Help**. Expand **NI Measurement Studio Help»NI Measurement Studio .NET Class Library»Reference** to view the function reference. Expand **NI Measurement Studio Help»NI Measurement Studio .NET Class Library»Using the Measurement Studio .NET Class** Libraries to view conceptual topics for using NI-DAQmx with Visual C# and Visual Basic .NET.

To get to the same help topics from within Visual Studio, go to **Help**» **Contents**. Select **Measurement Studio** from the **Filtered By** drop-down list and follow the previous instructions.

#### **Device Documentation and Specifications**

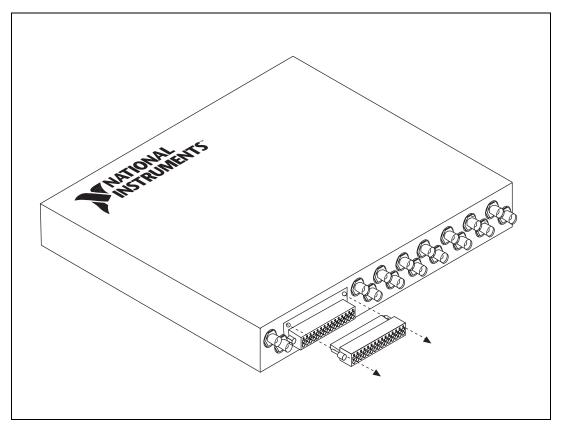

NI-DAQmx includes the Device Document Browser, which contains online documentation for supported DAQ and SCXI devices, such as documents describing device pinouts, features, and operation. You can find, view, and/or print the documents for each device using the Device Document Browser at any time by inserting the CD. After installing the Device Document Browser, device documents are accessible from **Start**» **All Programs**»**National Instruments**»**NI-DAQ**»**Browse Device Documentation**.

#### **Training Courses**

If you need more help getting started developing an application with NI products, NI offers training courses. To enroll in a course or obtain a detailed course outline, refer to ni.com/training.

#### **Technical Support on the Web**

For additional support, refer to ni.com/support or zone.ni.com.

Note You can download these documents at ni.com/manuals.

DAQ specifications and some DAQ manuals are available as PDFs. You must have Adobe Acrobat Reader with Search and Accessibility 5.0.5 or later installed to view the PDFs. Refer to the Adobe Systems Incorporated Web site at www.adobe.com to download Acrobat Reader. Refer to the National Instruments Product Manuals Library at ni.com/manuals for updated documentation resources.

# **DAQ System Overview**

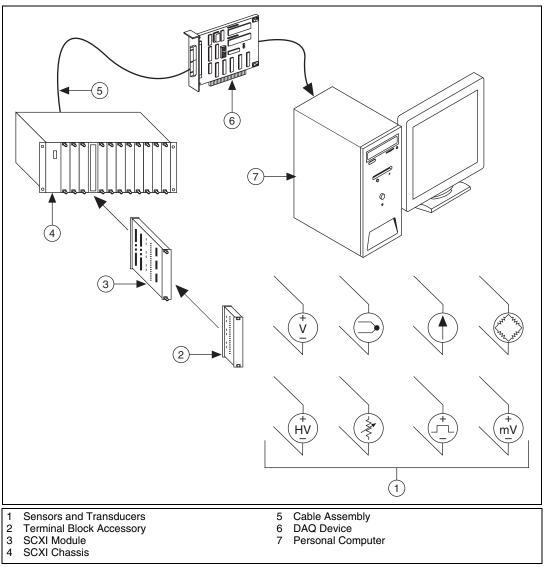

Figure 1-1 shows a typical DAQ system setup, which includes transducers, signal conditioning, cables that connect the various devices to the accessories, the E Series device, and the programming software. Refer to the *Using Accessories with Devices* section for a list of devices and their compatible accessories.

Figure 1-1. DAQ System Overview

# **DAQ** Hardware

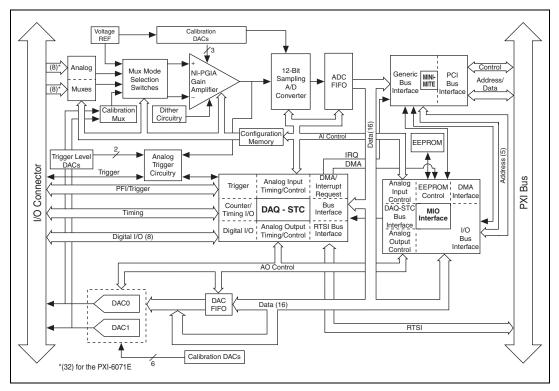

DAQ hardware digitizes signals, performs D/A conversions to generate analog output signals, and measures and controls digital I/O signals.

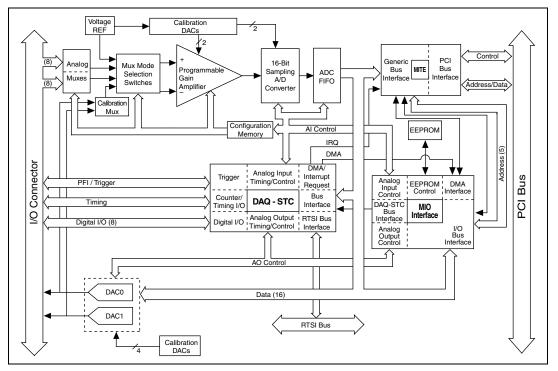

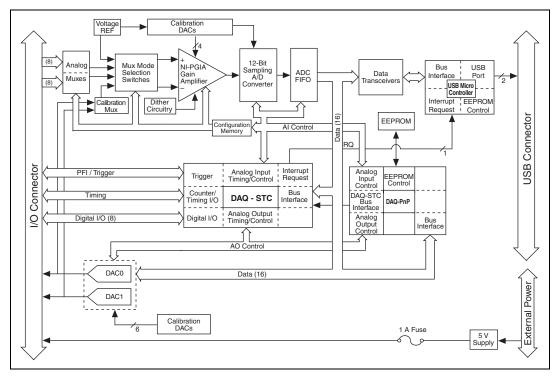

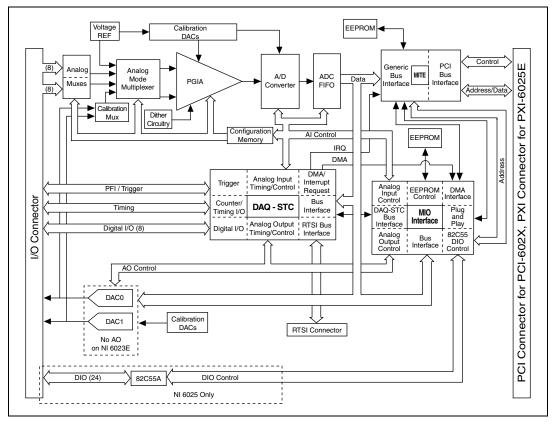

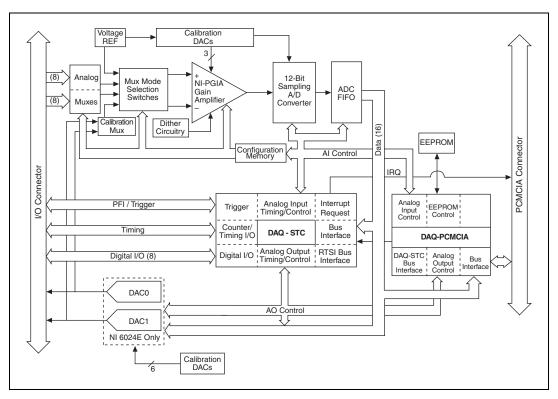

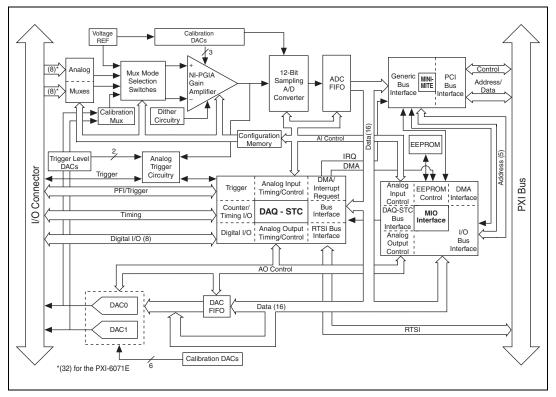

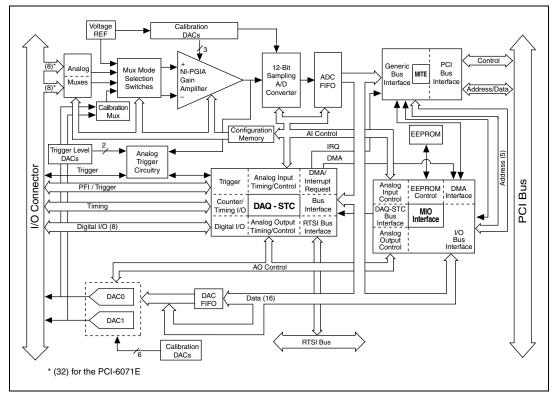

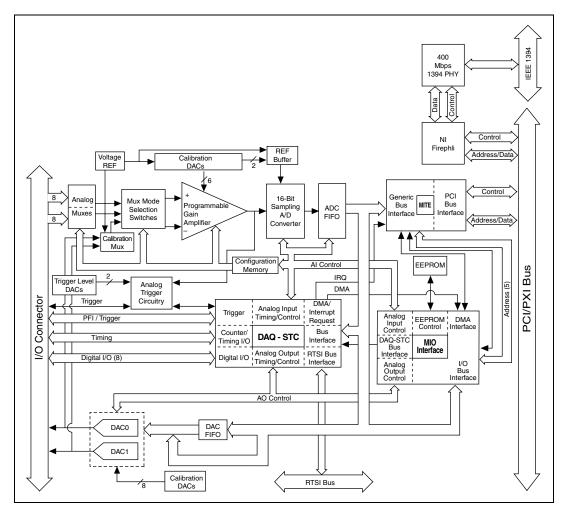

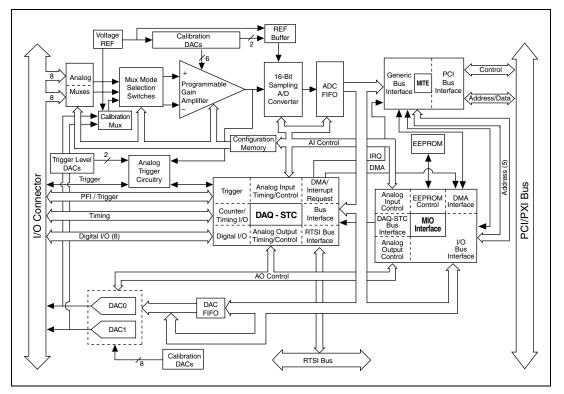

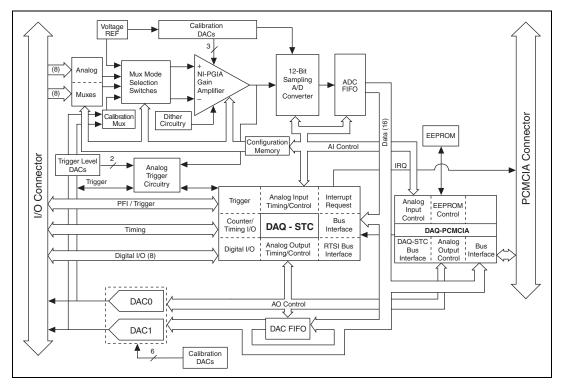

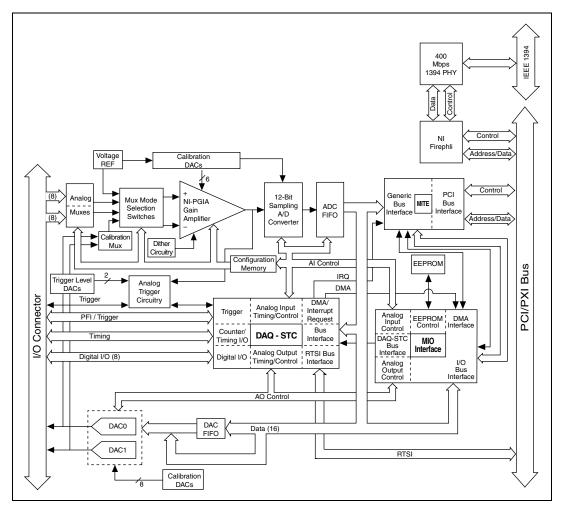

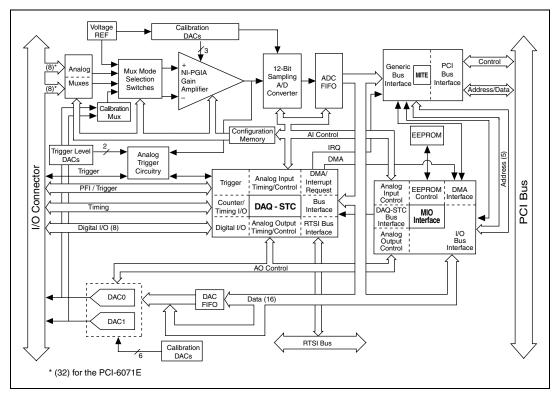

## DAQ-STC

E Series devices use the National Instruments DAQ system timing controller (DAQ-STC) for time-related functions. The DAQ-STC consists of the following timing groups.

- AI—Two 24-bit, two 16-bit counters

- AO—Three 24-bit, one 16-bit counter

- General-purpose counter/timer functions—Two 24-bit counters

You can independently configure the groups for timing resolutions of 50 ns or 10  $\mu$ s. With the DAQ-STC, you can interconnect a wide variety of internal timing signals to other internal blocks. The interconnection scheme is flexible and completely software-configurable.

The DAQ-STC offers PFI lines to import external timing and trigger signals or to export internally generated clocks and triggers. The DAQ-STC also supports buffered operations, such as buffered waveform acquisition, buffered waveform generation, and buffered period measurement. It also supports numerous non-buffered operations, such as single pulse or pulse train generation, digital input, and digital output.

#### **Calibration Circuitry**

Calibration is the process of making adjustments to a measurement device to reduce errors associated with measurements. Without calibration, the measurement results of your device will drift over time and temperature. Calibration adjusts for these changes to improve measurement accuracy and ensure that your product meets its required specifications.

DAQ devices have high precision analog circuits that must be adjusted to obtain optimum accuracy in your measurements. Calibration determines what adjustments these analog circuits should make to the device measurements. During calibration, the value of a known, high precision measurement source is compared to the value your device acquires or generates. The adjustment values needed to minimize the difference between the known and measured values are stored in the EEPROM of the device as calibration constants. Before performing a measurement, these constants are read out of the EEPROM and are used to adjust the calibration hardware on the device. NI-DAQ determines when this is necessary and does it automatically. If you are not using NI-DAQ, you must load these values yourself.

You can calibrate E Series devices using either internal calibration or external calibration.

#### **Internal or Self-Calibration**

Self-calibration is a process to adjust the device relative to a highly accurate and stable internal reference on the device. Self-calibration is similar to the auto-calibration or auto-zero found on some instruments. You should perform a self-calibration whenever environmental conditions, such as ambient temperature, change significantly. To perform self-calibration, use the self-calibrate function or VI that is included with your driver software. Self-calibration requires no external connections.

## **External Calibration**

External calibration is a process to adjust the device relative to a traceable, high precision calibration standard. The accuracy specifications of your device change depending on how long it has been since your last external calibration. National Instruments recommends that you calibrate your device at least as often as the intervals listed in the accuracy specifications.

For a detailed calibration procedure for E Series devices (and B Series devices such as the NI 6013, NI 6014, NI 6015, and NI 6016) using NI-DAQmx, refer to the *E/S/M/B Series Calibration Procedure for NI-DAQmx*. For a detailed calibration procedure for B/E Series devices using Traditional NI-DAQ (Legacy), refer to the *E Series Calibration Procedure*. These documents can be found by selecting **Manual Calibration Procedures** at ni.com/calibration.

# **Signal Conditioning**

Many sensors and transducers require signal conditioning before a computer-based measurement system can effectively and accurately acquire the signal. The front-end signal conditioning system can include functions such as signal amplification, attenuation, filtering, electrical isolation, simultaneous sampling, and multiplexing. In addition, many transducers require excitation currents or voltages, bridge completion, linearization, or high amplification for proper and accurate operation. Therefore, most computer-based measurement systems include some form of signal conditioning in addition to plug-in data acquisition DAQ devices.

#### Sensors and Transducers

Sensors can generate electrical signals to measure physical phenomena, such as temperature, force, sound, or light. Some commonly used sensors are strain gauges, thermocouples, thermistors, angular encoders, linear encoders, and resistance temperature detectors (RTDs).

To measure signals from these various transducers, you must convert them into a form that a DAQ device can accept. For example, the output voltage of most thermocouples is very small and susceptible to noise. Therefore, you may need to amplify or filter the thermocouple output before digitizing it. The manipulation of signals to prepare them for digitizing is called signal conditioning.

For more information about sensors, refer to the following documents.

- For general information about sensors, visit ni.com/sensors.

- If you are using LabVIEW, refer to the *LabVIEW Help* by selecting **Help**»Search the LabVIEW Help in LabVIEW, and then navigate to the **Taking Measurements** book on the **Contents** tab.

- If you are using other application software, refer to Common Sensors in the *NI-DAQmx Help*, which you can access from Start»All Programs»National Instruments»NI-DAQ»NI-DAQmx Help, or the *LabVIEW 8.x Help*.

# Signal Conditioning Options

SCXI is a front-end signal conditioning and switching system for various measurement devices, including E Series devices. An SCXI system consists of a rugged chassis that houses shielded signal conditioning modules that amplify, filter, isolate, and multiplex analog signals from thermocouples or other transducers. SCXI is designed for large measurement systems or systems requiring high-speed acquisition.

System features include:

- Modular architecture—Choose your measurement technology

- Expandability—Expand your system to 3,072 channels

- **Integration**—Combine analog input, analog output, digital I/O, and switching into a single, unified platform

- **High bandwidth**—Acquire signals at an aggregate rate of up to 333 kHz

- **Connectivity**—Select from SCXI modules with thermocouple connectors or terminal blocks

## SCC

SCC is a front-end signal conditioning system for E Series plug-in data acquisition devices. A SCC system consists of a shielded carrier that holds up to 20 single or dual-channel SCC modules for conditioning thermocouples and other transducers. SCC is designed for small measurement systems where you need only a few channels of each signal type, or for portable applications. SCC systems also offer the most comprehensive and flexible signal connectivity options.

System features include:

- Modular architecture—Select your measurement technology on a per-channel basis

- Small-channel systems—Condition up to 16 analog input and eight digital I/O lines

- Low-profile/portable—Integrates well with other laptop computer measurement technologies

- High bandwidth—Acquire signals at rates up to 1.25 MHz

- **Connectivity**—Incorporates panelette technology to offer custom connectivity to thermocouple, BNC, LEMO<sup>™</sup> (B Series), and MIL Spec connectors

#### **5B Series**

5B is a front-end signal conditioning system for plug-in data acquisition devices. A 5B system consists of eight or 16 single-channel modules that plug into a backplane for conditioning thermocouples and other analog signals. National Instruments offers a complete line of 5B modules, carriers, backplanes, and accessories.

Note For more information about SCXI, SCC, and 5B series products, refer to ni.com/ signalconditioning.

# **Cables and Accessories**

NI offers a variety of products to use with E Series devices, such as:

- Cables and cable assemblies, shielded and ribbon

- Connector blocks, shielded and unshielded 50- and 68-pin screw terminals

- RTSI bus cables

- SCXI modules and accessories for isolating, amplifying, exciting, and multiplexing signals for relays and analog output; with SCXI you can condition and acquire up to 3,072 channels

- Low-channel-count signal conditioning modules, devices, and accessories, including conditioning for strain gauges and RTDs, simultaneous sample-and-hold circuitry, and relays

For more specific information about these products, refer to ni.com.

#### **Using Accessories with Devices**

Complete the following steps to choose a cable to connect an E Series device and an accessory:

- 1. Select an E Series device.

- 2. Using Table 1-1 or Table 1-2 as a guide, determine which accessories are appropriate for that device. Select an accessory. Table 1-3 provides descriptions for E Series device accessories.

- 3. Using Table 1-1 or Table 1-2 as a guide, determine which cable is required to connect your selected device and accessory.

|                                                       | Acessories and Recommended Cables                                                                                       |                                               |  |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

| Device                                                | TBX-68, CB-68LP,<br>CB-68LPR, DAQ Signal<br>Accessory, CA-1000,<br>BNC-2110, BNC-2111,<br>BNC-2120, BNC-2090,<br>SCB-68 | TB-2705                                       |  |

| 68-pin E Series<br>(except DAQCard)                   | SH6868EP (shielded)<br>R6868 (unshielded)                                                                               | Connects directly to the device<br>(PXI only) |  |

| E Series DAQCards:<br>NI 6024E, NI 6036E,<br>NI 6062E | SHC6868EP/M (shielded)<br>RC6868 (unshielded)                                                                           | —                                             |  |

#### Table 1-1. 68-Pin and DAQCard E Series Accessories and Recommended Cables

|                                                                                   |                                                                                                                                          | Acessories and Rec                                                                                                                        | commended Cables                                                                                                                          |                        |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| Device                                                                            | TBX-68,<br>CB-68LP,<br>CB-68LPR,<br>DAQ Signal<br>Accessory,<br>CA-1000,<br>BNC-2110,<br>BNC-2111,<br>BNC-2120,<br>BNC-2090,<br>SCB-68   | BNC-2115                                                                                                                                  | TBX-68,<br>CB-68LP,<br>CB-68LPR,<br>CA-1000,<br>SCB-68                                                                                    | SCB-100                |

| 100-pin E Series<br>with 64 AI<br>channels:<br>NI 6071E,<br>NI 6031E,<br>NI 6033E | SH1006868<br>(shielded); splits<br>into two 68-pin<br>connectors; these<br>accessories are<br>used with the<br>first 68-pin<br>connector | SH1006868<br>(shielded); splits<br>into two 68-pin<br>connectors; these<br>accessories are<br>used with the<br>second 68-pin<br>connector | SH1006868<br>(shielded); splits<br>into two 68-pin<br>connectors; these<br>accessories are<br>used with the<br>second 68-pin<br>connector | SH100100<br>(shielded) |

| 100-pin E Series<br>with 16 AI<br>channels and<br>32 DIO lines:<br>NI PCI-6025E   | SH1006868<br>(shielded); splits<br>into two 68-pin<br>connectors; these<br>accessories are<br>used with the<br>first 68-pin<br>connector | SH1006868<br>(shielded); splits<br>into two 68-pin<br>connectors; these<br>accessories are<br>used with the<br>second 68-pin<br>connector | SH1006868<br>(shielded); splits<br>into two 68-pin<br>connectors; these<br>accessories are<br>used with the<br>second 68-pin<br>connector | SH100100<br>(shielded) |

Table 1-2. 100-Pin E Series Accessories and Recommended Cables

| Table 1-3. E Series DAQ Accessories Overview | V |

|----------------------------------------------|---|

|----------------------------------------------|---|

| Accessory                                              | Description                                        |

|--------------------------------------------------------|----------------------------------------------------|

| SCXI Signal Conditioning                               | High-channel-count signal conditioning platform    |

| SCC Modular Signal Conditioning                        | Single or dual-channel signal conditioning modules |

| AMUX-64T, 5B, SSR, ER, and SC-204x Signal Conditioning | External signal conditioning accessories           |

| BNC-2110                                               | BNC accessory for 68-pin E Series devices          |

| Accessory                        | Description                                                                        |

|----------------------------------|------------------------------------------------------------------------------------|

| BNC-2111                         | BNC accessory for 68- or 100-pin E Series devices                                  |

| BNC-2115                         | BNC accessory for extended I/O on 100-pin E Series devices                         |

| BNC-2120                         | BNC accessory with function generator<br>(for 68-pin E Series devices)             |

| BNC-2090                         | Rack-mountable BNC accessory (for 68-pin E Series devices)                         |

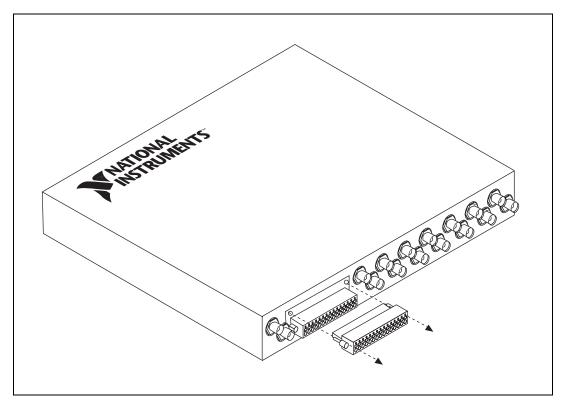

| CA-1000 enclosure                | Configurable connectivity enclosure                                                |

| TB-2705                          | Latching screw terminal block for PXI E Series modules                             |

| SCB-100                          | 100-pin, shielded screw terminal block with breadboard areas                       |

| SCB-68                           | 68-pin, shielded screw terminal block with breadboard areas                        |

| TBX-68                           | 68-pin, DIN rail-mountable screw terminal block                                    |

| CB-68LP, CB-68LPR                | 68-pin, low-cost screw terminal block                                              |

| Signal Source and Demo Accessory | DAQ signal accessory to demo and test analog, digital, and counter/timer functions |

Table 1-3. E Series DAQ Accessories Overview (Continued)

#### **Custom Cabling**

NI offers a variety of cables and accessories to help you prototype your application or to use if you frequently change device interconnections.

However, if you want to develop your own cable, adhere to the following guidelines for best results.

- Use shielded twisted-pair wires for each differential AI pair. Connect the shield for each signal pair to the ground reference at the source.

- Route the analog lines separately from the digital lines.

- When using a cable shield, use separate shields for the analog and digital halves of the cable. Failure to do so results in noise coupling into the analog signals from transient digital signals.

Mating connectors and a back-shell kit for making custom 68-pin cables are available from NI. For more information about the 68- and 100-pin

connectors used for DAQ devices, refer to the KnowledgeBase document, *Specifications and Manufacturers for Board Mating Connectors*.

# **Programming Devices in Software**

National Instruments measurement devices are packaged with NI-DAQ driver software, an extensive library of functions and VIs you can call from your application software, such as LabVIEW or LabWindows/CVI, to program all the features of your NI measurement devices. Driver software has an application programming interface (API), which is a library of VIs, functions, classes, attributes, and properties for creating applications for your device.

NI-DAQ includes two NI-DAQ drivers, Traditional NI-DAQ (Legacy) and NI-DAQmx. Each driver has its own API, hardware configuration, and software configuration. Refer to the *DAQ Getting Started Guide* for more information about the two drivers.

Traditional NI-DAQ (Legacy) and NI-DAQmx each include a collection of programming examples to help you get started developing an application. You can modify example code and save it in an application. You can use examples to develop a new application or add example code to an existing application.

To locate LabVIEW and LabWindows/CVI examples, open the National Instruments Example Finder:

- In LabVIEW, select Help»Find Examples.

- In LabWindows/CVI, select Help»NI Example Finder.

Measurement Studio, Visual Basic, and ANSI C examples are in the following directories:

- NI-DAQmx examples for Measurement Studio-supported languages are in the following directories:

- MeasurementStudio\VCNET\Examples\NI-DAQ

- MeasurementStudio\DotNET\Examples\NI-DAQ

- Traditional NI-DAQ (Legacy) examples for Visual Basic are in the following two directories:

- NI-DAQ\Examples\Visual Basic with Measurement Studio directory contains a link to the ActiveX control examples for use with Measurement Studio

- NI-DAQ\Examples\VBasic directory contains the examples not associated with Measurement Studio

- NI-DAQmx examples for ANSI C are in the NI-DAQ\Examples\ DAQmx ANSI C Dev directory

- Traditional NI-DAQ (Legacy) examples for ANSI C are in the NI-DAQ\Examples\VisualC directory

For additional examples, refer to zone.ni.com.

# I/O Connector Signal Descriptions

Table 1-4 describes the signals found on the I/O connectors. For a summary of the I/O signals by device family, refer to the specifications document for your device. Refer to Appendix A, *Device-Specific Information*, for the I/O pinout for your device.

| Signal Name | Reference | Direction | Description                                                                                                                                                                                                                                       |

|-------------|-----------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AI GND      | _         | _         | AI Ground—These pins are the reference point for<br>single-ended AI measurements in RSE mode and the bias<br>current return point for DIFF measurements. All three<br>ground references—AI GND, AO GND, and D GND—are<br>connected on the device. |

| AI <015>    | AI GND    | Input     | AI Channels 0 through 15—You can configure each channel pair, AI $< i, i+8 > (i = 07)$ , as either one differential input or two single-ended inputs.                                                                                             |

| AI <1663>   | AI GND    | Input     | AI Channels 16 through 63<br>(NI PCI-6031E/6033E/6071E only)—Each channel pair,<br>AI $\langle i, i + 8 \rangle$ ( $i = 1623, 3239, 4855$ ), can be configured<br>as either one differential input or two single-ended inputs.                    |

| AI SENSE    | —         | Input     | AI Sense—This pin is the reference node for AI <015> in NRSE mode.                                                                                                                                                                                |

| AI SENSE 2  | —         | Input     | <b>AI Sense 2</b> —This pin is the reference node for AI <16.63> in NRSE mode.                                                                                                                                                                    |

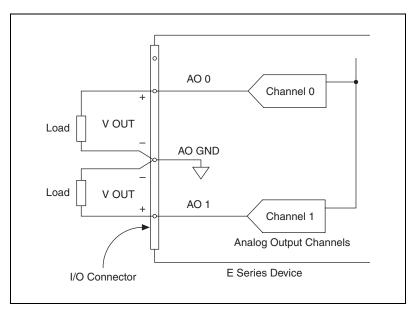

| AO 0        | AO GND    | Output    | Analog Channel 0 Output—This pin supplies the voltage output of AO channel 0.                                                                                                                                                                     |

| AO 1        | AO GND    | Output    | Analog Channel 1 Output—This pin supplies the voltage output of AO channel 1.                                                                                                                                                                     |

| AO GND      | _         | _         | <b>AO Ground</b> —The AO voltages are referenced to these<br>pins. All three ground references—AI GND, AO GND,<br>and D GND—are connected on the device.                                                                                          |

| Table 1-4 | 1/0 | Connector  | Signal | Descriptions |

|-----------|-----|------------|--------|--------------|

|           | 1/0 | 0011100101 | olynai | Descriptions |

| Signal Name            | Reference | Direction          | Description                                                                                                                                                                                                                                                                                                                                                                         |

|------------------------|-----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D GND                  | _         | _                  | <b>Digital Ground</b> —These pins supply the reference for the digital signals at the I/O connector as well as the +5 VDC supply. All three ground references—AI GND, AO GND, and D GND—are connected on the device.                                                                                                                                                                |

| P0.<07>                | D GND     | Input or<br>Output | <b>Digital I/O Signals</b> —You can individually configure each signal as an input or output. P0.6 and P0.7 can also control the up/down signal of Counters 0 and 1, respectively.                                                                                                                                                                                                  |

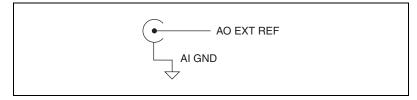

| AO EXT REF             | AO GND    | Input              | <b>External Reference</b> —This is the external reference input for the AO circuitry.                                                                                                                                                                                                                                                                                               |

| P1.<07>                | D GND     | Input or<br>Output | <b>NI 6025E only</b> —Port 1 bidirectional digital data lines for<br>the 82C55A programmable peripheral interface. P1.7 is the<br>most significant bit (MSB). P1.0 is the least significant bit<br>(LSB).                                                                                                                                                                           |

| P2.<07>                | D GND     | Input or<br>Output | <b>NI 6025E only</b> —Port 2 bidirectional digital data lines for the 82C55A programmable peripheral interface. P2.7 is the MSB. P2.0 is the LSB.                                                                                                                                                                                                                                   |

| P3.<07>                | D GND     | Input or<br>Output | <b>NI 6025E only</b> —Port 3 bidirectional digital data lines for<br>the 82C55A programmable peripheral interface. P3.7 is the<br>MSB. P3.0 is the LSB.                                                                                                                                                                                                                             |

| +5 V                   | D GND     | Output             | +5 V Power Source—These pins provide +5 V power.                                                                                                                                                                                                                                                                                                                                    |

| AI HOLD COMP           | D GND     | Output             | AI Hold Complete Event Signal—When enabled, this signal pulses once for each A/D conversion in sampling mode. The low-to-high edge indicates when the input signal can be removed from the input or switched to another signal.                                                                                                                                                     |

| EXT STROBE             | D GND     | Output             | <b>External Strobe Signal</b> —You can toggle this output with software controls to latch signals or trigger events on external devices. This functionality is not available in LabVIEW or NI-DAQ. EXT STROBE is used for controlling SCXI chassis, and it is not a general-purpose signal. If you want to use or control this signal, you must perform register-level programming. |

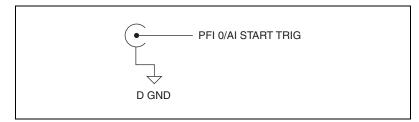

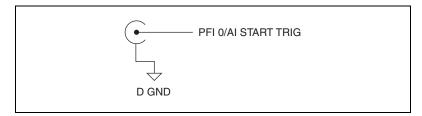

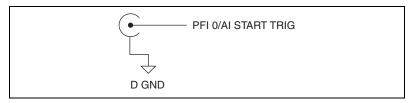

| PFI 0/AI START<br>TRIG | D GND     | Input              | <b>PFI 0</b> —As an input, this pin is a programmable function interface (PFI).                                                                                                                                                                                                                                                                                                     |

|                        |           | Output             | AI Start Trigger Signal—As an output, this pin is the<br>ai/StartTrigger signal. In post-trigger DAQ sequences, a<br>low-to-high transition indicates the initiation of the<br>acquisition sequence. In applications with pre-trigger<br>samples, a low-to-high transition indicates the initiation of<br>the pre-trigger samples.                                                  |

| Table 1-4. | I/O Connector | Signal Descriptions | (Continued) |

|------------|---------------|---------------------|-------------|

|------------|---------------|---------------------|-------------|

| Signal Name     | Reference | Direction | Description                                                                                                                                                                                                                                                                                                    |

|-----------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFI 1/AI REF    | D GND     | Input     | <b>PFI 1</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

| TRIG, PFI 1     |           | Output    | <b>AI Reference Trigger Signal</b> —As an output, this pin is<br>the ai/ReferenceTrigger signal. In applications with<br>pre-trigger samples, a low-to-high transition indicates the<br>initiation of the post-trigger samples. AI Reference Trigger<br>is not used in applications with post-trigger samples. |

| PFI 2/AI CONV   | D GND     | Input     | <b>PFI 2</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

| CLK             |           | Output    | AI Convert Clock Signal—As an output, this pin is the ai/ConvertClock signal. A high-to-low edge on AI CONV indicates that an A/D conversion is occurring.                                                                                                                                                     |

| PFI 3/CTR 1 SRC | D GND     | Input     | <b>PFI 3</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

|                 |           | Output    | <b>Counter 1 Source Signal</b> —As an output, this pin is the Ctr1Source signal. This signal reflects the actual source connected to the general-purpose Counter 1.                                                                                                                                            |

| PFI 4/CTR 1     | D GND     | Input     | <b>PFI 4</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

| GATE            |           | Output    | <b>Counter 1 Gate Signal</b> —As an output, this pin is the Ctr1Gate signal. This signal reflects the actual gate signal connected to the general-purpose Counter 1.                                                                                                                                           |

| CTR 1 OUT D     | D GND     | Input     | <b>CTR 1 OUT</b> —As an input, this pin can be used to route signals directly to the RTSI bus.                                                                                                                                                                                                                 |

|                 |           | Output    | <b>Counter 1 Output Signal</b> —As an output, this pin emits the Ctr1InternalOutput signal.                                                                                                                                                                                                                    |

| PFI 5/AO SAMP   | D GND     | Input     | <b>PFI 5</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

| CLK             |           | Output    | <b>AO Sample Clock Signal</b> —As an output, this pin is the ao/SampleClock signal. A high-to-low edge on AO SAMP indicates that the AO primary group is being updated.                                                                                                                                        |

| PFI 6/AO START  | D GND     | Input     | <b>PFI 6</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

| TRIG            |           | Output    | AO Start Trigger Signal—As an output, this pin is the ao/StartTrigger signal. In timed AO sequences, a low-to-high transition indicates the initiation of the waveform generation.                                                                                                                             |

| PFI 7/AI SAMP   | D GND     | Input     | <b>PFI 7</b> —As an input, this pin is a PFI.                                                                                                                                                                                                                                                                  |

| CLK             |           | Output    | AI Sample Clock Signal—As an output, this pin is the ai/SampleClock signal. This pin pulses once at the start of each AI sample in the interval sample. A low-to-high transition indicates the start of the sample.                                                                                            |

Table 1-4.

I/O Connector Signal Descriptions (Continued)

| Signal Name           | Reference | Direction | Description                                                                                                                                                                                                                               |

|-----------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PFI 8/CTR 0 SRC       | D GND     | Input     | <b>PFI 8</b> —As an input, this pin is a PFI.                                                                                                                                                                                             |

|                       |           | Output    | <b>Counter 0 Source Signal</b> —As an output, this pin is the Ctr0Source signal. This signal reflects the actual source connected to the general-purpose Counter 0.                                                                       |

| PFI 9/CTR 0<br>GATE   | D GND     | Input     | <b>PFI 9</b> —As an input, this pin is a PFI.                                                                                                                                                                                             |

|                       |           | Output    | <b>Counter 0 Gate Signal</b> —As an output, this pin is the Ctr0Gate signal. This signal reflects the actual gate signal connected to the general-purpose Counter 0.                                                                      |

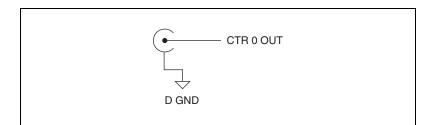

| CTR 1 OUT             | D GND     | Input     | <b>Counter 1 Output Signal</b> —As an input, this pin can be used to route signals directly to the RTSI bus.                                                                                                                              |

|                       |           | Output    | As an output, this pin emits the Ctr0InternalOutput signal.                                                                                                                                                                               |

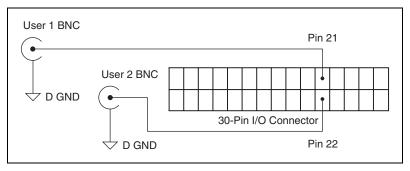

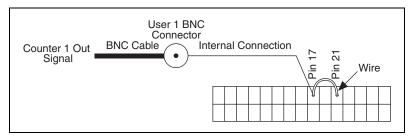

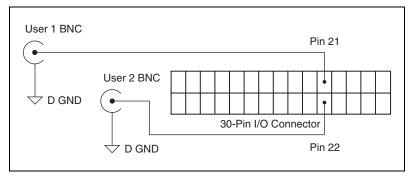

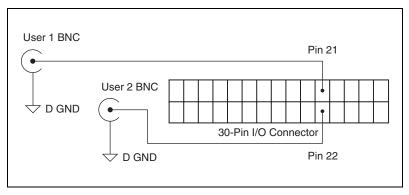

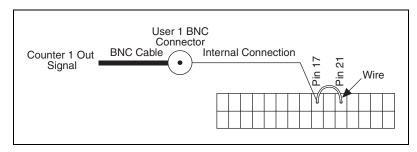

| FREQ OUT/USER<br><12> | D GND     | Output    | Frequency Output Signal—This output is from the frequency generator.                                                                                                                                                                      |

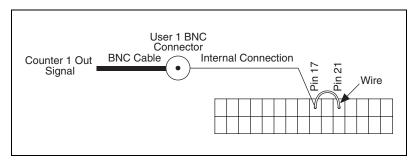

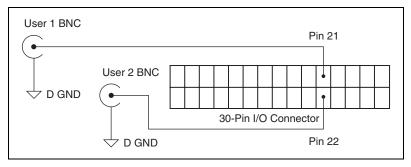

|                       |           | I/O       | User <12>—On BNC devices, these signals connect<br>directly from a screw terminal to a BNC. For example, if<br>you connect CTR 0 OUT to the USER 1 screw terminal<br>with a wire, the Ctr0Out signal also is driven to the User 1<br>BNC. |

Table 1-4. I/O Connector Signal Descriptions (Continued)

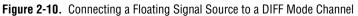

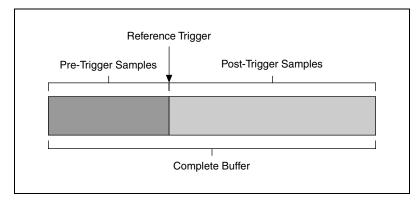

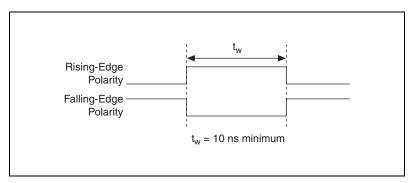

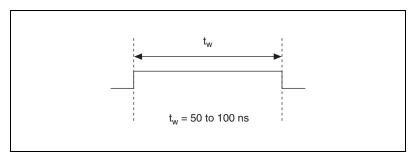

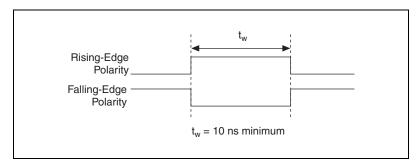

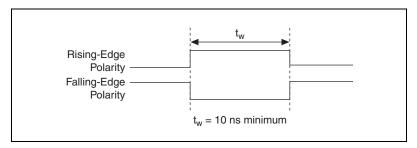

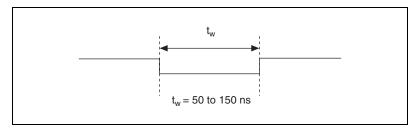

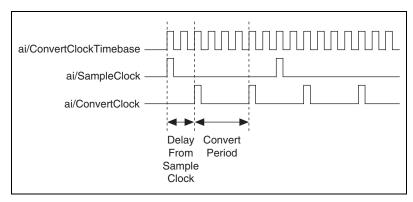

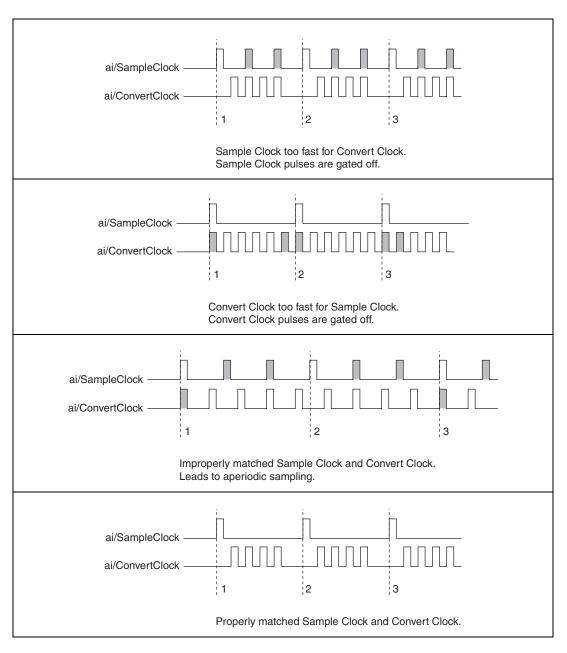

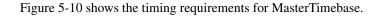

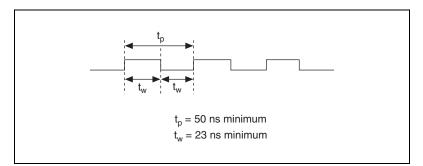

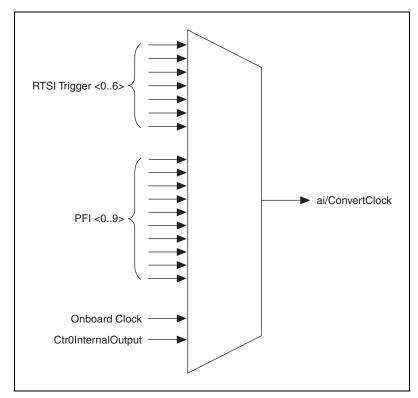

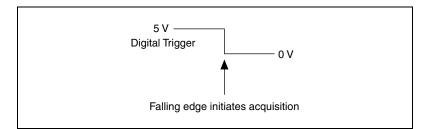

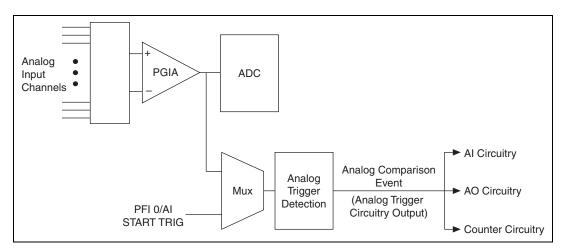

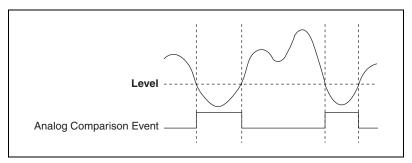

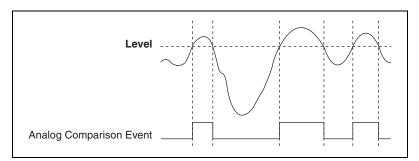

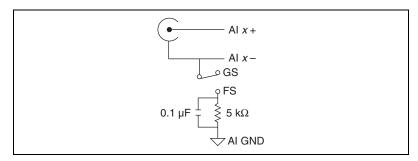

## **Terminal Name Equivalents**