#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

#### **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

**CB-27**

# PC-AO-2DC/ DAQCard TM-AO-2DC User Manual

Analog Output and Digital I/O Boards for the PC and Macintosh

**April 1996 Edition**

Part Number 320919B-01

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100

Technical support fax: (512) 794-5678

#### **Branch Offices:**

Australia 03 9 879 9422, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 519 622 9310, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 90 527 2321, France 1 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 95 800 010 0793, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, U.K. 01635 523545

#### **Limited Warranty**

The PC-AO-2DC and DAQCard™-AO-2DC are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

$LabVIEW^{\circledR}, NI-DAQ^{\circledR}, RTSI^{\circledR}, \ DAQCard^{\tiny{TM}}, and \ DAQPad^{\tiny{TM}} \ are \ trademarks \ of \ National \ Instruments \ Corporation.$

Product and company names listed are trademarks or trade names of their respective companies.

# WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

# **Contents**

| About This Manual                               | ix         |

|-------------------------------------------------|------------|

| Organization of This Manual                     |            |

| Conventions Used in This Manual                 | X          |

| National Instruments Documentation              |            |

| Related Documentation                           |            |

| Customer Communication                          |            |

|                                                 |            |

| Chapter 1                                       |            |

| Introduction                                    | 1_1        |

| About Your AO-2DC Device                        |            |

| What You Need to Get Started                    |            |

| Software Programming Choices                    |            |

| LabVIEW and LabWindows/CVI Application Software | 1-2<br>1_2 |

| NI-DAQ Driver Software                          |            |

| Register-Level Programming                      |            |

| Optional Equipment                              |            |

| Custom Cables                                   |            |

| Unpacking                                       |            |

| Onpacking                                       | 1-3        |

| Chapter 2                                       |            |

| <del>-</del>                                    | 2.1        |

| Installation and Configuration                  |            |

| Hardware Installation                           |            |

| Configuration                                   |            |

| Bus-Related Configuration                       |            |

| Plug and Play Mode                              |            |

| Switchless Mode                                 |            |

| Base I/O Address Selection                      |            |

| Data Acquisition-Related Configuration          |            |

| Analog Output Polarity Selection                |            |

| Current Outputs                                 |            |

| Digital I/O Configuration                       | 2-4        |

| Chapter 2                                       |            |

| Chapter 3                                       |            |

| Signal Connections                              |            |

| I/O Connectors                                  |            |

| Signal Connection Descriptions                  |            |

| Analog Output Signal Connections                |            |

| Voltage Output                                  |            |

| Power-up Condition                              |            |

| Current Output                                  |            |

| Power-up Condition                              |            |

| Digital I/O Signal Connections                  |            |

| Power-up Condition                              | 3-9        |

| Chapter 4                       |            |

|---------------------------------|------------|

| Theory of Operation             |            |

| Functional Overview             | 4-1        |

| I/O Channel Interface Circuitry | 4-2        |

| Analog Output                   | 4-3        |

| Digital I/O                     | 4-5        |

| Power-down Mode                 | 4-6        |

| Appendix A                      |            |

| Specifications                  | A-1        |

| -<br>                           |            |

| Appendix B                      |            |

| X25020 Data Sheet               | B-1        |

| Appendix C                      |            |

| Connector Block Pin Map         | C-1        |

| 1                               |            |

| Appendix D                      |            |

| Register-Level Programming      | D-1        |

| Appendix E                      |            |

| Calibration                     | E 1        |

| Candiation                      | ,L-1       |

| Appendix F                      |            |

| Power-Management Modes          | F-1        |

|                                 |            |

| Appendix G                      |            |

| PCMCIA Questions and Answers    | G-1        |

|                                 |            |

| Appendix H                      |            |

| Customer Communication          | H-1        |

| GlossaryG                       | loccory 1  |

| Giossai y                       | 1088ai y-1 |

| Index                           | Index-1    |

# **Figures**

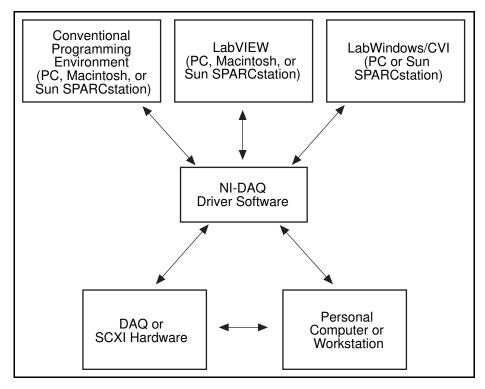

| Figure 1-1. | The Relationship between the Programming Environment, NI-DAQ, and |      |

|-------------|-------------------------------------------------------------------|------|

|             | Your Hardware                                                     | 1-3  |

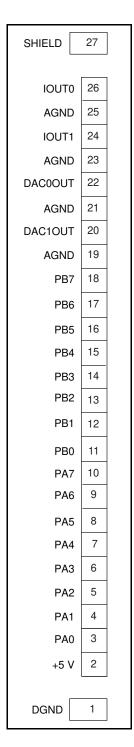

| Figure 3-1. | PC-AO-2DC I/O Connector Pin Assignments                           | 3-2  |

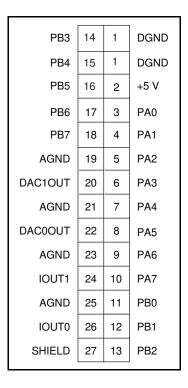

| Figure 3-2. | DAQCard-AO-2DC I/O Connector Pin Assignments                      |      |

| Figure 3-3. | Screw Terminal Assignments for the CB-27 I/O Connector Block      |      |

| Figure 3-4. | DAC Channel Connection as Voltage Output                          |      |

| Figure 3-5. | DAC Channel Connection as Current Output, External Loop Supply    |      |

| Figure 3-6. | Current Loop Connection, Load and External Supply Grounded        |      |

| Figure 3-7. | Digital I/O Connections                                           | 3-8  |

| Figure 4-1  | PC-AO-2DC and DAQCard-AO-2DC Block Diagram                        | 4-1  |

|             | PC I/O Interface Circuitry Block Diagram of PC-AO-2DC             |      |

| Figure 4-3. | PCMCIA I/O Interface Circuitry Block Diagram of DAQCard-AO-2DC    |      |

| Figure 4-4. | Analog Output Circuitry Block Diagram                             |      |

| Figure 4-5. | Digital I/O Circuitry Block Diagram                               |      |

| Figure C-1. | CB-50 LP and CB-50 Pin Assignments for the DAQCard-AO-2DC         |      |

|             | Using the PSH27-50F-D1 Cable                                      | C-2  |

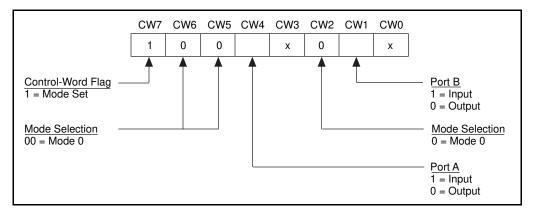

| Figure D-1. | Conrol Word Format                                                | D-12 |

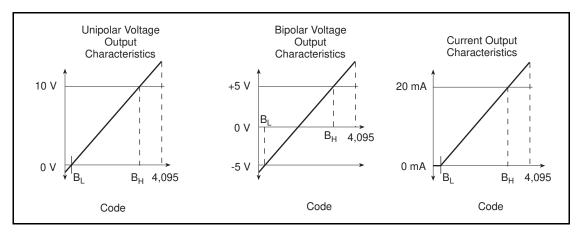

| Figure E-1. | PC-AO-2DC and DAQCard-AO-2DC Output Characteristics               | E-1  |

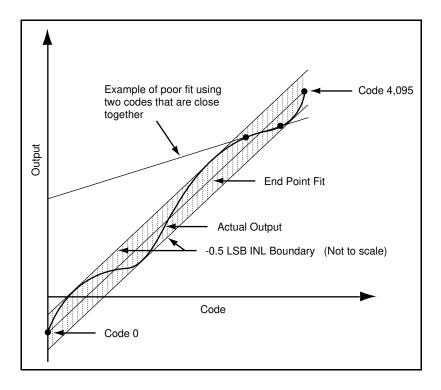

|             | DAC Characteristics                                               |      |

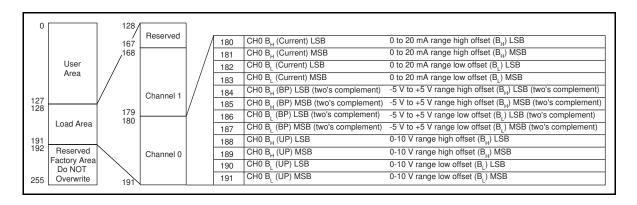

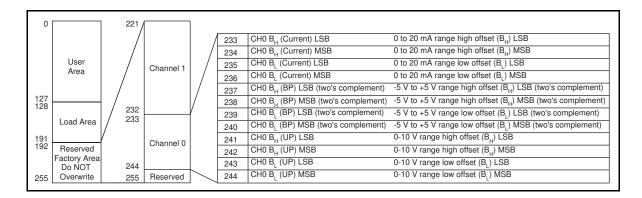

| Figure E-3. | EEPROM Map of the PC-AO-2DC and DAQCard-AO-2DC                    | E-5  |

|             | Factory Area of the EEPROM Map                                    |      |

|             |                                                                   |      |

|             | Tables                                                            |      |

| Table D-1.  | PC-AO-2DC and DAQCard-AO-2DC Register Map                         | D-2  |

| Table D-2.  |                                                                   |      |

| Table F-1.  | DAQCard-AO-2DC Power-Management Modes                             | F-2  |

# **About This Manual**

\_\_\_\_

This manual describes the electrical and mechanical aspects of the PC-AO-2DC and DAQCard-AO-2DC and contains information concerning their installation and operation. The PC-AO-2DC is fully compatible with the industry-standard Intel-Microsoft Plug and Play Specification version 1.0a. The DAQCard-AO-2DC is for computers equipped with a PCMCIA Type II slot.

The PC-AO-2DC and DAQCard-AO-2DC are analog output and digital I/O devices for PC/XT/AT and IBM Personal System 2 (PS/2) models 25 and 30 computers. You can also use the DAQCard-AO-2DC with Macintosh computers equipped with PCMCIA Type II slots. These devices are designed for low-cost data acquisition and control for applications in laboratory testing, production testing, and industrial process monitoring and control.

### **Organization of This Manual**

The PC-AO-2DC/DAQCard-AO-2DC User Manual is organized as follows:

- Chapter 1, Introduction, describes the PC-AO-2DC and DAQCard-AO-2DC; lists what you

need to get started; describes the optional software and optional equipment; and explains how

to unpack your AO-2DC.

- Chapter 2, *Installation and Configuration*, contains instructions for installing the PC-AO-2DC and DAQCard-AO-2DC, installing the NI-DAQ software, and cabling.

- Chapter 3, *Signal Connections*, describes the pin arrangement, signal names, and signal connections on the PC-AO-2DC and DAQCard-AO-2DC.

- Chapter 4, *Theory of Operation*, describes the theory of operation for analog output and digital I/O using the PC-AO-2DC and DAQCard-AO-2DC.

- Appendix A, Specifications, lists the specifications of the PC-AO-2DC and DAQCard-AO-2DC.

- Appendix B, X25020 Data Sheet, contains a manufacturer data sheet for the X25020 SPI serial EEPROM (Xicor). This EEPROM is used on both the PC-AO-2DC and DAQCard-AO-2DC.

- Appendix C, Connector Block Pin Map, gives the pin assignments for the CB-50 LP or CB-50 I/O connector blocks when using the PSH27-50F-D1 cable with the DAQCard-AO-2DC.

- Appendix D, *Register-Level Programming*, describes in detail the address and function of each of the PC-AO-2DC and DAQCard-AO-2DC registers.

- Appendix E, *Calibration*, discusses the calibration procedures for the PC-AO-2DC and DAQCard-AO-2DC. You can perform calibration only at the register level.

- Appendix F, Power-Management Modes, describes the power-management modes of the DAQCard-AO-2DC.

- Appendix G, *PCMCIA Questions and Answers*, contains a list of common questions and answers relating to PCMCIA card operation.

- Appendix H, *Customer Communication*, contains forms you can use to request help from National Instruments or to comment on our products.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, and symbols.

- The *Index* alphabetically lists the topics in this manual, including the page where you can find the topic.

#### **Conventions Used in This Manual**

The following conventions are used in this manual:

AO-2DC denotes either or both the PC-AO-2DC and DAQCard-AO-2DC.

**bold** Bold text denotes menus, menu items, or dialog box buttons or options.

**bold italic** Bold italic text denotes a note, caution, or warning.

italic Italic text denotes emphasis on a specific board or on other important

information, a cross reference, or an introduction to a key concept.

monospace Text in this font denotes text or characters that are to be literally input

from the keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, variables, filenames, and extensions, and for statements and

comments taken from program code.

Mac Mac refers to Macintosh computers.

NI-DAQ NI-DAQ refers to the NI-DAQ software for PC compatibles and

Macintosh computers unless otherwise noted.

PC PC refers to PC/XT/AT and IBM PS/2 models 25 and 30 computers.

SCXI SCXI stands for Signal Conditioning eXtensions for Instrumentation and

is a National Instruments product line designed to perform front-end signal

conditioning for National Instruments plug-in DAQ devices.

82C55A 82C55A refers to the OKI Semiconductor 82C55A programmable

peripheral interface.

- ◆ The ♦ symbol indicates that the following text applies only to a specific device.

- Angle brackets containing numbers separated by an ellipsis represent a range of values associated with a bit, port, or signal name (for example, ACH<0..7> stands for ACH0 through ACH7).

Abbreviations, acronyms, metric prefixes, mnemonics, symbols, and terms are listed in the *Glossary*.

#### **National Instruments Documentation**

The *PC-AO-2DC/DAQCard-AO-2DC User Manual* is one piece of the documentation set for your data acquisition system. You could have any of several types of manuals depending on the hardware and software in your system. Use the manuals you have as follows:

- Your DAQ hardware user manuals—These manuals have detailed information about the DAQ hardware that plugs into or is connected to your computer. Use these manuals for hardware installation and configuration instructions, specification information about your DAQ hardware, and application hints.

- Software manuals—Examples of software manuals you may have are the LabVIEW and LabWindows® /CVI manual sets. After you set up your hardware system, use either the application software (LabVIEW or LabWindows/CVI) manuals or the NI-DAQ manuals that came with other DAQ devices to help you write your application. If you have a large and complicated system, it is worthwhile to look through the software manuals before you configure your hardware.

- Accessory installation guides or manuals—If you are using accessory products, read the

terminal block and cable assembly installation guides or accessory board user manuals. They

explain how to physically connect the relevant pieces of the system. Consult these guides

when you are making your connections.

#### **Related Documentation**

The following documents contain information that you may find helpful as you read this manual:

- Your online NI-DAQ software manuals (hardcopy available upon request)

- Your computer operating system manual

# **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix H, *Customer Communication*, at the end of this manual.

# Chapter 1 Introduction

This chapter describes the PC-AO-2DC and DAQCard-AO-2DC; lists what you need to get started; describes the optional software and optional equipment; and explains how to unpack your AO-2DC.

#### **About Your AO-2DC Device**

Thank you for purchasing the PC-AO-2DC or DAQCard-AO-2DC, which are analog output and digital I/O devices for PC/XT/AT, IBM Personal System 2 (PS/2) models 25 and 30 and Macintosh computers equipped with PCMCIA Type II slot. Each device has two 12-bit DACs and current output circuitry providing two channels of voltage or current outputs. You can use the voltage or current outputs in set-point types of applications. Each device also provides 16 bits of digital I/O lines. You can install the PC-AO-2DC in any 8-bit or 16-bit expansion slot on a PC, while the DAQCard-AO-2DC is for PCs and Macintosh computers equipped with a PCMCIA Type II slot.

The low cost of a system based on the PC-AO-2DC or DAQCard-AO-2DC makes them ideal for laboratory work in industrial and academic environments. You can use the analog output channels to generate experimental stimuli, to control machines and processes, and to generate analog functions. You can use the digital I/O lines to switch external devices, such as transistors and solid-state relays, and to read the status of external digital logic.

Your AO-2DC device, used in conjunction with the computer, is a versatile, cost-effective platform for laboratory test, measurement, and control. The additional advantages of small size, light weight, and low power consumption make the DAQCard-AO-2DC ideal for use in portable computers. This portability makes remote data acquisition practical. The DAQCard-AO-2DC requires very little power when operating, thus extending the life of the computer batteries.

Detailed specifications of the PC-AO-2DC and DAQCard-AO-2DC are in Appendix A, *Specifications*.

### What You Need to Get Started

| To set up and use your AO-2DC device, you will need the fo | llowing: |

|------------------------------------------------------------|----------|

| One of the following devices: PC-AO-2DC DAQCard-AO-2DC     |          |

| ☐ PC-AO-2DC/DAQCard-AO-2DC User Manual                     |          |

Introduction Chapter 1

| One of the following software packages and documentation:                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LabVIEW for Macintosh (DAQCard-AO-2DC only)                                                                                                                                                                                            |

| LabVIEW for Windows                                                                                                                                                                                                                    |

| LabWindows/CVI for Windows                                                                                                                                                                                                             |

| NI-DAQ software for Macintosh (DAQCard-AO-2DC only)                                                                                                                                                                                    |

| NI-DAQ software for PC compatibles                                                                                                                                                                                                     |

| One of the following connector blocks (must be purchased separately): CB-50 LP (low cost) or CB-50 (DIN-rail mountable) I/O connector blocks with NB1 cable (PC-AO-2DC) CB-27 I/O connector block with PR27-30F cable (DAQCard-AO-2DC) |

| Your computer                                                                                                                                                                                                                          |

# **Software Programming Choices**

There are several options to choose from when programming your National Instruments DAQ and SCXI hardware. You can use LabVIEW, LabWindows/CVI, or NI-DAQ.

#### LabVIEW and LabWindows/CVI Application Software

LabVIEW and LabWindows/CVI are innovative program development software packages for data acquisition and control applications. LabVIEW uses graphical programming, whereas LabWindows enhances traditional programming languages. Both packages include extensive libraries for data acquisition, instrument control, data analysis, and graphical data presentation.

LabVIEW features interactive graphics, a state-of-the-art user interface, and a powerful graphical programming language. The LabVIEW Data Acquisition VI Library, a series of VIs for using LabVIEW with National Instruments DAQ hardware, is included with LabVIEW. The LabVIEW Data Acquisition VI Libraries are functionally equivalent to the NI-DAQ software.

LabWindows/CVI features interactive graphics, a state-of-the-art user interface, and uses the ANSI standard C programming language. The LabWindows/CVI Data Acquisition Library, a series of functions for using LabWindows/CVI with National Instruments DAQ hardware, is included with the NI-DAQ software kit. The LabWindows/CVI Data Acquisition libraries are functionally equivalent to the NI-DAQ software.

Using LabVIEW or LabWindows/CVI software will greatly reduce the development time for your data acquisition and control application.

Chapter 1 Introduction

#### **NI-DAQ Driver Software**

The NI-DAQ driver software is included at no charge with all National Instruments DAQ hardware. NI-DAQ is not packaged with SCXI or accessory products, except for the SCXI-1200. NI-DAQ has an extensive library of functions that you can call from your application programming environment. These functions include routines for analog input (A/D conversion), buffered data acquisition (high-speed A/D conversion), analog output (D/A conversion), waveform generation, digital I/O, counter/timer operations, SCXI, RTSI, self-calibration, messaging, and acquiring data to extended memory.

NI-DAQ has both high-level DAQ I/O functions for maximum ease of use and low-level DAQ I/O functions for maximum flexibility and performance. Examples of high-level functions are streaming data to disk or acquiring a certain number of data points. An example of a low-level function is writing directly to registers on the DAQ device. NI-DAQ does not sacrifice the performance of National Instruments DAQ devices because it lets multiple devices operate at their peak performance.

NI-DAQ also internally addresses many of the complex issues between the computer and the DAQ hardware such as programming interrupts and DMA controllers. NI-DAQ maintains a consistent software interface among its different versions so that you can change platforms with minimal modifications to your code. Figure 1-1 illustrates the relationship between NI-DAQ and LabVIEW and LabWindows/CVI. You can see that the data acquisition parts of LabVIEW and LabWindows/CVI are functionally equivalent to the NI-DAQ software.

Figure 1-1. The Relationship between the Programming Environment, NI-DAQ, and Your Hardware

Introduction Chapter 1

#### **Register-Level Programming**

The final option for programming any National Instruments DAQ hardware is to write register-level software. Writing register-level programming software can be very time-consuming and inefficient and is not recommended for most users.

Even if you are an experienced register-level programmer, consider using NI-DAQ, LabVIEW, or LabWindows/CVI to program your National Instruments DAQ hardware. Using the NI-DAQ, LabVIEW, or LabWindows/CVI software is as easy and as flexible as register-level programming and can save weeks of development time.

# **Optional Equipment**

You can use the following National Instruments product with your PC-AO-2DC board:

CB-50 LP or CB-50 I/O connector block with 0.5 m or 1.0 m NB-1 connector cable

You can use the following National Instruments product with your DAQCard-AO-2DC device:

• CB-27 I/O connector block with PR27-30F 1.0 m connector cable

Note: The CB-50 connector block with PSH27-50F-D1 I/O cable is not recommended for use with the DAQCard-AO-2DC. The PSH27-50F-D1 is optimized for use with the DAQCard-DIO-24.

For more information about optional equipment available from National Instruments, refer to your National Instruments catalog or call the office nearest you.

### **Custom Cables**

National Instruments currently offers cable termination accessories, the CB-50 LP and CB-50, for use with the PC-AO-2DC. A terminated, 50-conductor, flat ribbon cable is necessary to connect the board to the termination accessory. For the DAQCard-AO-2DC, National Instruments supplies the CB-27 kit, a 27-pin terminal block. A special cable is required to connect the card and accessory. You can attach signal input and output wires to screw terminals on the connector blocks and thereby connect to your AO-2DC device I/O connector.

The CB-50 LP, CB-50, and CB-27 are useful for initial prototyping of an application or in situations where your AO-2DC device interconnections are frequently changed. The CB-50 LP is the low-cost version of the CB-50, whereas the CB-50 is DIN-rail mountable for field wiring. When you develop a final field wiring scheme, however, you may want to develop your own cable. This section contains information and guidelines for designing custom cables.

#### ♦ PC-AO-2DC

The PC-AO-2DC I/O connector is a 50-pin male ribbon cable header. The manufacturer part numbers used by National Instruments for this header are as follows:

- Electronic Products Division/3M (part number 3596-5002)

- T&B/Ansley Corporation (part number 609-500)

The mating connector for the PC-AO-2DC is a 50-position, polarized, ribbon socket connector with strain relief. National Instruments uses a polarized (keyed) connector to

Chapter 1 Introduction

prevent inadvertent upside-down connection to the PC-AO-2DC. Recommended manufacturer part numbers for this mating connector are as follows:

- Electronic Products Division/3M (part number 3425-7650)

- T&B/Ansley Corporation (part number 609-5041CE)

The following are the standard ribbon cables (50-conductor, 28 AWG, stranded) that can be used with these connectors:

- Electronic Products Division/3M (part number 3365/50)

- T&B/Ansley Corporation (part number 171-50)

- ♦ DAQCard-AO-2DC

The DAQCard-AO-2DC I/O connector is a 25-pin female PCMCIA I/O connector. The manufacturer part number of the connector National Instruments uses is as follows:

• AMP Manufacturing (part number 746288-7)

The following are the standard ribbon cables (30-conductor, 28 AWG, stranded) that work with the 30-pin connectors:

- Electronic Products Division/3M (part number 3365-30)

- T&B/Ansley Corporation (part number 171-30)

# **Unpacking**

Your AO-2DC device is shipped in an antistatic envelope to prevent electrostatic damage. Electrostatic discharge can damage several components on the device. To avoid damage in handling the device, take the following precautions:

- Ground yourself via a grounding strap or by holding a grounded object.

- Touch the package to a metal part of your computer chassis before removing the device from the package.

- Remove the device from the package and inspect the device for loose components or any other sign of damage. Notify National Instruments if the device appears damaged in any way. *Do not* install a damaged device into your computer.

- *Never* touch the exposed pins of connectors.

- Store your AO-2DC device in the antistatic envelope when not in use.

# **Chapter 2 Installation and Configuration**

This chapter contains instructions for installing the PC-AO-2DC and DAQCard-AO-2DC, installing the NI-DAQ software, and cabling.

#### **Hardware Installation**

♦ PC-AO-2DC

You can install the PC-AO-2DC in any available 8-bit or 16-bit expansion slot in your computer. The following are general installation instructions, but consult your PC user manual or technical reference manual for specific instructions and warnings.

Warning: To prevent electrical SHOCK HAZARD, make sure that the power switch is off and the power cord has been removed from the power entry module.

- 1. Turn off your computer.

- 2. Remove the top cover or access port to the I/O channel.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Record the PC-AO-2DC serial and revision numbers on the Hardware and Software Configuration form in Appendix H, *Customer Communication*. You will need these numbers when you install and configure your device.

- 5. Insert the PC-AO-2DC into an 8-bit or a 16-bit slot.

- 6. Screw the mounting bracket of the PC-AO-2DC to the back panel rail of the computer.

- 7. Check the installation.

- 8. Replace the cover.

The PC-AO-2DC board is installed. You are ready to install your software and configure your board for the programming system you are using.

#### ♦ DAQCard-AO-2DC

You can install the DAQCard-AO-2DC in any available Type II PCMCIA slot in your computer.

The PCMCIA software configures the card for your computer and automatically determines the base address. The following are general installation instructions, but consult your computer user manual or technical reference manual for specific instructions and warnings.

- 1. Turn off your computer. If your computer supports hot insertion, you may insert or remove the DAQCard-AO-2DC at any time, whether the computer is powered on or off.

- 2. Remove the PCMCIA slot cover on your computer.

- 3. Insert the 68-pin PCMCIA bus connector of the DAQCard-AO-2DC into the PCMCIA slot. The card is keyed so that you can insert it only one way.

- 4. Attach the I/O cable. The optional PR27-30F cable available for the DAQCard-AO-2DC plugs into the 25-pin I/O connector on the other end of the card. This cable allows connection to other National Instruments products. When plugging and unplugging the cable, always grasp the cable by the connector. Never pull directly on the I/O cable to unplug it from the DAQCard-AO-2DC.

The DAQCard-AO-2DC is installed.

# Configuration

Whether you are using NI-DAQ, LabVIEW, or LabWindows/CVI, your AO-2DC devices are completely software configurable. Refer to your software documentation to install and configure your software.

If you are a register-level programmer, refer to Appendix D, *Register-Level Programming*, of this manual.

#### ♦ PC-AO-2DC

Two types of configuration are performed on the PC-AO-2DC—bus related and data acquisition related. Bus-related configuration includes setting the base I/O address. Data acquisition-related configuration includes such settings as analog output polarity selection, range selection, and digital I/O configuration.

#### **Bus-Related Configuration**

The PC-AO-2DC works in either a Plug and Play mode or a switchless mode. These modes dictate how the base I/O address is determined and assigned to the board.

#### **Plug and Play Mode**

The PC-AO-2DC is fully compatible with the industry-standard Intel/Microsoft Plug and Play Specification version 1.0. A Plug and Play system arbitrates and assigns resources through software, freeing you from manually setting switches and jumpers. These resources include the board base I/O address. The PC-AO-2DC is configured at the factory to request these resources from the Plug and Play Configuration Manager.

The Configuration Manager receives all of the resource requests at start up, compares the available resources to those requested, and assigns the available resources as efficiently as possible to the Plug and Play boards. Application software can query the Configuration Manager to determine the resources assigned to each board without your involvement. The Plug and Play software is installed as a device driver or as an integral component of the computer BIOS.

If you have the Windows 95 operating system on your PC, it will configure your PC-AO-2DC. Refer to your NI-DAQ documentation for more information.

#### **Switchless Mode**

You can use the PC-AO-2DC in a non-Plug and Play system as a switchless DAQ board. A non-Plug and Play system is a system in which the Configuration Manager has not been installed and which does not contain any non-National Instruments Plug and Play products. You use a configuration utility to enter the base address, and the application software assigns it to the board.

Note: Avoid resource conflicts with non-National Instruments devices. For example, do not configure two devices for the same base address.

#### **Base I/O Address Selection**

You can configure the PC-AO-2DC to use base addresses in the range of 100 to 3E0 hex. The PC-AO-2DC occupies 32 bytes of address space and must be located on a 32-byte boundary. Therefore, valid addresses include 100, 120, 140, ..., 3C0, 3E0 hex. This selection is software configured and does not require you to manually change any settings on the board.

#### DAQCard-AO-2DC

If you are using a PC, Windows 95 will automatically configure your DAQCard-AO-2DC.

If you are using a Macintosh with National Instruments software such as NI-DAQ or LabVIEW, see the *Using the NI-DAQ Control Panel to Configure Your Hardware* section in your *NI-DAQ Software Reference Manual*.

You can test the hardware configuration by using the NI-DAQ Configuration Utility or WDAQCONF if you are using a PC.

#### **Data Acquisition-Related Configuration**

The AO-2DC devices supply two channels of analog output voltage and two channels of analog output current sinks at the I/O connector. You can select the range for the analog output circuitry though software. The range can be either bipolar or unipolar.

#### **Analog Output Polarity Selection**

You can configure each analog output voltage channel for either unipolar or bipolar output. A unipolar configuration has a range of 0 to +10 V at the voltage outputs. A bipolar configuration has a range of -5 to +5 V at the voltage outputs. You do not need to configure both channels for the same range.

Note: As a power-on condition, both channels power up as unipolar outputs. The output voltage will be  $\pm 0.5$  V maximum within 100 ms of power up.

#### **Current Outputs**

For current outputs, the analog polarity selection should be unipolar.

The AO-2DC devices provide two channels of current sinks for current loop applications. You can program the current outputs for 0 to 20 mA current loops. You have to provide the voltage source for completing the current loop.

Note: As a power-on condition, both channels provide no current sink at power up.

#### **Digital I/O Configuration**

The AO-2DC devices contain 16 lines of digital I/O for general use. These lines are available as two 8-bit I/O ports. You may configure these ports as either an input port or an output port.

Note: As a power-on condition, all the digital lines are configured as digital inputs at power up. These lines have internal weak pull ups.

# Chapter 3 Signal Connections

This chapter describes the pin arrangement, signal names, and signal connections on the PC-AO-2DC and DAQCard-AO-2DC.

Warning:

Connections that exceed any of the maximum ratings of input or output signals on the PC-AO-2DC or DAQCard-AO-2DC may damage your AO-2DC device and your computer. This warning includes connecting any power signals to ground and vice versa. National Instruments is NOT liable for any damages resulting from any such signal connections.

#### I/O Connectors

Figure 3-1 shows the pin assignments for the PC-AO-2DC I/O connector. You can use the CB-50 LP or CB-50 I/O connector block and the NB1 cable with the PC-AO-2DC for your prototyping needs.

Figure 3-2 shows the pin assignments for the DAQCard-AO-2DC I/O connector. This connector is located on the edge of the DAQCard-AO-2DC and is accessible at the slot opening of your computer after the card has been properly installed.

Figure 3-3 shows the screw terminal assignments for the CB-27 accessory when connected to the DAQCard-AO-2DC using the PR27-30F ribbon cable.

Signal Connections Chapter 3

| IOUT0 | 1  | 2  | NC      |

|-------|----|----|---------|

| IOUT1 | 3  | 4  | NC      |

| NC    | 5  | 6  | NC      |

| NC    | 7  | 8  | NC      |

| NC    | 9  | 10 | DAC0OUT |

| AGND  | 11 | 12 | DAC1OUT |

| DGND  | 13 | 14 | PA0     |

| PA1   | 15 | 16 | PA2     |

| PA3   | 17 | 18 | PA4     |

| PA5   | 19 | 20 | PA6     |

| PA7   | 21 | 22 | PB0     |

| PB1   | 23 | 24 | PB2     |

| PB3   | 25 | 26 | PB4     |

| PB5   | 27 | 28 | PB6     |

| PB7   | 29 | 30 | NC      |

| NC    | 31 | 32 | NC      |

| NC    | 33 | 34 | NC      |

| NC    | 35 | 36 | NC      |

| NC    | 37 | 38 | NC      |

| NC    | 39 | 40 | NC      |

| NC    | 41 | 42 | NC      |

| NC    | 43 | 44 | NC      |

| NC    | 45 | 46 | NC      |

| NC    | 47 | 48 | DGND    |

| +5 V  | 49 | 50 | DGND    |

Figure 3-1. PC-AO-2DC I/O Connector Pin Assignments

Chapter 3 Signal Connections

Figure 3-2. DAQCard-AO-2DC I/O Connector Pin Assignments

Signal Connections Chapter 3

Figure 3-3. Screw Terminal Assignments for the CB-27 I/O Connector Block

# **Signal Connection Descriptions**

#### ♦ PC-AO-2DC

| Pin              | Signal Name | Description                                                                                                                |

|------------------|-------------|----------------------------------------------------------------------------------------------------------------------------|

| 1                | IOUT0       | Current Out 0—This signal is the current output for channel 0.                                                             |

| 2, 4–9,<br>30–48 | NC          | Not connected.                                                                                                             |

| 3                | IOUT1       | Current Out 1—This signal is the current output for channel 1.                                                             |

| 10               | DAC0OUT     | DAC0 Out—This signal is the voltage output for channel 0.                                                                  |

| 11               | AGND        | Analog Ground—This is the ground reference for analog output signals.                                                      |

| 12               | DAC1OUT     | DAC1 Out—This is the voltage output signal for channel 1.                                                                  |

| 13, 50           | DGND        | Digital Ground—This is the ground reference for digital output/input signals.                                              |

| 14–21            | PA<07>      | Port A0 through Port A7—These signals are the bidirectional digital data lines for port A. PA7 is the MSB; PA0 is the LSB. |

| 22–29            | PB<07>      | Port B0 through Port B7—These signals are the bidirectional digital data lines for port B. PB7 is the MSB; PB0 is the LSB. |

| 49               | +5 V        | +5 V—This output signal carries 1 A maximum. This has an internal resettable fuse.                                         |

Chapter 3 Signal Connections

#### **♦ DAQCard-AO-2DC**

| Pin               | Signal Name | Description                                                                                                            |

|-------------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| 1                 | DGND        | Ground—This pin is connected to the computer ground and digital ground signals.                                        |

| 2                 | + 5 V       | +5 V—This output signal carries 500 mA maximum and has an internal non-resettable wire fuse.*                          |

| 3–10              | PA<07>      | Port A0 through Port A7—These signals are bidirectional digital data lines for port A. PA7 is the MSB; PA0 is the LSB. |

| 11–18             | PB<07>      | Port B0 through Port B7—These signals are bidirectional digital data lines for port B. PB7 is the MSB; PB0 is the LSB. |

| 19, 21,<br>23, 25 | AGND        | Analog Ground—This is the ground reference for analog output signals.                                                  |

| 20                | DAC1OUT     | DAC1 Out—This is the voltage output signal for channel 1.                                                              |

| 22                | DAC0OUT     | DAC0 Out—This is the voltage output signal for channel 0.                                                              |

| 24                | IOUT1       | Current Out for Channel 1—This signal is the current output for channel 1.                                             |

| 26                | IOUT0       | Current Out for Channel 0—This signal is the current output for channel 0.                                             |

| 27                | SHIELD      | Shield—This pin is connected to the card shield and computer ground.                                                   |

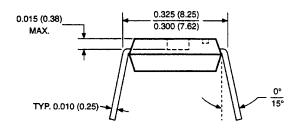

<sup>\*</sup> The DAQCard-AO-2DC fuse is a non-resettable 500 mA, 32 V, fast-acting fuse manufactured by Little Fuse (part number LIT 418.500).

You can use the CB-27 I/O connector block and the PR27-30F cable with the DAQCard-AO-2DC for your prototyping needs.

## **Analog Output Signal Connections**

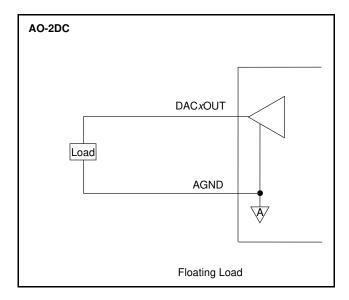

The PC-AO-2DC uses pins 1, 3, and 10–12 for analog output. The DAQCard-AO-2DC uses pins 20–26 for analog output. The DAQCard-AO-2DC provides individual grounds for each current/voltage output. You can connect each AO-2DC output channel independently for either voltage output or current output. Figure 3-4 shows how to make these signal connections.

Signal Connections Chapter 3

Figure 3-4. DAC Channel Connection as Voltage Output

#### **Voltage Output**

A floating load may be connected to your AO-2DC device at the voltage output channel.

Warning: Because the AO-2DC device is not optically or magnetically isolated from high voltages, a load with high common mode voltages may damage the AO-2DC device. National Instruments is NOT liable for any damages resulting from any such signal connections.

Your AO-2DC device may be configured in unipolar range of 0.0 to +10.0 V or in bipolar range of -5.0 to +5.0 V. The polarity is software programmable.

Maximum load current =  $\pm 1.0$  mA for 12-bit linearity

#### **Power-up Condition**

Range: Unipolar

• Output voltage: ±500 mV maximum within 100 ms of power up

#### **Current Output**

A floating load may be connected to your AO-2DC device at the current output channel. An external floating power supply is needed to complete the controlled current loop. You may control the current loop from 0 to 20 mA. The compliance for the current loop is +7.0 V to 40 VDC.

Chapter 3 Signal Connections

Warning: Because the AO-2DC device is not optically or magnetically isolated from high voltages, a load with high common mode voltages may damage the AO-2DC device. National Instruments is NOT liable for any damages resulting from any such signal connections.

Your AO-2DC device has to be configured in unipolar range of 0.0 to +10.0 V for the current outputs to function correctly. When you use an external supply, the order of the supply and load does not matter as long as you do not create a second loop through which current flows.

• External loop supply voltage: +7.0 V to +40.0 VDC

#### **Power-up Condition**

• Range: Unipolar

• Output current: 0 mA

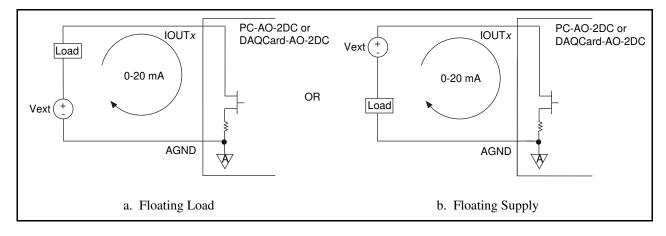

Figure 3-5 shows how to connect a DAC channel as a current output using an external loop supply.

Figure 3-5. DAC Channel Connection as Current Output, External Loop Supply

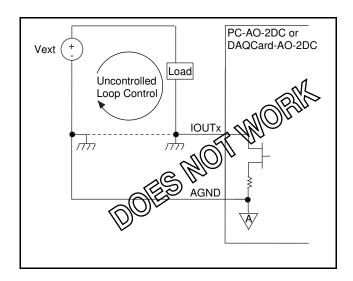

Figure 3-6 shows an example of a circuit with a second loop; this circuit does not work.

Signal Connections Chapter 3

Figure 3-6. Current Loop Connection, Load and External Supply Grounded

# **Digital I/O Signal Connections**

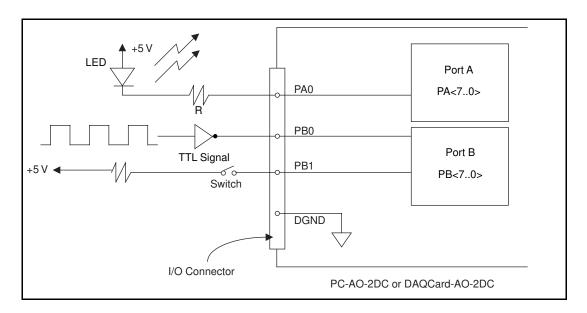

The PC-AO-2DC uses pins 13–29 and pin 50 for digital I/O; the DAQCard-AO-2DC uses pins 1–18 for digital I/O. Figure 3-7 illustrates signal connections for three typical digital I/O applications.

Figure 3-7. Digital I/O Connections

In Figure 3-7, port A is configured for digital output and port B is configured for digital input.

Chapter 3 Signal Connections

Digital input applications include receiving TTL signals and sensing external device states such as the switch in Figure 3-7. Digital output applications include sending TTL signals and driving external devices such as the LED shown in Figure 3-7.

Refer to Appendix A, Specifications, for a list of the digital I/O signal ratings.

#### **Power-up Condition**

At power up, both port A and port B of the digital I/O circuitry on the PC-AO-2DC and DAQCard-AO-2DC are configured as input ports. Also, these ports have weak internal pull ups.

# **Chapter 4 Theory of Operation**

This chapter describes the theory of operation for analog output and digital I/O using the PC-AO-2DC and DAQCard-AO-2DC.

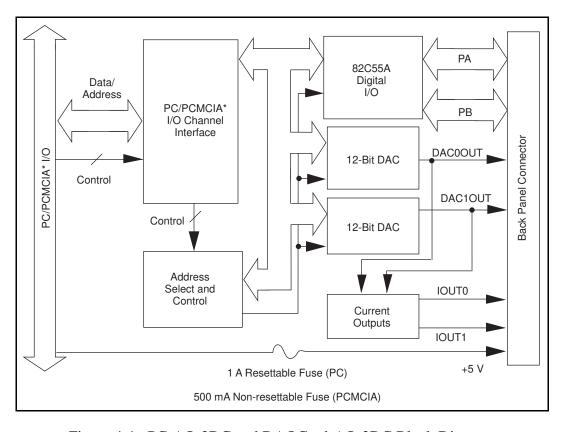

#### **Functional Overview**

The block diagram in Figure 4-1 shows a functional overview of the PC-AO-2DC and DAQCard-AO-2DC.

Figure 4-1. PC-AO-2DC and DAQCard-AO-2DC Block Diagram

\* PC I/O Channel for PC-AO-2DC; PCMCIA I/O Channel for DAQCard-AO-2DC

Theory of Operation Chapter 4

Your AO-2DC device consists of the following major components:

- I/O channel interface circuitry

- Analog output circuitry

- Digital I/O circuitry

You can execute data acquisition functions by using the analog output circuitry and the digital I/O circuitry, which are described in detail in the *Analog Output* and *Digital I/O* sections later in this chapter. The internal data and control buses interconnect the components.

#### I/O Channel Interface Circuitry

The I/O channel interface circuitry consists of address decoders, data buffers, and I/O channel interface timing control circuitry. The circuitry monitors the address lines and timing signals to generate the device select, register select, control, and read/write signals. The data buffers provide larger drive and control the direction of data transfer on the bidirectional data lines based on whether the transfer is a read or write.

#### ♦ PC-AO-2DC

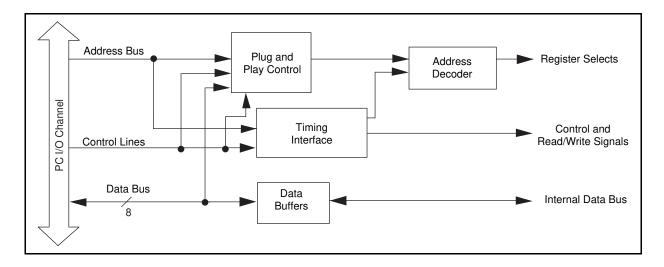

The PC I/O channel of the PC-AO-2DC consists of an address bus, a data bus, and several control and support signals. The components making up the PC I/O channel interface circuitry is shown in Figure 4-2.

Figure 4-2. PC I/O Interface Circuitry Block Diagram of PC-AO-2DC

Chapter 4 Theory of Operation

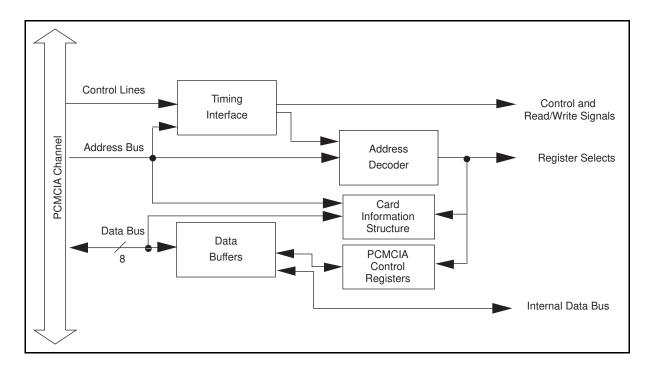

#### ♦ DAQCard-AO-2DC

The PCMCIA I/O channel of the DAQCard-AO-2DC consists of an address bus, a data bus, and several control and support signals. The components making up the PCMCIA I/O channel interface circuitry are shown in Figure 4-3.

Figure 4-3. PCMCIA I/O Interface Circuitry Block Diagram of DAQCard-AO-2DC

# **Analog Output**

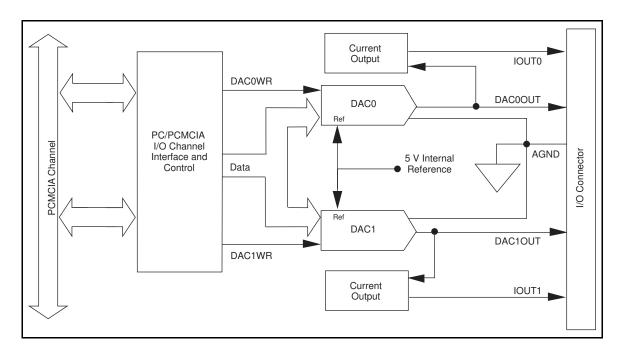

Analog outputs supported by the PC-AO-2DC and DAQCard-AO-2DC consist of two channels of voltage or current output. The theory of operation and signal connections of the analog output circuitry are described in this section.

Your AO-2DC device provides two channels of analog output through two 12-bit DACs. Each analog output channel can provide a unipolar or bipolar voltage output or current output. Figure 4-4 shows a block diagram of the analog output circuitry.

Theory of Operation Chapter 4

Figure 4-4. Analog Output Circuitry Block Diagram

Each analog output channel contains a 12-bit DAC and voltage-to-current conversion circuitry.

Each DAC channel can be software-configured for either a unipolar voltage output or a bipolar voltage output range. A unipolar output gives an output voltage range of 0.0 to +10.0 V. A bipolar output gives an output voltage range of -5.0 to +5.0 V. You can generate the desired voltage using applicable NI-DAQ function calls. For the proper connection for voltage output, refer to Chapter 3, *Signal Connections*.

Each DAC channel can be software-configured for current outputs. The voltage-to-current conversion circuitry of each analog output channel can create a 0 to 20 mA current sink using an external current loop supply of 7 to 40 V. The current sink converts the voltage from the output of DACs. For the current sink to operate properly, you must use the unipolar voltage output mode. You can use the current output with industry standard 0 to 20 mA or 4 to 20 mA current loops. You can generate the desired current loop using applicable NI-DAQ function calls. For proper connections for current outputs, refer to Chapter 3, *Signal Connections*.

Chapter 4 Theory of Operation

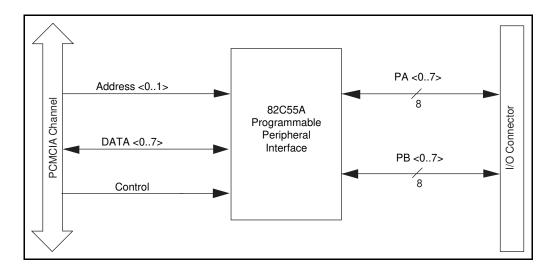

# Digital I/O

Your AO-2DC device supports 16-bit digital I/O. The 16 bits are configured as two 8-bit ports that can each be used either as an input port or an output port.

The digital I/O circuitry is designed around the 82C55A general-purpose programmable peripheral interface (PPI). Two of the ports, port A and port B, are used in the AO-2DC devices.

The pins that correspond to these ports are PA<0..7> and PB<0..7> on the AO-2DC connectors. Figure 4-5 shows a block diagram of the digital I/O circuitry. For performing and configuring digital I/O operations, use applicable NI-DAQ function calls.

Figure 4-5. Digital I/O Circuitry Block Diagram

All ports on the 82C55A are TTL-compatible. When enabled, the digital output ports are capable of sinking 2.5 mA of current and sourcing 2.5 mA of current on each digital I/O line. When the ports are not enabled, the digital I/O lines act as high-impedance inputs, which have been pulled up by weak pull-up resistors.

Theory of Operation Chapter 4

#### **Power-down Mode**

DAQCard-AO-2DC only

You can power down your DAQCard-AO-2DC by using the power-down utility provided with your NI-DAQ software. This utility will put your DAQCard-AO-2DC in a low-power consumption mode. The effects of power-down mode are as follows:

- The analog output values will not be maintained. For example, if you have set up your voltage output channel to unipolar mode and you are outputting +9.000 V, then after power-down mode the output levels will fall to an unknown level.

- The digital I/O will not be functional.

- After you bring your DAQCard-AO-2DC back from power-down mode to power-up mode, you are required to set up your analog outputs again.

If you are using a PC, bring your DAQCard-AO-2DC to power-down mode by typing: daqpower D and to power-up your DAQCard-AO-2DC again, type: daqpower U.

If you are using a Mac, refer to your NI-DAQ for Macintosh documentation to use the power-down utilities for PCMCIA cards.

Refer to the configuration utility online documentation that is shipped with your PCMCIA card for more information on power-down features.

# **Appendix A Specifications**

This appendix lists the specifications of the PC-AO-2DC and DAQCard-AO-2DC. These specifications are typical at  $25^{\circ}$  C and 50% relative humidity unless otherwise stated.

## **Analog Output**

## **Output Characteristics**

| Number of channels | Two voltage and two current |

|--------------------|-----------------------------|

| Resolution         | 12 bits                     |

| Type of DAC        | .Double buffered            |

| Data transfers     | Programmed I/O              |

## **Transfer Characteristics**

| Relative accuracy (INL) of the DAC | ±0.5 LSB max <sup>1</sup>   |

|------------------------------------|-----------------------------|

| DNL                                |                             |

| Monotonicity                       | Guaranteed over temperature |

## **Voltage Output**

| Ranges            | 0 to 10 VDC, $\pm 5$ V, software selectable |

|-------------------|---------------------------------------------|

| Output coupling   | DC                                          |

| Output impedance  | 0.5 Ω                                       |

| Current drive     |                                             |

| Absolute accuracy |                                             |

| Protection        |                                             |

| Power-on state    |                                             |

## **Current Output**

| Range                    | 0 to 20 mA |

|--------------------------|------------|

| Type                     |            |

| Output impedance         |            |

| Excitation voltage range |            |

| Absolute accuracy        |            |

| Protection               |            |

| Power-on state           |            |

<sup>&</sup>lt;sup>1</sup> The relative accuracy for the software corrected DAC is  $\pm 1.53$  LSB max.

This limit is for the  $\pm 5$  V range. For unipolar 0–10 VDC range, the current drive is  $\pm 1$  mA max.

<sup>&</sup>lt;sup>3</sup> The FSR for either unipolar or bipolar mode is 10 V.

<sup>&</sup>lt;sup>4</sup> The output level is unknown in the first 100 ms after power up.

Specifications Appendix A

## **Dynamic Characteristics**

#### **Stability**

## **Digital I/O**

Digital logic levels .....

| Level                                                         | Min             | Max            |

|---------------------------------------------------------------|-----------------|----------------|

| Input low voltage<br>Input high voltage<br>Input leak current | -0.3 V<br>2.2 V | 0.8 V<br>5.0 V |

| $(0 \le V_{\text{in}} \le 5 \text{ V})$                       | -1.0 μA         | 1 μΑ           |

| Output low voltage<br>(Iout = 2.5 mA)<br>Output high voltage  | 0.0 V           | 0.4 V          |

| (Iout = 2.5  mA)                                              | 3.7 V           | 5.0 V          |

## **Bus Interface**

Type ...... Slave

## **Power Requirements**

♦ PC-AO-2DC

| +5 VDC (±5%)  | 350 mA max |

|---------------|------------|

| +12 VDC (±5%) | 30 mA max  |

| -12 VDC (±5%) | 30 mA max  |

These limits on the transfer rates are set by the digital I/O circuitry on the card. Actual transfer rates may be lower than these limits, depending on the type of computer, CPU speed, operating system, and the software used.

Appendix A Specifications

## ♦ DAQCard-AO-2DC

Note: These specifications do not include power consumed by devices connected to the fused +5 V supply pin on the I/O connector.

## **Physical**

#### ♦ PC-AO-2DC

| Dimensions    | 11.3 by 9.9 cm (4.45 by 3.90 in.) |

|---------------|-----------------------------------|

| I/O connector | 50-pin male                       |

#### ♦ DAQCard-AO-2DC

| PCMCIA card type | Type II                                    |

|------------------|--------------------------------------------|

| I/O connector    | 25-pin female PCMCIA I/O connector on card |

## **Environment**

| Operating         | 0° to 50° C             |

|-------------------|-------------------------|

| Temperature       |                         |

| Relative humidity | 5% to 90% noncondensing |

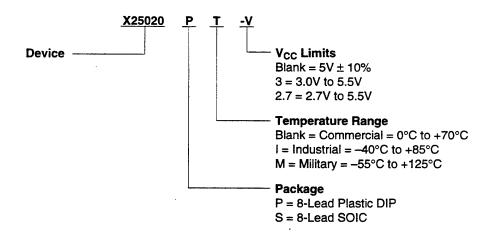

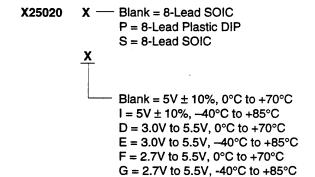

## Appendix B X25020 Data Sheet\*

This appendix contains a manufacturer data sheet for the X25020 SPI serial EEPROM (Xicor). This EEPROM is used on both the PC-AO-2DC and the DAQCard-AO-2DC.

<sup>\*</sup> Copyright © Xicor. 1995. Reprinted with permission of copyright owner. All rights reserved. Xicor, Inc. 1995 Data Book.

X25020 Data Sheet Appendix B

2K X25020 256 x 8 Bit

## SPI Serial E<sup>2</sup>PROM With BLOCK LOCK<sup>TM</sup> PROTECTION

#### **FEATURES**

- 1MHz Clock Rate

- 256 X 8 Bits

- -4 Byte Page Mode

- Low Power CMOS

- -150µA Standby Current

- -2mA Active Write Current

- 2.7V To 5.5V Power Supply

- Block Lock Protection

- -Protect 1/4, 1/2 or all of E<sup>2</sup>PROM Array

- Built-in Inadvertent Write Protection

- -Power-Up/Power-Down protection circuitry

- -Write Latch

- -Write Protect Pin

- Self-Timed Write Cycle

- -5mS Write Cycle Time (Typical)

- High Reliability

- -Endurance: 100,000 cycles per byte

- -Data Retention: 100 Years

- -ESD protection: 2000V on all pins

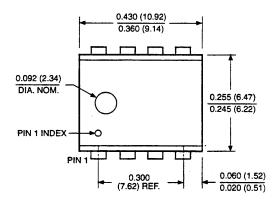

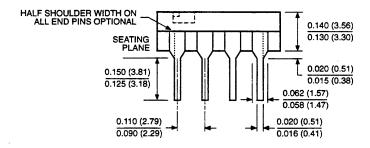

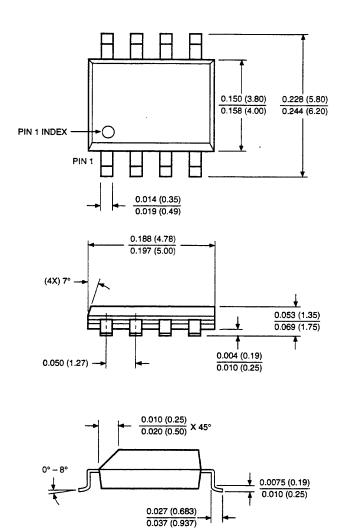

- 8-Pin Mini-DIP Package

- 8-Pin SOIC Package

#### DESCRIPTION

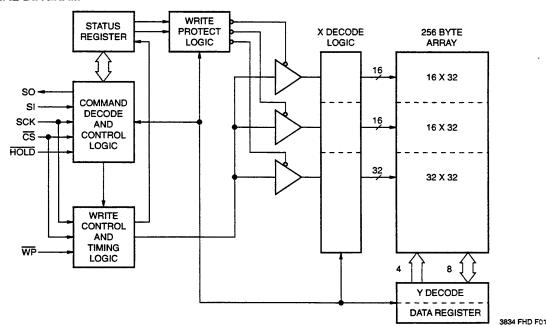

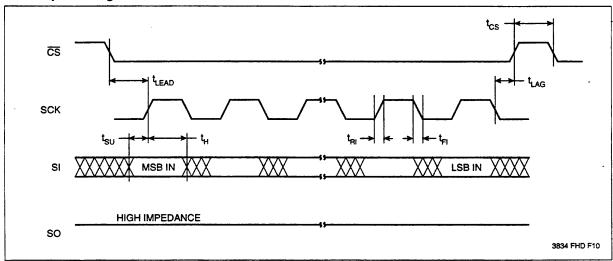

The X25020 is a CMOS 2048 bit serial E<sup>2</sup>PROM, internally organized as 256 x 8. The X25020 features a serial interface and software protocol allowing operation on a simple three wire bus. The bus signals are a clock input (SCK) plus separate data in (SI) and data out (SO) lines. Access to the device is controlled through a chip select (CS) input, allowing any number of devices to share the same bus.

The X25020 also features two additional inputs that provide the end user with added flexibility. By asserting the HOLD input, the X25020 will ignore transitions on its inputs, thus allowing the host to service higher priority interrupts. The WP input can be used as a hardwire input to the X25020 disabling all write attempts; thus providing a mechanism for limiting end user capability of altering the memory.

The X25020 utilizes Xicor's proprietary Direct Write<sup>™</sup> cell, providing a minimum endurance of 100,000 cycles per byte and a minimum data retention of 100 years.

#### **FUNCTIONAL DIAGRAM**

Direct Write<sup>™</sup> and Block Łock<sup>™</sup> Protection is a trademark of Xicor, Inc.

©Xicor, 1994 Patents Pending 3834-1.1 1/5/95 T0/C11/D0 TD Characteristics subject to change without notice

1

Appendix B X25020 Data Sheet

#### X25020

#### **PIN DESCRIPTIONS**

#### Serial Output (SO)

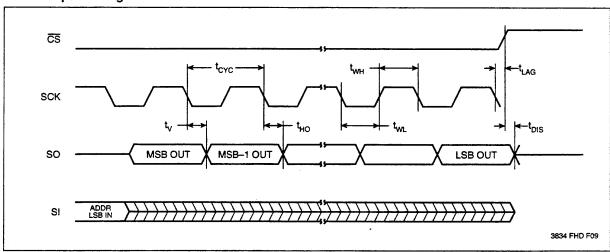

SO is a push-pull serial data output pin. During a read cycle, data is shifted out on this pin. Data is clocked out by the falling edge of the serial clock.

#### Serial Input (SI)

SI is the serial data input pin. All opcodes, byte addresses, and data to be written to the memory are input on this pin. Data is latched by the rising edge of the serial clock.

#### Serial Clock (SCK)

The Serial Clock controls the serial bus timing for data input and output. Opcodes, addresses, or data present on the SI pin are latched on the rising edge of the clock input, while data on the SO pin change after the falling edge of the clock input.

#### Chip Select (CS)

When  $\overline{\text{CS}}$  is high, the X25020 is deselected and the SO output pin is at high impedance and unless an internal write operation is underway the X25020 will be in the standby power mode.  $\overline{\text{CS}}$  low enables the X25020, placing it in the active power mode. It should be noted that after power-on, a high to low transition on  $\overline{\text{CS}}$  is required prior to the start of any operation.

#### Write Protect (WP)

When WP is low, nonvolatile writes to the X25020 are disabled, but the part otherwise functions normally. When WP is held high, all functions, including nonvolatile writes operate normally. WP going low while  $\overline{CS}$  is still low will interrupt a write to the X25020. If the internal write cycle has already been initiated, WP going low will have no affect on write.

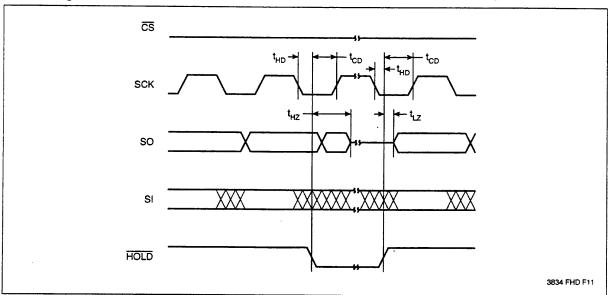

#### Hold (HOLD)

HOLD is used in conjunction with the  $\overline{CS}$  pin to select the device. Once the part is selected and a serial sequence is underway, HOLD may be used to pause the serial communication with the controller without resetting the serial sequence. To pause, HOLD must be brought low while SCK is Low. To resume communication, HOLD is brought high, again while SCK is low. If the pause feature is not used, HOLD should be held high at all times.

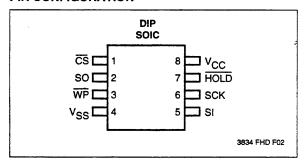

#### **PIN CONFIGURATION**

#### **PIN NAMES**

| Symbol | Description         |

|--------|---------------------|

| CS     | Chip Select Input   |

| SO     | Serial Output       |

| SI     | Serial Input        |

| SCK    | Serial Clock Input  |

| WP     | Write Protect Input |

| Vss    | Ground              |

| Vcc    | Supply Voltage      |

| HOLD   | Hold Input          |

3834 PGM T01

X25020 Data Sheet Appendix B

#### X25020

#### PRINCIPLES OF OPERATION

The X25020 is a 256 x 8 E<sup>2</sup>PROM designed to interface directly with the synchronous serial peripheral interface (SPI) of the popular 6805 and 68HC11 microcontroller families.

The X25020 contains an 8-bit instruction register. It is accessed via the SI input, with data being clocked in on the rising SCK.  $\overline{CS}$  must be low and the HOLD and WP inputs must be high during the entire operation.

Table 1 contains a list of the instructions and their operation codes. All instructions, addresses and data are transferred MSB first.

Data input is sampled on the first rising edge of SCK after  $\overline{\text{CS}}$  goes low. SCK is static, allowing the user to stop the clock and then resume operations. If the clock line is shared with other peripheral devices on the SPI bus, the user can assert the HOLD input to place the X25020 into a "PAUSE" condition. After releasing HOLD, the X25020 will resume operation from the point when HOLD was first asserted.

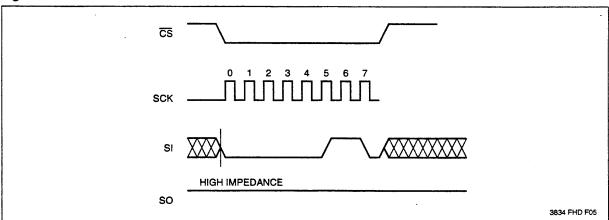

#### Write Enable (WREN) and Write Disable (WRDI)

The X25020 contains a write enable latch. This latch must be SET before a write operation will be completed internally. The WREN instruction will set the latch and the WRDI instruction will reset the latch. This latch is automatically reset upon a power-on condition and after the completion of a byte, page, or status register write cycle. The latch is also reset if WP is brought low.

#### Read Status Register (RDSR)

The RDSR instruction provides access to the status register. The status register may be read at any time, even during a write cycle. The status register is formatted as follows:

| 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---|---|---|---|-----|-----|-----|-----|

| Χ | Х | Χ | Х | BL1 | BL0 | WEL | WIP |

3834 PGM TO

The Write-In-Process (WIP) bit indicates whether the X25020 is busy with a write operation. When set to a "1" a write is in progress, when set to a "0" no write is in progress. During a write all other bits are set to "1". This bit is read only.

The Write Enable Latch (WEL) bit indicates the status of the write enable latch. When set to a "1" the latch is set, when set to a "0" the latch is reset. This bit is read only.

The **Block Lock (BL0 and BL1)** bits indicate the extent of protection employed. These bits are set by the user issuing the WRSR instruction.

#### Write Status Register (WRSR)

The write status register instruction allows the user to select one of four levels of protection. The X25020 is divided into four 512-bit segments. One, two, or all four of the segments may be protected. That is, the user may read the segments but will be unable to alter (write) data within the selected segments. The partitioning is controlled as illustrated below.

| Status Re | gister Bits | Array Addresses |

|-----------|-------------|-----------------|

| BL1       | BL0         | Locked          |

| 0         | 0           | None            |

| 0         | 1           | CO-\$FF (1/4)   |

| 1         | 0           | \$80-\$FF (1/2) |

| 1         | 1           | \$00-\$FF (all) |

Table 1. Instruction Set

3834 PGM T03

| Instruction Name | Instruction Format* | Operation                                                               |

|------------------|---------------------|-------------------------------------------------------------------------|

| WREN             | 0000 0110           | Set the Write Enable Latch (Enable Write Operations)                    |

| WRDI             | 0000 0100           | Reset the Write Enable Latch (Disable Write Operations)                 |

| RDSR             | 0000 0101           | Read Status Register                                                    |

| WRSR             | 0000 0001           | Write Status Register (Block Lock Bits)                                 |

| READ             | 0000 0011           | Read Data from Memory Array beginning at selected address               |

| WRITE            | 0000 0010           | Write Data to Memory Array beginning at Selected Address (1 to 4 Bytes) |

\*Instructions are shown MSB in leftmost position. Instructions are transferred MSB first.

3834 PGM T04

B-4

#### **DEVICE OPERATION**

#### **Clock and Data Timing**

Data input on the SI line is sampled and latched on the rising edge of SCK. Data is output on the SO line by the falling edge of SCK.

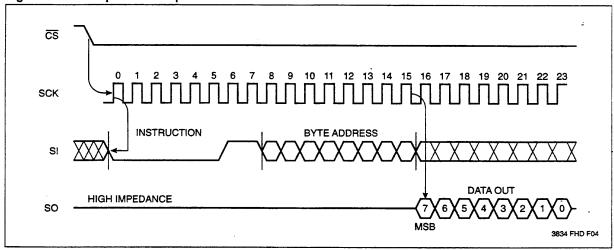

#### **Read Sequence**

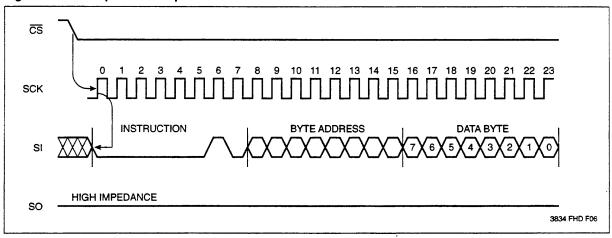

The  $\overline{\text{CS}}$  line is first pulled low to select the device. The 8 bit read opcode is transmitted to the X25020, followed by the 8 bit byte address. After the read opcode and byte address are sent, the data stored in the memory at the selected address is shifted out on the SO line. The data stored in memory at the next address can be read sequentially by continuing to provide clock pulses. The byte address is automatically incremented to the next higher address after each byte of data is shifted out. When the highest address is reached (\$FF) the address counter rolls over to address \$00 allowing the read cycle to be continued indefinitely. The read operation is terminated by taking  $\overline{\text{CS}}$  high. Refer to the read operation sequence illustrated in Figure 1.

#### Write Sequence

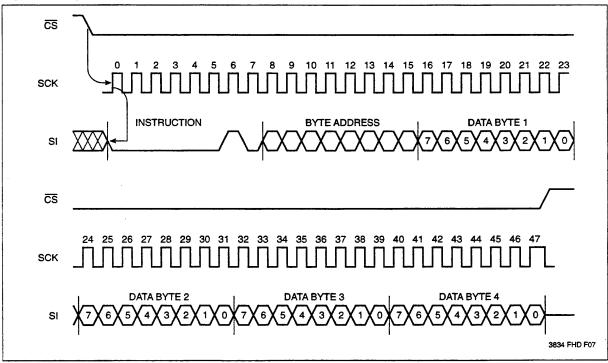

Prior to any attempt to write data into the X25020 the write enable latch must first be set by issuing the WREN instruction. (See Fig. 2)  $\overline{\text{CS}}$  is first taken low, then the instruction is clocked into the X25020. After all eight bits of the instruction are transmitted,  $\overline{\text{CS}}$  must then be taken high. If the user continues the write operation without taking  $\overline{\text{CS}}$  high after issuing the WREN instruction the write operation will be ignored.

Once the write enable latch is set, the user may proceed by issuing the write instruction, followed by the address and then the data to be written. This is minimally a twenty-four clock operation.  $\overline{CS}$  must go low and remain low for the duration of the operation. The host may continue to write up to four bytes of data to the X25020. The only restriction is the four bytes must reside on the same page. A page address begins with address XXXX XX00 and ends with XXXX XX11. If the byte address counter reaches XXXX XX11 and the clock continues the counter will roll back to the first address of the page and overwrite any data that may have been written.

For the write operation (byte or page write) to be completed,  $\overline{CS}$  can only be brought high after the twenty-fourth, thirty-second, fortieth or forty-eighth clock. If it is brought high at any other time the write operation will not be completed. Refer to Figure 4 below for a detailed illustration of the page write sequence and time frames in which  $\overline{CS}$  going high are valid.

While the write is in progress the status register may be read to check the WIP bit. During this time the WIP bit will be high and all other bits in the status register will be high.

#### **Hold Operation**

The HOLD input should be high (at  $V_{IH}$ ) under normal operation. If a data transfer is to be interrupted HOLD can be pulled low to suspend the transfer until it can be resumed. The only restriction is the SCK input must be low when HOLD is first pulled low and SCK must also be low when HOLD is released.

X25020 Data Sheet Appendix B

## X25020

The HOLD input may be tied high either directly to  $V_{CC}$  or tied to  $V_{CC}$  through a resistor.

#### **Operational Notes**

The X25020 powers-on in the following state:

- The device is in the low power standby state. .

- A high to low transition on  $\overline{\text{CS}}$  is required to enter an active state and receive an instruction.

- SO pin is high impedance.

- The write enable latch is reset.

#### **Data Protection**

The following circuitry has been included to prevent inadvertent writes:

- The write enable latch is reset upon power-up.

- A write enable instruction must be issued to set the write enable latch.

- CS must come high at the proper clock count in order to start a write cycle.

The write enable latch is reset when WP is brought low.

Figure 1. Read Operation Sequence

Figure 2. Write Enable Latch

X25020 Data Sheet

## X25020

Figure 3. Write Operation Sequence

Figure 4. Page Write Operation Sequence

X25020 Data Sheet Appendix B

## X25020

#### **ABSOLUTE MAXIMUM RATINGS\***

| Temperature Under Bias               | 65°C to +135°C      |

|--------------------------------------|---------------------|

| Storage Temperature                  | 65°C to +150°C      |

| Voltage on any Pin with Respect to 0 | Ground -1.0V to +7V |

| D.C. Output Current                  | 5mA                 |

| Lead Temperature                     |                     |

| (Soldering 10 Seconds)               | 300°C               |

#### \*COMMENT

Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and the functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### RECOMMENDED OPERATING CONDITIONS

| Temp       | Min.  | Max.        |

|------------|-------|-------------|

| Commercial | 0°C   | 70°C        |

| Industrial | -40°C | +85°C       |

| Military   | –55°C | +125°C      |

|            |       | 2004 5014 7 |

| Supply Voltage | Limits       |

|----------------|--------------|

| X25020         | 5V ± 10%     |

| X25020-3       | 3V to 5.5V   |

| X25020 - 2.7   | 2.7V to 5.5V |

| <del></del>    | <del></del>  |

3834 PGM T06

#### D.C. OPERATING CHARACTERISTICS (Over the recommended operating conditions unless otherwise specified.)

|                                |                                          | Limits                |                       | Limits |                                                                     | Limits |  | Limits |  | Limits |  |  |  |

|--------------------------------|------------------------------------------|-----------------------|-----------------------|--------|---------------------------------------------------------------------|--------|--|--------|--|--------|--|--|--|

| Symbol                         | Parameter                                | Min.                  | Max.                  | Units  | Test Conditions                                                     |        |  |        |  |        |  |  |  |

| lcc                            | V <sub>CC</sub> Supply Current (Active)  |                       | 3                     | mA     | SCK = $V_{CC} \times 0.1/V_{CC} \times 0.9$ @ 1MHz,<br>SO = OPEN    |        |  |        |  |        |  |  |  |

| I <sub>SB</sub>                | V <sub>CC</sub> Supply Current (Standby) |                       | 150                   | μА     | $\overline{CS} = V_{CC}$ , $V_{IN} = Gnd \text{ or } V_{CC} - 0.3V$ |        |  |        |  |        |  |  |  |

| ILI                            | Input Leakage Current                    |                       | 10                    | μΑ     | V <sub>IN</sub> = GND to V <sub>CC</sub>                            |        |  |        |  |        |  |  |  |

| ILO                            | Output Leakage Current                   |                       | 10                    | μA     | V <sub>OUT</sub> = GND to V <sub>CC</sub>                           |        |  |        |  |        |  |  |  |

| V <sub>IL</sub> (1)            | Input Low Voltage                        | -1.0                  | V <sub>CC</sub> • 0.3 | ٧      |                                                                     |        |  |        |  |        |  |  |  |