#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

## **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

CB-68LP

# DAQ Analog Output Series

NI 6738/6739 User Manual

## Worldwide Technical Support and Product Information $\mathtt{ni.com}$

#### Worldwide Offices

Visit ni.com/niglobal to access the branch office websites, which provide up-to-date contact information, support phone numbers, email addresses, and current events.

### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

For further support information, refer to the *Services and Resources* appendix. To comment on National Instruments documentation, refer to the National Instruments website at ni.com/info and enter the Info Code feedback.

© 2015–2017 National Instruments. All rights reserved.

## Legal Information

#### Limited Warranty

This document is provided 'as is' and is subject to being changed, without notice, in future editions. For the latest version, refer to ni.com/manuals. NI reviews this document carefully for technical accuracy; however, NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS.

NI warrants that its hardware products will be free of defects in materials and workmanship that cause the product to fail to substantially conform to the applicable NI published specifications for one (1) year from the date of invoice.

For a period of ninety (90) days from the date of invoice, NI warrants that (i) its software products will perform substantially in accordance with the applicable documentation provided with the software and (ii) the software media will be free from defects in materials and workmanship.

If NI receives notice of a defect or non-conformance during the applicable warranty period, NI will, in its discretion: (i) repair or replace the affected product, or (ii) refund the fees paid for the affected product. Repaired or replaced Hardware will be warranted for the remainder of the original warranty period or ninety (90) days, whichever is longer. If NI elects to repair or replace the product, NI may use new or refurbished parts or products that are equivalent to new in performance and reliability and are at least functionally equivalent to the original part or product.

You must obtain an RMA number from NI before returning any product to NI. NI reserves the right to charge a fee for examining and testing Hardware not covered by the Limited Warranty.

This Limited Warranty does not apply if the defect of the product resulted from improper or inadequate maintenance, installation, repair, or calibration (performed by a party other than NI); unauthorized modification; improper environment; use of an improper hardware or software key; improper use or operation outside of the specification for the product; improper voltages; accident, abuse, or neglect; or a hazard such as lightning, flood, or other act of nature.

THE REMEDIES SET FORTH ABOVE ARE EXCLUSIVE AND THE CUSTOMER'S SOLE REMEDIES, AND SHALL APPLY EVEN IF SUCH REMEDIES FAIL OF THEIR ESSENTIAL PURPOSE.

EXCEPT AS EXPRESSLY SET FORTH HEREIN, PRODUCTS ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND AND NI DISCLAIMS ALL WARRANTIES, EXPRESSED OR IMPLIED, WITH RESPECT TO THE PRODUCTS, INCLUDING ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, TITLE OR NON-INFRINGEMENT, AND ANY WARRANTIES THAT MAY ARISE FROM USAGE OF TRADE OR COURSE OF DEALING. NI DOES NOT WARRANT, GUARANTEE, OR MAKE ANY REPRESENTATIONS REGARDING THE USE OF OR THE RESULTS OF THE USE OF THE PRODUCTS IN TERMS OF CORRECTNESS, ACCURACY, RELIABILITY, OR OTHERWISE. NI DOES NOT WARRANT THAT THE OPERATION OF THE PRODUCTS WILL BE UNINTERRUPTED OR ERROR FREE.

In the event that you and NI have a separate signed written agreement with warranty terms covering the products, then the warranty terms in the separate agreement shall control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### End-User License Agreements and Third-Party Legal Notices

You can find end-user license agreements (EULAs) and third-party legal notices in the following locations:

- Notices are located in the <National Instruments>\\_Legal Information and <National Instruments> directories.

- EULAs are located in the <National Instruments>\Shared\MDF\Legal\license directory.

- Review <National Instruments>\\_Legal Information.txt for information on including legal information in installers built with NI products.

#### U.S. Government Restricted Rights

If you are an agency, department, or other entity of the United States Government ("Government"), the use, duplication, reproduction, release, modification, disclosure or transfer of the technical data included in this manual is governed by the Restricted Rights provisions under Federal Acquisition Regulation S2.227-14 for civilian agencies and Defense Federal Acquisition Regulation Supplement Section 252.227-7014 and 252.227-7015 for military agencies.

#### **Trademarks**

Refer to the NI Trademarks and Logo Guidelines at ni.com/trademarks for more information on National Instruments trademarks.

ARM, Keil, and µVision are trademarks or registered of ARM Ltd or its subsidiaries.

LEGO, the LEGO logo, WEDO, and MINDSTORMS are trademarks of the LEGO Group.

TETRIX by Pitsco is a trademark of Pitsco, Inc.

FIELDBUS FOUNDATION™ and FOUNDATION™ are trademarks of the Fieldbus Foundation.

EtherCAT® is a registered trademark of and licensed by Beckhoff Automation GmbH.

CANopen® is a registered Community Trademark of CAN in Automation e.V.

DeviceNet<sup>™</sup> and EtherNet/IP<sup>™</sup> are trademarks of ODVA.

Go!, SensorDAQ, and Vernier are registered trademarks of Vernier Software & Technology. Vernier Software & Technology and vernier.com are trademarks or trade dress.

Xilinx is the registered trademark of Xilinx, Inc.

Taptite and Trilobular are registered trademarks of Research Engineering & Manufacturing Inc.

FireWire® is the registered trademark of Apple Inc.

Linux® is the registered trademark of Linus Torvalds in the U.S. and other countries.

Handle Graphics<sup>®</sup>, MATLAB<sup>®</sup>, Real-Time Workshop<sup>®</sup>, Simulink<sup>®</sup>, Stateflow<sup>®</sup>, and xPC TargetBox<sup>®</sup> are registered trademarks, and TargetBox<sup>™</sup> and Target Language Compiler<sup>™</sup> are trademarks of The MathWorks, Inc.

Tektronix®, Tek, and Tektronix, Enabling Technology are registered trademarks of Tektronix, Inc.

The Bluetooth® word mark is a registered trademark owned by the Bluetooth SIG, Inc.

The ExpressCard™ word mark and logos are owned by PCMCIA and any use of such marks by National Instruments is under license

The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft Corporation in the United States and other countries.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents

For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.

#### Export Compliance Information

Refer to the Export Compliance Information at ni.com/legal/export-compliance for the National Instruments global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

YOU ARE ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY AND RELIABILITY OF THE PRODUCTS WHENEVER THE PRODUCTS ARE INCORPORATED IN YOUR SYSTEM OR APPLICATION, INCLUDING THE APPROPRIATE DESIGN, PROCESS, AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

PRODUCTS ARE NOT DESIGNED, MANUFACTURED, OR TESTED FOR USE IN LIFE OR SAFETY CRITICAL SYSTEMS, HAZARDOUS ENVIRONMENTS OR ANY OTHER ENVIRONMENTS REQUIRING FAIL-SAFE PERFORMANCE, INCLUDING IN THE OPERATION OF NUCLEAR FACILITIES; AIRCRAFT NAVIGATION; AIR TRAFFIC CONTROL SYSTEMS; LIFE SAVING OR LIFE SUSTAINING SYSTEMS OR SUCH OTHER MEDICAL DEVICES; OR ANY OTHER APPLICATION IN WHICH THE FAILURE OF THE PRODUCT OR SERVICE COULD LEAD TO DEATH, PERSONAL INJURY, SEVERE PROPERTY DAMAGE OR ENVIRONMENTAL HARM (COLLECTIVELY, "HIGH-RISK USES"). FURTHER, PRUDENT STEPS MUST BE TAKEN TO PROTECT AGAINST FAILURES, INCLUDING PROVIDING BACK-UP AND SHUT-DOWN MECHANISMS. NI EXPRESSLY DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY OF FITNESS OF THE PRODUCTS OR SERVICES FOR HIGH-RISK USES.

## Compliance

## **Electromagnetic Compatibility Information**

This product was tested and complies with the regulatory requirements and limits for electromagnetic compatibility (EMC) stated in the product specifications. These requirements and limits provide reasonable protection against harmful interference when the product is operated in the intended operational electromagnetic environment.

This product is intended for use in industrial locations. However, harmful interference may occur in some installations, when the product is connected to a peripheral device or test object, or if the product is used in residential or commercial areas. To minimize interference with radio and television reception and prevent unacceptable performance degradation, install and use this product in strict accordance with the instructions in the product documentation.

Furthermore, any modifications to the product not expressly approved by National Instruments could void your authority to operate it under your local regulatory rules.

**Notices** To ensure the specified EMC performance, operate this product only with shielded cables and accessories.

To ensure the specified EMC performance, the length of all I/O cables must be no longer than 30 m (100 ft).

## Contents

Chapter 1 **Getting Started** Safety Guidelines 1-1 Safety Guidelines for Hazardous Voltages......1-1 Installation 1-3 Device Pinouts 1-4 Device Specifications 1-4 Chapter 2 **DAQ System Overview** DAQ Hardware 2-1 Cables and Accessories 2-3 Custom Cabling and Connectivity......2-4 Programming Devices in Software......2-5 Chapter 3 Connector Information I/O Connector Pinouts 3-1 PCIe/PXIe-6738 Pinout 3-1 PXIe-6739 Pinout 3-3 RTSI Connector Pinout 3-5

## Chapter 4 **Analog Output**

| Analog Output Data Generation Methods                     | 4-2 |

|-----------------------------------------------------------|-----|

| Software-Timed Generations                                | 4-2 |

| Hardware-Timed Generations                                | 4-2 |

| Connecting Analog Output Signals                          | 4-3 |

| Analog Output Triggering                                  | 4-4 |

| Analog Output Timing Signals                              | 4-4 |

| AO Start Trigger Signal                                   | 4-5 |

| Retriggerable Analog Output                               |     |

| Using a Digital Source                                    | 4-5 |

| Routing AO Start Trigger Signal to an Output Terminal     |     |

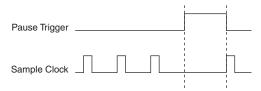

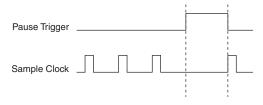

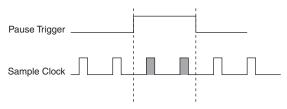

| AO Pause Trigger Signal                                   | 4-6 |

| Using a Digital Source                                    |     |

| Routing AO Pause Trigger Signal to an Output Terminal     | 4-7 |

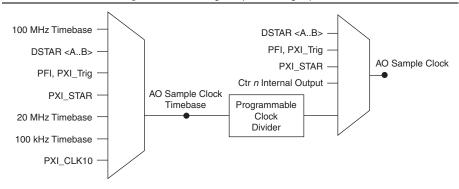

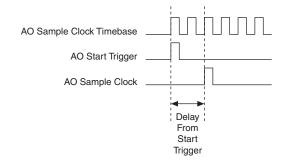

| AO Sample Clock Signal                                    |     |

| Using an Internal Source                                  | 4-7 |

| Using an External Source                                  | 4-8 |

| Routing AO Sample Clock Signal to an Output Terminal      | 4-8 |

| Other Timing Requirements                                 | 4-8 |

| AO Sample Clock Timebase Signal                           |     |

| Getting Started with AO Applications in Software          | 4-9 |

| Chantar F                                                 |     |

| Chapter 5                                                 |     |

| Digital I/O                                               |     |

| Digital Input Data Acquisition Methods                    |     |

| Software-Timed Acquisitions                               | 5-2 |

| Hardware-Timed Acquisitions                               | 5-2 |

| Digital Input Triggering                                  | 5-3 |

| Digital Waveform Acquisition                              | 5-4 |

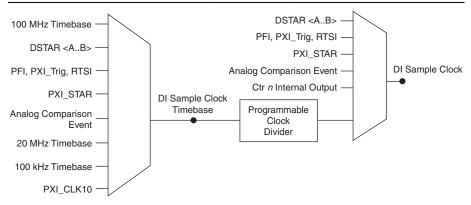

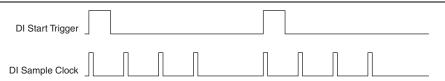

| DI Sample Clock Signal                                    | 5-4 |

| Using an Internal Source                                  | 5-5 |

| Using an External Source                                  | 5-5 |

| Routing DI Sample Clock to an Output Terminal             | 5-5 |

| Other Timing Requirements                                 | 5-5 |

| DI Sample Clock Timebase Signal                           | 5-6 |

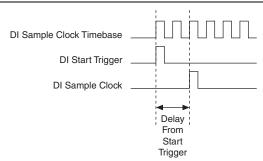

| DI Start Trigger Signal                                   |     |

| Retriggerable DI                                          | 5-7 |

| Using a Digital Source                                    |     |

| Routing DI Start Trigger to an Output Terminal            |     |

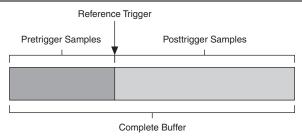

| DI Reference Trigger Signal                               |     |

| Using a Digital Source                                    |     |

| Routing DI Reference Trigger Signal to an Output Terminal | 5-9 |

|                                                           |     |

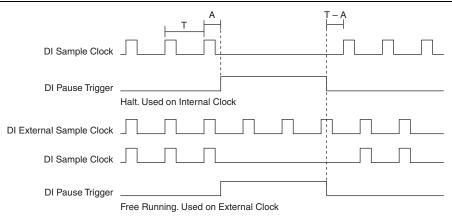

| DI Pause Trigger Signal                               | 5-9  |

|-------------------------------------------------------|------|

| Using a Digital Source                                | 5-10 |

| Routing DI Pause Trigger Signal to an Output Terminal | 5-10 |

| Digital Output Data Generation Methods                |      |

| Software-Timed Generations                            | 5-1  |

| Hardware-Timed Generations                            | 5-1  |

| Digital Output Triggering                             | 5-12 |

| Digital Waveform Generation                           | 5-12 |

| DO Sample Clock Signal                                | 5-13 |

| Using an Internal Source                              | 5-13 |

| Using an External Source                              | 5-13 |

| Routing DO Sample Clock to an Output Terminal         | 5-14 |

| Other Timing Requirements                             | 5-14 |

| DO Sample Clock Timebase Signal                       | 5-14 |

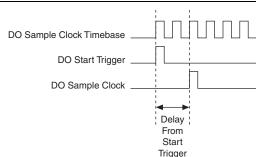

| DO Start Trigger Signal                               | 5-15 |

| Retriggerable DO                                      | 5-1: |

| Using a Digital Source                                | 5-15 |

| Routing DO Start Trigger Signal to an Output Terminal | 5-16 |

| DO Pause Trigger Signal                               | 5-10 |

| Using a Digital Source                                |      |

| Routing DO Pause Trigger Signal to an Output Terminal |      |

| I/O Protection                                        |      |

| Programmable Power-Up States                          |      |

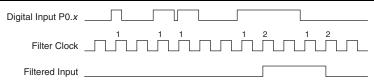

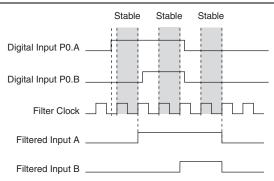

| DI Change Detection                                   |      |

| DI Change Detection Applications                      |      |

| Digital Filtering                                     |      |

| Watchdog Timer                                        |      |

| Connecting Digital I/O Signals                        |      |

| Getting Started with DIO Applications in Software     | 5-24 |

| Chapter 6                                             |      |

| Counters                                              |      |

| Counter Timing Engine                                 | 6-1  |

| Counter Input Applications                            | 6-2  |

| Counting Edges                                        |      |

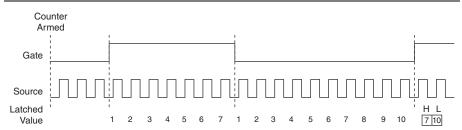

| Single Point (On-Demand) Edge Counting                |      |

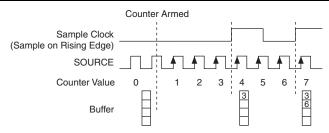

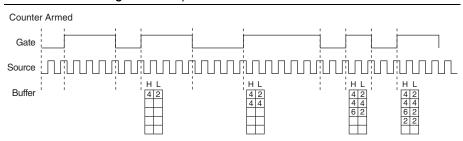

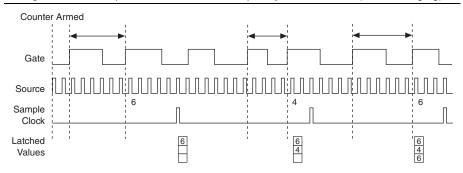

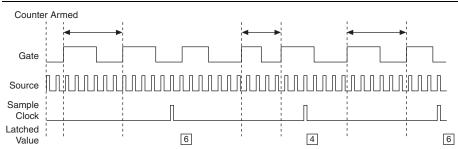

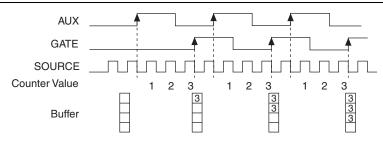

| Buffered (Sample Clock) Edge Counting                 |      |

| Controlling the Direction of Counting                 |      |

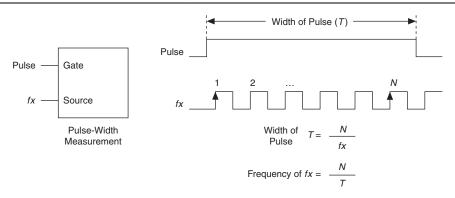

| Pulse-Width Measurement                               |      |

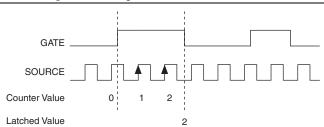

| Single Pulse-Width Measurement                        |      |

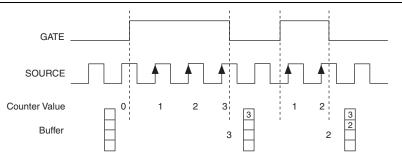

| Implicit Buffered Pulse-Width Measurement             |      |

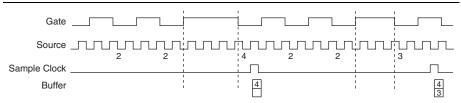

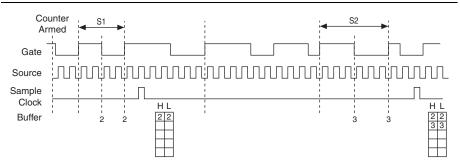

| Sample Clocked Buffered Pulse-Width Measurement       |      |

| Hardware-Timed Single Point Pulse-Width Measurement   |      |

|                                                       |      |

| Pulse Measurement                                             | 6-7  |

|---------------------------------------------------------------|------|

| Single Pulse Measurement                                      | 6-7  |

| Implicit Buffered Pulse Measurement                           | 6-7  |

| Sample Clocked Buffered Pulse Measurement                     | 6-8  |

| Hardware-Timed Single Point Pulse Measurement                 | 6-8  |

| Pulse versus Semi-Period Measurements                         | 6-9  |

| Semi-Period Measurement                                       | 6-9  |

| Single Semi-Period Measurement                                | 6-9  |

| Implicit Buffered Semi-Period Measurement                     | 6-9  |

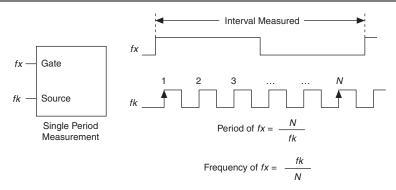

| Frequency Measurement                                         |      |

| Low Frequency with One Counter                                |      |

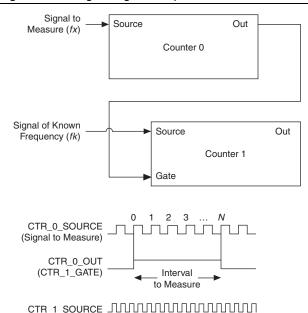

| High Frequency with Two Counters                              | 6-11 |

| Large Range of Frequencies with Two Counters                  |      |

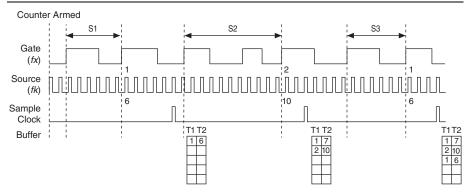

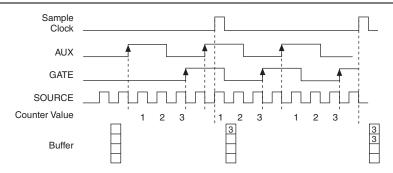

| Sample Clocked Buffered Frequency Measurement                 |      |

| Hardware-Timed Single Point Frequency Measurement             | 6-15 |

| Choosing a Method for Measuring Frequency                     |      |

| Period Measurement                                            |      |

| Position Measurement                                          |      |

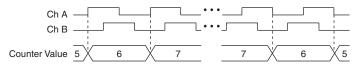

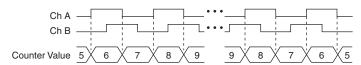

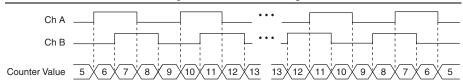

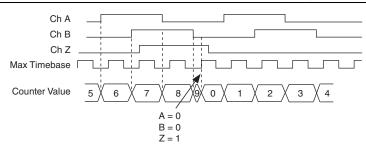

| Measurements Using Quadrature Encoders                        |      |

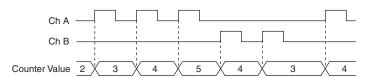

| Measurements Using Two Pulse Encoders                         |      |

| Buffered (Sample Clock) Position Measurement                  |      |

| Hardware-Timed Single Point Position Measurement              |      |

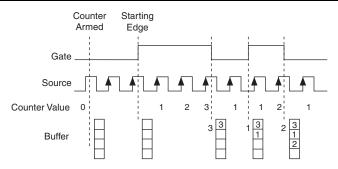

| Two-Signal Edge-Separation Measurement                        |      |

| Single Two-Signal Edge-Separation Measurement                 |      |

| Implicit Buffered Two-Signal Edge-Separation Measurement      |      |

| Sample Clocked Buffered Two-Signal Separation Measurement     |      |

| Hardware-Timed Single Point Two-Signal Separation Measurement |      |

| Counter Output Applications                                   |      |

| Simple Pulse Generation                                       |      |

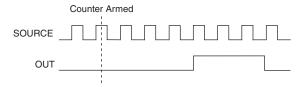

| Single Pulse Generation                                       |      |

| Single Pulse Generation with Start Trigger                    |      |

| Pulse Train Generation                                        |      |

| Finite Pulse Train Generation                                 |      |

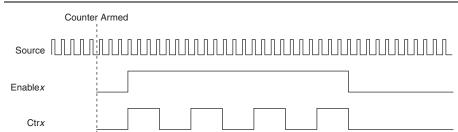

| Retriggerable Pulse or Pulse Train Generation                 |      |

| Continuous Pulse Train Generation                             |      |

| Buffered Pulse Train Generation                               |      |

| Finite Implicit Buffered Pulse Train Generation               |      |

| Continuous Buffered Implicit Pulse Train Generation           |      |

| Finite Buffered Sample Clocked Pulse Train Generation         |      |

| Continuous Buffered Sample Clocked Pulse Train Generation     |      |

| Frequency Generation                                          |      |

| Frequency Division                                            |      |

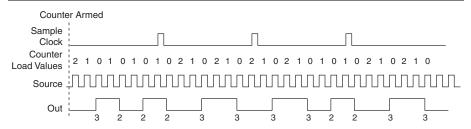

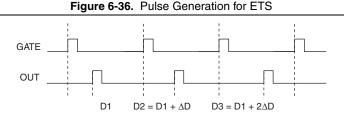

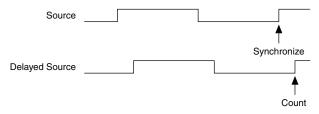

| Pulse Generation for ETS                                      | 6-32 |

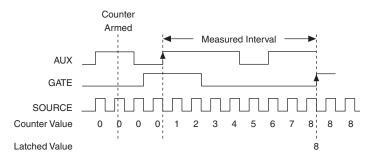

| Counter Timing Signals                                                 | 6-33  |

|------------------------------------------------------------------------|-------|

| Counter <i>n</i> Source Signal                                         | 6-33  |

| Routing a Signal to Counter <i>n</i> Source                            | 6-34  |

| Routing Counter <i>n</i> Source to an Output Terminal                  | 6-34  |

| Counter n Gate Signal                                                  | 6-34  |

| Routing a Signal to Counter n Gate                                     | 6-34  |

| Routing Counter n Gate to an Output Terminal                           |       |

| Counter n Aux Signal                                                   | 6-35  |

| Routing a Signal to Counter <i>n</i> Aux                               |       |

| Counter <i>n</i> A, Counter <i>n</i> B, and Counter <i>n</i> Z Signals |       |

| Routing Signals to A, B, and Z Counter Inputs                          |       |

| Routing Counter n Z Signal to an Output Terminal                       |       |

| Counter n Up_Down Signal                                               | 6-36  |

| Counter n HW Arm Signal                                                | 6-36  |

| Routing Signals to Counter n HW Arm Input                              |       |

| Counter n Sample Clock Signal                                          |       |

| Using an Internal Source                                               | 6-37  |

| Using an External Source                                               |       |

| Routing Counter n Sample Clock to an Output Terminal                   | 6-37  |

| Counter n Internal Output and Counter n TC Signals                     | 6-37  |

| Routing Counter <i>n</i> Internal Output to an Output Terminal         |       |

| Default Counter/Timer Pinouts                                          |       |

| Counter Triggering                                                     | 6-41  |

| Other Counter Features                                                 | 6-41  |

| Cascading Counters                                                     | 6-41  |

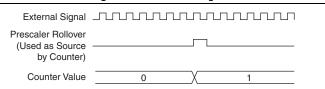

| Prescaling                                                             | 6-42  |

| Synchronization Modes                                                  | 6-42  |

| 100 MHz Source Mode                                                    | 6-43  |

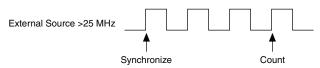

| External Source Greater than 25 MHz                                    | 6-43  |

| External or Internal Source Less than 25 MHz                           | 6-43  |

| Ohantar 7                                                              |       |

| Chapter 7                                                              |       |

| PFI                                                                    |       |

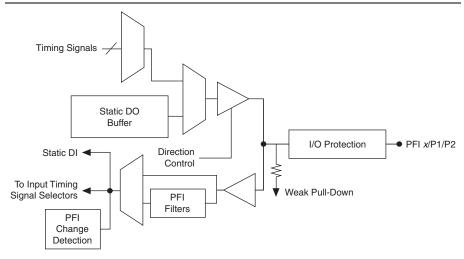

| Using PFI Terminals as Timing Input Signals                            | . 7-2 |

| Exporting Timing Output Signals Using PFI Terminals                    | . 7-2 |

| Using PFI Terminals as Static Digital I/Os                             | . 7-3 |

| Using PFI Terminals to Digital Detection Events                        | 7-3   |

| Connecting PFI Input Signals                                           | 7-4   |

| PFI Filters                                                            | 7-4   |

| I/O Protection                                                         | 7-6   |

| Programmable Power-Up States                                           | 7-6   |

| Digital Routing and Clock Generation         8-1           Clock Routing         8-1           100 MHz Timebase         8-1           20 MHz Timebase         8-2           100 kHz Timebase         8-2           External Reference Clock         8-2           10 MHz Reference Clock         8-2           Synchronizing Multiple Devices         8-3           PXI Express Devices         8-3           PCI Express Devices         8-3           Real-Time System Integration (RTSI)         8-3 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100 MHz Timebase       8-1         20 MHz Timebase       8-2         100 kHz Timebase       8-2         External Reference Clock       8-2         10 MHz Reference Clock       8-2         Synchronizing Multiple Devices       8-3         PXI Express Devices       8-3         PCI Express Devices       8-3                                                                                                                                                                                        |

| 20 MHz Timebase       8-2         100 kHz Timebase       8-2         External Reference Clock       8-2         10 MHz Reference Clock       8-2         Synchronizing Multiple Devices       8-3         PXI Express Devices       8-3         PCI Express Devices       8-3                                                                                                                                                                                                                           |

| 100 kHz Timebase       8-2         External Reference Clock       8-2         10 MHz Reference Clock       8-2         Synchronizing Multiple Devices       8-3         PXI Express Devices       8-3         PCI Express Devices       8-3                                                                                                                                                                                                                                                             |

| External Reference Clock 8-2 10 MHz Reference Clock 8-2 Synchronizing Multiple Devices 8-3 PXI Express Devices 8-3 PCI Express Devices 8-3                                                                                                                                                                                                                                                                                                                                                              |

| 10 MHz Reference Clock8-2Synchronizing Multiple Devices8-3PXI Express Devices8-3PCI Express Devices8-3                                                                                                                                                                                                                                                                                                                                                                                                  |

| Synchronizing Multiple Devices8-3PXI Express Devices8-3PCI Express Devices8-3                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PXI Express Devices 8-3 PCI Express Devices 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PCI Express Devices 8-3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Real-Time System Integration (RTSI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| RTSI Connector Pinout8-4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Using RTSI as Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| RTSI Filters 8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PXI and PXI Express Clock and Trigger Signals 8-6                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| PXIe CLK100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PXIe_CLN100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| PXI CLK10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| PXI Triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| PXI STAR Trigger 8-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| PXI_STAR Higger 8-7 PXI_STAR Filters 8-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| PXIe DSTAR <ac>8-7</ac>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PAIE_DSTAR\AC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Chapter 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Bus Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Device Data Transfer Methods9-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PXI Express Considerations                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| PXI and PXI Express Clock and Trigger Signals9-2                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| PXI Express9-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Appendix A<br>Where to Go from Here                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Appendix B<br>NI 6738/6739 in an NI 6723 System (PXI Express Only)                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Appendix C NI Services

## **Getting Started**

The NI 6738/6739 User Manual contains information about using the National Instruments data acquisition (DAQ) devices with NI-DAQmx. The NI 6738/6739 features up to 64 analog output (AO) channels, up to 20 lines of digital input/output (DIO), and four counters. This chapter provides basic information you need to get started using your device.

**Notice** This icon denotes a notice advising you to take precautions to avoid data loss, loss of signal integrity, or void of guaranteed specifications.

**Caution** This icon denotes a caution advising you take precautions to avoid injury.

## Safety Guidelines

Operate the NI 6738/6739 devices and modules only as described in this user manual.

**Caution** NI 6738/6739 devices and modules are *not* certified for use in hazardous locations.

**Caution** Never connect the +5 V power terminals to analog or digital ground or to any other voltage source on the NI 6738/6739 device or any other device. Doing so can damage the device and the computer. NI is not liable for damage resulting from such a connection.

**Caution** Exceeding the maximum input voltage ratings, which are listed in the specifications document for each NI 6738/6739 device, can damage the DAQ device and the computer. NI is not liable for any damage resulting from such signal connections.

**Caution** Damage can result if these lines are driven by the sub-bus. NI is not liable for any damage resulting from improper signal connections.

## Safety Guidelines for Hazardous Voltages

If hazardous voltages are connected to the device/module, take the following precautions. A hazardous voltage is a voltage greater than 42.4 V<sub>pk</sub> or 60 VDC to earth ground.

**Caution** Ensure that hazardous voltage wiring is performed only by qualified personnel adhering to local electrical standards.

Chapter 1 Getting Started

**Caution** Do *not* mix hazardous voltage circuits and human-accessible circuits on the same module.

**Caution** Make sure that chassis and circuits connected to the module are properly insulated from human contact.

**Caution** NI 6738/6739 devices and modules provide no isolation.

## Electromagnetic Compatibility Information

This product was tested and complies with the regulatory requirements and limits for electromagnetic compatibility (EMC) stated in the product specifications. These requirements and limits provide reasonable protection against harmful interference when the product is operated in the intended operational electromagnetic environment.

This product is intended for use in industrial locations. However, harmful interference may occur in some installations, when the product is connected to a peripheral device or test object, or if the product is used in residential or commercial areas. To minimize interference with radio and television reception and prevent unacceptable performance degradation, install and use this product in strict accordance with the instructions in the product documentation.

Furthermore, any modifications to the product not expressly approved by National Instruments could void your authority to operate it under your local regulatory rules.

**Notices** To ensure the specified EMC performance, operate this product only with shielded cables and accessories.

To ensure the specified EMC performance, the length of all I/O cables must be no longer than 30 m (100 ft).

## Hardware Symbol Definitions

The following symbols are marked on your device or module.

**Caution** When this symbol is marked on a product, refer to the *Safety Guidelines* section for information about precautions to take.

**EU Customers** At the end of the product life cycle, all products *must* be sent to a WEEE recycling center. For more information about WEEE recycling centers, National Instruments WEEE initiatives, and compliance with WEEE Directive

2002/96/EC on Waste and Electronic Equipment, visit ni.com/environment/ weee.

中国客户 National Instruments 符合中国电子信息产品中限制使用某些有害物质指令 (RoHS)。关于 National Instruments 中国 RoHS 合规性信息,请登录 ni.com/ environment/rohs\_china。 (For information about China RoHS compliance, go to ni.com/environment/rohs\_china.)

### Installation

Before installing your DAQ device, you must install the software you plan to use with the device.

- **Installing application software**—Refer to the installation instructions that accompany your software.

- 2.. **Installing NI-DAQmx**—The DAQ Getting Started guides, packaged with NI-DAQmx and also on ni.com/manuals, contain step-by-step instructions for installing software and hardware, configuring channels and tasks, and getting started developing an application.

- **Installing the hardware**—Unpack your device as described in the *Unpacking* section. The DAQ Getting Started guides describe how to install the device, as well as accessories and cables.

## Unpacking

The NI 6738/6739 device ships in an antistatic package to prevent electrostatic discharge (ESD). ESD can damage several components on the device.

**Caution** Never touch the exposed pins of connectors.

To avoid ESD damage in handling the device, take the following precautions:

- Ground yourself with a grounding strap or by touching a grounded object.

- Touch the antistatic package to a metal part of your computer chassis before removing the device from the package.

Remove the device from the package and inspect it for loose components or any other signs of damage. Notify NI if the device appears damaged in any way. Do not install a damaged device in your computer or chassis.

Store the device in the antistatic package when the device is not in use.

### **Device Self-Calibration**

NI recommends that you self-calibrate your device after installation and whenever the ambient temperature changes. Self-calibration should be performed after the device has warmed up for the recommended time period. Refer to the device specifications to find your device warm-up time. This function measures the onboard reference voltage of the device and adjusts the

self-calibration constants to account for any errors caused by short-term fluctuations in the environment. Disconnect all external signals when you self-calibrate a device.

You can initiate self-calibration using NI Measurement & Automation Explorer (MAX), by completing the following steps.

- Launch MAX. 1.

- 2. Select My System» Devices and Interfaces» your device.

- 3. Initiate self-calibration using one of the following methods:

- Click Self-Calibrate in the upper right corner of MAX.

- Right-click the name of the device in the MAX configuration tree and select **Self-Calibrate** from the drop-down menu.

**Note** You can also programmatically self-calibrate your device with NI-DAOmx, as described in Device Calibration in the NI-DAQmx Help or the LabVIEW Help.

### **Device Pinouts**

Refer to Chapter 3, Connector Information, for device pinouts.

## **Device Specifications**

Refer to the device specifications document for your device. To locate your NI 6738/6739 device documentation, go to ni.com/manuals and search for your device:

- PCIe-6738

- PXIe-6738

- PXIe-6739

### **Device Accessories and Cables**

NI offers a variety of accessories and cables to use with your DAO device. Refer to the *Cables* and Accessories section of Chapter 2, DAQ System Overview, for more information.

## DAQ System Overview

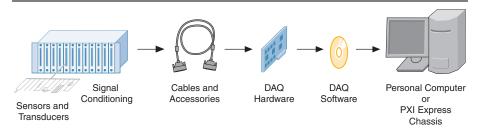

Figure 2-1 shows a typical DAQ system, which includes sensors, transducers, signal conditioning devices, cables that connect the various devices to the accessories, the NI 6738/6739 device, programming software, and PC. The following sections cover the components of a typical DAQ system.

Figure 2-1. Components of a Typical DAQ System

### **DAQ** Hardware

DAQ hardware digitizes signals, performs D/A conversions to generate analog output signals, and measures and controls digital I/O signals. Figure 2-2 features components common to most DAQ devices.

**Analog Output** Digital //O Connector Digital I/O Bus Routing Bus and Clock Interface Generation Counters PXI\_Trig/ **RTSI** PFI

Figure 2-2. General DAQ Device Block Diagram

### DAQ-STC3

The DAQ-STC3 used in the NI 6738/6739 implements a high-performance digital engine for DAO data acquisition hardware. Some key features of this engine include the following:

- Flexible AO sample and convert timing

- Many triggering modes

- Independent AO, DI, DO, and counter FIFOs

- Generation and routing of RTSI or PXI Trig signals for multi-device synchronization

- Generation and routing of internal and external timing signals

- Four flexible 32-bit counter/timer modules with hardware gating

- Digital waveform acquisition and generation

- Static DIO signals

- True 5 V high current drive DO

- DI change detection

- DO watchdog timers

- PLL for clock synchronization

- Seamless interface to signal conditioning accessories

- PCI Express/PXI Express interface

- Independent scatter-gather DMA controllers for all acquisition and generation functions

## Calibration Circuitry

The NI 6738/6739 analog outputs have calibration circuitry to correct gain and offset errors. You can calibrate the device to minimize AO errors caused by time and temperature drift at run time. No external circuitry is necessary; an internal reference ensures high accuracy and stability over time and temperature changes.

Factory-calibration constants are permanently stored in an onboard EEPROM and cannot be modified. When you self-calibrate the device, as described in the *Device Self-Calibration* section of Chapter 1, Getting Started, software stores new constants in a user-modifiable section of the EEPROM. To return a device to its initial factory calibration settings, software can copy the factory-calibration constants to the user-modifiable section of the EEPROM. Refer to the NI-DAQmx Help or the LabVIEW Help for more information about using calibration constants.

For a detailed calibration procedure for NI 6738/6739 devices, refer to the NI 6738/6739 Calibration Procedure available at ni.com/manuals.

### Cables and Accessories

**Caution** For compliance with Electromagnetic Compatibility (EMC) requirements, this product must be operated with shielded cables and accessories. If unshielded cables or accessories are used, the EMC specifications are no longer guaranteed unless all unshielded cables and/or accessories are installed in a shielded enclosure with properly designed and shielded input/output ports.

NI offers a variety of products to use with the NI 6738/6739, including cables, connector blocks, and other accessories, as follows:

- Shielded cable assemblies

- Screw terminal connector blocks

- RTSI bus cable

- I/O connector adapters

For more specific information about these products, refer to ni.com.

Refer to the Custom Cabling and Connectivity section of this chapter for information about how to select accessories for your device.

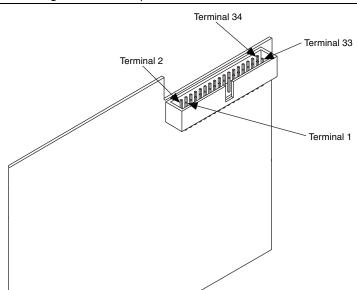

### PCI Express and PXI Express Device Cables and Accessories

This section describes some cable and accessory options for devices with one or more 68-pin connectors. Refer to ni.com/info and enter the Info Code AOCables for a complete list of all accessory options.

#### Screw Terminal Accessories

National Instruments offers several styles of screw terminal connector blocks. All terminal connector blocks require a cable to connect the NI 6738/6739 to a connector block, as listed in Table 2-1.

**Screw Terminal Accessory** Description CB-68LP and CB-68LPR Unshielded connector blocks Shielded connector block SCB-68A **TBX-68** DIN rail-mountable connector block

Table 2-1. Screw Terminal Accessories

#### RTSI Cables

A RTSI bus cable connects timing and synchronization signals among PCI Express devices. Since PXI Express devices use PXI backplane signals for timing and synchronization, no cables are required.

#### Cables

You can use the following cables:

- SHC68-68-A2— Shielded 68-pin, with separate shielding around analog and digital cable sections.

- SH68-C68-S—Only for use integrating the NI 6738/6739 into a NI 6723 system. Refer to the Connecting the NI 6738/6739 in a NI 6723 System section for more information.

### Custom Cabling and Connectivity

The CA-1000 is a configurable enclosure that gives user-defined connectivity and flexibility through customized panelettes. Visit ni. com for more information about the CA-1000.

NI offers cables and accessories for many applications. However, if you want to develop your own cable, adhere to the following guidelines for best results:

- Route the analog lines separately from the digital lines.

- To prevent noise when using a cable shield, use separate shields for the analog and digital sections of the cable.

For more information about the connectors used for DAQ devices, refer to the KnowledgeBase document, Specifications and Manufacturers for Board Mating Connectors, by going to ni.com/info and entering the Info Code rdspmb.

### Connecting the NI 6738/6739 in a NI 6723 System

You can add the NI 6738/6739 to an existing system configured to use the NI 6723. For information on integrating the NI 6738/6739 into an existing NI 6723 system, refer to Appendix B, NI 6738/6739 in an NI 6723 System (PXI Express Only).

## Programming Devices in Software

National Instruments measurement devices are packaged with NI-DAOmx driver software, an extensive library of functions and VIs you can call from your application software, such as LabVIEW or LabWindows/CVI, to program all the features of your NI measurement devices. Driver software has an application programming interface (API), which is a library of VIs, functions, classes, attributes, and properties for creating applications for your device.

The NI 6738/6739 uses the NI-DAQmx driver. NI-DAQmx includes a collection of programming examples to help you get started developing an application. You can modify example code and save it in an application. You can use examples to develop a new application or add example code to an existing application.

To locate LabVIEW, LabWindows/CVI, Measurement Studio, Visual Basic, and ANSI C examples, refer to the document, Where Can I Find NI-DAQmx Examples?, by going to ni.com/info and entering the Info Code dagmxexp.

For additional examples, refer to ni.com/examples.

Table 2-2 lists the earliest NI-DAQmx support version for each device.

Table 2-2. X Series NI-DAQmx Software Support

| Device            | NI-DAQmx Earliest Version Support |  |  |  |  |

|-------------------|-----------------------------------|--|--|--|--|

| NI PCIe-6738      | NI-DAQmx 17.6                     |  |  |  |  |

| NI PXIe-6738/6739 | NI-DAQmx 15.1                     |  |  |  |  |

## **Connector Information**

This chapter contains information on the NI 6738/6739 pinouts and information about the connector signals and power.

## I/O Connector Pinouts

## PCIe/PXIe-6738 Pinout

Figure 3-1 shows the pinout of the PCIe/PXIe-6738 device. For a detailed description of each signal, refer to the I/O Connector Signal Descriptions section.

Figure 3-1. PCIe/PXIe-6738 Pinout

|         | CONNECTOR 0<br>(AO 0-31) |    |    |                     |  |  |  |  |

|---------|--------------------------|----|----|---------------------|--|--|--|--|

|         |                          |    |    |                     |  |  |  |  |

| 녿       | AO GND 30/31             | 68 | 34 | AO 31               |  |  |  |  |

| AO Bank | AO 30                    | 67 | 33 | AO GND 28/29        |  |  |  |  |

| A       | AO 29                    | 66 | 32 | AO 28               |  |  |  |  |

| ¥       | AO GND 26/27             | 65 | 31 | AO 27               |  |  |  |  |

| AO Bank | AO 26                    | 64 | 30 | AO GND 24/25        |  |  |  |  |

| AO      | AO 25                    | 63 | 29 | AO 24               |  |  |  |  |

| ~       | AO GND 22/23             | 62 | 28 | AO 23               |  |  |  |  |

| AO Bank | AO 22                    | 61 | 27 | AO GND 20/21        |  |  |  |  |

| AO      | AO 21                    | 60 | 26 | AO 20               |  |  |  |  |

| Ų       | AO GND 18/19             | 59 | 25 | AO 19               |  |  |  |  |

| AO Bank | AO 18                    | 58 | 24 | AO GND 16/17        |  |  |  |  |

| AO      | AO 17                    | 57 | 23 | AO 16               |  |  |  |  |

|         | AO GND <sup>1</sup>      | 56 | 22 | AO 15               |  |  |  |  |

| AO Bank | AO GND 14/15             | 55 | 21 | AO 14               |  |  |  |  |

| Š       | AO 13                    | 54 | 20 | AO GND 12/13        |  |  |  |  |

|         | AO 12                    | 53 | 19 | AO GND <sup>1</sup> |  |  |  |  |

| Bank    | AO 11                    | 52 | 18 | AO GND 11           |  |  |  |  |

| AO B    | AO 10                    | 51 | 17 | AO 9                |  |  |  |  |

| ٩       | AO GND 8/9/10            | 50 | 16 | AO 8                |  |  |  |  |

| ă.      | AO GND 6/7               | 49 | 15 | AO 7                |  |  |  |  |

| AO Bank | AO 6                     | 48 | 14 | AO GND 4/5          |  |  |  |  |

| ĕ       | AO 5                     | 47 | 13 | AO 4                |  |  |  |  |

| 논       | AO GND 2/3               | 46 | 12 | AO 3                |  |  |  |  |

| AO Bank | AO 2                     | 45 | 11 | AO GND 0/1          |  |  |  |  |

| A       | AO 1                     | 44 | 10 | AO 0                |  |  |  |  |

|         | D GND <sup>1</sup>       | 43 | 9  | PFI 7/P1.7          |  |  |  |  |

|         | D GND PFI 6/7            | 42 | 8  | PFI 6/P1.6          |  |  |  |  |

|         | D GND PFI 4/5            | 41 | 7  | PFI 5/P1.5          |  |  |  |  |

|         | PFI 4/P1.4               | 40 | 6  | PFI 3/P1.3          |  |  |  |  |

|         | D GND PFI 2/3            | 39 | 5  | PFI 2/P1.2          |  |  |  |  |

|         | PFI 1/P1.1               | 38 | 4  | PFI 0/P1.0          |  |  |  |  |

|         | D GND PFI 0/1            | 37 | 3  | P0.1                |  |  |  |  |

|         | D GND P0.0/0.1           | 36 | 2  | P0.0                |  |  |  |  |

|         | D GND <sup>1</sup>       | 35 | 1  | +5 V                |  |  |  |  |

|         | ,                        | _  | _  | J                   |  |  |  |  |

<sup>&</sup>lt;sup>1</sup> No connect when using the SHC68-68-A2 cable.

For the pin assignments of the PCIe/PXIe-6738 using the adapter and SH68-C68-S cable, refer to Appendix B, NI 6738/6739 in an NI 6723 System (PXI Express Only).

Note For more information about default NI-DAQmx counter inputs, refer to Connecting Counter Signals in the NI-DAQmx Help or the LabVIEW Help.

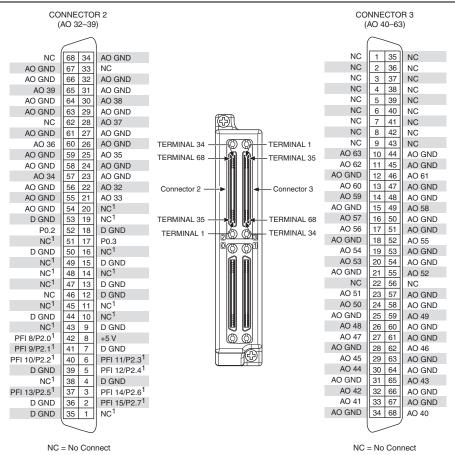

### PXIe-6739 Pinout

Figure 3-2 shows the pinout of the PXIe-6739. For a detailed description of each signal, refer to the I/O Connector Signal Descriptions section.

Figure 3-2. PXIe-6739 Pinout

|           | CONNECTOR 0 CONNECTOR 1 |    |        |                     |     |                     |    |        |                     |         |

|-----------|-------------------------|----|--------|---------------------|-----|---------------------|----|--------|---------------------|---------|

| (AO 0–31) |                         |    |        |                     | - 1 | (AO 32-63)          |    |        |                     |         |

|           |                         | _  |        |                     |     |                     |    | )      |                     |         |

| 논         | AO GND 30/31            | 68 | 34     | AO 31               |     | AO GND 62/63        | 68 | 34     | AO 63               | Þ       |

| Bank      | AO 30                   | 67 | 33     | AO GND 28/29        |     | AO 62               | 67 | 33     | AO GND 60/61        | AO Bank |

| AO        | AO 29                   | 66 | 32     | AO 28               |     | AO 61               | 66 | 32     | AO 60               | ž       |

| ~         | AO GND 26/27            | 65 | 31     | AO 27               |     | AO GND 58/59        | 65 | 31     | AO 59               | >       |

| Bank      | AO 26                   | 64 | 30     | AO GND 24/25        |     | AO 58               | 64 | 30     | AO GND 56/57        | AO Bank |

| AO        | AO 25                   | 63 | 29     | AO 24               |     | AO 57               | 63 | 29     | AO 56               | ank     |

| Ų         | AO GND 22/23            | 62 | 28     | AO 23               |     | AO GND 54/55        | 62 | 28     | AO 55               |         |

| Bank      | AO 22                   | 61 | 27     | AO GND 20/21        |     | AO 54               | 61 | 27     | AO GND 52/53        | Ó       |

| AO        | AO 21                   | 60 | 26     | AO 20               |     | AO 53               | 60 | 26     | AO 52               | AO Bank |

|           | AO GND 18/19            | 59 | 25     | AO 19               |     | AO GND 50/51        | 59 | 25     | AO 51               |         |

| Bank      | AO 18                   | 58 | 24     | AO GND 16/17        |     | AO 50               | 58 | 24     | AO GND 48/49        | AO Bank |

| AO E      | AO 17                   | 57 | 23     | AO 16               |     | AO 49               | 57 | 23     | AO 48               | Ban     |

|           | AO GND <sup>1</sup>     | 56 | 22     | AO 15               |     | AO GND <sup>1</sup> | 56 | 22     | AO 47               | ~       |

| Bank      | AO GND 14/15            | 55 | 21     | AO 14               |     | AO GND 46/47        | 55 | 21     | AO 46               | AO      |

| AO B      | AO 13                   | 54 | 20     | AO GND 12/13        |     | AO 45               | 54 | 20     | AO GND 44/45        | AO Bank |

| ٩         | AO 12                   | 53 | 19     | AO GND <sup>1</sup> |     | AO 44               | 53 | 19     | AO GND <sup>1</sup> | *       |

| Bank      | AO 11                   | 52 | 18     | AO GND 11           |     | AO 43               | 52 | 18     | AO GND 43           | AO      |

| AO Be     | AO 10                   | 51 | 17     | AO 9                |     | AO 42               | 51 | 17     | AO 41               | ) Bank  |

| ¥         | AO GND 8/9/10           | 50 | 16     | AO 8                |     | AO GND 40/41/42     | 50 | 16     | AO 40               | 긎       |

| Bank      | AO GND 6/7              | 49 | 15     | AO 7                |     | AO GND 38/39        | 49 | 15     | AO 39               | AO      |

|           | AO 6                    | 48 | 14     | AO GND 4/5          |     | AO 38               | 48 | 14     | AO GND 36/37        | Bank    |

| AO        | AO 5                    | 47 | 13     | AO 4                |     | AO 37               | 47 | 13     | AO 36               | 큿       |

| 녿         | AO GND 2/3              | 46 | 12     | AO 3                |     | AO GND 34/35        | 46 | 12     | AO 35               | ≥       |

| Bank      | AO 2                    | 45 | 11     | AO GND 0/1          |     | AO 34               | 45 | 11     | AO GND 32/33        | AO Bank |

| AO        | AO 1                    | 44 | 10     | AO 0                |     | AO 33               | 44 | 10     | AO 32               | ž       |

|           | D GND <sup>1</sup>      | 43 | 9      | PFI 7/P1.7          |     | D GND <sup>1</sup>  | 43 | 9      | PFI 15/P2.7         |         |

|           | D GND PFI 6/7           | 42 | 8      | PFI 6/P1.6          |     | D GND PFI 14/15     | 42 | 8      | PFI 14/P2.6         |         |

|           | D GND PFI 4/5           | 41 | 7      | PFI 5/P1.5          |     | D GND PFI 12/13     | 41 | 7      | PFI 13/P2.5         |         |

|           | PFI 4/P1.4              | 40 | 6      | PFI 3/P1.3          |     | PFI 12/P2.4         | 40 | 6      | PFI 11/P2.3         |         |

|           | D GND PFI 2/3           | 39 | 5      | PFI 2/P1.2          |     | D GND PFI 10/11     | 39 | 5      | PFI 10/P2.2         |         |

|           | PFI 1/P1.1              | 38 | 4      | PFI 0/P1.0          |     | PFI 9/P2.1          | 38 | 4      | PFI 8/P2.0          |         |

|           | D GND PFI 0/1           | 37 | 3      | P0.1                |     | D GND PFI 8/9       | 37 | 3      | P0.3                |         |

|           | D GND P0.0/0.1          | 36 | 2      | P0.0                |     | D GND P0.2/0.3      | 36 | 2      | P0.2                |         |

|           | D GND <sup>1</sup>      | 35 | 1      | +5 V                |     | D GND <sup>1</sup>  | 35 | 1      | +5 V                |         |

|           |                         |    |        |                     |     |                     |    |        | J                   |         |

|           |                         | _  | $\sim$ | ,                   | - 1 |                     | _  | $\sim$ | <i>'</i>            |         |

<sup>&</sup>lt;sup>1</sup> No connect when using the SHC68-68-A2 cable.

For the pin assignments of the PXIe-6739 using the adapter and SH68-C68-S cable, refer to Appendix B, NI 6738/6739 in an NI 6723 System (PXI Express Only).

Note For more information about default NI-DAQmx counter inputs, refer to Connecting Counter Signals in the NI-DAQmx Help or the LabVIEW Help.

## I/O Connector Signal Descriptions

Table 3-1 describes the signals found on the I/O connectors. Not all signals are available on all devices.

Table 3-1. I/O Connector Signals

| Signal Name                      | Reference | Direction          | Description                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------|-----------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AO <063>                         | AO GND    | Output             | Analog Output Lines 0 to 63—These terminals supply the voltage output of AO lines 0 to 63.                                                                                                                                                                                                                                                    |

| AO GND                           | _         | _                  | Analog Output Ground—AO GND is the reference for AO <063>. When AO GND is listed next to an analog signal name, it is the dedicated ground reference for those signals (e.g. AO GND 2/3 is the ground reference for AO 2 and AO 3).Both ground references—AO GND and D GND—are connected on the device.*                                      |

| D GND                            | _         | _                  | <b>Digital Ground</b> —D GND supplies the reference for P0.<03>, PFI<015>/P1/P2, and +5 V. When D GND is listed next to a digital signal name, it is the dedicated ground reference for those signals (e.g. D GND PFI 2/3 is the ground reference for PFI 2 and PFI 3). Both ground references—AO GND and D GND—are connected on the device.* |

| P0.<03>                          | D GND     | Input or<br>Output | Port 0 Digital I/O Channels 0 to 3—You can individually configure each signal as an input or output.                                                                                                                                                                                                                                          |

| +5 V                             | D GND     | Output             | +5 V Power Source—These terminals provide a fused +5 V power source. Refer to the +5 V Power Source section for more information.                                                                                                                                                                                                             |

| PFI <015>/<br>P1.<07><br>P2.<07> | D GND     | Input or<br>Output | Programmable Function Interface or Digital I/O Lines 0 to 7 and Lines 8 to 15—Each of these terminals can be individually configured as a PFI terminal or a digital I/O terminal.                                                                                                                                                             |

|                                  |           |                    | As an input, each PFI terminal can be used to supply an external source for AO, DI, and DO timing signals, or counter/timer inputs.                                                                                                                                                                                                           |

|                                  |           |                    | As a PFI output, you can route many different internal AO, DI, or DO timing signals to each PFI terminal. You can also route the counter/timer outputs to each PFI terminal.                                                                                                                                                                  |

|                                  |           |                    | As a Port 1 or Port 2 digital I/O signal, you can individually configure each signal as an input or output. Port 1 and Port 2 signals, however, do not support hardware-timed digital I/O.                                                                                                                                                    |

| NC                               | _         | _                  | No connect—Do not connect signals to these terminals.                                                                                                                                                                                                                                                                                         |

<sup>\*</sup> Though AO GND and D GND are connected on the NI 6738/6739, they are connected by small traces to reduce crosstalk between subsystems. Each ground may have a slight difference in potential.

## +5 V Power Source

The +5 V terminals on the I/O connector supply +5 V referenced to D GND. Use these terminals to power external circuitry.

**Caution** Never connect the +5 V power terminals to analog or digital ground or to any other voltage source on the NI 6738/6739 or any other device. Doing so can damage the device and the computer. NI is not liable for damage resulting from such a connection.

Refer to the specifications document for your device to obtain the device power rating.

## **RTSI Connector Pinout**

(PCle-6738 Devices) Refer to the RTSI Connector Pinout section of Chapter 8, Digital Routing and Clock Generation, for information about the RTSI connector on the PCIe-6738 device.

## **Analog Output**

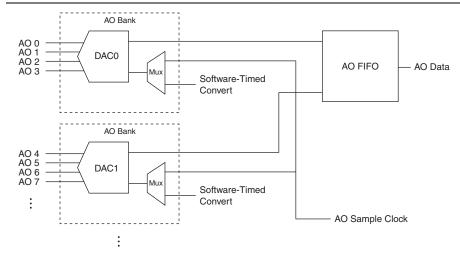

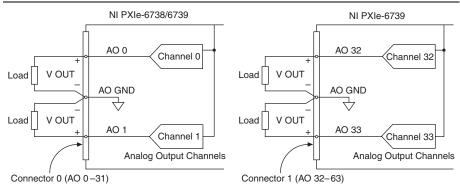

NI 6738/6739 have either 32 or 64 AO channels that are controlled by a single clock and are capable of waveform generation. Figure 4-1 shows the analog output circuitry of the NI 6738/6739. Refer to the list below for detailed descriptions of the AO circuitry elements.

Figure 4-1. NI 6738/6739 Analog Output Circuitry

The main blocks featured in the NI 6738/6739 analog output circuitry are as follows:

- **DACs**—Digital-to-analog converters (DACs) convert digital data to analog voltages.

- Banks—Analog outputs are grouped into four-channel banks. Each bank of four channels

is supported by one DAC per bank, and can select between the AO Sample Clock or a

software-timed convert.

- AO FIFO—The AO FIFO enables analog output waveform generation. It is a

first-in-first-out (FIFO) memory buffer between the computer and the DACs. It allows you

to download the points of a waveform to your device without host computer interaction.

- AO Sample Clock—The AO Sample Clock is the convert source for hardware-timed tasks.

Refer to the *Hardware-Timed Generations* section for more information.

- Software-Timed Convert

—The software-timed convert causes updates on all of the banks

in a software-timed task. Refer to the Software-Timed Generations section for more

information.

## Analog Output Data Generation Methods

When performing an analog output operation, each AO bank of four channels can operate in either software-timed or hardware-timed generations. Each bank can only perform one type of generation at a time.

### Software-Timed Generations

With a software-timed generation, software controls the rate at which data is generated. Software sends a separate command to the hardware to initiate each DAC conversion. In NI-DAQmx, software-timed generations are referred to as on-demand timing. Software-timed generations are also referred to as immediate or static operations. They are typically used for writing a single value out, such as a constant DC voltage.

Software-timed tasks update all channels within their respective AO banks simultaneously. Each bank has a unique software-timed convert signal. A single on-demand task can update any combination of banks simultaneously. Multiple software-timed tasks can be run in parallel on separate banks.

### Hardware-Timed Generations

With a hardware-timed generation, a digital signal controls the rate of the generation. This signal can be generated internally on your device or provided externally.

**Note** Only one hardware-timed generation can be performed on the NI 6738/6739 at a time.

Hardware-timed generations have several advantages over software-timed generations:

- The time between samples can be much shorter.

- The timing between samples can be deterministic.

- Hardware-timed generations can use hardware triggering.

Hardware-timed operations can be buffered or hardware-timed single point (HWTSP). A buffer is a temporary storage in computer memory for to-be-transferred samples.

- Hardware-timed single point (HWTSP)—HWTSP operations, used in conjunction with the wait for next sample clock function, provide tight synchronization between the software layer and the hardware layer. Typically, HWTSP operations are used to write single samples at known time intervals, which provides low latency and low jitter. In addition, HWTSP can notify software if it falls behind hardware in order to avoid writing stale samples. These features make HWTSP ideal for real time control applications such as hardware-in-the-loop (HIL). Refer to the NI-DAOmx Hardware-Timed Single Point Lateness Checking document for more information. To access this document, go to ni.com/info and enter the Info Code daghwtsp.

- **Buffered**—In a buffered generation, data is moved from a PC buffer to the DAQ device's onboard FIFO using DMA. Buffered generation typically allow for much faster transfer

rates than non-buffered generations because data is moved in large blocks, rather than one point at a time.

One property of buffered I/O operations is the sample mode. The sample mode can be either finite or continuous:

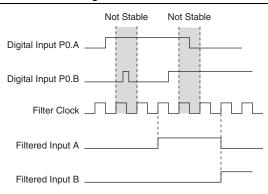

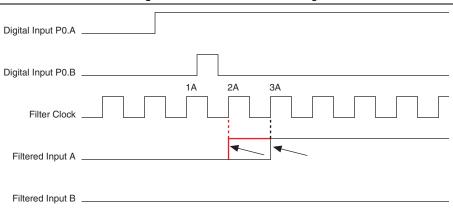

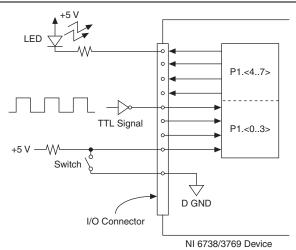

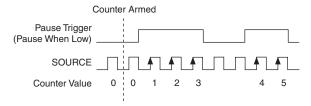

- Finite sample mode generations refers to generations of a specific, predetermined number of data samples. Once the specified number of samples has been written out, the generations stop.