#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs. We Sell For Cash We Get Credit We Receive a Trade-In Deal

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE DAQCard-1200

# DAQCard<sup>™</sup>-1200 Register-Level Programmer Manual

Multifunction I/O Card for the PCMCIA Bus

**October 1995 Edition**

Part Number 340988A-01

© Copyright 1995 National Instruments Corporation. All Rights Reserved.

#### National Instruments Corporate Headquarters

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100 Technical support fax: (800) 328-2203 (512) 794-5678

#### **Branch Offices:**

Australia 03 9 879 9422, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 519 622 9310, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 90 527 2321, France 1 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Italy 02 48301892, Japan 03 5472 2970, Korea 02 596 7456, Mexico 95 800 010 0793, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, U.K. 01635 523545

## **Limited Warranty**

The DAQCard-1200 is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

## Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

## Trademarks

LabVIEW<sup>®</sup>, NI-DAQ<sup>®</sup>, RTSI<sup>®</sup>, and DAQCard<sup>™</sup> are trademarks of National Instruments Corporation.

Product and company names listed are trademarks or trade names of their respective companies.

### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

# Contents

| About This Manual                             | ix   |

|-----------------------------------------------|------|

| Organization of This Manual                   |      |

| Conventions Used in This Manual               | X    |

| National Instruments Documentation            |      |

| Related Documentation                         | xi   |

| Customer Communication                        |      |

| Chapter 1                                     |      |

| General Description                           | 1-1  |

| General Characteristics                       |      |

| Board Configuration Overview                  |      |

| Analog Input Configuration                    |      |

| Analog Output Configuration                   |      |

| Digital I/O Configuration                     |      |

| Counter Configuration                         |      |

|                                               |      |

| Chapter 2                                     |      |

| Register Map and Descriptions                 | 2-1  |

| Register Map                                  |      |

| Register Description Overview                 |      |

| Configuration and Status Register Group       | 2-4  |

| Command Register 1                            |      |

| Command Register 2                            |      |

| Command Register 3                            |      |

| Command Register 4                            |      |

| Command Register 5                            |      |

| Command Register 6                            |      |

| Status Register 1                             |      |

| Status Register 2                             |      |

| Analog Input Register Group                   | 2-17 |

| A/D FIFO Register                             |      |

| A/D Clear Register                            | 2-20 |

| Start Convert Register                        | 2-20 |

| Analog Output Register Group                  | 2-21 |

| DAC0 Low-Byte, DAC0 High-Byte, DAC1 Low-Byte, |      |

| and DAC1 High-Byte Register                   |      |

| 82C53 Counter/Timer Register Groups A and B   |      |

| Counter A0 Data Register                      |      |

| Counter A1 Data Register                      |      |

| Counter A2 Data Register                      |      |

| Counter A Mode Register                       |      |

| Timer Interrupt Clear Register                |      |

| Counter B0 Data Register                      |      |

| Counter B1 Data Register                      |      |

| Counter B2 Data Register                      | 2-27 |

| Counter B Mode Register           | 2-28 |

|-----------------------------------|------|

| 82C55A Digital I/O Register Group |      |

| Port A Register                   |      |

| Port B Register                   |      |

| Port C Register                   |      |

| Digital Control Register          | 2-31 |

| Interval Counter Register Group   |      |

| Interval Counter Data Register    |      |

| Interval Counter Strobe Register  |      |

# Chapter 3

| Programming                                                       | 3-1  |

|-------------------------------------------------------------------|------|

| PCMCIA Card Initialization                                        |      |

| Register Programming Considerations                               | 3-2  |

| Initializing the DAQCard-1200 Circuitry                           | 3-2  |

| Programming the Analog Input Circuitry for Single A/D Conversions | 3-4  |

| Clearing the Analog Input Circuitry                               | 3-4  |

| Configuring the Analog Input Circuitry                            |      |

| Performing Single A/D Conversions                                 |      |

| Programming a DAQ Operation Using Internal Timing                 |      |

| Programming Counter A0 and Counter B0                             |      |

| Programming Counter A1                                            |      |

| Programming Counter B1 and the Interval Counter Register          |      |

| Triggering the DAQ Operation                                      | 3-10 |

| Servicing the DAQ Operation                                       |      |

| Programming a DAQ Operation Using External Timing                 |      |

| Programming a DAQ Operation Using EXTCONV*                        |      |

| Programming a DAQ Operation Using EXTTRIG in Posttrigger Mode     |      |

| Programming a DAQ Operation Using EXTTRIG in Pretrigger Mode      |      |

| Programming a DAQ Operation Using OUTB1                           |      |

| DAQ Interrupt Programming                                         |      |

| Programming the Analog Output Circuitry                           |      |

| Configuring the Analog Output Circuitry                           |      |

| Programming the Update Mode of the Analog Output Circuitry        |      |

| DAC Interrupt Programming                                         |      |

| Programming the Digital I/O Circuitry                             |      |

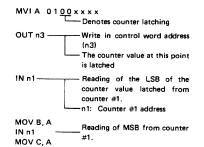

| Programming the General-Purpose Counter/Timers                    | 3-17 |

|                                                                   |      |

# Chapter 4

| Calibration                         | 4-1 |

|-------------------------------------|-----|

| Storing User-Defined Constants      | 4-1 |

| Calibration DACs                    |     |

| Analog Input Calibration            | 4-3 |

| Bipolar Input Calibration Procedure |     |

| Pregain Offset Coarse Calibration   |     |

| Pregain Offset Fine Calibration     | 4-4 |

| Gain Calibration                    | 4-5 |

| Postgain Offset Calibration         | 4-5 |

|                                     |     |

| Calibration at Higher Gains4-5                      |

|-----------------------------------------------------|

| Unipolar Input Calibration Procedure4-5             |

| Pregain Offset Calibration                          |

| Gain Calibration4-6                                 |

| Postgain Offset Calibration4-6                      |

| Analog Output Calibration4-6                        |

| Bipolar Output Calibration Procedure4-7             |

| Gain Calibration4-7                                 |

| Offset Calibration                                  |

| Unipolar Output Calibration Procedure               |

| Gain Calibration                                    |

| Offset Calibration                                  |

| EEPROM Map4-9                                       |

|                                                     |

| Appendix A<br>Card Information Structure (CIS)      |

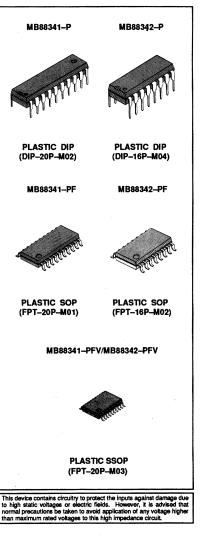

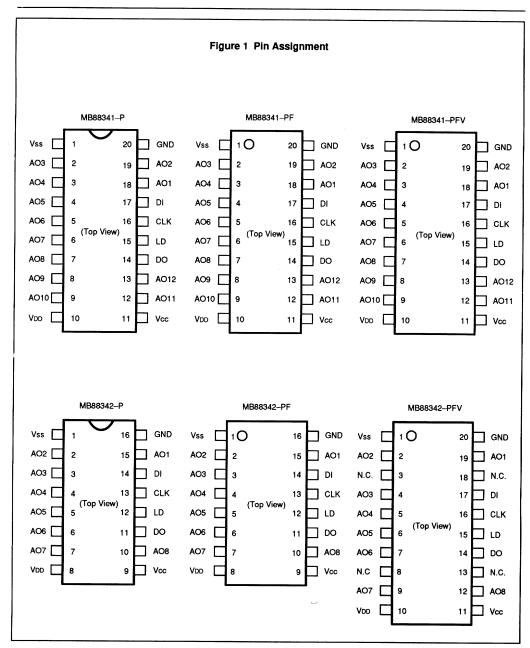

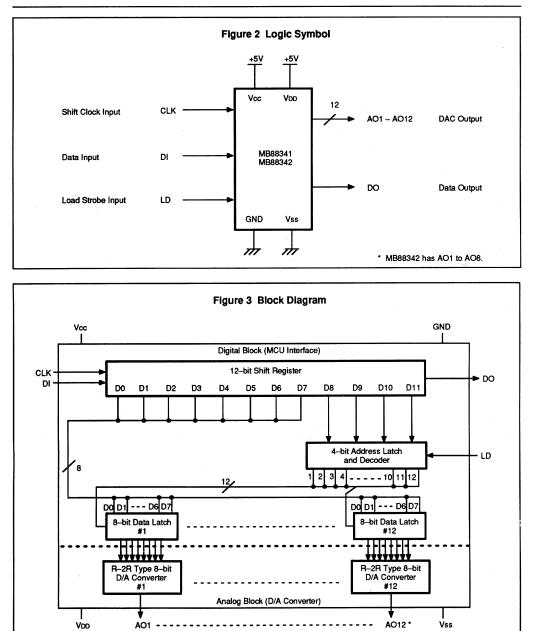

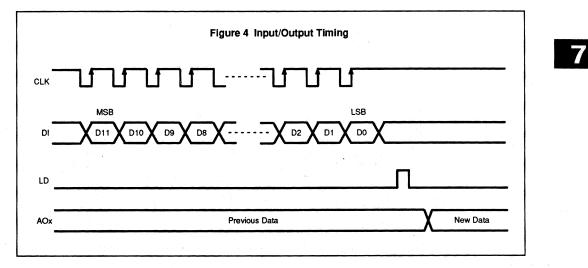

| Appendix B<br>Fujitsu MB88341/MB88342 Data SheetB-1 |

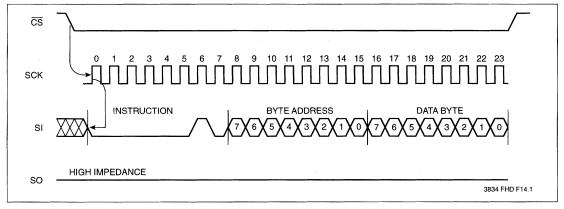

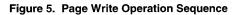

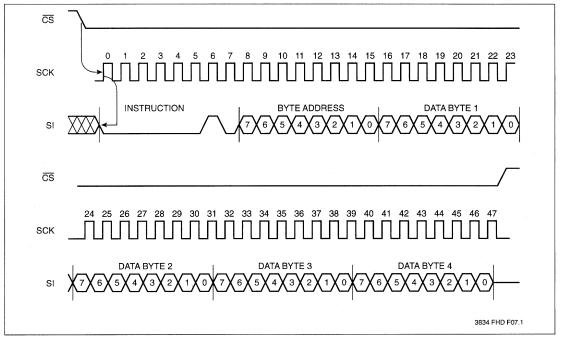

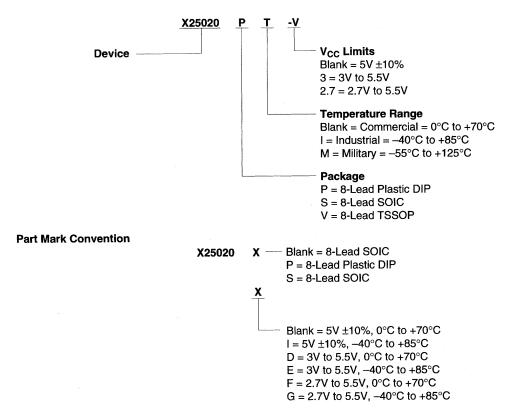

| Appendix C<br>Xicor X25020 Data SheetC-1            |

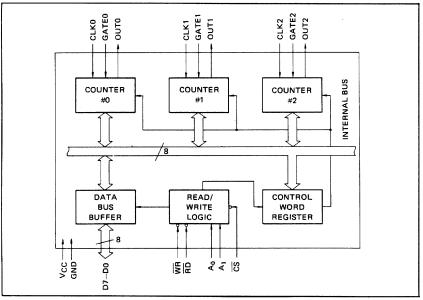

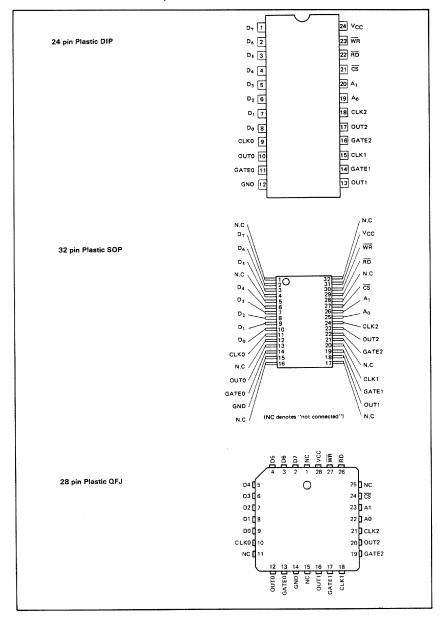

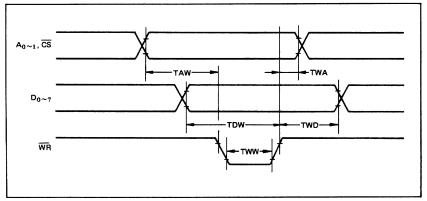

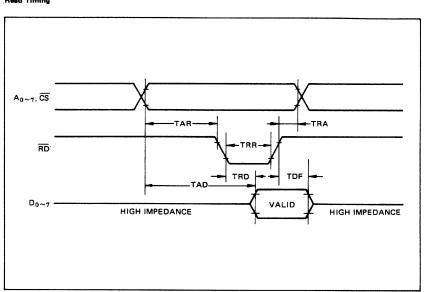

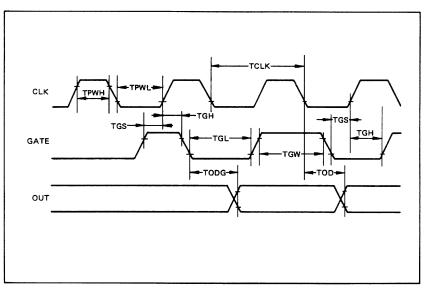

| Appendix D<br>Oki MSM82C53 Data SheetD-1            |

| Appendix E<br>MSM82C55A Data SheetE-1               |

| Appendix F<br>Customer CommunicationF-1             |

| GlossaryG-1                                         |

| Index                                               |

## Tables

|                                        | Analog Input Settings1<br>Analog Output Settings1                                    |      |

|----------------------------------------|--------------------------------------------------------------------------------------|------|

| Table 2-1.                             | DAQCard-1200 Register Map                                                            | 2-2  |

| Table 3-1.                             | Analog Output Voltage Versus Digital Code<br>(Unipolar Mode, Straight Binary Coding) | 3-15 |

| Table 3-2.                             | Analog Output Voltage Versus Digital Code<br>(Bipolar Mode, Two's Complement Coding) | 3-15 |

| Table 4-1.<br>Table 4-2.<br>Table 4-3. | Calibration DAC Characteristics for Analog Input Circuitry                           | 4-3  |

# **About This Manual**

This manual contains information about the internal operation and programming of the DAQCard-1200. The DAQCard-1200 is a low-cost, low-power analog input, analog output, digital, and timing PCMCIA card for computers equipped with a Type II PCMCIA slot.

This manual assumes you are familiar with the *DAQCard-1200 User Manual*. If you will be using National Instruments software with the DAQCard-1200, you do not need to read this manual. For information on the DAQCard-1200 installation, signal connections, and theory of operation, consult your user manual.

# **Organization of This Manual**

The DAQCard-1200 Register-Level Programmer Manual is organized as follows:

- Chapter 1, *General Description*, describes the general characteristics and gives a configuration overview of the DAQCard-1200.

- Chapter 2, *Register Map and Descriptions*, describes in detail the address and function of each of the DAQCard-1200 registers.

- Chapter 3, *Programming*, contains programming instructions for operating the DAQCard-1200 circuitry.

- Chapter 4, *Calibration*, contains instructions for creating user-defined calibration constants for the DAQCard-1200 CALDACs.

- Appendix A, Card Information Structure (CIS), lists the CIS for the DAQCard-1200.

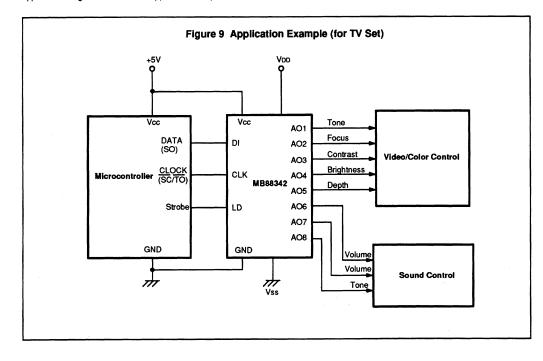

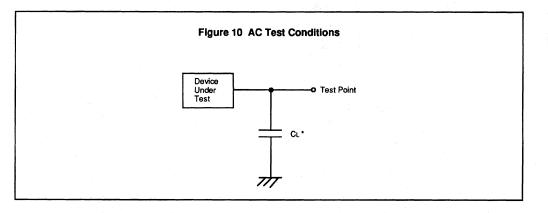

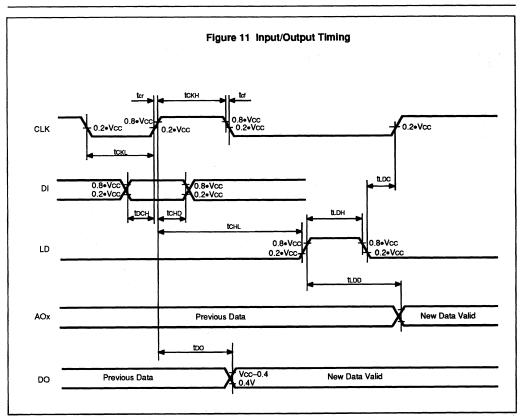

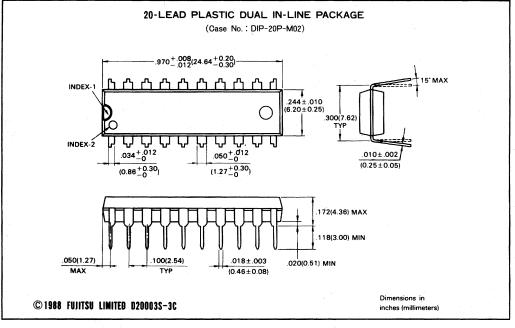

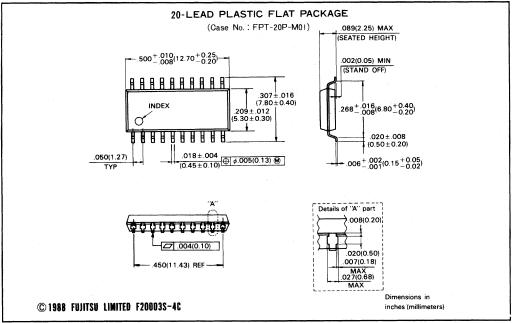

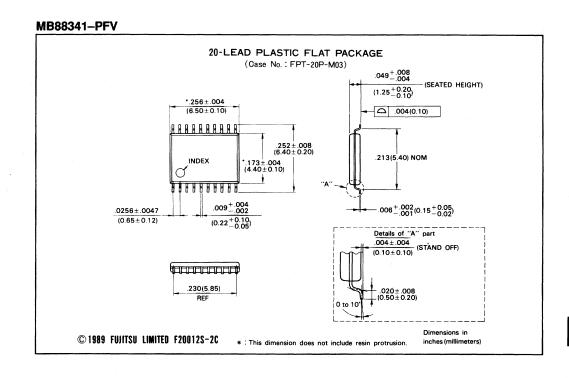

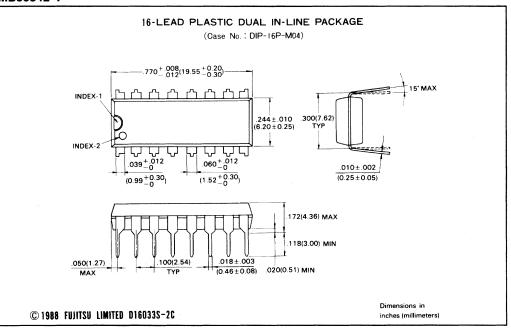

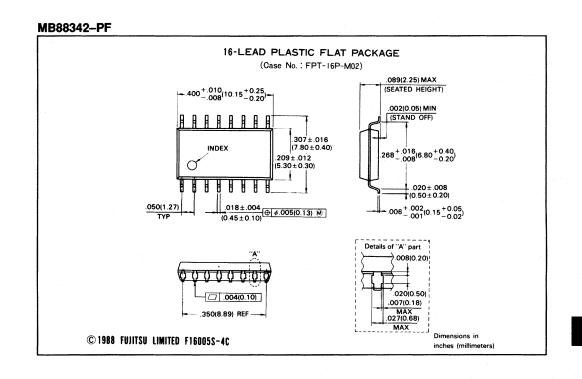

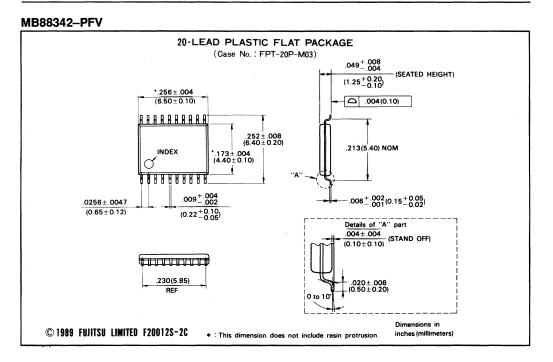

- Appendix B, *Fujitsu MB88341/MB88342 Data Sheet*, contains a manufacturer data sheet for the MB88341 CALDACs (Fujitsu). These CALDACs are used on the DAQCard-1200.

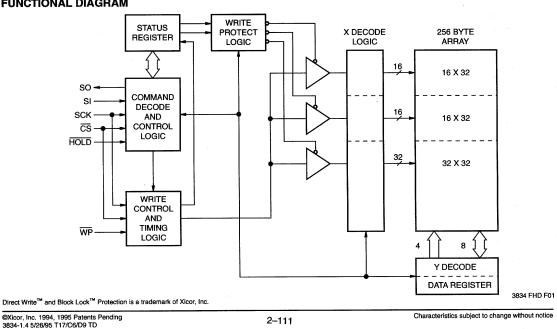

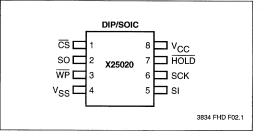

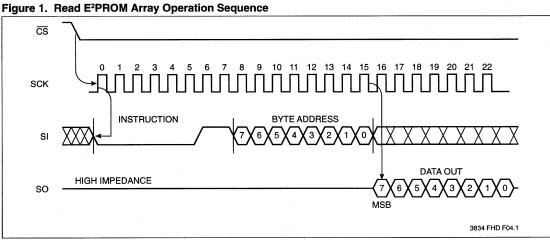

- Appendix C, *Xicor X25020 Data Sheet*, contains a manufacturer data sheet for the X25020 SPI Serial EEPROM (Xicor). This EEPROM is used on the DAQCard-1200.

- Appendix D, *Oki MSM82C53 Data Sheet*, contains a manufacturer data sheet for the MSM82C53 counter/timer (OKI Semiconductor). This counter/timer is used on the DAQCard-1200.

- Appendix E, *Oki MSM82C55A Data Sheet*, contains a manufacturer data sheet for the MSM82C55A programmable peripheral interface (PPI) (OKI Semiconductor). This PPI is used on the DAQCard-1200.

- Appendix F, *Customer Communication*, has a form you can use to comment on the product documentation. This appendix also contains information on how to access technical assistance for your National Instruments product.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, and symbols.

- The *Index* contains an alphabetical list of key terms and topics covered in this manual, including the page where you can find each one.

# **Conventions Used in This Manual**

The following conventions are used in this manual:

| <>          | Angle brackets containing numbers separated by an ellipses represent a range of values associated with a bit, signal, or port (for example, ACH<07> stands for ACH0 through ACH7).                                                                                                                                                                                                                                     |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bold        | Bold text denotes menus, menu items, or dialog box buttons or options.                                                                                                                                                                                                                                                                                                                                                 |

| bold italic | Bold italic text denotes a note, caution, or warning.                                                                                                                                                                                                                                                                                                                                                                  |

| italic      | Italic text denotes emphasis, a cross reference, or an introduction to a key concept.                                                                                                                                                                                                                                                                                                                                  |

| monospace   | Text in this font denotes text or characters that are to be literally input<br>from the keyboard, sections of code, programming examples, and syntax<br>examples. This font is also used for the proper names of disk drives,<br>paths, directories, programs, subprograms, subroutines, device names,<br>functions, variables, filenames, and extensions, and for statements and<br>comments taken from program code. |

| NI-DAQ      | NI-DAQ refers to the NI-DAQ software for PC or Macintosh unless otherwise stated.                                                                                                                                                                                                                                                                                                                                      |

Abbreviations, acronyms, metric prefixes, mnemonics, and terms are listed in the Glossary.

# **National Instruments Documentation**

The *DAQCard-1200 Register-Level Programmer Manual* is one piece of the documentation set for your data acquisition (DAQ) system. You could have any of several types of manuals, depending on the hardware and software in your system. Use the different types of manuals you have as follows:

- *Getting Started with SCXI*—If you are using SCXI, this is the first manual you should read. It gives an overview of the SCXI system and contains the most commonly needed information for the modules, chassis, and software.

- Your SCXI hardware user manuals—If you are using SCXI, read these manuals next for detailed information about signal connections and module configuration. They also explain in greater detail how the module works and contain application hints.

- Your DAQ hardware user manuals—These manuals have detailed information about the DAQ hardware that plugs into or is connected to your computer. Use these manuals for

hardware installation and configuration instructions, specification information about your DAQ hardware, and application hints.

- Software manuals—Examples of software manuals you may have are the LabVIEW and LabWindows<sup>®</sup>/CVI manual sets and the NI-DAQ manuals. After you set up your hardware system, use either the application software (LabVIEW or LabWindows/CVI) manuals or the NI-DAQ manuals to help you write your application. If you have a large and complicated system, it is worthwhile to look through the software manuals before you configure your hardware.

- Accessory installation guides or manuals—If you are using accessory products, read the terminal block and cable assembly installation guides or accessory board user manuals. They explain how to physically connect the relevant pieces of the system. Consult these guides when you are making your connections.

- SCXI chassis manuals—If you are using SCXI, read these manuals for maintenance information on the chassis and installation instructions.

# **Related Documentation**

As you read this manual, you may find it helpful to refer to the following documents:

- Your DAQCard-1200 User Manual

- Your personal computer technical reference manual

- *PC Card Standard, Release 2.1* or later, Personal Computer Memory Card International Association (PCMCIA)

- *Card Services Specifications, Release 2.1* or later, Personal Computer Memory Card International Association (PCMCIA)

- *Socket Services Specifications, Release* 2.1 or later, Personal Computer Memory Card International Association (PCMCIA)

# **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains a comment form for you to complete. This form is in Appendix F, *Customer Communication*, at the end of this manual.

# **Chapter 1 General Description**

This chapter describes the general characteristics and gives a configuration overview of the DAQCard-1200.

# **General Characteristics**

Thank you for your purchase of the National Instruments DAQCard-1200. The DAQCard-1200 is a low-cost, low-power analog input, output, digital, and timing I/O board for PCs equipped with a type II PCMCIA slot. The board contains a 12-bit, successive-approximation ADC with eight input channels, which you can configure as eight single-ended, eight pseudodifferential, or four differential. The DAQCard-1200 also has two 12-bit DACs with voltage outputs, 24 lines of TTL-compatible digital I/O, and three 16-bit counter/timers for timing I/O. The DAQCard-1200 is fully software configurable and calibrated so that you can easily install the card and begin your acquisition without having to spend time configuring or calibrating the board.

The small size and weight of the DAQCard-1200 coupled with its low-power consumption makes this board ideal for use in portable computers, making portable data acquisition practical. The board requires very little power when operating and has a power-down mode that uses even less power, thus conserving the life of your computer batteries.

In addition, the low cost of a system based on the DAQCard-1200 makes it ideal for laboratory work in industrial and academic environments. The multichannel analog input is useful in signal analysis and data logging. The 12-bit ADC is useful in high-resolution applications such as chromatography, temperature measurement, and DC voltage measurement. You can use the analog output channels to generate experimental stimuli, for machine and process control, and for analog function generation. You can use the TTL-compatible digital I/O line for switching external devices such as transistors and solid-state relays, for reading the status of external digital logic, and for generating interrupts. You can use the counter/timers to synchronize events, generate pulses, and measure frequency and time. The DAQCard-1200, used in conjunction with the PC, is a versatile, cost-effective platform for laboratory test, measurement, and control.

The DAQCard-1200 ships with NI-DAQ, the National Instruments complete DAQ driver that handles every function listed on the DAQ hardware data sheet. Using NI-DAQ you can quickly and easily start your application without having to program the card at the register level.

This manual is intended for programming at the register level. Even if you are an experienced register-level programmer, consider using NI-DAQ, LabVIEW, or LabWindows/CVI to program the DAQCard-1200. If NI-DAQ does not support your operating system, or you have other reasons to write your own register-level programs, continue reading this manual.

# **Board Configuration Overview**

This section is a reference to the DAQCard-1200 configuration options. You should already have unpacked and installed your DAQCard-1200. Refer to your *DAQCard-1200 User Manual* if you have not already performed these tasks.

## **Analog Input Configuration**

The DAQCard-1200 is completely software configurable, and at startup, defaults to the following configuration:

- Referenced single-ended input mode

- $\pm 5$  V analog input range

Table 1-1 lists the available analog I/O configurations for the DAQCard-1200 and shows the default settings.

| Parameter          | Configuration                                                                                               |

|--------------------|-------------------------------------------------------------------------------------------------------------|

| Analog Input Range | Bipolar—±5 V (default setting)<br>Unipolar—0–10 V                                                           |

| Analog Input Mode  | Referenced single-ended (RSE) (default setting)<br>Nonreferenced single-ended (NRSE)<br>Differential (DIFF) |

The analog input circuit is software configurable.

## **Analog Output Configuration**

At startup, the two channels of analog output of the DAQCard-1200 default to the following configuration:

• ±5 V analog input range

Table 1-2 lists the available analog I/O configurations for the DAQCard-1200 and shows the default settings.

| Table 1-2. | Analog | Output | Settings |

|------------|--------|--------|----------|

|------------|--------|--------|----------|

| Parameter           | Configuration                                     |

|---------------------|---------------------------------------------------|

| Analog Output Range | Bipolar—±5 V (default setting)<br>Unipolar—0–10 V |

The analog output circuit is software configurable.

## **Digital I/O Configuration**

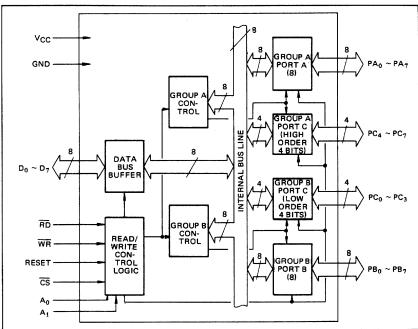

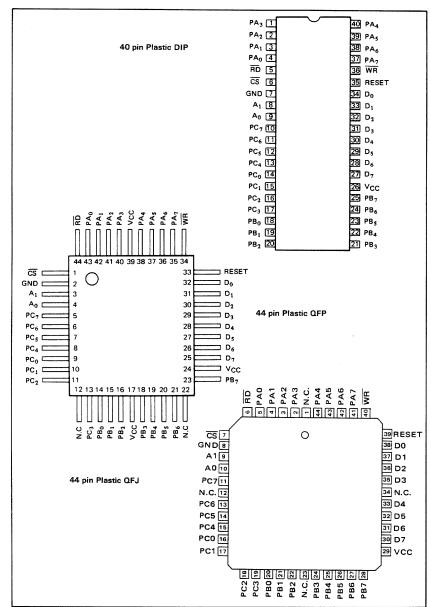

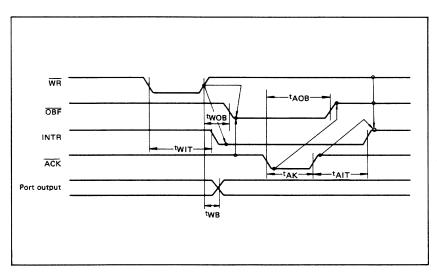

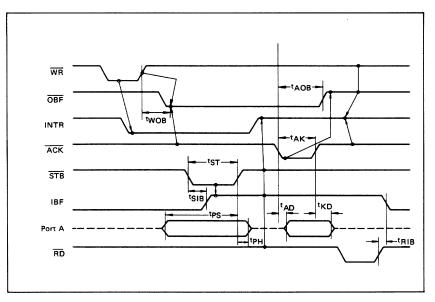

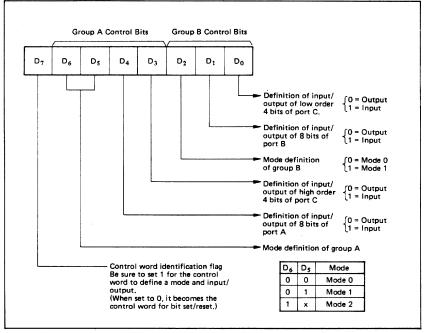

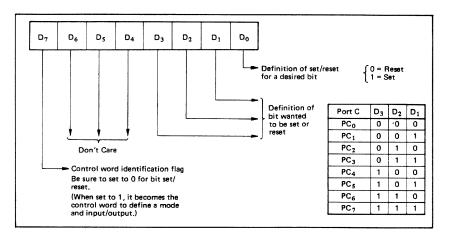

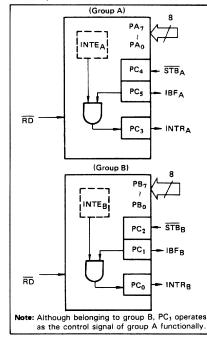

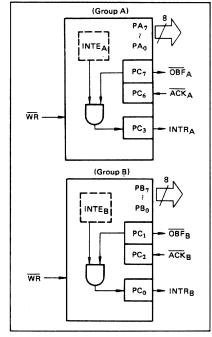

The DAQCard-1200 uses the MSM82C55 PPI, which provides 24 digital lines in the form of three ports—A, B, and C. On power up, all three ports reset to mode 0 input. Appendix E, *OKI MSM82C55 Data Sheet*, has the 82C55 data sheets that you need to program the digital I/O.

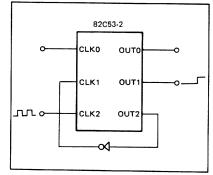

## **Counter Configuration**

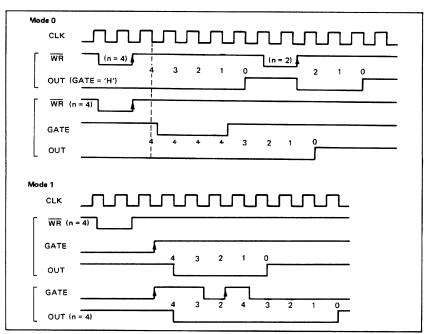

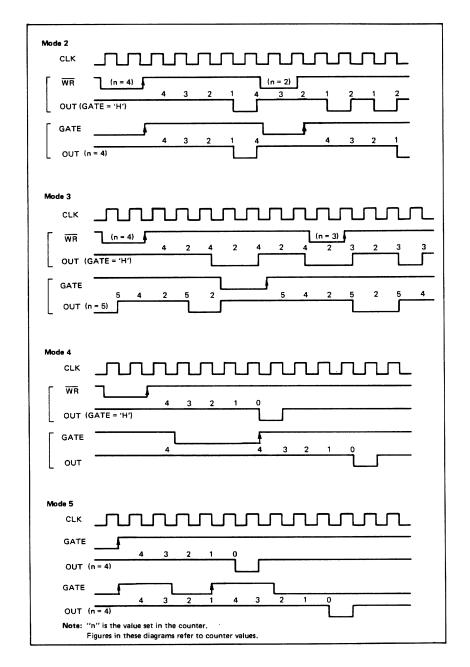

You can use the MSM82C53 counter/timers for general-purpose applications, such as pulse and square wave generation, event counting, and pulsewidth, time-lapse, and frequency measurement. Appendix D, *Oki MSM82C53 Data Sheet*, has the 82C53 data sheet that you need to program the counters/timers.

# Chapter 2 Register Map and Descriptions

This chapter describes in detail the address and function of each of the DAQCard-1200 registers.

# **Register Map**

Table 2-1 shows the register map for the DAQCard-1200 and lists the register name, address, type (read-only, write-only, or read-write), and size in bits.

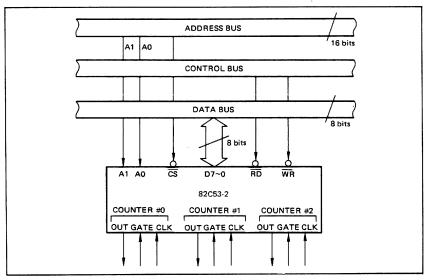

Table 2-1 divides the DAQCard-1200 registers into six groups. The Configuration and Status Register Group controls the overall operation of the DAQCard-1200. The Analog Input Register Group reads output from the 12-bit successive-approximation ADC. The Analog Output Register Group accesses the two 12-bit DACs. The two Counter/Timer Register Groups (A and B) access each of the two onboard 82C53 counter/timer integrated circuits. The Digital I/O Register Group consists of the four registers of the onboard 82C55A PPI integrated circuit that are used for digital I/O. The Interval Counter registers are used in the single-channel interval-acquisition mode.

The DAQCard-1200 registers are 8-bit registers. To transfer 16-bit data, you must perform two consecutive I/O readings or writings. For example, to read the 16-bit A/D conversion result, you must make two consecutive 8-bit readings of the FIFO. The first reading returns the low byte of the 16-bit data, and the second returns the high byte of the data.

The register addresses are the offsets from the base address. For example, if the base address is 0x220, Command Register 1 is at address 0x220, Command Register 2 is at address 0x221, and so on. The base address and interrupt channel must be allocated prior to activating the card. For more information, refer to *PCMCIA Card Initialization* in Chapter 3, *Programming*.

| Register Name                                                                                                                                                                                                         | Address Offset<br>(Hex)                      | Туре                                                                                         | Size                                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| Configuration and Status Register Group<br>Command Register 1<br>Command Register 2<br>Command Register 3<br>Command Register 4<br>Command Register 5<br>Command Register 6<br>Status Register 1<br>Status Register 2 | 00<br>01<br>02<br>0F<br>1C<br>0E<br>00<br>1D | Write-only<br>Write-only<br>Write-only<br>Write-only<br>Write-only<br>Read-only<br>Read-only | 8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit |

| Analog Input Register Group<br>A/D FIFO Register<br>A/D Clear Register<br>Start Convert Register                                                                                                                      | 0A<br>08<br>03                               | Read-only<br>Write-only<br>Write-only                                                        | 8-bit<br>8-bit<br>8-bit                                              |

| Analog Output Register Group<br>DAC0 Low-Byte Register<br>DAC0 High-Byte Register<br>DAC1 Low-Byte Register<br>DAC1 High-Byte Register                                                                                | 04<br>05<br>06<br>07                         | Write-only<br>Write-only<br>Write-only<br>Write-only                                         | 8-bit<br>8-bit<br>8-bit<br>8-bit                                     |

| 82C53 Counter/Timer Register Group A<br>Counter A0 Data Register<br>Counter A1 Data Register<br>Counter A2 Data Register<br>Counter A Mode Register<br>Timer Interrupt Clear Register                                 | 14<br>15<br>16<br>17<br>0C                   | Read-Write<br>Read-Write<br>Read-Write<br>Write-only<br>Write-only                           | 8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit                   |

| 82C53 Counter/Timer Register Group B<br>Counter B0 Data Register<br>Counter B1 Data Register<br>Counter B2 Data Register<br>Counter B Mode Register                                                                   | 18<br>19<br>1A<br>1B                         | Read-Write<br>Read-Write<br>Read-Write<br>Write-only                                         | 8-bit<br>8-bit<br>8-bit<br>8-bit                                     |

| 82C55A Digital I/O Register Group<br>Port A Register<br>Port B Register<br>Port C Register<br>Digital Control Register                                                                                                | 10<br>11<br>12<br>13                         | Read-Write<br>Read-Write<br>Read-Write<br>Write-only                                         | 8-bit<br>8-bit<br>8-bit<br>8-bit<br>8-bit                            |

| Interval Counter Register Group<br>Interval Counter Data Register<br>Interval Counter Strobe Register                                                                                                                 | 1E<br>1F                                     | Write-only<br>Write-only                                                                     | 8-bit<br>8-bit                                                       |

### Table 2-1. DAQCard-1200 Register Map

# **Register Description Overview**

The remainder of this chapter discusses each of the DAQCard-1200 registers in the order shown in Table 2-1. Each register group is introduced, followed by a detailed bit description of each register on the DAQCard-1200. For a detailed bit description of each register concerning the 82C53 (A or B) chip or the 82C55A chip on the DAQCard-1200, refer to Appendix D, *OKI MSM82C53 Data Sheet*, or Appendix E, *OKI MSM82C55A Data Sheet*. The individual register description gives the address, type, word size, and bit map of the register, followed by a description of each bit.

The register bit map shows a diagram of the register with the most significant bit (MSB) (bit 7 for an 8-bit register) shown on the left, and the least significant bit (LSB), bit 0, shown on the right. A rectangle labeled with the bit name inside its rectangle represents each bit. An asterisk (\*) after the bit name indicates that the bit is inverted (negative logic).

In a few of the registers, several bits are labeled with an X, indicating *don't care bits*. When you read a register, these bits may appear set or cleared but should be ignored because they have no significance. When you write to a register, setting or clearing these bit locations has no effect on the DAQCard-1200 hardware.

The bit map field for some write-only registers states *not applicable, no bits used*. Writing to these registers causes some event to occur on the DAQCard-1200, such as clearing the analog input circuitry. The data is ignored when writing to these registers; therefore, any bit pattern will suffice.

## **Configuration and Status Register Group**

The eight registers of the Configuration and Status Register Group allow general control and monitoring of the DAQCard-1200 A/D and D/A circuitry.

Command Register 1 and Command Register 2 contain bits that control the operation modes of the A/D and D/A circuitry. Command Register 3 enables or disables interrupt operations. Use Command Register 4 to select the analog input mode and to allow certain DAQ signals to be externally driven at the I/O connector. Use Command Register 5 for software calibration of the A/D circuitry. Use Command Register 6 to enable and disable interrupt operations and to configure the A/D and D/A circuitry.

Status Register 1 reports the status of a DAQ operation and the status of analog output during waveform generation. Status Register 2 reports the status of a DAQ operation and gives access to the output of the EEPROM.

On power up or through a software reset, all of the Command Registers are cleared.

Bit descriptions for the registers in the Configuration and Status Register Group are on the following pages.

Use Command Register 1 to select the input channel you want to read, the gain for the analog input circuitry, the DAQ scanning mode, and the coding used for the output of the ADC.

| Address: | 00 (hex) |

|----------|----------|

|----------|----------|

Type: Write-only

Word Size: 8-bit

Bit Map:

| 7      | 6     | 5     | 4     | 3       | 2   | 1   | 0   |

|--------|-------|-------|-------|---------|-----|-----|-----|

| SCANEN | GAIN2 | GAIN1 | GAIN0 | TWOSCMP | MA2 | MA1 | MA0 |

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                          |

|-----|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | SCANEN | Scan Enable—This bit enables or disables multiple-channel scanning during data acquisition. Set this bit to scan the analog channels as specified by MA<20> and SE*/D (bit 3 of Command Register 4). Clear this bit to sample a single analog channel specified by MA<20> and SE*/D during the entire DAQ operation. |

6–4 GAIN<2..0> Gain—These three bits select the gain setting as follows:

| GAIN<20> | Selected Gain |

|----------|---------------|

| 000      | 1             |

| 001      | Invalid       |

| 010      | 2             |

| 011      | 5             |

| 100      | 10            |

| 101      | 20            |

| 110      | 50            |

| 111      | 100           |

<sup>3</sup> TWOSCMP Two's Complement—This bit selects the coding format of the ADC output. Set this bit to sign-extend the 12-bit data from the ADC to 16 bits (two's complement). Clear this bit to make bits 12 through 15 return 0 (straight binary).

#### Bit Name Description (continued)

2–0 MA<2..0> Multiplexed Analog—These three bits select which of the eight input channels are read. The analog input multiplexers depend on these bits and also on SCANEN and SE\*/D. Input channels are selected as follows:

|            | Selected                              | Analog Input Ch  | annels          |

|------------|---------------------------------------|------------------|-----------------|

| MA<20>     | Single-Ended Differentia<br>Mode Mode |                  |                 |

|            | Scan<br>Disabled/Enabled              | Scan<br>Disabled | Scan<br>Enabled |

| 000        | 0                                     | 0                | 0               |

| 001<br>010 | $\frac{1}{2}$                         | $0 \\ 2$         | $\frac{2}{4}$   |

| 010        | $\frac{2}{3}$                         | $\frac{2}{2}$    | 6               |

| 100        | 4                                     | 4                | 0               |

| 101<br>110 | 5                                     | 4                | $\frac{2}{4}$   |

| 110        | 7                                     | 6                | 6               |

In single-ended mode (SE\*/D cleared), if you set SCANEN, analog channels MA<2..0> through 0 are sampled sequentially. If you clear SCANEN, a single analog channel specified by MA<2..0> is sampled during the entire DAQ operation.

In DIFF mode, the number of analog inputs reduces to four. The single-ended input channels 0 and 1 (pins 3 and 4) become differential input channel 0. The single-ended input channels 2 and 3 (pins 5 and 6) become differential input channel 2. There are no odd differential input channels.

Command Register 2 contains eight bits that control the DAQCard-1200 analog input trigger modes, analog output update modes, and the coding scheme of the DACs.

Address: 01 (hex)

Type: Write-only

Word Size: 8-bit

| 7     | 6     | 5      | 4      | 3     | 2      | 1      | 0       |

|-------|-------|--------|--------|-------|--------|--------|---------|

| LDAC1 | LDAC0 | 2SDAC1 | 2SDAC0 | TBSEL | SWTRIG | HWTRIG | PRETRIG |

| Bit | Name   | Description                                                                                                                                                                                                                                                                                                                                                |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | LDAC1  | LDAC1—This bit enables timer waveform generation from DAC1.<br>If you set this bit, DAC1 updates its output at regular intervals as<br>determined by counter A2 or the EXTUPDATE* signal at the I/O<br>connector. If you clear this bit, the voltage output of DAC1 is<br>immediately updated when data is loaded into the DAC1 High-<br>Byte Register.    |

| 6   | LDAC0  | LDAC0—This bit enables timer waveform generation from DAC0.<br>If you set this bit, DAC0 updates its output at regular intervals as<br>determined by counter A2 or the EXTUPDATE* signal at the I/O<br>connector. If you clear this bit, the voltage output of DAC0 is<br>immediately updated when data is loaded into the DAC0 High-<br>Byte Register.    |

| 5   | 2SDAC1 | 2SDAC1—This bit selects the binary coding scheme used for the DAC1 data. If you set this bit, a two's complement binary coding scheme is used for interpreting the 12-bit data. Two's complement is used with bipolar output mode. If you clear this bit, a straight binary coding scheme is used. Straight binary is used with unipolar output mode.      |

| 4   | 2SDAC0 | 2SDAC0—This bit selects the binary coding scheme used for the DAC0 data. If you set this bit, then a two's complement binary coding scheme is used for interpreting the 12-bit data. Two's complement is used with bipolar output mode. If you clear this bit, a straight binary coding scheme is used. Straight binary is used with unipolar output mode. |

| Bit | Name    | Description (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | TBSEL   | Time Base Select—This bit selects the clock source for counter A0, the sample interval timer. If you clear this bit, a 1 MHz clock drives counter A0, and the interval between samples is the value loaded into counter A0 multiplied by 1 $\mu$ s. If you set this bit, the output of counter B0 is used as the clock source. The timebase for counter B0 is fixed at 2 MHz. The sample interval is the value loaded into counter A0 multiplied by the period of the output signal from counter B0. |

| 2   | SWTRIG  | Software Trigger—This bit is a software trigger for a DAQ operation. You can trigger a DAQ operation by setting this bit. The terminal count signal of counter A1 or a cleared SWTRIG terminates a DAQ process.                                                                                                                                                                                                                                                                                      |

| 1   | HWTRIG  | Hardware Trigger—This bit enables or disables the posttrigger<br>mode using the EXTTRIG signal at the I/O connector. If you set<br>this bit, you can use the EXTTRIG signal to trigger a DAQ<br>operation in place of SWTRIG. A DAQ process is terminated by a<br>terminal count signal of counter A1 or by writing to the A/D Clear<br>Register. You must clear PRETRIG to use this mode.                                                                                                           |

| 0   | PRETRIG | Pretrigger—This bit enables or disables the pretrigger mode using<br>the EXTTRIG signal at the I/O connector. If you set this bit, you<br>can use the EXTTRIG signal at the I/O connector to terminate a<br>DAQ operation by using counter A1. Data acquisition is<br>terminated by a terminal count on A1. You must clear the<br>HWTRIG to use this mode.                                                                                                                                           |

The Command Register 3 contains four bits that enable and disable interrupts for a DAQ operation and for digital I/O.

Address: 02 (hex)

Type: Write-only

Word Size: 8-bit

| 7 | 6 | 5         | 4        | 3        | 2 | 1        | 0 |

|---|---|-----------|----------|----------|---|----------|---|

| 0 | 0 | FIFOINTEN | ERRINTEN | CNTINTEN | 0 | DIOINTEN | 0 |

| Bit           | Name      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7, 6,<br>2, 0 | 0         | Always leave these bits cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5             | FIFOINTEN | FIFO Interrupt Enable—This bit enables and disables the generation of an interrupt when an A/D conversion result is available to be read from the A/D FIFO. If you set FIFOINTEN, an interrupt is generated whenever the DAVAIL bit becomes set in Status Register 1. Service this interrupt by reading the data from the FIFO.                                                                                                                                                                                          |

| 4             | ERRINTEN  | Error Interrupt Enable—This bit enables and disables the<br>generation of an interrupt when an A/D error condition is detected.<br>If you set ERRINTEN, an interrupt is generated whenever the<br>OVERFLOW or OVERRUN bit becomes set in Status Register 1.<br>Service the interrupt by writing to the A/D Clear Register.                                                                                                                                                                                               |

| 3             | CNTINTEN  | Counter Interrupt Enable—This bit enables the counter A2 output<br>or the EXTUPDATE* signal to generate an interrupt. If you set<br>CNTINTEN, an interrupt occurs whenever the CNTINT bit<br>becomes set in Status Register 1. Clear this interrupt by writing to<br>the Timer Interrupt Clear Register. This interrupt allows<br>waveform generation on the analog output because the same signal<br>that sets the interrupt also updates the DAC output if the<br>corresponding LDAC bit in Command Register 2 is set. |

| 1             | DIOINTEN  | DIO Interrupt Enable—This bit enables or disables generation of<br>an interrupt when either Port A or Port B is ready to transfer data,<br>and an interrupt request is set via PC3 or PC0 of 82C55A. See<br>Appendix D, <i>OKI MSM82C55A Data Sheet</i> , for details. Clear this<br>interrupt by clearing PC3 or PC0. If you clear DIOINTEN, the<br>interrupts from PC3 or PC0 are disabled.                                                                                                                            |

Use this register to select the analog input mode, to enable interval scanning, and to allow the I/O connector pins to externally drive certain DAQ signals.

Address: 0F (hex)

Type: Write-only

Word Size: 8-bit

| 7 | 6 | 5 | 4       | 3     | 2       | 1      | 0       |

|---|---|---|---------|-------|---------|--------|---------|

| 0 | 0 | 0 | ECLKRCV | SE*/D | ECLKDRV | EOIRCV | INTSCAN |

| Bit | Name    | Description                                                                                                                                                                                                                                                                                                                                                 |                                                                                                       |                                                                                                                                                                                                    |                     |  |  |  |

|-----|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|--|--|--|

| 7–5 | 0       | Always leave these                                                                                                                                                                                                                                                                                                                                          | Always leave these bits cleared.                                                                      |                                                                                                                                                                                                    |                     |  |  |  |

| 4   | ECLKRCV | External Clock Receive—This bit disables or enables the external signal EXTCONV*. If you set this bit, transitions on EXTCONV* will not effect data acquisition. If you clear this bit, a falling edge on EXTCONV* initiates an A/D conversion.                                                                                                             |                                                                                                       |                                                                                                                                                                                                    |                     |  |  |  |

| 3   | SE*/D   | Register 6 (RSE*/N<br>of the DAQCard-12<br>clearing this bit and<br>this bit. Refer to the<br>explanation of the o                                                                                                                                                                                                                                          | NRSE), selects one<br>200. You can select<br>d you can select the<br>DAQCard-1200<br>different modes. | along with bit 0 of Comr<br>e of three analog input mo<br>ect the single-ended mode<br>he differential mode by se<br>D User Manual for an<br>The following table illustr<br>les by using SE*/D and | odes<br>by<br>tting |  |  |  |

|     |         | RSE*/NRSE                                                                                                                                                                                                                                                                                                                                                   | SE*/D                                                                                                 | Input Mode                                                                                                                                                                                         |                     |  |  |  |

|     |         | 0<br>1<br>X                                                                                                                                                                                                                                                                                                                                                 | 0<br>0<br>1                                                                                           | RSE (reset condition)<br>NRSE<br>DIFF                                                                                                                                                              |                     |  |  |  |

| 2   | ECLKDRV | External Clock Drive—When you reset this bit (default power up), you can drive the EXTCONV* pin at the I/O connector to cause conversions (if ECLKRCV is also cleared). When you set this bit, you enable internally timed conversions and you drive conversion pulses onto the EXTCONV pin for synchronizing channels on SCXI modules (if used with SCXI). |                                                                                                       |                                                                                                                                                                                                    |                     |  |  |  |

| Bit | Name    | Description (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | EOIRCV  | External Output Interval Clock Receive—This bit selects the clock<br>source for interval scanning. If you clear this bit, counter B1<br>drives the interval scanning circuitry. This will also configure<br>OUTB1 on the I/O Connector as an output signal. If you set this<br>bit, OUTB1 on the I/O Connector is selected as an input signal and<br>allows you to externally drive the interval scanning circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0   | INTSCAN | Interval Scan—This bit distinguishes between the continuous and<br>interval DAQ modes. When you set this bit, the DAQCard-1200<br>performs interval data acquisition. If you clear this bit, continuous<br>data acquisition occurs. For an explanation of the two different<br>modes, refer to Chapter 4, <i>Theory of Operation</i> , in the<br><i>DAQCard-1200 User Manual</i> . Also, this bit selects the clock<br>source for counter B1 used in interval scanning. If interval<br>scanning is disabled (INTSCAN = 0), then counter B1 is available<br>for user applications. You can then drive CLKB1 externally at the<br>I/O connector. If interval scanning is enabled (INTSCAN = 1), the<br>clock source of counter A0 also drives CLKB1. This source can<br>further be selected by using the TBSEL bit in Command<br>Register 2. |

Use Command Register 5 for software calibration of the A/D and D/A circuitry, for interaction with the EEPROM, and for enabling dither.

Address: 1C (hex)

Type: Write-only

Word Size: 8-bit

| 7        | 6     | 5    | 4        | 3        | 2      | 1 | 0 |

|----------|-------|------|----------|----------|--------|---|---|

| EEPROMCS | SDATA | SCLK | CALDACLD | DITHEREN | WRTPRT | 0 | 0 |

| Bit  | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | EEPROMCS | EEPROM Chip Select—This bit enables and disables the<br>EEPROM. You can enable the EEPROM for both read and write<br>operations by setting this bit. You can disable the EEPROM by<br>clearing this bit. Notice that this bit is inverted on the<br>DAQCard-1200 to make EEPROMCS* as explained in the<br><i>Calibration</i> section of Chapter 4, <i>Theory of Operation</i> , in your<br>DAQCard-1200 User Manual. |

| 6    | SDATA    | Serial Data—This bit is a serial data input for both the calibration DACs and the EEPROM.                                                                                                                                                                                                                                                                                                                            |

| 5    | SCLK     | Serial Clock—This bit is a serial clock for both the calibration DACs and the EEPROM. A low-to-high transition of this bit clocks data into the EEPROM (during a write operation) and the calibration DAC. A high-to-low transition of the bit clocks data out of the EEPROM (during a read operation).                                                                                                              |

| 4    | CALDACLD | Calibration DAC Load—This bit updates the calibration DACs.<br>After you load the calibration DAC address and data, set<br>CALDACLD high to update the selected CALDAC output signal.                                                                                                                                                                                                                                |

| 3    | DITHEREN | Dither Enable—This bit enables or disables the dither circuitry.<br>When you set this bit, 0.5 LSB of white Gaussian noise is added to<br>the selected analog input signal. By enabling dither and using<br>averaging, you can achieve greater input resolution.                                                                                                                                                     |

| 2    | WRTPRT   | Write Protect—This bit controls the write protect input signal for<br>the EEPROM. When you set this bit, you enable normal write<br>operations. When you clear this bit, you disable write operations.                                                                                                                                                                                                               |

| 1, 0 | 0        | Always leave these bits cleared.                                                                                                                                                                                                                                                                                                                                                                                     |

Use Command Register 6 to enable A/D interrupts and to configure the A/D and D/A circuitry.

Address: 0E (hex)

Type: Write-only

Word Size: 8-bit

| 7   | 6           | 5 4                                               | 3                                                                                                                                                                                                                                                                                                 | 2                             | 1                        | 0                   |  |  |  |  |

|-----|-------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------|---------------------|--|--|--|--|

| 0   | DQINTEN     | HFINTEN 0                                         | DAC1UNI/BI*                                                                                                                                                                                                                                                                                       | *DAC0UNI/BI*                  | ADCUNI/BI*               | RSE*/NRSE           |  |  |  |  |

| Bit | Name        | Description                                       |                                                                                                                                                                                                                                                                                                   |                               |                          |                     |  |  |  |  |

| 7,4 | 0           | Always leave                                      | these bits cleare                                                                                                                                                                                                                                                                                 | ed.                           |                          |                     |  |  |  |  |

| 6   | DQINTEN     | DAQ operation<br>whenever the<br>Service this in  | DAQ Interrupt Enable—This bit enables and disables the end of a DAQ operation interrupt. Set this bit to generate an interrupt whenever the OUTA1 bit in Status Register 2 becomes set. Service this interrupt by resetting counter A1. Clear this bit to disable interrupt generation.           |                               |                          |                     |  |  |  |  |

| 5   | HFINTEN     | half-full intern<br>the FIFOHF*<br>this interrupt | Half-Full Interrupt Enable—This bit enables and disables the FIFO half-full interrupt. Set this bit to generate an interrupt whenever the FIFOHF* bit in Status Register 2 becomes cleared. Service this interrupt by reading data from the FIFO. Clear this bit to disable interrupt generation. |                               |                          |                     |  |  |  |  |

| 3   | DAC1UNI/BI* | range for $DAC (0 \text{ to } +10 \text{ V}) c$   | DAC1 Unipolar/Bipolar—This bit sets the analog voltage output<br>range for DAC1. Set this bit to configure DAC1 for a unipolar<br>(0 to +10 V) output voltage range. Clear this bit to configure<br>DAC1 for a bipolar (-5 to +5 V) output voltage range.                                         |                               |                          |                     |  |  |  |  |

| 2   | DAC0UNI/BI* | range for $DAC (0 \text{ to } +10 \text{ V}) c$   | ar/Bipolar—Th<br>C0. Set this bit<br>putput voltage ra<br>ipolar (-5 to +5                                                                                                                                                                                                                        | to configure lange. Clear the | DAC0 for a his bit to co | unipolar<br>nfigure |  |  |  |  |

| Bit | Name       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | ADCUNI/BI* | ADC Unipolar/Bipolar—This bit sets the analog voltage input<br>range for data acquisition. Set this bit to select a unipolar (0 to<br>+10 V) voltage input range. Clear this bit to select a bipolar (-5 to<br>+5 V) voltage input range.                                                                                                                                                                                                                                            |

| 0   | RSE*/NRSE  | Referenced Single-Ended/Nonreferenced Single-Ended—This bit,<br>and bit 3 of Command Register 4 (SE*/D), selects one of three<br>input modes of the DAQCard-1200. The status of RSE*/NRSE is<br>only important with the single-ended analog-input modes. Set this<br>bit to select the nonreferenced single-ended mode. Clear this bit to<br>select the referenced single-ended mode. For an explanation of the<br>three input modes, refer to the <i>DAQCard-1200 User Manual</i> . |

### **Status Register 1**

Status Register 1 indicates the status of the current DAQ operation and the status of analog output during waveform generation. These bits indicate if a DAQ operation is in progress or if data is available, whether any errors have been found, and the analog output interrupt status.

|     | 7 | 6        | 5                                                                                                                                                                                                                                                                                                                                                            | 4                                               | 3                                         | 2                                                                                        | 1                                | 0                       |  |

|-----|---|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------|----------------------------------|-------------------------|--|

|     | Х | EXTGATA0 | GATA0                                                                                                                                                                                                                                                                                                                                                        | Х                                               | CNTINT                                    | OVERFLOW                                                                                 | OVERRUN                          | DAVAIL                  |  |

| Bit |   | Name     | Descr                                                                                                                                                                                                                                                                                                                                                        | iption                                          |                                           |                                                                                          |                                  |                         |  |

| 7,4 |   | Х        | Don't ca                                                                                                                                                                                                                                                                                                                                                     | are bits.                                       |                                           |                                                                                          |                                  |                         |  |

| 6   |   | EXTGATA0 | External Gate A0—This bit indicates the status of the external trigger signal (EXTTRIG) during a DAQ operation in posttrigger mode. If this bit is set, EXTTRIG has triggered a DAQ operation. Clear this bit by writing to the A/D Clear Register.                                                                                                          |                                                 |                                           |                                                                                          |                                  |                         |  |

| 5   |   | GATA0    | Gate A0—This bit indicates the status of the GATEA0 input for<br>counter A0. Use this bit as a busy indicator for DAQ operations<br>because conversions are enabled as long as GATEA0 is high and<br>counter A0 is programmed appropriately. A DAQ operation is<br>terminated when GATA0 is cleared.                                                         |                                                 |                                           |                                                                                          |                                  |                         |  |

| 3   |   | CNTINT   | Counter Interrupt—This bit reflects the status of the interrupt caused<br>by counter A2 output or the EXTUPDATE* signal. A low-to-high<br>transition on counter A2 output or on EXTUPDATE* sets this bit.<br>You can generate an interrupt if you set CNTINTEN in Command<br>Register 3. Clear this bit by writing to the Timer Interrupt Clear<br>Register. |                                                 |                                           |                                                                                          |                                  |                         |  |

| 2   |   | OVERFLOW | Overflow—This bit indicates if an overflow error has occurred. If<br>this bit is cleared, no error was encountered. If this bit is set, the<br>A/D FIFO has overflowed because the DAQ servicing operation<br>could not keep up with the sampling rate.                                                                                                      |                                                 |                                           |                                                                                          |                                  |                         |  |

| 1   |   | OVERRUN  | Overrun—This bit indicates if an overrun error has occurred. If this bit is cleared, no error occurred. This bit is set if a convert command is issued to the ADC while the last conversion is still in progress.                                                                                                                                            |                                                 |                                           |                                                                                          |                                  |                         |  |

| 0   |   | DAVAIL   | If this biresult care                                                                                                                                                                                                                                                                                                                                        | it is set, the<br>in be read fi<br>After writir | ADC is fin<br>rom the FIF<br>ng to the A/ | ates if conver<br>ished with the<br>O. This bit is<br>D Clear Regised<br>clear this bit. | e last conver<br>s cleared if th | sion and the ne FIFO is |  |

### Status Register 2

Status Register 2 reports the status of a DAQ operation and the FIFO half-full output as well as gives access to the output of the EEPROM.