#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

### **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

**GPIB-VXI**

# **AT-MXI**User Manual

February 1994 Edition

**Part Number 320339-01**

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100

Technical support fax: (800) 328-2203

(512) 794-5678

#### **Branch Offices:**

Australia (03) 879 9422, Austria (0662) 435986, Belgium 02/757.00.20, Canada (Ontario) (519) 622-9310, Canada (Québec) (514) 694-8521, Denmark 45 76 26 00, Finland (90) 527 2321, France (1) 48 14 24 24, Germany 089/741 31 30, Italy 02/48301892, Japan (03) 3788-1921, Netherlands 03480-33466, Norway 32-848400, Spain (91) 640 0085, Sweden 08-730 49 70, Switzerland 056/20 51 51, U.K. 0635 523545

### **Limited Warranty**

The AT-MXI is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

LabVIEW® and NI-VXI<sup>TM</sup> are trademarks of National Instruments Corporation.

Product and company names listed are trademarks or trade names of their respective companies.

### Warning Regarding Medical and Clinical Use of National Instruments Products

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

#### FCC/DOC Radio Frequency Interference Compliance

This equipment generates and uses radio frequency energy and, if not installed and used in strict accordance with the instructions in this manual, may cause interference to radio and television reception. This equipment has been tested and found to comply with the following two regulatory agencies:

#### **Federal Communications Commission**

This device complies with Part 15 of the Federal Communications Commission (FCC) Rules for a Class A digital device. Operation is subject to the following two conditions:

- 1. This device may not cause harmful interference in commercial environments.

- 2. This device must accept any interference received, including interference that may cause undesired operation.

#### **Canadian Department of Communications**

This device complies with the limits for radio noise emissions from digital apparatus set out in the Radio Interference Regulations of the Canadian Department of Communications (DOC).

Le présent appareil numérique n'émet pas de bruits radioélectriques dépassant les limites applicables aux appareils numériques de classe A prescrites dans le règlement sur le brouillage radioélectrique édicté par le ministère des communications du Canada.

#### **Instructions to Users**

These regulations are designed to provide reasonable protection against harmful interference from the equipment to radio reception in commercial areas. Operation of this equipment in a residential area is likely to cause harmful interference, in which case the user will be required to correct the interference at his own expense.

There is no guarantee that interference will not occur in a particular installation. However, the chances of interference are much less if the equipment is installed and used according to this instruction manual.

If the equipment does cause interference to radio or television reception, which can be determined by turning the equipment on and off, one or more of the following suggestions may reduce or eliminate the problem.

- Operate the equipment and the receiver on different branches of your AC electrical system.

- Move the equipment away from the receiver with which it is interfering.

- Reorient or relocate the receiver's antenna.

- Be sure that the equipment is plugged into a grounded outlet and that the grounding has not been defeated with a cheater plug.

**Notice to user:** Changes or modifications not expressly approved by National Instruments could void the user's authority to operate the equipment under the FCC Rules.

If necessary, consult National Instruments or an experienced radio/television technician for additional suggestions. The following booklet prepared by the FCC may also be helpful: *How to Identify and Resolve Radio-TV Interference Problems*. This booklet is available from the U.S. Government Printing Office, Washington, DC 20402, Stock Number 004-000-00345-4.

### **Contents**

| About This Manual                        |     |    |

|------------------------------------------|-----|----|

| Organization of the AT-MXI User Manual   | . X | i  |

| Conventions Used in This Manual          |     |    |

| How to Use This Manual                   | . X | ii |

| Related Documentation                    | . X | ii |

| Customer Communication                   | . X | ii |

|                                          |     |    |

| Chapter 1                                |     |    |

| Introduction to MXIbus                   | 1-  | 1  |

| Overview                                 |     |    |

| The Need for MXIbus                      |     |    |

| VXI Connection                           |     |    |

| MXIbus Applications                      |     |    |

| MXIbus – An Open Standard                |     |    |

| MXIbus Operation                         |     |    |

| MXIbus Signals                           |     |    |

| MXIbus Cables                            |     |    |

| MXIbus Termination                       |     |    |

| MXIbus Performance                       | 1-  | 7  |

| Data Transfer Rates                      |     |    |

| MXIbus Data Rates                        | 1-  | 8  |

| Local Performance                        | 1-  | 9  |

|                                          |     |    |

| Chapter 2                                |     |    |

| General Information                      | 2-  | 1  |

| Overview                                 | .2- | 1  |

| What Your Kit Should Contain             | 2-  | 2  |

| Optional Hardware                        | 2-  | 3  |

| Optional Software                        | 2-  | 3  |

|                                          |     |    |

| Chapter 3                                |     |    |

| Configuration and Installation           | 3-  | 1  |

| Step 1. Unpack the AT-MXI                | 3-  | 1  |

| Step 2. Configure the AT-MXI             | 3-  | 1  |

| Switch and Jumper Settings               |     |    |

| Base I/O Address Selection               |     |    |

| Interrupt Level Selection                |     |    |

| DMA Channel Selection                    | 3-  | 8  |

| Master Mode Versus Slave Mode            | 3-  | 8  |

| MXIbus Termination Option                |     |    |

| Step 3. Install the AT-MXI               | 3-  | 12 |

| Step 4. Connect the AT-MXI to the MXIbus | 3-  | 13 |

| Chapter 4                                                   |            |

|-------------------------------------------------------------|------------|

| Register Descriptions                                       | 4-1        |

| Register Map                                                | 4-1        |

| Register Description Format                                 | 4-3        |

| Slave Mode Address Register                                 | 4-4        |

| Slave Mode Address Mapping Register                         | 4-6        |

| Master Mode Address Page Register                           | 4-8        |

| Master Mode Address Modifier and Enable Register            | 4-9        |

| Signal Register                                             | 4-12       |

| Board Status Register                                       | 4-13       |

| Board Control Register                                      | 4-1′       |

| Slave Mode Timer Register                                   | 4-2        |

| Master Mode Timer Register                                  | 4-22       |

| System Controller Timer Register                            | 4-23       |

| Timer Control Register                                      | 4-24       |

| Chapter 5                                                   |            |

|                                                             | <b>7</b> 1 |

| Programming Considerations                                  | 5-1        |

| Initialization                                              | 5-1        |

| Initializing the Timers                                     | 5-1        |

| Programming the AT-MXI to be the MXIbus System Controller   | 5-3        |

| Initializing the AT-MXI for Slave-Mode Operation            | 5-3        |

| Initializing the Master-Mode Window                         | 5-4        |

| Master-Mode Operation                                       | 5-5        |

| Paging                                                      | 5-6        |

| Deadlock                                                    |            |

| Timing Incompatibilities                                    |            |

| Performing MXIbus Block-Mode Transfers                      | 5-8        |

| Using a Processor for MXIbus Blocks                         | 5-9        |

| Using the System DMA Controller for MXIbus Blocks           | 5-9        |

| Performing MXIbus Indivisible Transfers                     |            |

| Channel I/O Transfers                                       |            |

| Read-Modify-Write Cycles                                    | 5-1        |

| Locking the MXIbus                                          | 5-1        |

| Slave-Mode Operation                                        | 5-12       |

| Locking the PC AT Bus                                       |            |

| Using the AT-MXI Communication Registers                    | 5-13       |

| AT-MXI Interrupts                                           | 5-13       |

| Chapter 6                                                   |            |

| Theory of Operation                                         | 6-1        |

| AT-MXI Functional Description                               |            |

| MXIbus Terminators                                          | 6-3        |

| System Controller Logic                                     | 6-3        |

| Address Modifier, Address/Data, MXIbus Control Transceivers |            |

| Master-Mode Address Modifier Register                       |            |

| Slave-Mode Address Latch/Counter                            | 6-3        |

| Slave-Mode Address Decoder                                  |            |

| Slave-Mode Offset Register                                  |            |

| Slave-Mode State Machine                                    |            |

| Master-Mode Address Latch                                   |            |

| Master-Mode Address Decoder                                 |            |

| Master-Mode Address Page Register            | 6-:   | 5  |

|----------------------------------------------|-------|----|

| Master-Mode State Machine                    | 6-:   | 5  |

| Parity Generator/Checker                     | 6-5   | 5  |

| Data Latch/Byte Swapper                      | 6-5   | 5  |

| Communication Registers                      | 6-:   | 5  |

| Interrupt Circuitry                          |       |    |

| PC AT Address, Data and Control Transceivers |       |    |

| Master-Mode Operation                        |       |    |

| MXIbus Arbitration                           | 6-6   | 5  |

| MXIbus Address Broadcast                     |       |    |

| Master-Mode Data Transfer                    | 6-8   | 8  |

| Master-Mode Cycle Termination                |       |    |

| Slave-Mode Operation                         | 6-1   | 10 |

| Slave-Mode Address Mapping                   |       |    |

| PC AT Bus Arbitration                        | 6-1   | 10 |

| Slave-Mode Data Transfer                     |       |    |

| Slave-Mode Block Transfers                   | 6-1   | 12 |

| Slave-Mode Cycle Termination                 | 6-1   | 12 |

| Appendix A Specifications                    | A-    | -1 |

| Appendix B<br>Mnemonics                      | B-    | 1  |

| Appendix C MXIbus Connector Description      | C-    | 1  |

| Appendix D Customer Communication            | D-    | -1 |

| GlossaryGloss                                | sary- | 1  |

| <b>Index</b> Ir                              | ıdex- | -1 |

### **Figures**

| Figure 1-1.<br>Figure 1-2.<br>Figure 1-3.<br>Figure 1-4.<br>Figure 1-5. | Comparison of Data Transfer Rates1-2PC Using MXI to Control VXIbus or VMEbus1-3MXI Used for Multiple Mainframe VXIbus or VMEbus System1-4MXI Used for High-Speed Shared-Memory Network1-4MXIbus Multi-Drop Cable Assembly1-6 |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-1.                                                             | AT-MXI Interface Board                                                                                                                                                                                                       |

| Figure 3-1. Figure 3-2. Figure 3-3. Figure 3-4. Figure 3-5.             | AT-MXI Parts Locator Diagram                                                                                                                                                                                                 |

| Figure 6-1. Figure 6-2.                                                 | AT-MXI Block Diagram                                                                                                                                                                                                         |

| Figure C-1.                                                             | MXIbus Connector                                                                                                                                                                                                             |

|                                                                         | Tables                                                                                                                                                                                                                       |

| Table 3-1. Table 3-2.                                                   | AT-MXI Factory Default Settings and Optional Configurations                                                                                                                                                                  |

| Table 4-1. Table 4-2.                                                   | AT-MXI Register Map                                                                                                                                                                                                          |

| Table 5-1.                                                              | AT-MXI Timers5-2                                                                                                                                                                                                             |

| Table 6-1. Table 6-2.                                                   | PC AT Control Signals and MXIbus Control Signals                                                                                                                                                                             |

| Table C-1. Table C-2.                                                   | MXIbus Connector Signal Assignments                                                                                                                                                                                          |

### **About This Manual**

The *AT-MXI User Manual* describes the functional, physical, and electrical aspects of the AT-MXI and contains information concerning its operation and programming.

### **Organization of the** *AT-MXI User Manual*

The AT-MXI User Manual is organized as follows:

- Chapter 1, *Introduction to MXI*, is a tutorial of MXIbus concepts.

- Chapter 2, *General Information*, contains an overview of the functionality of the AT-MXI interface board, shows a picture of the AT-MXI board, and lists the contents of your kit and available optional equipment.

- Chapter 3, *Configuration and Installation*, describes the procedures for unpacking, configuring, and installing your AT-MXI interface board.

- Chapter 4, *Register Descriptions*, contains detailed information on the use of the AT-MXI registers that are accessible via the PC AT bus using I/O operations.

- Chapter 5, *Programming Considerations*, contains information on how to program the AT-MXI interface registers.

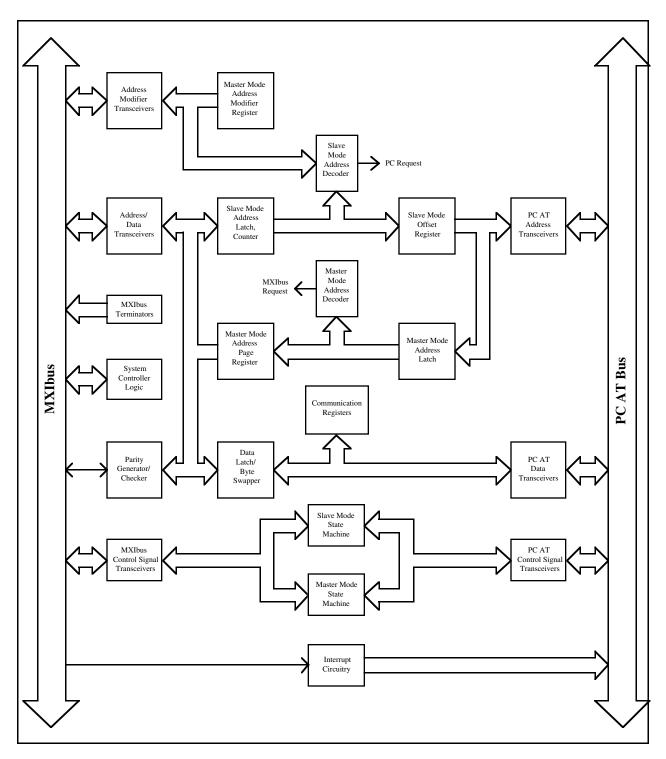

- Chapter 6, *Theory of Operation*, contains a functional block diagram of the AT-MXI, a brief description of the major elements of the interface board, and a detailed description of both master-mode and slave-mode operation.

- Appendix A, *Specifications*, lists various module specifications of the AT-MXI, such as physical dimensions and power requirements.

- Appendix B, *Mnemonics Key*, contains an alphabetical listing of mnemonics used in this manual to describe signals, registers, and register bits. Refer also to the *Acronyms* section later in this Preface.

- Appendix C, *MXIbus Connector Description*, describes the connector pin assignments for the MXIbus connector.

- Appendix D, *Customer Communication*, contains forms for you to complete to facilitate communication with National Instruments concerning our products.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, and symbols.

- The *Index* contains an alphabetical list of key terms and topics used in this manual, including the page where each one can be found.

### **Conventions Used in This Manual**

The following conventions are used in this manual.

italic Italic text denotes emphasis, a cross reference, or an introduction to a key

concept.

monospace Txt in this font denotes sections of code.

**bold italic** Bold italic text denotes a note, caution, or warning.

Abbreviations, acronyms, metric prefixes, symbols, and terms are listed in the *Glossary*.

### **How to Use This Manual**

You should begin with Chapter 1 to gain an understanding of MXIbus concepts. This chapter explains how MXIbus devices attach together and communicate with each other. Chapter 2 contains a general overview about the AT-MXI board. Chapter 3 contains information on how to configure and install your AT-MXI into an AT-based computer. Chapters 4 and 5 contain information you will need to program your AT-MXI. You can skip these chapters if you are using a compatible National Instruments software package because the software routines perform these functions automatically. Chapter 6 contains more technical information on the use of the AT-MXI.

### **Related Documentation**

The following manuals contain information that you may find helpful as you read the *AT-MXI User Manual*:

- Multisystem Extension Interface Bus Specification, Version 1.2 (part number 340007-01)

- *VXIbus System Specification*, Revision 1.4, VXIbus Consortium (available from National Instruments, part number 350083-01)

### **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix D, *Customer Communication*, at the end of this manual.

### Chapter 1 Introduction to MXIbus

### **Overview**

The MXIbus (Multisystem Extension Interface Bus) is a high-performance communication link that interconnects devices using round, flexible cables. MXI operates like modern backplane computer buses, but is a cabled communication link for very high-speed communication between physically separate devices. The emergence of the VXIbus inspired MXI. National Instruments, a member of the VXIbus Consortium, recognized that VXI requires a new generation of connectivity for the instrumentation systems of the future. National Instruments developed the MXIbus specification over a period of two years and announced it in April 1989 as an open industry standard.

You can use MXIbus interface products in a variety of platforms, including the VXIbus and VMEbus backplane systems, and the IBM PC AT, EISA, PS/2, Sun SPARCstation, DECstation 5000, RISC System/6000, and Macintosh computer systems. MXIbus products directly and transparently couple these industry-standard computers to the VXIbus and the VMEbus backplanes. They also transparently extend VXI/VME across multiple mainframes, and seamlessly integrate external devices that cannot physically fit on a plug-in module into a VXI/VME system.

### The Need for MXIbus

Modern PCs and engineering workstations have evolved to the point that today, sophisticated I/O architectures can move data at rates exceeding 10 Mbytes/s. At the same time, modern peripherals such as color scanners and printers, and instruments such as digitizers, logic analyzers, and digital test subsystems generate vast amounts of data at ever increasing data rates. The capabilities of MXI have become increasingly useful for applications that use these data-intensive peripherals.

Clearly the I/O capabilities of modern PCs and workstations can handle data-intensive instrumentation applications. However, the industry has lacked a standard communication link that interconnects devices so that they can operate at full speed across the connection. The worldwide GPIB standard, which was initially designed in the mid 1960s, is relatively slow. Some of the latest networks have higher burst data rates than GPIB, but are not appropriate for real-time, data-intensive applications because their heavy protocol overhead is geared for efficient passing of small message packets.

A memory-mapped communication system that transparently extends bus-level I/O transactions between systems is an ideal solution. It eliminates software protocol overhead altogether, provides direct control and shared memory between devices, and matches the data rates of high-performance computers and peripherals. The MXIbus is such a communication system.

Introduction to MXIbus Chapter 1

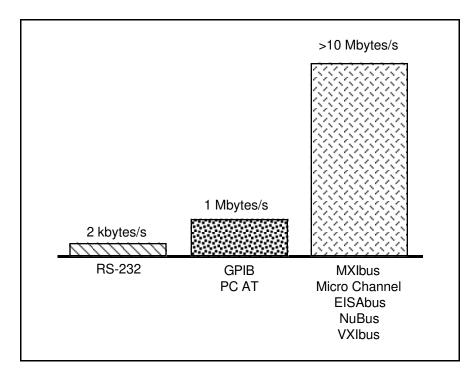

Figure 1-1 shows a comparison of MXIbus transfer data rates against those of RS-232 and GPIB.

Figure 1-1. Comparison of Data Transfer Rates

### **VXI Connection**

Many VXI users migrate from GPIB-based systems. As a result, a GPIB-to-VXI interface such as the National Instruments GPIB-VXI is a popular way to control VXI instruments from a GPIB controller. An increasingly popular way to control VXI, however, is to use a custom VXI computer that plugs directly into the VXI mainframe. This *embedded* approach is technically attractive because the computer communicates directly with the VXIbus and is tightly coupled to the instruments.

An embedded computer is very powerful, but custom VXI computers cannot possibly keep pace with the general-purpose computer market. In the last decade, specialized instrument controllers have rapidly declined. General-purpose PCs and workstations, with their vast array of software and accessories, have revolutionized our industry. By using general-purpose computers, the instrumentation industry directly benefits from the billions of dollars spent each year in the general computer market.

For VXI to truly become the platform for the 90s, it must align itself with the powerful general computer market. This will enable VXI to take advantage of the billions of dollars being spent and bring this investment to bear on the needs of the instrumentation community. VXI must be able to take full advantage of industry-standard PCs, such as the PC AT, PS/2, Macintosh, and EISA computers, as well as workstations from Sun, DEC, IBM, and others. VXI also must have a transparent mechanism for extending to multiple mainframes, and a way to accommodate instruments that can not physically fit on a VXI module. MXIbus meets each of these needs.

Chapter 1 Introduction to MXIbus

### **MXIbus Applications**

A computer, instrument, or other device with a MXI interface is called a MXI device. Typically, MXI devices are systems or instruments that have a MXI interface board installed. Most MXI devices have their own internal system bus for internal communication. The MXI interface board interfaces this internal bus to or from the MXIbus.

Many MXI products have been developed for VXI applications. MXI gives external computers direct control of the VXIbus, as if they were embedded in the VXI mainframe. A VXI-to-MXI mainframe extender can extend VXI to multiple mainframes. Software is also available for VXI programming.

VME systems are another target application for MXI products. You can use VME interface kits to directly control the VMEbus, and a VME-to-MXI chassis extender to extend VME for multiple- chassis configurations. Software is available for VME programming.

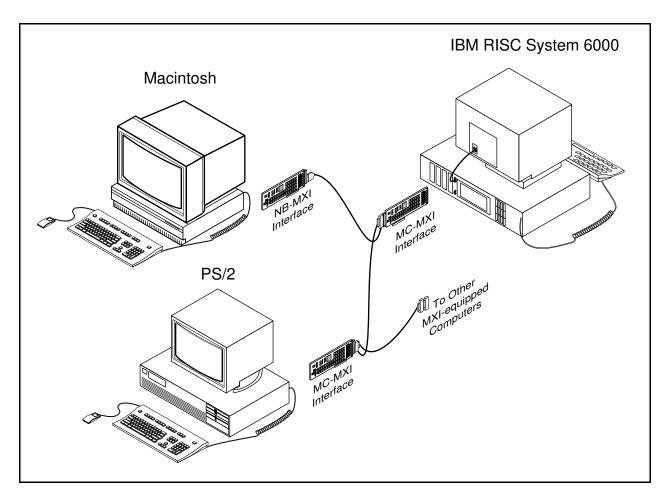

In addition to VXI and VME applications, you can use MXI interface products in a variety of general-purpose, computer-to-computer applications. You can mix and match MXI products to interconnect any number of MXI devices for very high-performance communication. For example, MXI can connect PC AT, EISA, PS/2, SunSPARCstation, DECstation 5000, RISC System/6000, Macintosh, and other computers and workstations for a very high-speed, shared-memory network. You can order MXI computer interfaces individually. The hardware documentation has comprehensive register descriptions that show how to configure the MXI interfaces programmably to establish such a shared-memory network.

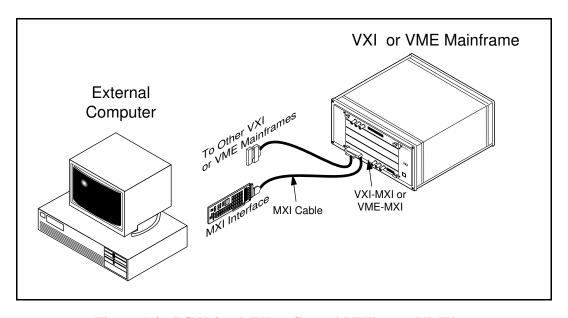

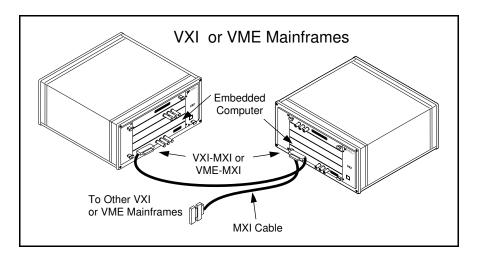

Figures 1-2, 1-3, and 1-4 show three examples of MXIbus applications.

Figure 1-2. PC Using MXI to Control VXIbus or VMEbus

Introduction to MXIbus Chapter 1

Figure 1-3. MXI Used for Multiple Mainframe VXIbus or VMEbus System

Figure 1-4. MXI Used for High-Speed Shared-Memory Network

Chapter 1 Introduction to MXIbus

### **MXIbus – An Open Standard**

Because MXI is an open industry standard, documented with a comprehensive specification, you can design MXI interfaces for your own devices. In this way, your proprietary peripherals or instruments can use MXI to connect to industry-standard computers or to a VXI or VME system. Several third-party companies have successfully used the MXI specification to develop their own MXI interfaces. National Instruments distributes the MXI specification, and will be pursuing formal MXI standardization.

### **MXIbus Operation**

MXIbus is a general-purpose, 32-bit, multimaster system bus on a cable. MXI interconnects multiple devices with flexible, round cables similar to GPIB, but uses a hardware memory-mapped communication scheme that eliminates all software overhead. MXI is very similar to the VMEbus itself, and can be described as a *backplane bus on a cable*. You can daisy-chain up to eight MXI devices together.

MXIbus tightly couples multiple devices by mapping together portions of their individual address spaces. In other words, MXI devices connect at the hardware level, and operate as if they are a single system with a shared address space. MXI devices can directly access each other's resources by performing simple reads and writes to appropriate address locations, thus requiring no software protocol.

Each MXIbus hardware interface has *address window* circuitry that detects internal bus cycles that map out to the MXIbus. Likewise, the circuitry also detects external MXIbus cycles whose address maps into the system. When a hardware write or read occurs with an address that maps across MXI, the MXI hardware interlocks the bus cycle between the devices across the MXIbus. This hardware scheme matches the system used by embedded VXI computers to access VXI.

### **MXIbus Signals**

The MXI connector is a single, rugged, high-density, 62-pin D-subminiature connector. MXIbus signals include 32 multiplexed address and data lines with parity, address modifiers for multiple address spaces, single-level multimaster prioritized bus arbitration, a single interrupt line, a bus error line for handling timeouts and deadlock conditions, and handshake lines for asynchronous operation. You can perform data transfers of 8, 16, and 32 bits, as well as indivisible read/write operations and integrated block-mode transfers. The maximum data rate for MXIbus is 20 Mbytes/s.

### **MXIbus Cables**

There are two basic types of MXIbus cables. One type of MXIbus cable is a point-to-point cable with a single connector on each end. The other type of MXIbus cable is known as a multi-drop cable, and has a single connector on one cable end and a double connector on the other end. A MXIbus system consists of two or more MXIbus devices connected in a daisy-chain fashion. Every MXIbus system has one MXI device that acts as the MXIbus System Controller. The MXIbus System Controller must be the first device in the daisy-chain (requiring it to have a single connector cable end). Subsequent devices will have the double connector end.

Introduction to MXIbus Chapter 1

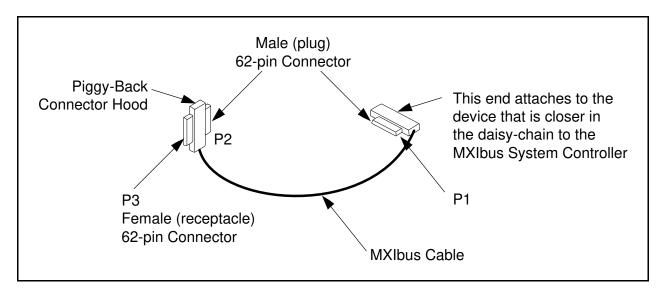

Figure 1-5 is a diagram of the multi-drop type of cable assembly used in a daisy-chained MXIbus system. You can daisy-chain additional devices to the double connector to propagate the bus. Use a MXIbus cable with a single connector on each end when the system contains only two MXI devices or when you are connecting the last cable section in the daisy-chain.

Figure 1-5. MXIbus Multi-Drop Cable Assembly

A single MXI cable can be any length up to 20 m. If multiple MXI devices are daisy-chained together, the total cable distance must be no more than 20 m. The MXI cable is a flexible, round cable similar to a GPIB cable (about 0.6 in. in diameter). Internally there are 48 single-ended, twisted-pair signal lines. Double shielding with an aluminum mylar shield as well as a copper braid shield eliminates any EMI problems. The stacking depth of two daisy-chained MXI cables is approximately 3.4 in.

MXI is essentially a backplane bus on a cable. Each MXI signal line is twisted with its own ground line. All MXIbus signal lines have matched impedance to minimize signal skew and reflections. Limiting stub lengths to no more than 4 in. off the mainline interconnection minimizes reflections due to impedance discontinuities. You must have termination networks at the first and last MXIbus devices to minimize reflections at the ends of cables.

MXI uses state-of-the-art, single-ended, trapezoidal bus transceivers to reduce noise crosstalk in the transmission system. Designed specifically for driving backplane bus signals, these transceivers have open-collector drivers that generate precise trapezoidal waveforms with typical rise and fall times of 9 ns. The trapezoidal shape, due to the constant rise and fall times, reduces noise coupling (crosstalk) on adjacent lines. The receiver uses a lowpass filter to remove noise and a high-speed comparator that recognizes the trapezoidal-shaped signal from the noise.

Chapter 1 Introduction to MXIbus

### **MXIbus Termination**

The MXIbus requires that the first and last devices in the daisy-chain have a termination network. Two basic types of termination networks are available. Some MXIbus devices have onboard termination schemes that should be enabled on the end devices of the daisy-chain. You can also use external terminating packs for easy system reconfiguration and for MXIbus devices that lack onboard terminating networks. MXIbus devices other than the two end devices should *not* have an external terminating pack and must have any onboard terminating networks defeated. Also, each end device must have only one of these termination options.

### **MXIbus Performance**

It is often difficult to understand how a performance specification for a single component relates to the overall performance of your system. In the case of MXI, it is important to understand not only the performance issues associated with the MXI link, but also the devices that communicate across the link. MXI works exactly like an embedded computer, using a direct hardware memory-map to eliminate software overhead between your computer and the VXIbus or VMEbus. Both MXI and embedded VXI computers can use shared memory communication protocols and direct register accesses for potentially dramatic performance improvements over GPIB. If your VXI instruments themselves do not use these capabilities, however, your system performance using MXI or an embedded computer may be no higher than a GPIB-controlled VXI system.

There are several factors to consider when comparing a MXI-equipped computer to an embedded computer. A MXI-equipped computer is functionally equivalent to an embedded computer. In fact, application software developed on a MXI computer can execute on an embedded computer and vice versa. There are subtle hardware timing differences, but there is no dramatic performance difference because of architecture. MXI, for example, can take approximately 100 ns more to perform a single VXI read or write than an embedded computer, because the MXI signals must propagate down the MXI cable at 10 ns/m, and the signals must be synchronized by each device involved in the transfer. This is negligible compared to the other factors that affect your system performance, such as the execution speed of your application software or your instruments.

Often, the most important performance issue to consider when evaluating a computer for your system is the performance of the processor itself. Most applications spend much more time computing, displaying, or performing disk I/O than actually performing I/O across the VXIbus or VMEbus. Current external MXI computers are over four times as fast as the fastest embedded VXI computer. In addition, because of the physical space constraints of embedded computers, external computers often have much more sophisticated architectures with faster processors, cache RAM, faster disk drives, and other benefits. Raw computing power can be the single most important consideration for the performance of your system.

Introduction to MXIbus Chapter 1

### **Data Transfer Rates**

A common benchmark for VXI computers is the *Block Data Rate*. This benchmark is easy for vendors to isolate and measure under ideal conditions. It is important to understand what Block Data Rate means to your application. Block Data Rate is the rate at which you can move a large block of data to or from memory on an ideal VXI device using back-to-back VXI transfers. It does not measure how fast the computer can process the blocks of data or store them to disk once they are moved, or whether your instruments themselves can actually support that data rate. Most applications are not limited by the Block Data Rate of the VXI interface hardware, but rather by the total time required to both move and handle the data, or by the rate at which the instruments themselves can generate or accept the data.

Block Data Rate is easy for vendors to specify, but often difficult for users to relate to overall system performance. It is only one of many elements that affect the actual throughput of your system. For example, Block Data Rate does not indicate the processing power of your computer or the performance of the instruments themselves. In addition, a benchmark for Block Data Rate does not measure how fast you can control instruments using VXI Word Serial Protocol or random VXI reads and writes. The speed for Word Serial communication and random VXI reads and writes is dependent on the speed of the processor and the particular VXI instruments.

### **MXIbus Data Rates**

The theoretical maximum Block Data Rate for MXI is 20 Mbytes/s. As with any bus, the performance of a particular MXI interface depends on the actual design implementation for that interface. All National Instruments MXI user manuals contain a *Specifications* appendix, in which you will find both the single (random access) and block transfer rates for their respective devices. You can think of these values as a propagation delay and use them to calculate the transfer time of your system. To determine the MXI cycle time, add the appropriate master rating of the device that will initiate the MXI transfer to the appropriate slave rating of the device that will accept the MXI transfer.

The read/write access time of your remote system and the length of your MXI cable affect the actual data transfer rate you can achieve. To determine the actual data transfer data rate to expect with a particular device, consider the following equation:

Data Rate (bytes/s) =

$$\frac{\text{Transfer Width (bytes)}}{\text{Transfer Time (s)}}$$

where Transfer Width equals the number of bytes per transfer, and the Transfer Time equals the sum of five components:

- MXI Master Mode time

- MXI Slave Mode time

- Bus access time of the remote system

- Recovery time of the local system (the time it takes the system to generate the next cycle from an acknowledgement of the previous cycle)

- MXI cable propagation time

The MXI cable propagation time is 10 ns/m.

Chapter 1 Introduction to MXIbus

For example, consider the National Instruments VXI-AT2000 kit. The MXI Master Mode time of the AT-MXI is 190 ns for block reads and the MXI Slave Mode time of the VXI-MXI is 240 ns for block reads. Therefore, if your actual application uses a 2 m MXI cable (20 ns MXI cable propagation time) and your VXI device has a bus access time of 100 ns, then the total transfer time for a single read during a block is 550 ns (assuming a 0 ns recovery time for the local system).

Note: The following calculations assume a 0 ns recovery time. Thus, the block data rate computed below is the theoretical maximum. Once you determine your system recovery time, use that value with these calculations to determine the actual block data rate for your system.

Assuming that your VXI device is a 16-bit (2 bytes/transfer) device, your expected Block Read Data Rate to that VXI device using the VXI-AT2000 is 3.64 Mbytes/s as calculated by the following formula:

Block Data Rate =

$$\frac{2 \text{ bytes/transfer}}{550 \text{ ns/transfer}} = 3.64 \text{ Mbytes/s}$$

### **Local Performance**

The MXIbus does not degrade the performance of the devices connected to it. Each MXI device can operate internally at full speed in parallel with other MXI devices. Because MXIbus is a true system bus with multimaster arbitration, the only time MXI devices must synchronize their operation is when they perform transactions that map across the MXIbus. When one MXI device performs a read or write that maps to a remote MXI device, the MXI hardware on both devices interlocks the bus cycle across the MXIbus to accomplish the transfer.

### Chapter 2 General Information

This chapter contains an overview of the functionality of the AT-MXI interface board, shows a picture of the AT-MXI board, and lists the contents of your kit and available optional equipment.

The AT-MXI is an interface board that links an IBM Personal Computer AT or compatible computer (hereafter referred to as the PC AT) directly to the MXIbus. It uses address mapping to translate bus cycles on the PC AT bus to the MXIbus and vice versa. Figure 2-1 shows the AT-MXI interface board.

Figure 2-1. AT-MXI Interface Board

### **Overview**

The AT-MXI can function as both a MXIbus master and a MXIbus slave. When operating as a MXIbus master, the AT-MXI converts PC AT memory cycles initiated by the CPU or an alternate bus master on the PC AT bus into MXIbus cycles intended for a MXIbus slave device. When operating as a MXIbus slave, the AT-MXI converts MXIbus cycles initiated by a MXIbus master into PC AT memory or I/O bus cycles so that other MXIbus devices can freely access (share) resources within the PC AT.

As a MXIbus master, the AT-MXI supports 32-bit (A32), 24-bit (A24) and 16-bit (A16) addressing. As a MXIbus slave, the AT-MXI supports A24 addressing to PC AT memory and A16 addressing to the AT-MXI communication registers and to the PC AT I/O space. The AT-MXI supports both 16-bit (D16) and 8-bit (D08) data transfers while operating as either a MXIbus master or a MXIbus slave. The AT-MXI cannot support 32-bit (D32) data transfers because the PC AT data bus is only 16 bits wide.

General Information Chapter 2

Because the AT-MXI uses the same communication register set that is used by VXIbus Message-Based devices, other MXIbus devices can view the AT-MXI as a VXIbus device. The following are some of the numerous benefits that can result from using the VXIbus register architecture:

- Dynamic device identification and configuration during system initialization

- Standardized Word Serial communication between devices

- Dynamic resource (memory) allocation

- Message (signal) passing protocols between devices

- Shared memory architectures

The AT-MXI supports MXIbus block-mode transfers while operating as either a MXIbus master or a MXIbus slave. With block-mode transfers, data located in consecutive memory locations can be transferred at higher rates because MXIbus addressing information is not sent with each data transfer. The AT-MXI supports the use of the direct memory access (DMA) controller on the PC AT computer when transferring block-mode data between the PC AT bus and the MXIbus. Optionally, any MXIbus or PC AT bus master can be used to initiate and transfer block-mode data via the AT-MXI.

In addition to these features, the AT-MXI is also able to function as the MXIbus System Controller and can terminate the MXIbus signals directly on the AT-MXI interface board. The AT-MXI also supports the MXIbus arbitration lock and fairness options.

#### What Your Kit Should Contain

Your AT-MXI kit should contain the following components:

| Kit Component          | Part Number |

|------------------------|-------------|

| AT-MXI Interface Board | 180775-01   |

| AT-MXI User Manual     | 320339-01   |

Chapter 2 General Information

### **Optional Hardware**

| Cables                                                                         | Part Number                                                   |

|--------------------------------------------------------------------------------|---------------------------------------------------------------|

| Type M1 MXIbus Cables Straight Point-to-Point Connectors:                      |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                     | 180758-01<br>180758-02<br>180758-04<br>180758-08<br>180758-20 |

| Type M2 MXIbus Cables<br>Straight Point-to-Right Angle Daisy-Chain Connectors: |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                     | 180760-01<br>180760-02<br>180760-04<br>180760-08<br>180760-20 |

| Type M3 MXIbus Cables Right Angle Point-to-Right Angle Daisy-Chain Connectors: |                                                               |

| - 1 m<br>- 2 m<br>- 4 m<br>- 8 m<br>- 20 m                                     | 180761-01<br>180761-02<br>180761-04<br>180761-08<br>180761-20 |

| MXIbus Terminating Pac (External)                                              | 180780-01                                                     |

| MXIbus Connector Extender                                                      | 181663-01                                                     |

### **Optional Software**

Your AT-MXI is shipped without interface software. This manual contains complete instructions for programming the AT-MXI directly. You can order various software packages from National Instruments for programming and controlling the AT-MXI.

You can use the AT-MXI with LabWindows, an innovative program development software package for test and measurement applications. LabWindows enhances Microsoft QuickBASIC and C with an interactive development environment, function panels to generate source code, and libraries for data acquisition, instrument control, and data analysis and presentation. LabWindows for DOS is available for programming in C or BASIC. LabWindows/CVI is a complete, full-function C programming environment for PC-compatible computers running Windows.

General Information Chapter 2

You can also use the AT-MXI with LabVIEW, a complete programming environment with a unique graphical methodology. LabVIEW departs from the sequential nature of traditional programming languages and features a graphical programming environment and all the tools needed for data acquisition, analysis, and presentation. LabVIEW matches the modular virtual instrument capability of VXI, and can reduce your VXIbus software development time. LabVIEW packages are available for PC-compatible computers running either Windows or Windows NT.

The AT-MXI can also be used with the NI-VXI bus interface software package, a comprehensive software package for configuring, programming, and truobleshooting a VXI system. NI-VXI features a standardized set of utilities and C library functions that give you simple, low-level access to other MXIbus devices. NI-VXI is available across many different operating system platforms.

The following table lists the application software packages and the NI-VXI bus interface software packages you can order for the AT-MXI.

| Software                                                                                                                                                                                      | Part Number                                                   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| LabWindows VXI Development System for DOS<br>LabWindows/CVI VXI Development System for Windows<br>LabVIEW VXI Development System for Windows<br>LabVIEW VXI Development System for Windows NT | 776729-01<br>776804-01<br>776674-01<br>776774-01              |

| NI-VXI Bus Interface Software Packages for AT-MXI  - MS-DOS - Microsoft Windows - SCO UNIX - ISC UNIX - Windows NT                                                                            | 776418-01<br>776458-01<br>776368-02<br>776368-03<br>776873-58 |

## **Chapter 3 Configuration and Installation**

This chapter describes the procedures for unpacking, configuring, and installing your AT-MXI interface board. The instructions are given in the order that you should perform them. A summary of the steps is as follows:

- 1. Unpack the AT-MXI.

- 2. Configure the AT-MXI.

- 3. Install the AT-MXI.

- 4. Connect the AT-MXI to the rest of your MXIbus system.

### **Step 1. Unpack the AT-MXI**

Follow these steps when unpacking your AT-MXI interface board:

- 1. Before attempting to configure or install the AT-MXI, inspect the shipping container and its contents for damage. If damage appears to have been caused in shipment, file a claim with the carrier. Retain the packing material for possible inspection and/or for reshipment.

- 2. Verify that the pieces contained in the package you received match the kit parts list. *Do not* remove the board from its plastic bag at this point.

- 3. Your AT-MXI board is shipped packaged in an antistatic plastic bag to prevent electrostatic damage to the board. Some of the circuitry on the AT-MXI uses CMOS technology and can be damaged by electrostatic discharge. Before removing the board from the antistatic bag, touch the bag to a metal part of your computer chassis.

- 4. As you remove the AT-MXI from its bag, be sure to handle the board only by its edges. Avoid touching any of the IC components or connectors. Inspect the board for loose components or any other sign of damage. Notify National Instruments if the board appears damaged in any way. *Do not* install equipment that appears to be damaged.

### **Step 2. Configure the AT-MXI**

You can configure four options on the AT-MXI board:

- Base I/O address

- Interrupt levels

- DMA channels

- MXIbus termination option

Figure 3-1. AT-MXI Parts Locator Diagram

#### **Switch and Jumper Settings**

Table 3-1 shows the factory settings and optional settings for the configurable options on the AT-MXI.

| Feature                | Default   | Optional Configurations                            |

|------------------------|-----------|----------------------------------------------------|

| Base I/O Address (hex) | 340       | 100 to 3E0, increments of 20 hex                   |

| Board Interrupt Level  | 12        | 3, 4, 5, 6, 7, 9, 10, 11, 12, 14, 15, and Not Used |

| MXIbus Interrupt Level | 10        | 3, 4, 5, 6, 7, 9, 10, 11, 12, 14, 15, and Not Used |

| Master DMA Channel     | 6         | 0, 1, 2, 3, 5, 6, 7, and Not Used                  |

| Slave DMA Channel      | 3         | 0, 1, 2, 3, 5, 6, 7, and Not Used                  |

| MXIbus Termination     | Installed | Not Installed                                      |

Table 3-1. AT-MXI Factory Default Settings and Optional Configurations

The factory-configured settings of the base I/O address, the interrupt levels, and the DMA channels are suitable for most computer systems. The following sections describe under what conditions it would be necessary to change the configuration jumpers, switches, and/or terminators on the AT-MXI and how to make these changes.

#### **Base I/O Address Selection**

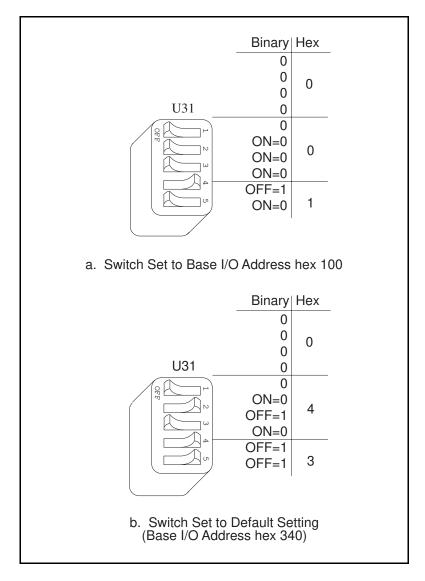

The base I/O address of the AT-MXI is the starting address of the AT-MXI configuration registers in PC AT I/O space. The base I/O address is determined by the position of the five switches at location U31, as shown in Figure 3-1. The switches are set at the factory for a base I/O address of 340 hex. Because the AT-MXI requires 32 bytes of consecutive I/O space for its internal registers, the factory configuration uses the I/O address space in the range of 340 to 35F hex.

Note: Check to determine that this I/O space is not already used by any other interface installed in your PC AT computer. If any equipment in your computer uses this I/O address space, you must change either the base I/O address of the AT-MXI or the I/O address space requirements of the other device. All PC AT devices must have a unique partition of the system's I/O address space.

Each switch in U31 (1 through 5) corresponds to one of the PC AT address lines (A5 through A9). The first switch (1) corresponds to address line A5, the next switch (2) corresponds to address line A6, and so on. The five least significant bits of the address (A4 through A0) are used by the AT-MXI to select the appropriate AT-MXI register and cannot be changed; therefore, bits A4 through A0 are always zeros when determining the base I/O address.

To change the base I/O address of the AT-MXI, press the side marked *OFF* to select a binary value of 1 for the corresponding address bit. Press the *ON* side of the switch to select a binary value of 0 for the corresponding address bit. Refer to Table 3-2.

Figure 3-2 shows two possible switch settings.

Figure 3-2. Base I/O Address Switch Settings

Table 3-2 lists the 24 possible switch settings, the corresponding base I/O address, and the I/O address space used for that setting. Notice that the base address settings that correspond to an I/O address in the range from 0 to FF hex are not listed. These addresses are used by logic on the PC AT motherboard and cannot be used by I/O adapter modules.

Table 3-2. Possible Base I/O Address Settings for the AT-MXI

| S<br>A9 | wite | ch S<br>S A7 | etti<br>A6 | ng<br>A5 | Base I/O Address<br>(hex) | I/O Ports Used (hex) |

|---------|------|--------------|------------|----------|---------------------------|----------------------|

| 0       | 1    | 0            | 0          | 0        | 100                       | 100 - 11F            |

| 0       | 1    | 0            | 0          | 1        | 120                       | 120 - 13F            |

| 0       | 1    | 0            | 1          | 0        | 140                       | 140 - 15F            |

| 0       | 1    | 0            | 1          | 1        | 160                       | 160 - 17F            |

| 0       | 1    | 1            | 0          | 0        | 180                       | 180 - 19F            |

| 0       | 1    | 1            | 0          | 1        | 1A0                       | 1A0 - 1BF            |

| 0       | 1    | 1            | 1          | 0        | 1C0                       | 1C0 - 1DF            |

| 0       | 1    | 1            | 1          | 1        | 1E0                       | 1E0 - 1FF            |

| 1       | 0    | 0            | 0          | 0        | 200                       | 200 - 21F            |

| 1       | 0    | 0            | 0          | 1        | 220                       | 220 - 23F            |

| 1       | 0    | 0            | 1          | 0        | 240                       | 240 - 25F            |

| 1       | 0    | 0            | 1          | 1        | 260                       | 260 - 27F            |

| 1       | 0    | 1            | 0          | 0        | 280                       | 280 - 29F            |

| 1       | 0    | 1            | 0          | 1        | 2A0                       | 2A0 - 2BF            |

| 1       | 0    | 1            | 1          | 0        | 2C0                       | 2C0 - 2DF            |

| 1       | 0    | 1            | 1          | 1        | 2E0                       | 2E0 - 2FF            |

| 1       | 1    | 0            | 0          | 0        | 300                       | 300 - 31F            |

| 1       | 1    | 0            | 0          | 1        | 320                       | 320 - 33F            |

| 1       | 1    | 0            | 1          | 0        | 340 (default)             | 340 - 35F            |

(continues)

| Switch Setting<br>A9 A8 A7 A6 A5 | Base I/O Address<br>(hex) | I/O Ports Used (hex) |

|----------------------------------|---------------------------|----------------------|

| 1 1 0 1 1                        | 360                       | 360 - 37F            |

| 1 1 1 0 0                        | 380                       | 380 - 39F            |

| 1 1 1 0 1                        | 3A0                       | 3A0 - 3BF            |

| 1 1 1 1 0                        | 3C0                       | 3C0 - 3DF            |

| 1 1 1 1 1                        | 3E0                       | 3E0 - 3FF            |

Table 3-2. Possible Base I/O Address Settings for the AT-MXI (Continued)

#### **Interrupt Level Selection**

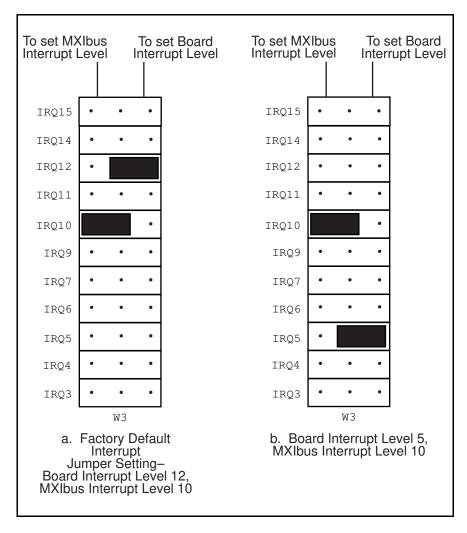

The AT-MXI interface board can use one, two, or none of the eleven interrupt levels of the PC AT I/O bus. Setting up an interrupt level for operation involves two steps. First you select the interrupt level by arranging the jumpers on an array of pins. Next you enable the interrupt level in the system software. Interrupt levels must be enabled by the system software before they can function. Any interrupt level not enabled is not driven by the AT-MXI and can be used by other devices, regardless of the positions of the jumpers.

Interrupt levels are selected by the position of two jumpers on the 3 by 11 array of pins labeled *W3*, located above the I/O card-edge connector on the AT-MXI (refer to Figure 3-1). The jumper farther from the card-edge connector is used to select which PC AT interrupt level is used to convey board status and error information. This jumper is set at the factory to a default level of 12.

The jumper on the W3 pin array closer to the I/O card-edge connector is used to select which PC AT interrupt level corresponds to the MXIbus interrupt signal  $IRQ^*$ . Because the MXIbus interrupt is also one of the conditions covered by the other jumper, a separate interrupt level for the MXIbus  $IRQ^*$  signal is normally not needed and is useful only if you want a different interrupt vector or priority for MXIbus interrupts. This jumper is set at the factory to a default level of 10.

Note: The AT-MXI does not have the ability to share interrupt levels with other devices. If you select an interrupt level by placing a jumper on a particular level and enable that level in software, no other device in the system can use that level. Make sure that no other devices in your system use the interrupt level(s) selected and enabled for use by the AT-MXI. If they do, change the interrupt level(s) of either the AT-MXI or the other devices.

The AT-MXI can use interrupt levels IRQ3, 4, 5, 6, 7, 9, 10, 11, 12, 14, and 15. Be careful when re-assigning interrupt levels on the AT-MXI. Notice that most PC ATs use interrupt level 6 for the diskette drive controller and interrupt level 14 for the hard disk drive controller. Other interrupt levels might be used by standard logic devices on the motherboard, so check your computer documentation before changing interrupt levels on the AT-MXI.

Once you have chosen an interrupt level, place the jumper on the appropriate pins to select that interrupt level. Use the two rows of pins farther from the card-edge connector to select the board interrupt level, and the two rows of pins closer to the card-edge connector to select the MXIbus interrupt level. Figure 3-3a shows the factory default interrupt jumper setting of the AT-MXI, with board interrupt level 12 and MXIbus interrupt level 10.

Figure 3-3. Board and MXIbus Interrupt Jumper Settings

To change to another interrupt level, remove the appropriate jumper from its current position and place it on the new posts. Figure 3-3b shows the board interrupt level changed to IRQ5.

#### **DMA Channel Selection**

The AT-MXI interface board can use one, two, or none of the seven DMA channels of the PC AT I/O bus. Setting up a DMA channel for operation involves two steps. First you select the DMA channel by arranging the jumpers on an array of pins. Next you enable the DMA channel in the system software. DMA channels must be enabled by the system software before they can function. Any DMA channel not enabled is not driven by the AT-MXI and can be used by other devices, regardless of the positions of the jumpers.

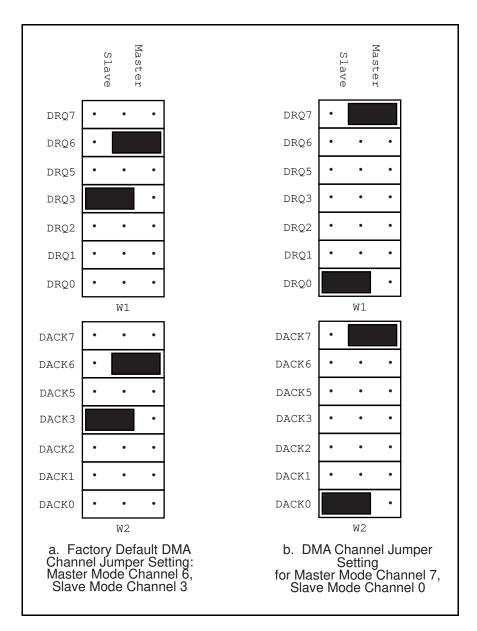

Select the DMA channels on the two 3 by 7 arrays of pins labeled *W1* and *W2*, located above the I/O card-edge connector on the AT-MXI (refer to Figure 3-1). Use the W1 array to select the DMA request line(s), and use the W2 array to select the DMA acknowledge line(s). You must position two jumpers to select a single DMA channel. The DMA ACKnowledge (DACK*n*) and DMA ReQuest (DRQ*n*) lines selected must have the same numeric suffix for proper operation. Therefore, make sure that the jumper positions on the W1 array are identical to the jumper positions on the W2 array.

#### **Master Mode Versus Slave Mode**

The AT-MXI can function as both a MXIbus master and a MXIbus slave. As a MXIbus master, the AT-MXI circuitry determines whether a PC AT cycle is to be mapped into a MXIbus cycle intended for some external MXIbus device, such as a VMEbus chassis. As a MXIbus slave, the AT-MXI circuitry determines whether an external device is attempting to access PC AT memory or I/O resources. When allocating DMA channels for use by the AT-MXI, keep in mind that master-mode and slave-mode operation are two distinct asynchronous functions and require different DMA channels.

The slave-mode DMA channel must be enabled to allow shared access to PC AT resources from an external MXIbus master. If you intend to share memory or I/O resources within the PC AT, you must select and enable a DMA channel for slave-mode operation.

You can use the master-mode DMA channel to perform high-speed block-mode transfers to or from external MXIbus devices. If you selected a master-mode DMA channel and enabled it in software, all block-mode transfers that map to the MXIbus will use the PC AT DMA controller to perform the block-mode move via that channel.

If the master-mode DMA channel is not enabled by software, the jumper-selected DMA channel is not used by the AT-MXI and can be used by other devices. Block-mode transfers can still be performed by using the processor's movs (move string) command or by writing a move string function. This does not necessarily mean that it will take any longer for the data to be transferred. In fact, most PC ATs can transfer data faster using the movs instruction than they can using the DMA controller. However, you may prefer to use the DMA controller if you have other useful work to do during a block-mode operation (such as when using a multitasking operating system).

The DMA jumpers are configured at the factory set to master-mode DMA Channel 6 and slave-mode DMA Channel 3.

Note: Seldom, if ever, can the AT-MXI share DMA channels with other devices. If you have selected a DMA channel by placing jumpers on that channel's request and acknowledge lines and enabled the channel in software, no other devices in your system should use that channel. If DMA channels conflict, change the DMA channel(s) used by either the AT-MXI or the other device(s).

The AT-MXI can use DMA Channels 0, 1, 2, 3, 5, 6, and 7. Be careful when re-assigning DMA channels on the AT-MXI. Notice that most PC ATs use DMA Channel 2 for the disk controller interface. Other DMA channels might be used by standard logic devices on the motherboard, so check your computer documentation before changing DMA channels.

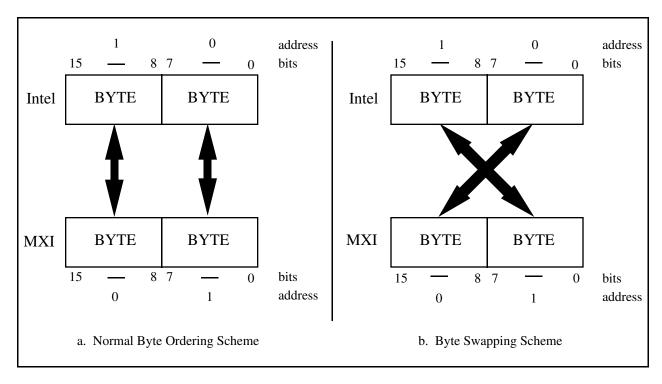

Notice that the PC AT makes a distinction between 8-bit and 16-bit DMA channels. The 8-bit channels are 0, 1, 2, and 3. The 16-bit channels are 5, 6, and 7. The master-mode DMA channel must be set on a level that matches the data width of the intended block transfers. It is preferable to use one of the 16-bit channels for the master-mode interface because a 16-bit DMA channel can transfer twice the amount of data in the same number of cycles. The slave-mode DMA channel is used only to request the PC AT bus for an alternate PC AT bus master cycle. It can use any available 8-bit or 16-bit channel regardless of the intended data width of the transfers.

Use the two rows of pins farther from the card-edge connector to select the master-mode DMA channel and the two rows closer to the card-edge connector to select the slave-mode DMA channel. Remember that the jumper positions should be identical on both the W1 and W2 arrays. Figure 3-4a shows the factory default DMA channel setting of the AT-MXI, with master-mode DMA Channel 6 and slave-mode DMA Channel 3.

Figure 3-4. DMA Channel Settings

To change to another DMA channel, remove both the DRQ and DACK jumpers from their current positions and place them on their new posts. Figure 3-4b displays the jumper position necessary for selecting master-mode DMA Channel 7 and slave-mode DMA Channel 0.

### **MXIbus Termination Option**

The AT-MXI has the ability to terminate the MXIbus signals on the interface board using terminating resistor networks in single inline packages (SIPs). You also have the option of terminating the MXIbus signals externally, by using an add-on module to aid in easy system reconfiguration. As mentioned in Chapter 1, only the first and last devices in the MXIbus daisy-chain should be terminated.

Because of the onboard termination option, you can install or remove terminating resistor networks from their sockets on the AT-MXI board. The board is shipped from the factory with these terminating resistor networks installed. If your AT-MXI is to be the first or last device in the MXIbus daisy-chain and you will *not* be using external terminating resistor networks, leave these internal resistor terminators in place. If the AT-MXI is *not* going to be an end device on the MXIbus daisy-chain, or if you *will* be using external terminating resistor networks, remove all six of the internal terminating resistor networks from their sockets. Store them in a safe place in case the MXIbus system configuration changes. When reinstalling the resistor networks, be sure to note the position of pin 1 of the socket and the terminators and make sure that the terminating networks are plugged firmly into their respective sockets.

Figure 3-5. MXIbus Terminating Networks

# **Step 3. Install the AT-MXI**

In the space provided here, record the settings of the base I/O address, the DMA channel(s), the interrupt level(s), and the position of the MXIbus termination option so that you will have them handy for future reference.

| AT-MXI                    | Setting |

|---------------------------|---------|

| Base I/O Address          |         |

| Board Interrupt Level     |         |

| MXIbus Interrupt Level    |         |

| Master DMA Channel        |         |

| Slave DMA Channel         |         |

| MXIbus Termination Option |         |

Before attempting to install the AT-MXI, notice that some MXIbus cable connector hoods are slightly wider than most standard connector hoods and might interfere with other cables installed in adjacent PC AT slots. Normally, this will only be a problem if the cable connector hoods for the adjacent slots are also oversized. When choosing a PC AT slot in which to install the AT-MXI, verify that the MXIbus cable connector will not interfere with cables and connectors in other PC AT slots. If necessary, reposition the boards in the system to prevent cabling conflicts. It may also help to install the AT-MXI in one of the end slots so that you will only have to contend with the cable connectors of one other board.

If you cannot configure the AT-MXI to co-exist in an existing PC AT system by repositioning the boards, you can use one of the MXIbus cable options with a straight-point connector hood on the cable end that attaches to the AT-MXI. The straight-point connector hood is narrower than the MXIbus dual-connector arrangement and provides an easier fit for many system configurations. However, this approach requires that the AT-MXI be the first device in the MXIbus daisy-chain because a cable with a straight-point connector end cannot accept another MXIbus cable to propagate the bus. Remember that the first device in the MXIbus daisy-chain must also be configured as the MXIbus System Controller.

The following instructions are general installation instructions. Consult the user or technical reference manual of your computer for specific instructions and warnings.

1. Plug in your PC AT computer before installing the AT-MXI. The plug grounds the computer and protects it from electrical damage while you are installing boards.

Warning: To protect both yourself and the computer from electrical hazards, the computer should remain off until you are finished installing the board.

- 2. Remove the top cover or access port to the PC AT I/O bus.

- 3. Select any available 16-bit full-length PC AT expansion slot. The 16-bit expansion slots have two card-edge receptacle connectors.

- 4. Locate the metal bracket that covers the cut-out in the back panel of the PC AT chassis for the slot you have selected. Remove and save the bracket-retaining screw and the bracket cover.

- 5. Before picking up the AT-MXI, touch the metal part of the power supply case inside the computer to discharge any static electricity that might be on your clothes or body.

- 6. Line up the AT-MXI with the MXIbus connector near the cut-out on the back panel and the other card edge lined up with the respective slot guide. Slowly push down on the front of the AT-MXI until its card edge connector is resting on the expansion slot receptacle. Using slow, evenly distributed pressure, press the AT-MXI straight down until it seats in the expansion slot.

- 7. Reinstall the bracket retaining screw to secure the AT-MXI to the back panel rail.

- 8. Check the installation.

- 9. Replace the computer cover.

# **Step 4. Connect the AT-MXI to the MXIbus**

After the AT-MXI has been installed, add it to the rest of your MXIbus system by connecting the MXIbus cable(s) to the MXIbus connector on the back of the board and to the other MXIbus devices in your system. The AT-MXI should be connected to the MXIbus system as described in Chapter 1. Be sure to tighten the screw locks on both sides of the cable connectors to ensure proper pin connection.

Once the AT-MXI is properly connected to the MXIbus system, you can restore power to the PC AT computer. The AT-MXI will remain offline on the MXIbus until it is initialized by the system software. Make sure that all devices on the MXIbus are powered up, initialized and operational before attempting to transfer data on the MXIbus.

This chapter contains detailed information on the use of the AT-MXI registers that are accessible via the PC AT bus using I/O operations. These registers are used to configure and control the board's operation and to obtain relevant status information on the state of the board and the MXIbus.

Another group of AT-MXI registers are accessible via MXIbus A16 space after the board has been properly configured. Refer to Chapter 5, *Programming Considerations*, for a description of these registers.

Note: If you plan to use the NI-VXI software package, you do not need to read this chapter

because the software routines automatically handle the configuration and maintenance of these registers.

# **Register Map**

The AT-MXI maps its registers into 32 consecutive byte-wide I/O locations starting at the I/O address established by the onboard switches (see Chapter 3). Some of the registers are read-only, while others are write-only registers. All register pairs can be accessed as either words or bytes except for the Signal Register, which must be accessed as a word, and the timer registers, which must be accessed as bytes. When a 16-bit register is accessed with a byte-wide operation, the least significant 8 bits are available at the even I/O address, while the most significant 8 bits are available at the odd I/O address.

The register map for the AT-MXI registers is shown in Table 4-1. The table gives the register name, the register address, the type of the register (read or write), and the size of the register in bits.

Table 4-1. AT-MXI Register Map

| Register Name                                                                                                                      | Mnemonic                    | Offset from<br>Base Address<br>(hex) | Туре                             | Size<br>(bits)       |

|------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------|----------------------------------|----------------------|

| Slave Mode Configuration Register Group:<br>Slave Mode Address Register<br>Slave Mode Address Mapping Register                     | SMAR<br>SMAMR               | 00<br>02                             | Write<br>Write                   | 16, 8<br>16, 8       |

| Master Mode Configuration Register Group:<br>Master Mode Address Page Register<br>Master Mode Address Modifier and Enable          | MMAPR<br>MMAMEN             | 04<br>06                             | Write<br>Write                   | 16, 8<br>16, 8       |

| Board Register Group: Signal Register Board Status Register Board Control Register                                                 | SR<br>BSR<br>BCR            | 08<br>0A<br>0A                       | Read<br>Read<br>Write            | 16<br>16, 8<br>16, 8 |

| Timer Register Group: Slave Mode Timer Register Master Mode Timer Register System Controller Timer Register Timer Control Register | SMTR<br>MMTR<br>SCTR<br>TCR | 10<br>12<br>14<br>16                 | Write<br>Write<br>Write<br>Write | 8<br>8<br>8          |

Table 4-1 shows the AT-MXI registers divided into four different register groups. These groups represent the four major logic blocks on the AT-MXI interface card. The Slave Mode Configuration Register Group is used to configure the AT-MXI interface so that it can accept MXIbus cycles intended for PC AT resources. The Master Mode Configuration Register Group is used to configure and control the AT-MXI when it is operating as a MXIbus master. The Board Register group consists of registers that are used to configure the different board options and obtain relevant status information from the AT-MXI board. The Timer Register Group is used to establish time limits for the different modes of operation of the AT-MXI. The following pages contain bit descriptions of each of the registers making up these groups.

#### **Register Description Format**

The remainder of this chapter discusses each of the AT-MXI registers in the order shown in Table 4-1. The individual register descriptions give the function, address, type, size, and bit map of the register, followed by a detailed description of each bit function.