#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

#### **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

**NB-DIO-24**

# AT-DIO-32F User Manual

High-Speed 32-Bit Parallel Digital I/O Interface for the PC

**April 1995 Edition**

**Part Number 320147-01**

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100

Technical support fax: (800) 328-2203

(512) 794-5678

#### **Branch Offices:**

Australia (03) 879 9422, Austria (0662) 435986, Belgium 02/757.00.20, Canada (Ontario) (519) 622-9310, Canada (Québec) (514) 694-8521, Denmark 45 76 26 00, Finland (90) 527 2321, France (1) 48 14 24 24, Germany 089/741 31 30, Italy 02/48301892, Japan (03) 3788-1921, Mexico 95 800 010 0793, Netherlands 03480-33466, Norway 32-84 84 00, Singapore 2265886, Spain (91) 640 0085, Sweden 08-730 49 70, Switzerland 056/20 51 51, Taiwan 02 377 1200, U.K. 0635 523545

#### **Limited Warranty**

The AT-DIO-32F is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### **Trademarks**

LabVIEW®, NI-DAQ®, and RTSI® are trademarks of National Instruments Corporation.

Product and company names listed are trademarks or trade names of their respective companies.

# Warning Regarding Medical and Clinical Use of National Instruments Products

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

## **Contents**

| About This Manual                             |      |

|-----------------------------------------------|------|

| Introduction to the AT-DIO-32F                | X1   |

| Organization of This Manual                   | X1   |

| Conventions Used in This Manual               |      |

| Related Documentation  Customer Communication |      |

| Customer Communication                        | XII  |

| Chapter 1                                     |      |

| Introduction                                  | 1_1  |

| What Your Kit Should Contain                  |      |

| Optional Software                             |      |

| Optional Equipment                            |      |

| Unpacking                                     |      |

| Onpacking                                     | 1-3  |

| Chapter 2                                     |      |

| Configuration and Installation                | 2-1  |

| Board Configuration                           |      |

| AT Bus Interface                              |      |

| Base I/O Address Selection                    | 2-4  |

| DMA Channel Selection                         |      |

| Interrupt Selection                           | 2-9  |

| RTSI Bus Clock Selection                      |      |

| Installation                                  |      |

| Signal Connections                            | 2-13 |

| I/O Connector Pin Description                 |      |

| Signal Connection Descriptions                | 2-14 |

| I/O Connector Electrical Specifications       | 2-10 |

| I/O Signals Rating                            |      |

| Input Signal Specifications                   | 2-16 |

| Output Signal Specifications                  | 2-16 |

| Timing Specifications                         | 2-16 |

| AT-DIO-32F Read and Write Timing              |      |

| Cabling                                       | 2-19 |

| Charter 2                                     |      |

| Chapter 3                                     |      |

| Theory of Operation                           |      |

| Address Decoder                               |      |

| Bus Transceivers                              |      |

| PC I/O Channel Control Circuitry              |      |

| Configuration and Status Registers            |      |

| Data Latches and Drivers                      |      |

| Onboard Counters                              |      |

| Digital I/O Connector                         | 3-4  |

| Handshaking Circuitry                     | 3-4         |

|-------------------------------------------|-------------|

| Level Mode                                |             |

| Leading Edge Mode                         |             |

| Trailing Edge Mode                        |             |

| Interrupt Control Circuitry               |             |

| DMA Control Circuitry                     |             |

| RTSI Bus Interface                        |             |

|                                           |             |

| Chapter 4                                 |             |

| Programming                               | <i>A</i> _1 |

| Register Map                              |             |

|                                           |             |

| Register Sizes                            |             |

| Register Description                      |             |

| Register Description Format               |             |

| Configuration and Status Register Group   |             |

| CFG2 Register                             |             |

| CFG2 Register                             |             |

| CFG4 Register                             |             |

| CFG4 Register                             |             |

| STAT Register                             |             |

| CNTINTCLR Register                        |             |

| DMACLR1 Register                          |             |

| DMACLR2 Register                          |             |

| Digital I/O Port Register Group           | 4-21        |

| Port A Register                           |             |

| Port B Register                           |             |

| Port C Register                           | 4-24        |

| Port D Register                           |             |

| RTSI Bus Register Group                   |             |

| RTSISHFT Register                         |             |

| RTSISTRB Register                         |             |

| Counter Register Group                    |             |

| CNTR1 Register (REQ1 Generator)           |             |

| CNTR2 Register (REQ2 Generator)           | 4-31        |

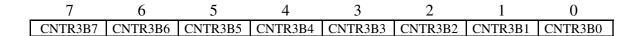

| CNTR3 Register (Timebase Generator)       |             |

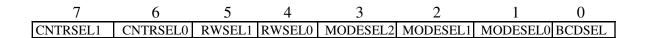

| CNTRCMD Register                          |             |

| Programming Considerations                |             |

| Initializing the AT-DIO-32F Board         |             |

| Mode 0 Programming                        |             |

| Mode 1 Programming                        |             |

| Leading Edge Mode                         |             |

| Trailing Edge Mode                        |             |

| Data Settling Delay                       | 4-43        |

| Programmed I/O Transfers                  | 4-43        |

| Input Data Latch                          |             |

| Interrupt Handling                        |             |

| DMA Transfers                             |             |

| 32-Bit Transfers                          |             |

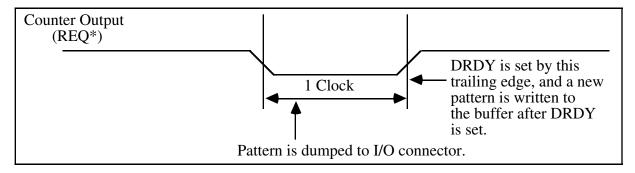

| Pattern Generation Using Onboard Counters | 4-49        |

| Pattern Generation Using an External Signal     |      |

|-------------------------------------------------|------|

| Programming the RTSI Bus Interface              |      |

| Programming the RTSI Bus Switch                 |      |

| Initializing the RTSI Bus Switch                | 4-55 |

| Appendix A                                      |      |

| Specifications                                  | A-1  |

|                                                 |      |

| Appendix B                                      |      |

| I/O Connector and Register Descriptions         |      |

| I/O Connector                                   |      |

| AT-DIO-32F Register Descriptions                |      |

| CFG1 Register                                   |      |

| CFG2 Register                                   |      |

| CFG3 Register                                   | B-2  |

| CFG4 Register                                   | B-2  |

| STAT Register                                   | B-3  |

| CNTINTCLR Register                              | B-3  |

| DMACLR1 Register                                | B-3  |

| DMACLR2 Register                                | B-3  |

| Port A Register                                 |      |

| Port B Register                                 |      |

| Port C Register                                 |      |

| Port D Register                                 |      |

| RTSISHFT Register                               |      |

| RTSISTRB Register                               |      |

| CNTR1 Register (REQ1 Generator)                 |      |

| CNTR2 Register (REQ2 Generator)                 |      |

| CNTR3 Register (Timebase Generator)             |      |

| CNTRCMD Register                                |      |

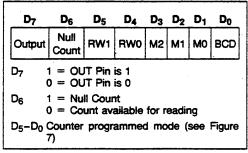

| Read-Back Command                               |      |

| Status Byte                                     |      |

| Status Dye                                      |      |

| Appendix C                                      |      |

| Application Notes                               | C-1  |

| Communicating with a Printer                    | C-1  |

| Cabling                                         |      |

| Sending Files to be Printed                     | C-2  |

| AT-DIO-32F to AT-DIO-32F 16-Bit Communications  | C-4  |

| Cabling                                         | C-5  |

| Sending and Receiving files with the AT-DIO-32F | C-5  |

| The AT-DIO-32F and I/O Module Racks             |      |

|                                                 |      |

| Appendix D                                      |      |

| Intel Data Sheet                                | D-1  |

| Appendix 1<br>Customer | E<br>C <b>ommunication</b>                                      | E-1      |

|------------------------|-----------------------------------------------------------------|----------|

| Glossary               | Gl                                                              | ossary-1 |

| Index                  |                                                                 | Index-1  |

|                        | Figures                                                         |          |

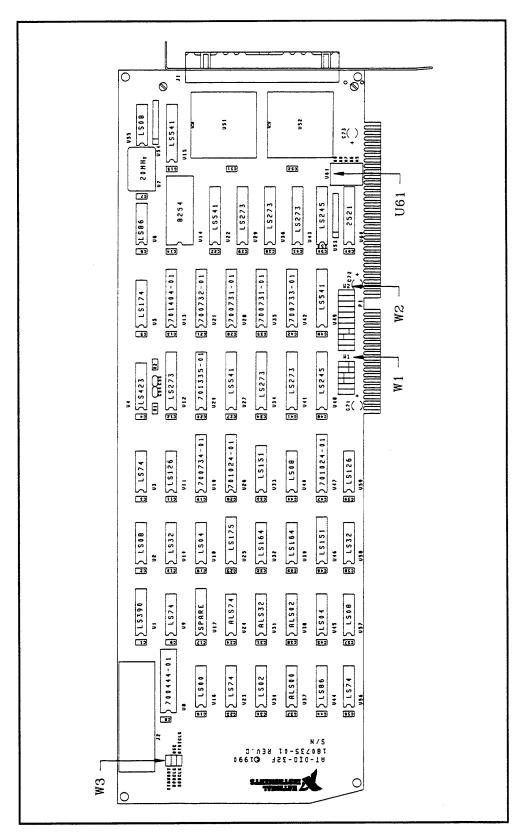

| Figure 2-1.            | AT-DIO-32-F Parts Locator Diagram                               | 2-3      |

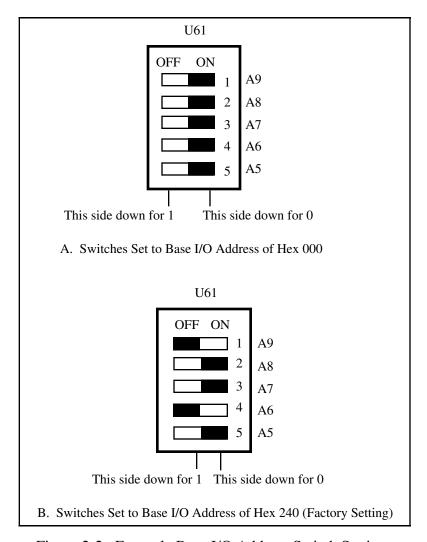

| Figure 2-2.            | Example Base I/O Address Switch Settings                        |          |

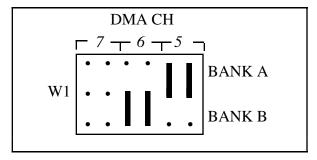

| Figure 2-3.            | DMA Jumper Settings for DMA Channels 5 and 6 (Factory Settings) |          |

| Figure 2-4.            | DMA Jumper Settings for DMA Channel 5 Only                      |          |

| Figure 2-5.            | DMA Jumper Settings for Disabling DMA Transfers                 |          |

| Figure 2-6.            | Interrupt Jumper Settings IRQ11 and IRQ12 (Factory Settings)    |          |

| Figure 2-7.            | Interrupt Jumper Settings for Disabling Interrupts              |          |

| Figure 2-8.            | Interrupt Jumper Setting IRQ5 Only                              |          |

| Figure 2-9.            | Disconnect from RTSI Bus Clock;                                 |          |

| C                      | Use Onboard Oscillator (Factory Settings)                       | 2-11     |

| Figure 2-10.           | Receive RTSI Bus Clock Signal                                   |          |

| Figure 2-11.           | Drive RTSI Bus Clock Signal with Onboard Oscillator             |          |

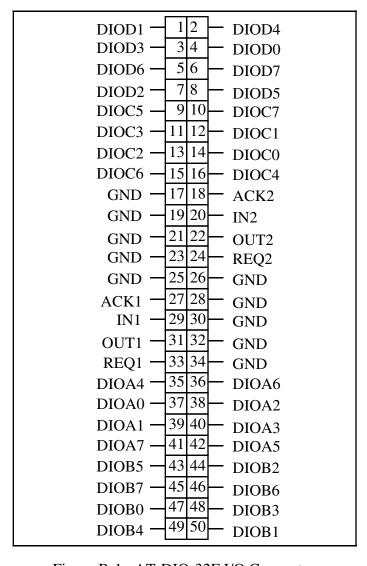

| Figure 2-12.           | Digital I/O Connector Pin Assignments                           |          |

| Figure 3-1.            | AT-DIO-32F Block Diagram                                        | 3-1      |

| Figure 3-2.            | AT-DIO-32F Clock Routing Scheme                                 |          |

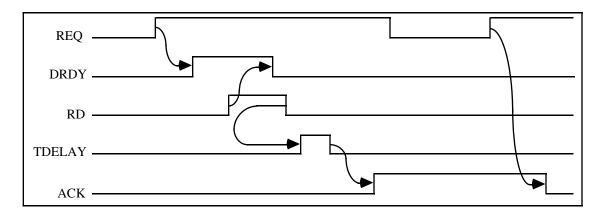

| Figure 3-3.            | Level Mode – Read                                               | 3-5      |

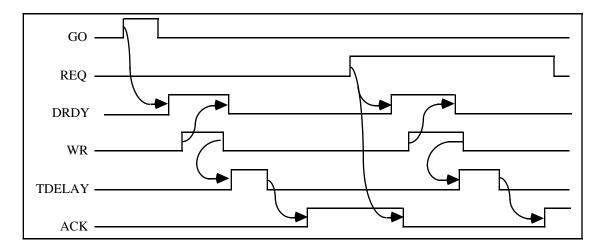

| Figure 3-4.            | Level Mode – Write                                              | 3-6      |

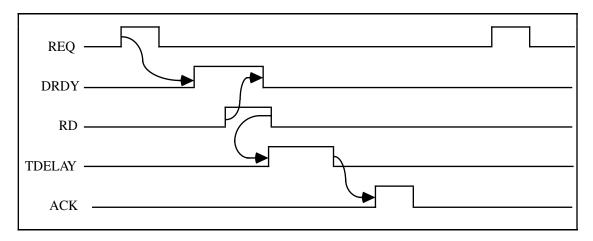

| Figure 3-5.            | Leading Edge Mode – Read                                        | 3-7      |

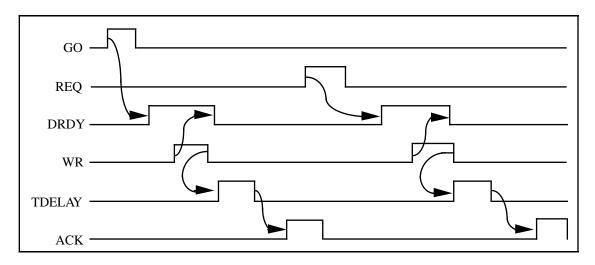

| Figure 3-6.            | Leading Edge Mode – Write                                       |          |

| Figure 3-7.            | Trailing Edge Mode – Read                                       |          |

| Figure 3-8.            | Trailing Edge Mode – Write                                      | 3-10     |

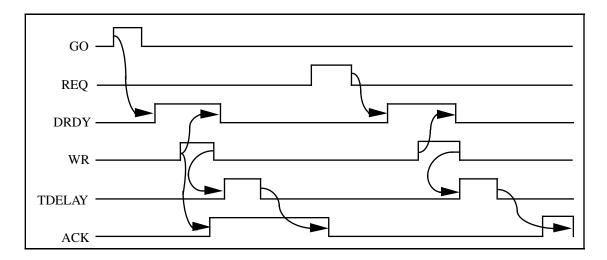

| Figure 4-1.            | Level Mode Write Handshake Timing                               | 4-40     |

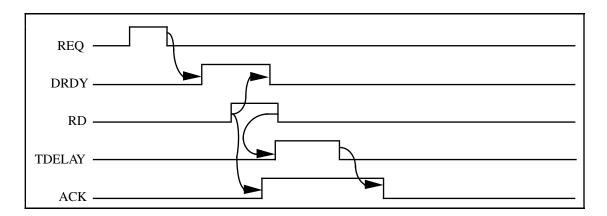

| Figure 4-2.            | Level Mode Read Handshake Timing                                |          |

| Figure 4-3.            | Leading Edge Mode Write Handshake Timing (LPULSEx cleared)      | 4-41     |

| Figure 4-4.            | Leading Edge Mode Read Handshake Timing (LPULSEx cleared)       |          |

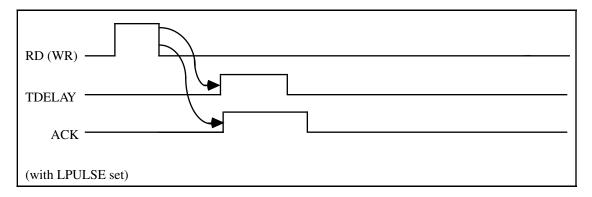

| Figure 4-5.            | Leading Edge Mode Read/Write ACK Pulse Width                    |          |

|                        | with LPULSEx of CFG4 Set                                        |          |

| Figure 4-6.            | Trailing Edge Mode Write Handshake Timing                       |          |

| Figure 4-7.            | Trailing Edge Mode Read Handshake Timing                        |          |

| Figure 4-8.            | Pattern Generation                                              |          |

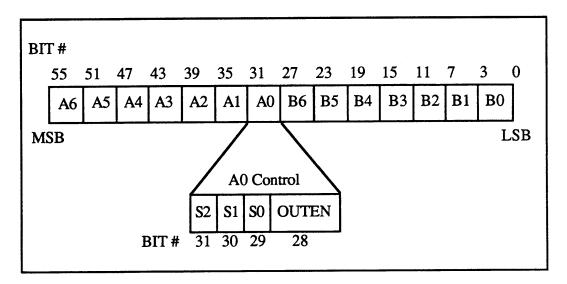

| Figure 4-9.            | RTSI Switch Control Pattern                                     | 4-54     |

| Figure B-1.            | AT-DIO-32F I/O Connector                                        | B-1      |

#### **Tables**

| Table 2-1. | AT-DIO-32F Factory-Set Jumper and Switch Settings                | 2-2  |

|------------|------------------------------------------------------------------|------|

| Table 2-2. | Default Settings of National Instruments Products for the PC     |      |

| Table 2-3. | Switch Settings with Corresponding Base I/O Address and          |      |

|            | Base I/O Address Space                                           | 2-7  |

| Table 2-4. | DMA Channels for the AT-DIO-32F                                  |      |

| Table 2-5. | Configurations for RTSI Bus Clock Selection                      | 2-11 |

| Table 4-1. | AT-DIO-32F Register Map                                          | 4-2  |

| Table 4-2. | CFG1 Data-Settling Time Settings                                 |      |

| Table 4-3. | Interrupt Condition and Status                                   |      |

| Table 4-4. | Counter 3 Programmable Frequency Output                          |      |

| Table 4-5. | Counters 1 and 2 Programmable Frequency Output (Source = 10 MHz) |      |

| Table 4-6. | RTSI Switch Signal Connections                                   |      |

| Table C-1. | Cable Specification for Connections to                           |      |

|            | 8, 16, or 24-channel I/O Module Racks                            | C-10 |

## **About This Manual**

#### Introduction to the AT-DIO-32F

The AT-DIO-32F is a high-speed, 32-bit, parallel, digital I/O interface. The AT-DIO-32F is a member of the National Instruments AT Series of PC AT I/O channel expansion boards for the IBM PC AT and compatible computers. These boards are designed for high-performance data acquisition and control for applications in laboratory testing, production testing, and industrial process monitoring and control.

This manual describes the installation, basic programming considerations, and theory of operation for the AT-DIO-32F. Example programs are provided in the C programming language.

## **Organization of This Manual**

The manual is divided into the following chapters and appendixes:

- Chapter 1, *Introduction*, describes the AT-DIO-32F, lists the contents of your AT-DIO-32F kit, and explains how to unpack the AT-DIO-32F kit.

- Chapter 2, *Configuration and Installation*, explains the installation of the AT-DIO-32F board into your computer, signal connections to the AT-DIO-32F board, and cable wiring.

- Chapter 3, *Theory of Operation*, explains the basic operation of the AT-DIO-32F circuitry.

- Chapter 4, *Programming*, describes in detail the address and function of each of the AT-DIO-32F control and status registers. This chapter also includes important information about programming the AT-DIO-32F.

- Appendix A, Specifications, lists the specifications for the AT-DIO-32F.

- Appendix B, *I/O Connector and Register Descriptions*, contains a description of the AT-DIO-32F I/O connector and references to the registers of the AT-DIO-32F.

- Appendix C, Application Notes, contains the application notes for the AT-DIO-32F board.

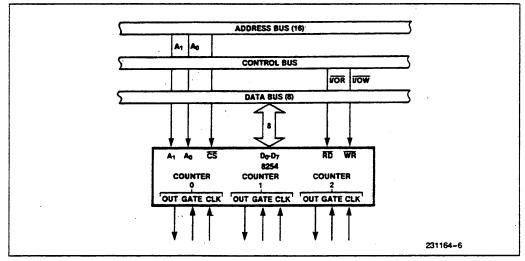

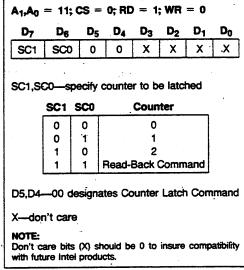

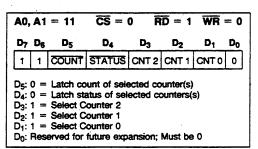

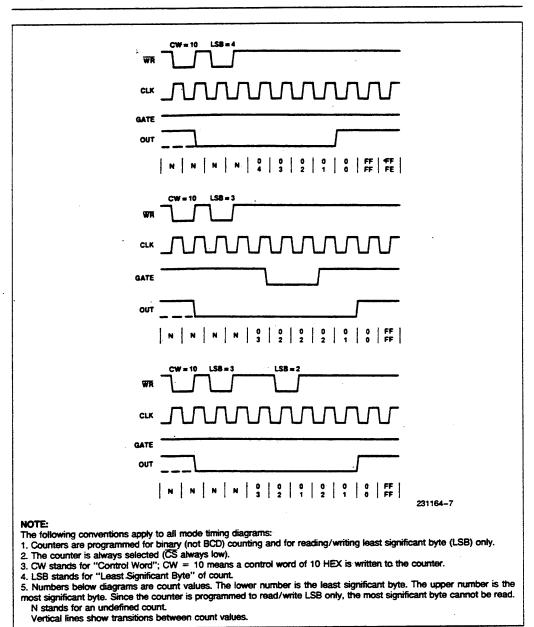

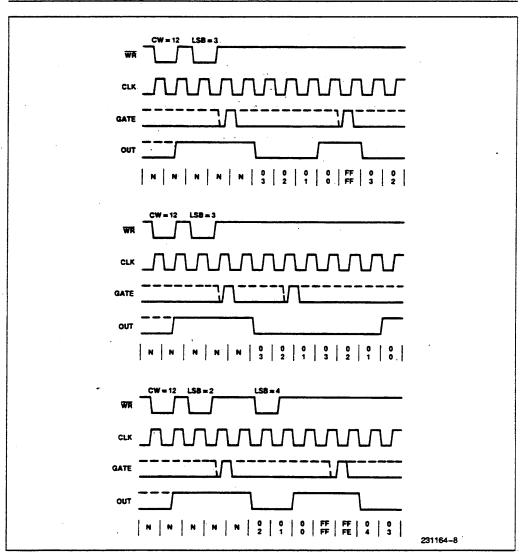

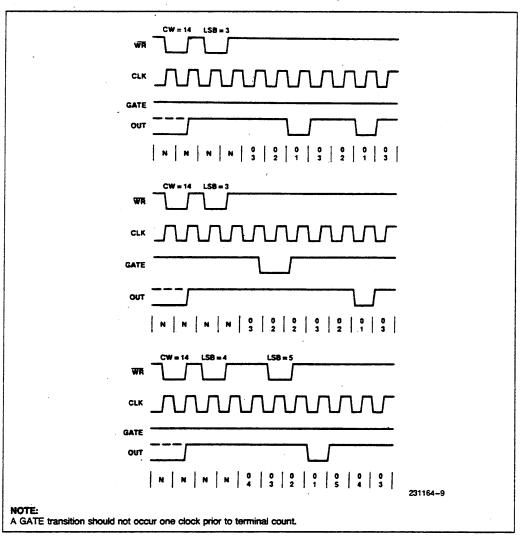

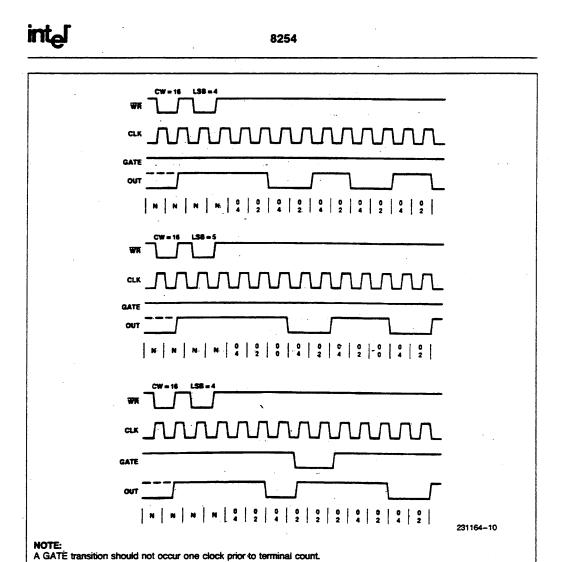

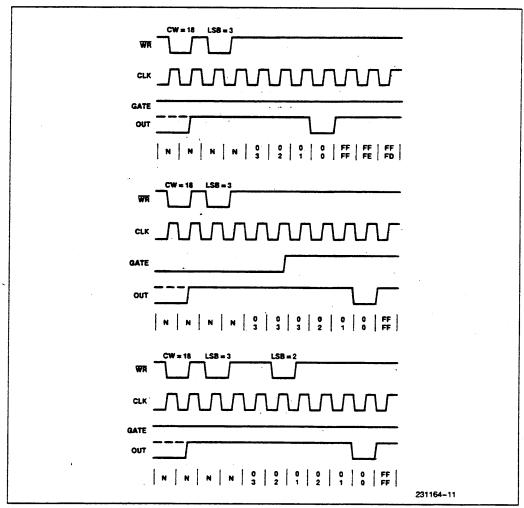

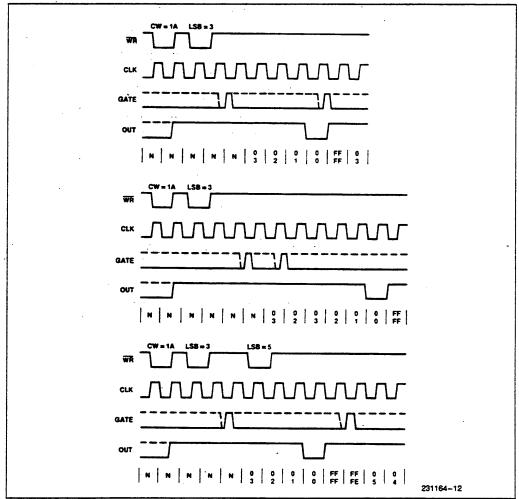

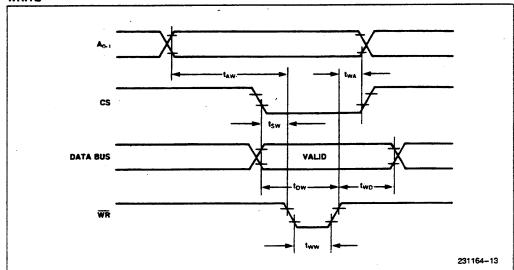

- Appendix D, *Intel Data Sheet*, contains the 8254 *Programmable Interval Timer* (Intel Corporation) data sheet. This counter/timer device is used on the AT-DIO-32F board.

- Appendix E, *Customer Communication*, contains forms for you to complete to facilitate communications with National Instruments concerning our products.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, symbols, and terms.

- The *Index* alphabetically lists topics covered in this manual, including the page where the topic can be found.

#### **Conventions Used in This Manual**

The following conventions are used throughout this manual:

italic Italic text denotes emphasis, a cross reference, or an introduction to a key

concept.

NI-DAQ is used throughout this manual to refer to the NI-DAQ software

for DOS/Windows/LabWindows unless otherwise noted

PC PC refers to the IBM PC AT and compatible computers.

#### **Related Documentation**

The following manual contains information that you may find helpful as you read this manual:

• IBM Personal Computer AT Technical Reference manual

You may also want to consult the following manual if you plan to program the Intel 8254-2 Counter/Timer used on the AT-DIO-32F:

• Intel 8254 System Timing Controller technical manual

#### **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix E, *Customer Communication*, at the end of this manual.

## Chapter 1 Introduction

This chapter describes the AT-DIO-32F, lists the contents of your AT-DIO-32F kit, and explains how to unpack the AT-DIO-32F kit.

The AT-DIO-32F is a high-speed, 32-bit, parallel, digital I/O interface board for the PC. The 32 lines of digital I/O are organized into four 8-bit ports. With the various handshaking options available, the AT-DIO-32F is compatible with a wide range of peripheral devices and other computers. The AT-DIO-32F can be used for interrupt handling and DMA transfers on two DMA channels. Onboard counters can be used for pattern generation. A RTSI bus interface can transfer signals from other AT Series boards to the AT-DIO-32F.

All digital I/O is transferred through a standard, 50-pin, male connector. The pin assignments for this connector are compatible with the DEC DRV11J parallel interface and most standard 32-channel digital I/O applications.

The AT-DIO-32F can be used in a wide range of digital I/O applications. With the AT-DIO-32F, a digital pattern generator can be implemented, or the PC can be interfaced to any of the following:

- Other computers

- Another IBM PC/XT, PC AT, or compatible computer with a National Instruments PC-DIO-24 or AT-DIO-32F

- IBM Personal System/2 computer with a National Instruments MC-DIO-24 or MC-DIO-32F

- Apple Macintosh II computer with a National Instruments NB-DIO-24 or NB-DIO-32F

- DEC, UNIBUS, or Q-BUS system with a 16-bit interface

- DEC LSI-11 microcomputer with a 32-bit DRV11J interface

- Any other computer with an 8-bit, 16-bit, or 32-bit parallel interface

- Centronics-compatible printers and plotters

- Panel meters

- Instruments and test equipment with BCD readouts and/or controls

- Opto-isolated solid-state relays and I/O module mounting racks

With the AT-DIO-32F, the PC can serve as a digital I/O system controller for laboratory testing, production testing, and industrial process monitoring and control.

Introduction Chapter 1

#### What Your Kit Should Contain

The contents of the AT-DIO-32F kit (part number 776246-01) are listed as follows.

| Kit Component                                                                                                                                                                                                            | Part Number                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| AT-DIO-32F board AT-DIO-32F User Manual NI-DAQ software for DOS/Windows/LabWindows, with manuals NI-DAQ Software Reference Manual for DOS/Windows/LabWindows NI-DAQ Function Reference Manual for DOS/Windows/LabWindows | 180735-01<br>320147-01<br>776250-01<br>320498-01<br>320499-01 |

If your kit is missing any of the components, contact National Instruments.

Your AT-DIO-32F is shipped with the NI-DAQ software for DOS/Windows/LabWindows. NI-DAQ has a library of functions that can be called from your application programming environment. These functions include routines for analog input (A/D conversion), buffered data acquisition (high-speed A/D conversion), analog output (D/A conversion), waveform generation, digital I/O, counter/timer, SCXI, RTSI, and self-calibration. NI-DAQ maintains a consistent software interface among its different versions so you can switch between platforms with minimal modifications to your code. NI-DAQ comes with language interfaces for Professional BASIC, Turbo Pascal, Turbo C, Turbo C++, Borland C++, and Microsoft C for DOS; and Visual Basic, Turbo Pascal, Microsoft C with SDK, and Borland C++ for Windows. NI-DAQ software is on high-density 5.25 in. and 3.5 in. diskettes.

Chapter 1 Introduction

## **Optional Software**

This manual contains complete instructions for directly programming the AT-DIO-32F. Normally, however, you should not need to read the low-level programming details in the user manual because the NI-DAQ software package for controlling the AT-DIO-32F is included with the board. Using NI-DAQ is quicker and easier than and as flexible as using the low-level programming described in Chapter 4, *Programming*.

You can use the AT-DIO-32F with LabVIEW for Windows or LabWindows for DOS. LabVIEW and LabWindows are innovative program development software packages for data acquisition and control applications. LabVIEW uses graphical programming, whereas LabWindows enhances Microsoft C and QuickBASIC. Both packages include extensive libraries for data acquisition, instrument control, data analysis, and graphical data presentation.

Part numbers for these software packages are listed in the following table.

| Software                                                                                       | Part Number                         |

|------------------------------------------------------------------------------------------------|-------------------------------------|

| LabVIEW for Windows<br>LabWindows                                                              | 776670-01                           |

| Standard package Advanced Analysis Library Standard package with the Advanced Analysis Library | 776473-01<br>776474-01<br>776475-01 |

Introduction Chapter 1

## **Optional Equipment**

| Equipment                                                                                                                   |                                 | Part Number                                      |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------|--------------------------------------------------|

| Signal Conditioning Accessories                                                                                             |                                 |                                                  |

| Cable Adapter Board for Signal C<br>SC-2052 and 50-conductor cable                                                          | Conditioning:<br>0.5 m<br>1.0 m | 776335-02<br>776335-12                           |

| Optically-Isolated Digital Input: SC-2060 and 26-conductor cable                                                            | 0.2 m<br>0.4 m                  | 776336-00<br>776336-10                           |

| Optically-Isolated Digital Output SC-2061 and 26-conductor cable                                                            | 0.2 m<br>0.4 m                  | 776336-01<br>776336-11                           |

| Electromechanical Relay Digital SC-2062 and 26-conductor cable                                                              |                                 | 776336-02<br>776336-12                           |

| General-Purpose Termination Bro SC-2072 with 50-conductor cable                                                             |                                 | 776358-02<br>776358-12                           |

| Digital Signal Conditioning Mod-<br>SSR Series mounting rack and 1.0<br>32-channel<br>24-channel<br>16-channel<br>8-channel |                                 | 776290-32<br>776290-24<br>776290-16<br>776290-08 |

| CB-50 I/O connector block (50 so with 0.5 m type NB1 cable with 1.0 m type NB1 cable                                        | crew terminals)                 | 776164-01<br>776164-02                           |

| AT Series RTSI bus cables for<br>2 boards<br>3 boards<br>4 boards<br>5 boards                                               |                                 | 776249-02<br>776249-03<br>776249-04<br>776249-05 |

| Standard ribbon cable                                                                                                       | 0.5 m<br>1.0 m                  | 180524-05<br>180524-10                           |

| Shielded ribbon cable                                                                                                       | 0.5 m*<br>1.0 m*                | 180554-05<br>180554-10                           |

| Ribbon cable with edge connection                                                                                           | on at one end 0.5 m             |                                                  |

<sup>\*</sup> The AT-DIO-32F is equipped with an EMI shield on the I/O connector that can be used to connect the shield of a shielded ribbon cable to the computer chassis. Shielded ribbon cables are necessary to meet FCC Class A Emission Limits.

Chapter 1 Introduction

Refer to the *Cabling* section in Chapter 2, *Configuration and Installation*, for additional information on cabling and connectors.

## Unpacking

Your AT-DIO-32F board is shipped in an antistatic plastic package to prevent electrostatic damage to the board. Several components on the board can be damaged by electrostatic discharge. To avoid such damage in handling the board, take the following precautions:

- Touch the plastic package to a metal part of your PC chassis before removing the board from the package.

- Remove the board from the package and inspect the board for loose components or any other sign of damage. Notify National Instruments if the board appears damaged in any way. *Do not* install a damaged board into your computer.

# **Chapter 2 Configuration and Installation**

This chapter explains the installation of the AT-DIO-32F board into your computer, signal connections to the AT-DIO-32F board, and cable wiring.

## **Board Configuration**

The AT-DIO-32F contains three jumpers and one DIP switch to configure the AT bus interface and board clock settings. The jumpers are shown in the parts locator diagram in Figure 2-1. Jumper W3 selects the clock signal used by the board and the clock pin on the RTSI bus. Jumper W1 selects the DMA channel, and jumper W2 selects the interrupt enable lines. The DIP switch is used to set the base I/O address.

#### **AT Bus Interface**

The AT-DIO-32F is configured at the factory to use a base I/O address of hex 240, to use interrupt lines 11 and 12, to use DMA channels 5 and 6, and to disconnect the board from the RTSI clock. These settings (shown in Table 2-1) are suitable for most systems. However, if your system has other hardware at this base I/O address, interrupt level, or DMA channel, you need to change these settings on the AT-DIO-32F (as described in the following pages) or on the other hardware. Record your settings in the *AT-DIO-32F Hardware and Software Configuration Form* in Appendix E, *Customer Communication*.

Table 2-1. AT-DIO-32F Factory-Set Jumper and Switch Settings

| Base I/O Address | Hex 240 (factory setting)                                                  | U61  A9 A8 A7 A6 A5  The black side indicates the side that is pushed down. |

|------------------|----------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| DMA Channel      | Bank A = Channel 5 Bank B = Channel 6 (factory setting)                    | W1: Upper-right two rows W1: Lower-middle two rows                          |

| Interrupt Level  | Lines 11 and 12 selected (factory setting)                                 | W2: Row 4 from left W2: Row 3 from left                                     |

| RTSI Clock       | Disconnect board from RTSI clock; use onboard oscillator (factory setting) | W3: STANDBY,<br>BRDCLK-OSC                                                  |

Figure 2-1. AT-DIO-32F Parts Locator Diagram

#### **Base I/O Address Selection**

The base I/O address for the AT-DIO-32F is determined by the switches at position U61 (see Figure 2-1). The switches are set at the factory for the base I/O address hex 240. This factory setting is used as the default base I/O address value by National Instruments software packages using the AT-DIO-32F. The AT-DIO-32F uses the base I/O address space hex 240 through 25F with the factory setting.

Note: Verify that this space is not already used by other equipment installed in your computer. If any equipment in your computer uses this base I/O address space, change the base I/O address of the AT-DIO-32F or of the other device. If you change the AT-DIO-32F base I/O address, make a corresponding change to any software packages you use with the AT-DIO-32F. Table 2-2 lists the default settings of other National Instruments products for the PC. For more information about the I/O address of your PC, refer to the technical reference manual for your computer.

Each switch in U61 corresponds to one of the address lines A9 through A5. Press the side marked OFF to select a binary value of 1 for the corresponding address bit. Press the other side of the switch to select a binary value of 0 for the corresponding address bit. Figure 2-2 shows two possible switch settings. The shaded portion indicates the side of the switch that is pressed down.

Figure 2-2. Example Base I/O Address Switch Settings

The five LSBs of the address (A4 through A0) are decoded by the AT-DIO-32F to select the appropriate AT-DIO-32F register. To change the base I/O address, remove the plastic cover on U61, press each switch to the desired position, verify that each switch is completely pressed down, and replace the plastic cover. Make a note of the new AT-DIO-32F base I/O address for use when configuring the AT-DIO-32F software (a form is included for you in Appendix E). Table 2-3 lists the possible switch settings, the corresponding base I/O address, and the base I/O address space used for that setting.

Table 2-2. Default Settings of National Instruments Products for the PC

| Board        | DMA Channel   | Interrupt Level | Base I/O Address |

|--------------|---------------|-----------------|------------------|

| AT-A2150     | None*         | None*           | 120 hex          |

| AT-AO-6/10   | Channel 5     | Lines 11, 12    | 1C0 hex          |

| AT-DIO-32F   | Channels 5, 6 | Lines 11, 12    | 240 hex          |

| AT-DSP2200   | None*         | None*           | 120 hex          |

| AT-GPIB      | Channel 5     | Line 11         | 2C0 hex          |

| AT-MIO-16    | Channels 6, 7 | Line 10         | 220 hex          |

| AT-MIO-16D   | Channels 6, 7 | Lines 5, 10     | 220 hex          |

| AT-MIO-16F-5 | Channels 6, 7 | Line 10         | 220 hex          |

| AT-MIO-16X   | None*         | None*           | 220 hex          |

| AT-MIO-64F-5 | None*         | None*           | 220 hex          |

| GPIB-PCII    | Channel 1     | Line 7          | 2B8 hex          |

| GPIB-PCIIA   | Channel 1     | Line 7          | 02E1 hex         |

| GPIB-PCIII   | Channel 1     | Line 7          | 280 hex          |

| Lab-PC       | Channel 3     | Line 5          | 260 hex          |

| PC-DIO-24    | None          | Line 5          | 210 hex          |

| PC-DIO-96    | None          | Line 5          | 180 hex          |

| PC-LPM-16    | None          | Line 5          | 260 hex          |

| PC-TIO-10    | None          | Line 5          | 1A0 hex          |

<sup>\*</sup> These settings are software configurable and are disabled at startup time.

Table 2-3. Switch Settings with Corresponding Base I/O Address and Base I/O Address Space

| Switch Setting<br>A9 A8 A7 A6 A5 | Base I/O Address<br>(hex) | Base I/O Address<br>Space Used (hex) |

|----------------------------------|---------------------------|--------------------------------------|

| 0 0 0 0 0                        | 000                       | 000 - 01F                            |

| 0 0 0 0 1                        | 020                       | 020 - 03F                            |

| 0 0 0 1 0                        | 040                       | 040 - 05F                            |

| 0 0 0 1 1                        | 060                       | 060 - 07F                            |

| 0 0 1 0 0                        | 080                       | 080 - 09F                            |

| 0 0 1 0 1                        | 0A0                       | 0A0 - 0BF                            |

| 0 0 1 1 0                        | 0C0                       | 0C0 - 0DF                            |

| 0 0 1 1 1                        | 0E0                       | 0E0 - 0FF                            |

| 0 1 0 0 0                        | 100                       | 100 - 11F                            |

| 0 1 0 0 1                        | 120                       | 120 - 13F                            |

| 0 1 0 1 0                        | 140                       | 140 - 15F                            |

| 0 1 0 1 1                        | 160                       | 160 - 17F                            |

| 0 1 1 0 0                        | 180                       | 180 - 19F                            |

| 0 1 1 0 1                        | 1A0                       | 1A0 - 1BF                            |

| 0 1 1 1 0                        | 1C0                       | 1C0 - 1DF                            |

| 0 1 1 1 1                        | 1E0                       | 1E0 - 1FF                            |

| 1 0 0 0 0                        | 200                       | 200 - 21F                            |

| 1 0 0 0 1                        | 220                       | 220 - 23F                            |

| 1 0 0 1 0                        | 240                       | 240 - 25F                            |

| 1 0 0 1 1                        | 260                       | 260 - 27F                            |

| 1 0 1 0 0                        | 280                       | 280 - 29F                            |

| 1 0 1 0 1                        | 2A0                       | 2A0 - 2BF                            |

| 1 0 1 1 0                        | 2C0                       | 2C0 - 2DF                            |

| 1 0 1 1 1                        | 2E0                       | 2E0 - 2FF                            |

| 1 1 0 0 0                        | 300                       | 300 - 31F                            |

| 1 1 0 0 1                        | 320                       | 320 - 33F                            |

| 1 1 0 1 0                        | 340                       | 340 - 35F                            |

| 1 1 0 1 1                        | 360                       | 360 - 37F                            |

| 1 1 1 0 0                        | 380                       | 380 - 39F                            |

| 1 1 1 0 1                        | 3A0                       | 3A0 - 3BF                            |

| 1 1 1 1 0                        | 3C0                       | 3C0 - 3DF                            |

| 1 1 1 1 1                        | 3E0                       | 3E0 - 3FF                            |

**Note:** Base I/O address values hex 000 through 0FF are reserved for system use. Base I/O address values hex 100 through 3FF are available on the I/O channel.

#### **DMA Channel Selection**

The DMA channel used by the AT-DIO-32F is selected by jumpers on W1 (see Figure 2-1). The AT-DIO-32F is set at the factory to use DMA Channels 5 and 6. These are the default DMA channels used by the AT-DIO-32F software handler. Verify that these DMA channels are not also used by equipment already installed in your computer. If any device uses DMA Channel 5 and/or Channel 6, change the DMA channel used by either the AT-DIO-32F or the other device.

The AT-DIO-32F hardware can only use Channels 5, 6, and 7 as DMA channels. Notice that these are the three available 16-bit channels on the PC I/O channel. The AT-DIO-32F *does not* use and *cannot* be configured to use the 8-bit DMA channels on the PC I/O channel.

Each DMA channel consists of two signal lines as shown in Table 2-4.

| DMA     | DMA         | DMA     |

|---------|-------------|---------|

| Channel | Acknowledge | Request |

| 5       | DACK5       | DRQ5    |

| 6       | DACK6       | DRQ6    |

| 7       | DACK7       | DRQ7    |

Table 2-4. DMA Channels for the AT-DIO-32F

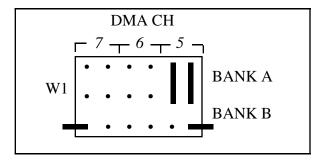

Two jumpers must be installed to select a DMA channel. The switch BANK A is used to select the DMA channel for Group 1, and the switch BANK B is used to select the DMA channel for Group 2. Figure 2-3 displays the jumper positions for selecting DMA Channels 5 and 6. In this setting, Group 1 uses DMA Channel 5, and Group 2 uses DMA Channel 6.

Figure 2-3. DMA Jumper Settings for DMA Channels 5 and 6 (Factory Settings)

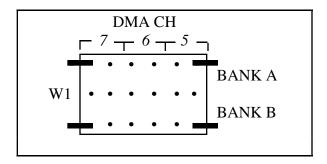

If you want to use only one DMA channel, then place the configuration jumpers in the positions shown in Figure 2-4.

Figure 2-4. DMA Jumper Settings for DMA Channel 5 Only

If you do not want to use DMA for AT-DIO-32F transfers, then place the configuration jumpers in the positions shown in Figure 2-5.

Figure 2-5. DMA Jumper Settings for Disabling DMA Transfers

#### **Interrupt Selection**

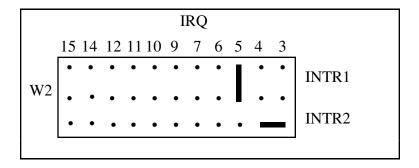

The AT-DIO-32F board can connect to one or two of any of the 11 interrupt lines of the PC I/O channel. The interrupt lines are selected by jumper W2, which is located above the I/O slot edge connector on the AT-DIO-32F (see Figure 2-1). To use the interrupt capability of the AT-DIO-32F, select one or two interrupt lines and place the jumpers in the appropriate positions to enable the particular interrupt lines. The Group 1 interrupt uses the upper two rows of jumper W2, and the Group 2 interrupt uses the lower two rows of jumper W2.

The AT-DIO-32F can share interrupt lines with other devices by using a tri-state driver to drive its selected interrupt line. The AT-DIO-32F hardware can use the following interrupt lines: IRQ3, IRQ4, IRQ5, IRQ6, IRQ7, IRQ9, IRQ10, IRQ11, IRQ12, IRQ14, and IRQ15.

**Note:** *Do not* use interrupt line 6 or interrupt line 14. Interrupt line 6 is used by the diskette drive controller, and interrupt line 14 is used by the hard disk controller on most PCs.

Once you have selected an interrupt level, place the interrupt jumper on the appropriate pins to enable the interrupt line.

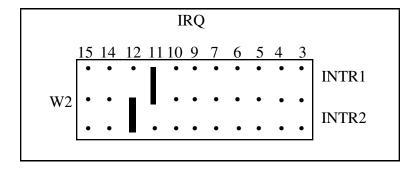

The default interrupt lines are IRQ11 for Group 1 and IRQ12 for Group 2. These lines are selected by placing the jumper on the pins in row 11 of W1 and row 12 of W1, respectively. Figure 2-6 shows the default interrupt jumper setting IRQ11 and IRQ12. To change the default setting, remove the jumpers from their current settings and place them on the new pins.

Figure 2-6. Interrupt Jumper Settings IRQ11 and IRQ12 (Factory Settings)

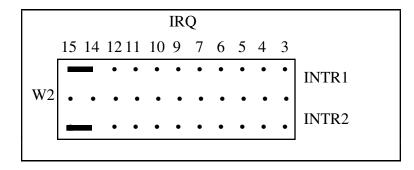

If you do not want to use interrupts, place the jumper on W2 in the positions shown in Figure 2-7. This setting disables the AT-DIO-32F from asserting any interrupt lines on the PC I/O channel.

Figure 2-7. Interrupt Jumper Settings for Disabling Interrupts

Figure 2-8 shows the Group 2 interrupts disabled, and interrupt line 5 is selected for Group 1.

Figure 2-8. Interrupt Jumper Setting IRQ5 Only

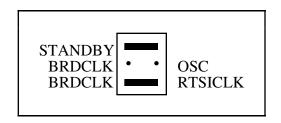

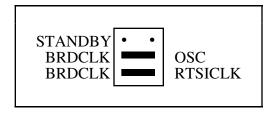

#### **RTSI Bus Clock Selection**

When multiple AT Series boards are connected via the RTSI bus, you may want to have all the boards use the same 10-MHz clock. This arrangement is useful for applications that require counter/timer synchronization between boards. Each AT Series board with a RTSI bus interface has an onboard oscillator. Thus, one board can drive the RTSI bus clock signal, and the other boards can receive this signal or disconnect from it.

The configuration for jumper W3 determines whether a board drives the onboard 10-MHz clock onto the RTSI bus, receives the RTSI bus clock, or disconnects from the RTSI bus clock. This clock source, whether a local or RTSI signal, is then used as the onboard counter frequency source.

The jumper selections are shown in Table 2-5.

Table 2-5. Configurations for RTSI Bus Clock Selection

| Configuration                                              | W3                                    |

|------------------------------------------------------------|---------------------------------------|

| Disconnect board from RTSI bus clock; use local oscillator | STANDBY, BRDCLK-OSC (factory setting) |

| Receive RTSI bus clock signal                              | STANDBY, BRDCLK-RTSICLK               |

| Drive RTSI bus clock signal with local oscillator          | BRDCLK-OSC, BRDCLK-RTSICLK            |

Figures 2-9, 2-10, and 2-11 show the jumper positions for each of the preceding configurations.

Figure 2-9. Disconnect from RTSI Bus Clock; Use Onboard Oscillator (Factory Settings)

Figure 2-10. Receive RTSI Bus Clock Signal

Figure 2-11. Drive RTSI Bus Clock Signal with Onboard Oscillator

#### **Installation**

The AT-DIO-32F can be installed in any available 16-bit expansion slot (AT style) in your computer. The AT-DIO-32F *does not* work if installed in an 8-bit expansion slot (PC style). After you have made any necessary changes, verified, and recorded the switch settings and jumper settings (a form is given in Appendix E), you are ready to install the AT-DIO-32F. The following are general installation instructions, but consult the user manual or technical reference manual of your PC for specific instructions and warnings.

- 1. Turn off your computer.

- 2. Remove the top cover or access port to the I/O channel.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Insert the AT-DIO-32F into a 16-bit slot. It may be a tight fit, but do not force the board into place.

- 5. If you want to connect multiple AT Series boards, attach a RTSI cable to the RTSI connector at this time.

- 6. Screw the mounting bracket of the AT-DIO-32F to the back panel rail of the computer.

- 7. Check the installation.

- 8. Replace the cover.

The AT-DIO-32F board is installed and ready for operation.

## **Signal Connections**

#### **I/O Connector Pin Description**

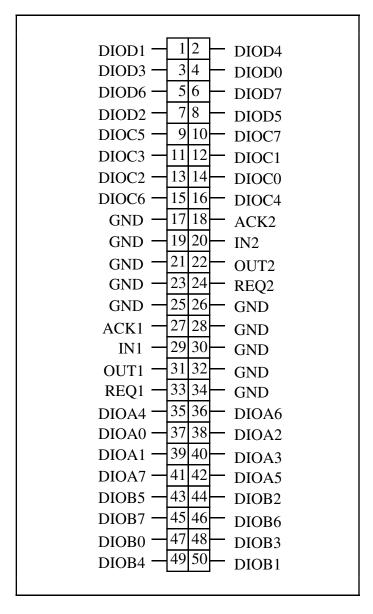

Figure 2-12 shows the pin assignments for the AT-DIO-32F digital I/O connector.

Warning: Connections that exceed any of the maximum ratings of input or output signals on the AT-DIO-32F may result in damage to the AT-DIO-32F board and to the PC.

Maximum input ratings for each signal are given in this chapter under the discussion of that signal. National Instruments is not liable for any damages resulting from any such signal connections.

Figure 2-12. Digital I/O Connector Pin Assignments

## **Signal Connection Descriptions**

| Pins  | Signal Names | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 43-50 | DIOB<07>     | Bidirectional data lines for Port B. DIOB7 is the MSB; DIOB0 is the LSB.                                                                                                                                                                                                                                                                                                                               |

| 35-42 | DIOA<07>     | Bidirectional data lines for Port A. DIOA7 is the MSB; DIOA0 is the LSB.                                                                                                                                                                                                                                                                                                                               |

| 33    | REQ1         | Input handshaking request line for Group 1. When the AT-DIO-32F is in write mode, the external device activates this signal to indicate that it is ready to receive data. When the AT-DIO-32F is in read mode, the external device activates this signal if data can be read on the data lines. The polarity of this signal is changed by the INVRQ1 bit in the CFG1 Register.                         |

| 31    | OUT1         | Extra output signal #1. This additional output signal can be connected to extra control lines, and is controlled by the OUT1 bit in the CFG1 Register.                                                                                                                                                                                                                                                 |

|       | IN1          | Extra input signal #1.  This additional input signal is pulled up to +5 V by an onboard resistor. The status of this signal can be obtained by reading the IN1 bit in the STAT Register. This input signal can be used as an extra input signal line or as an external enable signal of Counter 1 of the board.                                                                                        |

| 27    | ACK1         | Output handshaking acknowledge signal for Group 1. When the AT-DIO-32F is in write mode, this signal becomes active when data has been written to the data lines. When the AT-DIO-32F is in read mode, this signal becomes active when the available data on the data lines has been read. The polarity of this signal is configured by the INVACK1 bit in the CFG1 Register.                          |

| 24    | REQ2         | Input handshaking request line for Group 2. When the AT-DIO-32F is in write mode, the external device should activate this signal to indicate that it is ready to receive data. When the AT-DIO-32F is in read mode, the external device should activate this signal if data is available to be read on the data lines. The polarity of this signal is changed by the INVRQ2 bit in the CFG2 Register. |

| Pins                                              | Signal Names | <b>Description</b> (continued)                                                                                                                                                                                                                                                                                                                                                |

|---------------------------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22                                                | OUT2         | Extra output signal #2. This additional output signal can be connected to extra control lines and is controlled by the OUT2 bit in the CFG2 Register.                                                                                                                                                                                                                         |

| 20                                                | IN2          | Extra input signal #2. This additional input signal is pulled up to +5 V by an onboard resistor. The status of this signal can be obtained by reading the IN2 bit in the STAT Register. This input signal can be used as an extra input signal line or as an external enable signal of Counter 2 of the board.                                                                |

| 18                                                | ACK2         | Output handshaking acknowledge signal for Group 2. When the AT-DIO-32F is in write mode, this signal becomes active when data has been written to the data lines. When the AT-DIO-32F is in read mode, this signal becomes active when the available data on the data lines has been read. The polarity of this signal is configured by the INVACK2 bit in the CFG2 Register. |

| 9-16                                              | DIOC<07>     | Bidirectional data lines for Port C. DIOC7 is the MSB; DIOC0 is the LSB.                                                                                                                                                                                                                                                                                                      |

| 1-8                                               | DIOD<07>     | Bidirectional data lines for Port D. DIOD7 is the MSB; DIOD0 is the LSB.                                                                                                                                                                                                                                                                                                      |

| 17, 19,<br>21, 23,<br>25, 26<br>28, 30,<br>32, 34 | GND          | These signals are connected to the ground signal of the PC.                                                                                                                                                                                                                                                                                                                   |

## I/O Connector Electrical Specifications

#### I/O Signals Rating

Absolute maximum voltage input rating: -0.5 to Vcc +0.5 V

(Vcc: -0.5 V to 6.0 V)

#### **Input Signal Specifications**

|                                                     | Minimum | Maximum |

|-----------------------------------------------------|---------|---------|

| Input logic high voltage                            | 2 V     | 5.5 V   |

| Input logic low voltage                             | 0 V     | 0.8 V   |

| Input current                                       |         |         |

| at $V_{cc} = 5.5 \text{ V}, V_{in} = 5.5 \text{ V}$ | _       | 10 μΑ   |

#### **Output Signal Specifications**

|                               | Minimum      | Maximum |

|-------------------------------|--------------|---------|

| Output logic high voltage     |              |         |

| at $I_{out} = -15 \text{ mA}$ | 2.4 V        | 5 V     |

| Output logic low voltage      |              |         |

| at $I_{out} = 48 \text{ mA}$  | 0 V          | 0.5 V   |

| Output logic high current     | <del>-</del> | -30 mA  |

| Output logic low current      | _            | 70 mA   |

| 1 0                           |              |         |

## **Timing Specifications**

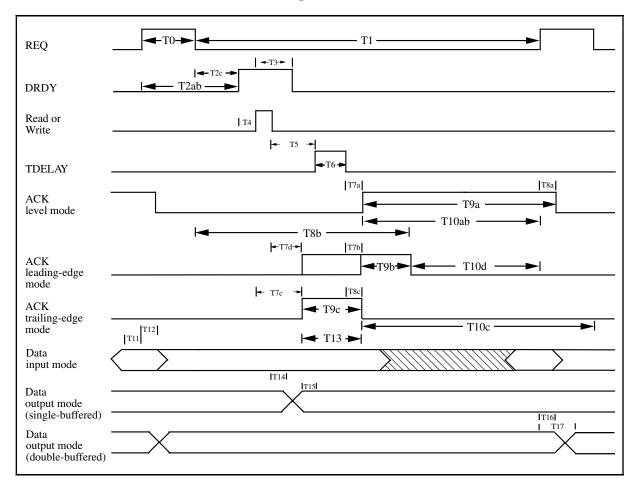

This section lists the timing specifications for handshaking with the AT-DIO-32F. The REQ and ACK signals are available on the I/O connector, and in the following diagrams they are non-inverted. The digital I/O ports are divided into two groups: Group 1 and Group 2. The timing specifications for Group 1 and Group 2 handshaking are identical.

The following signals are used in the timing diagrams later in this chapter.

| Name | Туре     | Description                                                                                                                                                                                                                 |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GO   | Internal | Internal GO pulse. This pulse is sent to the handshaking circuitry when the group's WRITE bit is set. This signal initializes the circuitry for a data write transfer. The GO signal is not available on the I/O connector. |

(continues)

| Name   | Type     | <b>Description</b> (continued)                                                                                                                                                                                                                                                                                               |

|--------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ    | Input    | Handshaking request signal. If the AT-DIO-32F is in write mode, this signal is asserted when the external device is ready to receive data. If the AT-DIO-32F is in read mode, this signal is asserted when data is available to be read. This signal is available on the I/O connector.                                      |

| ACK    | Output   | Handshaking acknowledge signal. If the AT-DIO-32F is in read mode, this signal is asserted by the AT-DIO-32F when it has read the available data. If the AT-DIO-32F is in write mode, this signal is asserted when the AT-DIO-32F has written the data to the specified port. This signal is available on the I/O connector. |

| DRDY   | Internal | Data transfer ready. In read mode, this signal is high when data is available to be read. In write mode, this signal is high when the external device is ready to receive the data. The status of this signal is available in the STAT register. This signal is not available on the I/O connector.                          |

| RD     | Internal | Read signal. This signal is the read signal generated from the control lines of the PC. This signal is not available on the I/O connector.                                                                                                                                                                                   |

| WR     | Internal | Write signal. This signal is the write signal generated from the control lines of the PC. This signal is not available on the I/O connector.                                                                                                                                                                                 |

| TDELAY | Internal | Data transmission delay.  A data-settling delay is added to ensure that data has settled during a transfer. The delay for Group 1 is controlled by bits T1S2 through T1S0 in the CFG1 Register. The delay for Group 2 is controlled by bits T2S2 through T2S0 in CFG2. This signal is not available on the I/O connector.    |

| DATA   | I/O      | Data signals on the I/O connector.  In write mode these lines are driven by the AT-DIO-32F, and data is transfered from memory to the external device. In read mode these lines are driven by the external device, and data is transfered from the external device to memory.                                                |

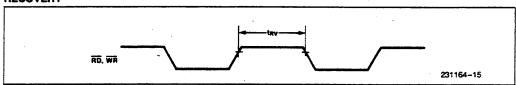

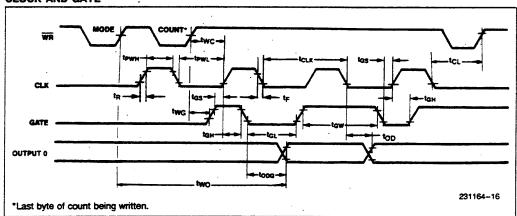

#### **AT-DIO-32F Read and Write Timing**

| Name | Description                                                         | Minimum | Maximum |

|------|---------------------------------------------------------------------|---------|---------|

| T0a  | REQ pulse width in level mode                                       | 125     | -       |

| T0bc | REQ pulse width in leading- or trailing-edge mode                   | 100     | -       |

| T1   | REQ low duration                                                    | 160     | -       |

| T2ab | REQ to DRDY in level or leading-edge mode                           | 0       | 225     |

| T2c  | REQ inactive to DRDY in trailing-edge mode                          | 0       | 100     |

| T3   | Start of read or write to DRDY inactive                             | 50      | 240     |

| T4   | DRDY to read or write                                               | 0       | -       |

| T5   | End of read or write to TDELAY                                      |         |         |

|      | (with TDELAY equal to 0)                                            | 0       | 175     |

|      | (with TDELAY not equal to 0)                                        | 50      | 360     |

| T6   | TDELAY (programmable)                                               | 0       | 700     |

| T7ab | TDELAY to ACK in level mode, or in leading-edge mode without LPULSE | 10      | 100     |

| T7c  | Start of read or write to ACK in trailing-edge mode                 | 60      | 220     |

| T7d  | End of read or write to ACK in leading-edge mode with LPULSE set    | 0       | 180     |

| T8a<br>T8b | REQ to ACK inactive in level mode                                               | 110 | 320 |

|------------|---------------------------------------------------------------------------------|-----|-----|

| 100        | REQ inactive to ACK inactive in leading-<br>edge mode (but T9b can prolong ACK) | 110 | 320 |

| T8c        | TDELAY to ACK inactive in trailing-edge                                         | 50  | 90  |

| 100        | mode                                                                            | 30  | 70  |

| T9a        | ACK pulse width in level mode                                                   | 225 | _   |

|            | (delaying REQ prolongs ACK)                                                     |     |     |

| T9b        | ACK pulse width in leading-edge mode                                            | 125 | 175 |

|            | without LPULSE (but T8b can prolong ACK)                                        |     |     |

| T9c        | ACK pulse width in trailing-edge mode                                           | 225 | -   |

|            | (increasing TDELAY prolongs ACK)                                                |     |     |

| T10ab      | ACK to next REQ in level mode or in                                             | 35  | -   |

|            | leading-edge mode without LPULSE                                                | _   |     |

| T10c       | ACK inactive to next REQ inactive in                                            | 0   | -   |

|            | trailing-edge mode                                                              |     |     |

| T10d       | ACK inactive to next REQ in leading-edge                                        | 0   | -   |

|            | mode with LPULSE set                                                            |     |     |

| T11        | Input data valid before REQ                                                     | 0   | -   |

| T12        | Input data valid after REQ                                                      | 120 | -   |

|            | (double-buffered input)                                                         |     |     |

| T13        | Input data valid after ACK                                                      | 0   | -   |

|            | (single-buffered input)                                                         |     |     |

| T14        | Old output data invalid after write                                             | 0   | -   |

|            | (single-buffered output)                                                        | _   |     |

| T15        | Output data valid before TDELAY                                                 | 5   | -   |

|            | (single-buffered output)                                                        |     |     |

| T16        | Old output data invalid after REQ                                               | 0   | -   |

|            | (double-buffered output)                                                        |     |     |

| T17        | Output data valid after REQ                                                     | 0   | 100 |

|            | (double-buffered output)                                                        |     |     |

All timing values are in nanoseconds.

## **Cabling**

The AT-DIO-32F can be interfaced to a wide range of printers, plotters, test instruments, I/O racks and modules, screw terminal panels, and almost any device with a parallel interface. The AT-DIO-32F digital I/O connector is a standard 50-pin header connector. The pin assignments are compatible with the DEC DRV11J parallel interface and most standard 32-channel I/O module mounting racks (such as those manufactured by Opto 22 and Gordos).

The CB-50, a cable termination accessory, is available from National Instruments for use with the AT-DIO-32F board. This kit includes a 50-conductor, flat ribbon cable and a connector block. Signal input and output wires can be attached to screw terminals on the connector block and thereby connected to the AT-DIO-32F I/O connector.

The CB-50 is useful for initially prototyping an application or in situations where AT-DIO-32F interconnections are frequently changed. Once a final field wiring scheme has been developed, however, you may want to develop your own cable. This section contains information and guidelines for the design of such a cable.

The AT-DIO-32F I/O connector is a 50-pin male ribbon cable header. Recommended manufacturers and the appropriate part numbers for this header are as follows:

Electronic Products Division/3M part number 3596-5002 T&B/Ansley Corporation part number 609-5007

The mating connector for the AT-DIO-32F is a 50-position, polarized, ribbon socket connector with strain relief. National Instruments uses a polarized (keyed) connector to prevent inadvertent upside-down connection to the AT-DIO-32F. Recommended manufacturers and the appropriate part numbers for this mating connector are as follows:

Electronic Products Division/3M part number 3425-7650 T&B/Ansley Corporation part number 609-5041CE

Recommended manufacturers and the appropriate part numbers for the standard ribbon cable (50-conductor, 28 AWG, stranded) that can be used with these connectors are as follows:

Electronic Products Division/3M part number 3365/50 T&B/Ansley Corporation part number 171-50

If you plan to use the AT-DIO-32F for a communications application, you may need shielded cables to meet FCC requirements. The AT-DIO-32F I/O bracket has been designed so that the shield of the I/O cable can be grounded through the computer chassis when a mating connector such as the following is used:

AMP Special Industries part number 2-746483-2

Many varieties of shielded ribbon cable can work with the preceding mating connector. One type of shielded cable encloses a standard ribbon cable with a shielded jacket. Recommended manufacturers and the appropriate part numbers for this type of cable are as follows:

Belden Electronic Wire and Cable part number 9L28350 T&B/Ansley Corporation part number 187-50

# **Chapter 3 Theory of Operation**

This chapter explains the basic operation of the AT-DIO-32F circuitry.

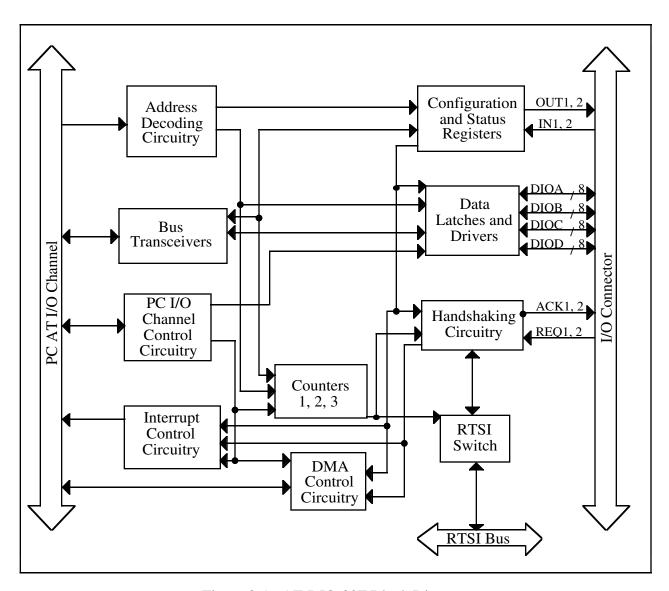

The AT-DIO-32F is a high-speed, 32-bit, parallel, digital I/O interface for the PC. The 32 lines of digital I/O on the AT-DIO-32F are divided into four 8-bit ports (DIOA, DIOB, DIOC, and DIOD). Ports A and B are assigned to handshaking Group 1, and Ports C and D are assigned to handshaking Group 2. Each group can be programmed as either an input or an output group, and each group has its own independent handshaking signals for data transfers.

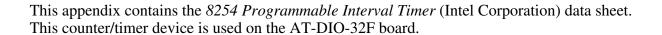

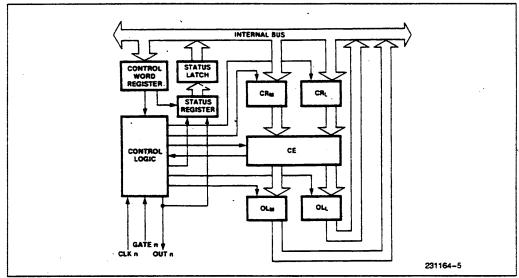

The key functional components of the hardware are illustrated in the block diagram shown in Figure 3-1.

Figure 3-1. AT-DIO-32F Block Diagram

Theory of Operation Chapter 3

The AT-DIO-32F board is a full-size, 16-bit, PC I/O channel adapter. The PC I/O channel consists of a 24-bit address bus, a 16-bit data bus, a DMA arbitration bus, interrupt lines, and several control and support signals.

### **Address Decoder**

The PC I/O channel has 24 address lines; the AT-DIO-32F uses ten of these lines to decode the board address. Therefore, the board address range is hex 000 to 3FF. Address lines SA5 through SA9 are used to generate the board enable signal. SA0 through SA4 are used to select the onboard registers.

### **Bus Transceivers**

The bus transceivers control the sending and receiving of the data lines to and from the PC I/O channel.

# **PC I/O Channel Control Circuitry**

This circuitry monitors and transmits the PC I/O channel control and support signals. The control signals identify transfers as read or write, configuration or I/O, and 8-bit or 16-bit. A support signal is returned to the PC I/O channel from the AT-DIO-32F to indicate the size of the current data transfer.

# **Configuration and Status Registers**

The AT-DIO-32F has seven configuration registers and a status register. Four 16-bit configuration registers (CFG1, CFG2, CFG3, and CFG4) are used to program all of the digital I/O modes of the

AT-DIO-32F. The other configuration registers are used to configure three onboard counters and the RTSI bus and to clear certain interrupt status bits. The 16-bit status register (STAT) contains DMA, interrupt, and handshaking signal status information. Refer to Chapter 4, *Programming*, for additional information about these registers.

# **Data Latches and Drivers**

The four 8-bit digital I/O ports are divided into two handshaking groups. Ports A and B are assigned to handshaking Group 1. Ports C and D are assigned to handshaking Group 2. Each port can be configured as read or write, and single-buffered or doubled-buffered. When the board is first turned on, each port is configured as a single-buffered read port. Reading a single-buffered input port returns the data currently available for that port at the I/O connector. Data is latched in a read port on the appropriate active edge of the handshaking request line, REQ1 or REQ2, when the port is configured as a double-buffered input port.

Chapter 3 Theory of Operation

If a port is configured as a single-buffered write port, the data written to that port is latched into the port and driven on the corresponding digital I/O lines. Reading the port returns the data that is currently driven by the port. Write ports configured for double-buffering are often used for pattern generation. A double-buffered write port consists of two buffers: the write buffer and the output buffer. Data written to the port is loaded into the write buffer. When a handshaking request, REQ1 or REQ2, is received on the I/O connector for the double-buffered group, the contents of the write buffer are loaded into the output buffer. Data loaded in the output buffer is driven on the digital I/O lines.

## **Onboard Counters**

The AT-DIO-32F includes three onboard counters, useful for pattern generation and periodic data acquisition. Counter 1 can be programmed to generate group 1 handshaking requests on the REQ1 line. Likewise, counter 2 can be programmed to generate group 2 handshaking requests on the REQ2 line. Counter 3 can alter the counting rate of the other two counters and can also be programmed to generate periodic interrupts.

The clock that runs the counters, BRDCLK, connects to a 10 MHz clock source: either an onboard clock, OSC, or to the RTSI clock line, RTSICLK. With BRDCLK connected to both OSC and RTSICLK, the onboard clock source can drive both the counters and the RTSI clock line. See *RTSI Bus Clock Selection* in Chapter 2, *Configuration and Installation*, for information about connecting the BRDCLK signal.

The signal you select for BRDCLK is slowed by a factor of 5, creating a 2 MHz clock signal that operates Counter 3. The output of Counter 3 forms a time base for Counters 1 and 2, but Counters 1 and 2 can also run directly from the BRDCLK clock, if so directed in CFG3 register. Figure 3-2 shows the clock routing scheme.

Theory of Operation Chapter 3

Figure 3-2. AT-DIO-32F Clock Routing Scheme

# **Digital I/O Connector**

All digital I/O is through a standard, 50-pin, male connector. The pin assignments for this connector are compatible with the DEC DRV11-J parallel interface and most 32-channel I/O module racks. Refer to *Signal Connections* in Chapter 2, *Configuration and Installation*, for pin assignments and additional information.

# **Handshaking Circuitry**

The four 8-bit digital I/O ports are divided into two handshaking groups: Group 1 and Group 2. These groups are independent of each other, so two separate transfers can occur simultaneously.

Chapter 3 Theory of Operation

Group 1 handshaking is controlled by REQ1 and ACK1. Group 2 handshaking is controlled by REQ2 and ACK2. The handshaking circuitry controls these handshaking signals and the data flow through the digital I/O data latches and drivers.

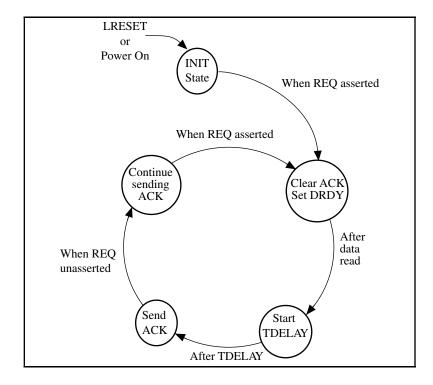

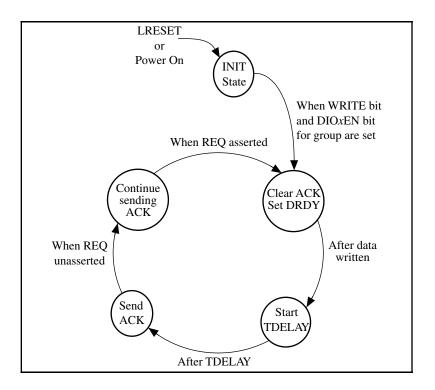

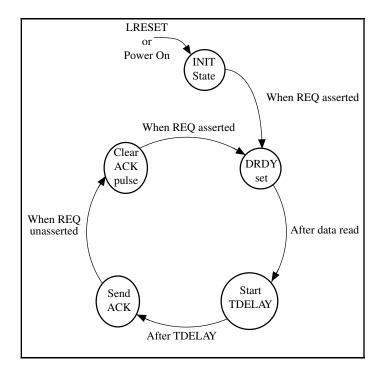

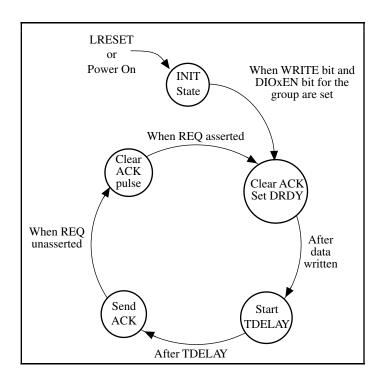

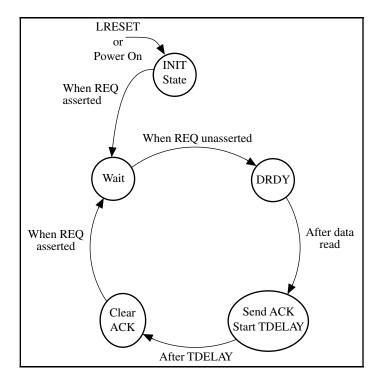

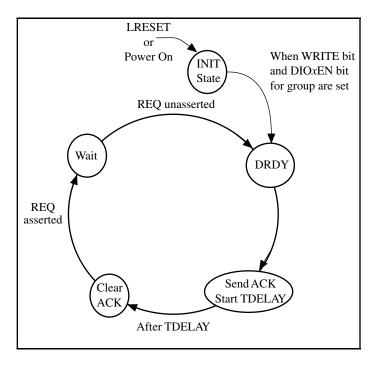

Each group can be programmed to operate in one of three handshaking modes: level signals, leading edge signals, or trailing edge signals. Refer to Chapter 2, *Configuration and Installation*, and Chapter 4, *Programming*, for the timing diagrams for each of these modes. The state diagrams that describe each handshaking mode are shown later in this chapter.

After start-up or LRESET, the handshaking circuitry is in the INIT state. During a read transfer, DRDY is set once a REQ is received. DRDY remains set until the data is read from the selected ports. During a write transfer, DRDY is set as soon as the group's WRITE bit is set, indicating that the group is in write mode. DRDY remains set until data is written to the selected ports.

In the Figures 3-3 and 3-4, REQ and ACK are shown as active high logic; that is, INVRQ and INVACK are cleared.