#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE NB-MIO-16X

# SCXI-1140 User Manual

An Eight-Channel Simultaneously Sampling Differential Amplifier Module for Signal Conditioning

**September 1994 Edition**

Part Number 320410B-01

© Copyright 1991, 1994 National Instruments Corporation. All Rights Reserved.

#### National Instruments Corporate Headquarters

6504 Bridge Point Parkway Austin, TX 78730-5039 (512) 794-0100 Technical support fax: (800) 328-2203 (512) 794-5678

#### **Branch Offices:**

Australia (03) 879 9422, Austria (0662) 435986, Belgium 02/757.00.20, Canada (Ontario) (519) 622-9310, Canada (Québec) (514) 694-8521, Denmark 45 76 26 00, Finland (90) 527 2321, France (1) 48 14 24 24, Germany 089/741 31 30, Italy 02/48301892, Japan (03) 3788-1921, Netherlands 03480-33466, Norway 32-848400, Spain (91) 640 0085, Sweden 08-730 49 70, Switzerland 056/20 51 51, U.K. 0635 523545

## **Limited Warranty**

The SCXI-1140 is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

## Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

## Trademarks

LabVIEW<sup>®</sup>, NI-DAQ<sup>®</sup>, and RTSI<sup>®</sup> are trademarks of National Instruments Corporation.

Product and company names listed are trademarks or trade names of their respective companies.

## Warning Regarding Medical and Clinical Use of National Instruments Products

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

# **About This Manual**

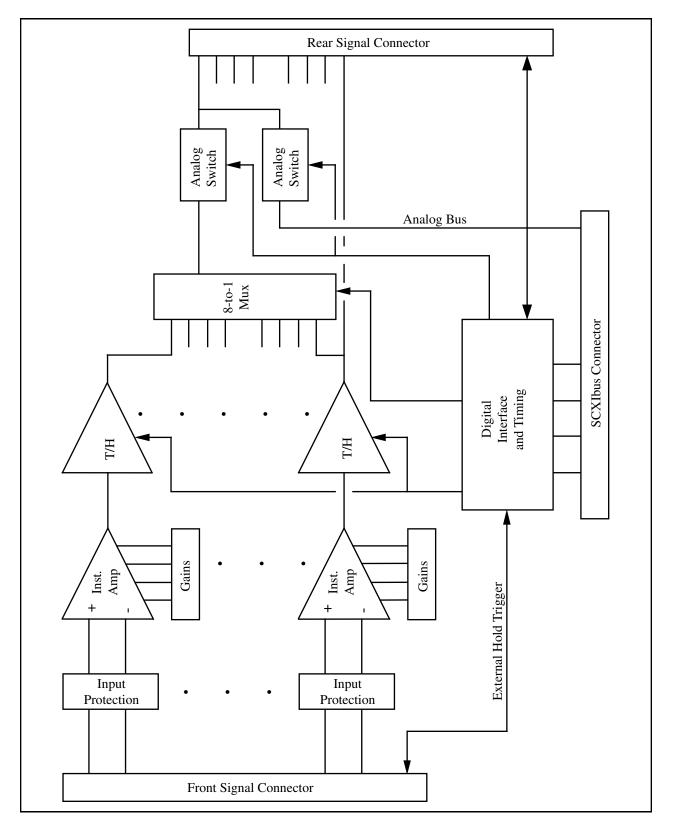

This manual describes the electrical and mechanical aspects of the SCXI-1140 and contains information concerning its operation and programming. The SCXI-1140 is a member of the National Instruments Signal Conditioning eXtensions for Instrumentation (SCXI) Series modules for National Instruments data acquisition plug-in boards. This module is designed for low-cost signal conditioning of a wide variety of high-level and low-level DC and AC voltage sources.

This manual also describes the installation, basic programming considerations, and theory of operation for the SCXI-1140.

# **Organization of This Manual**

The SCXI-1140 User Manual is organized as follows:

- Chapter 1, *Introduction*, describes the SCXI-1140; lists the contents of your SCXI-1140 kit; describes the optional software, optional equipment, and custom cables; and explains how to unpack the SCXI-1140 kit.

- Chapter 2, *Configuration and Installation*, describes the SCXI-1140 jumper configurations, DIP switch settings, installation of the SCXI-1140 into the SCXI chassis, signal connections to the SCXI-1140, and cable wiring.

- Chapter 3, *Theory of Operation*, contains a functional overview of the SCXI-1140 module and explains the operation of each functional unit making up the SCXI-1140.

- Chapter 4, *Register Descriptions*, describes in detail the SCXI-1140 Configuration Register, the Module ID Register, and the Slot 0 registers.

- Chapter 5, *Programming*, contains a functional programming description of the SCXI-1140 and Slot 0.

- Chapter 6, *Calibration Procedures*, discusses the calibration procedures for the SCXI-1140 module.

- Appendix A, *Specifications*, lists the specifications for the SCXI-1140.

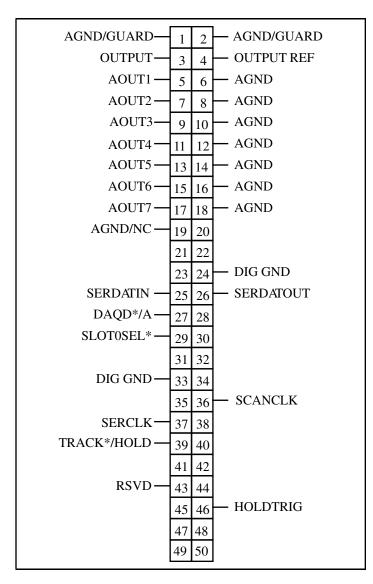

- Appendix B, *Rear Signal Connector*, describes the pinout and signal names for the SCXI-1140 50-pin rear signal connector, including a description of each connection.

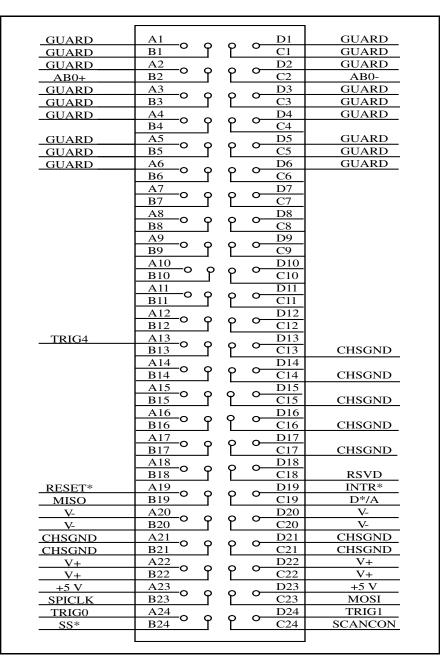

- Appendix C, *SCXIbus Connector*, describes the pinout and signal names for the SCXI-1140 96-pin SCXIbus connector, including a description of each signal.

- Appendix D, *SCXI-1140 Front Connector*, describes the pinout and signal names for the SCXI-1140 front connector, including a description of each connection.

- Appendix E, *SCXI-1140 Cabling*, describes the usage and installation of the hardware accessories that you can use with the SCXI-1140.

- Appendix F, *Revision A and B Photograph and Parts Locator Diagram*, contains a photograph of the Revision A and B SCXI-1140 signal conditioning module and the SCXI-1140 parts locator diagram.

- Appendix G, *Customer Communication*, contains forms you can use to request help from National Instruments or to comment on our products.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, and symbols.

- The *Index* contains an alphabetical list of key terms and topics used in this manual, including the page where you can find each one.

# **Conventions Used in This Manual**

The following conventions are used in this manual:

| DIO board | DIO board refers to the National Instruments AT-DIO-32F, MC-DIO-24, MC-DIO-32F, NB-DIO-24, NB-DIO-96, NB-DIO-32F, PC-DIO 24, and PC-DIO-96 digital I/O data acquisition boards unless otherwise noted.                                                                                                                                                                                                                           |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| italic    | Italic text denotes emphasis, a cross reference, or an introduction to a key concept.                                                                                                                                                                                                                                                                                                                                            |

| Lab board | Lab board refers to the National Instruments Lab-LC, Lab-NB, Lab-PC, and Lab-PC+ boards unless otherwise noted.                                                                                                                                                                                                                                                                                                                  |

| MC        | MC refers to the Micro Channel series computers.                                                                                                                                                                                                                                                                                                                                                                                 |

| MIO board | MIO board refers to the National Instruments AT-MIO-16, AT-MIO-16D, AT-MIO-16F-5, AT-MIO-16X, AT-MIO-64F-5, MC-MIO-16, NB-MIO-16, and NB-MIO-16X multichannel I/O data acquisition boards unless otherwise noted.                                                                                                                                                                                                                |

| monospace | Lowercase text in this font denotes text or characters that are to be literally<br>input from the keyboard, sections of code, programming examples, and<br>syntax examples. This font is also used for the proper names of disk<br>drives, paths, directories, programs, subprograms, subroutines, device<br>names, functions, variables, filenames, and extensions, and for statements<br>and comments taken from program code. |

| NB        | NB refers to the NuBus series computers.                                                                                                                                                                                                                                                                                                                                                                                         |

| PC        | PC refers to the IBM PC/XT/AT and compatible computers.                                                                                                                                                                                                                                                                                                                                                                          |

| SCXIbus   | SCXIbus refers to the backplane in the chassis. A signal on the backplane is referred to as the SCXIbus <signal name=""> line (or signal). The SCXIbus descriptor may be omitted when the meaning is clear. Descriptions of all SCXIbus signals are given in Appendix C, <i>SCXIbus Connector</i>.</signal>                                                                                                                      |

| Slot 0    | Slot 0 refers to the power supply and control circuitry in the SCXI chassis.                                                                                                                                                                                                                                                                                                                                                     |

Abbreviations, acronyms, metric prefixes, mnemonics, symbols, and terms are listed in the *Glossary*.

# **Related Documentation**

The following documents contain information that you may find helpful as you read this manual:

- AT-MIO-16 User Manual (part number 320476-01)

- *AT-MIO-16D User Manual* (part number 320489-01)

- AT-MIO-16F-5 User Manual (part number 320266-01)

- *AT-MIO-16X User Manual* (part number 320488-01)

- *AT-MIO-64F-5 User Manual* (part number 320487-01)

- Lab-LC User Manual (part number 320380-01)

- *Lab-NB User Manual* (part number 320174-01)

- *Lab-PC User Manual* (part number 320205-01)

- *Lab-PC+ User Manual* (part number 320502-01)

- *MC-MIO-16 User Manual*, Revisions A to C (part number 320130-01)

- *MC-MIO-16 User Manual*, Revision D (part number 320560-01)

- *NB-MIO-16 User Manual* (part number 320295-01)

- *NB-MIO-16X User Manual* (part number 320157-01)

- *PC-LPM-16 User Manual* (part number 320287-01)

- SCXI-1000/1001 User Manual (part number 320423-01)

# **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix G, *Customer Communication*, at the end of this manual.

# Contents

| About This Manual                              | xi    |

|------------------------------------------------|-------|

| Organization of This Manual                    | xi    |

| Conventions Used in This Manual                | xii   |

| Related Documentation                          |       |

| Customer Communication                         | xiii  |

| Chapter 1                                      |       |

| Introduction                                   | .1-1  |

| What Your Kit Should Contain                   | .1-2  |

| Optional Software                              |       |

| Optional Equipment                             |       |

| Custom Cables                                  |       |

| Unpacking                                      | .1-4  |

| Chapter 2                                      |       |

| Configuration and Installation                 | .2-1  |

| Module Configuration                           | .2-1  |

| Digital Signal Connections                     |       |

| Jumper W11                                     |       |

| Jumper W14                                     |       |

| Jumper W13                                     | .2-4  |

| Using Jumpers W13 and W14                      |       |

| Analog Configuration                           |       |

| Input Mode Selection                           |       |

| Jumpers W1 through W8                          |       |

| Output Selection                               |       |

| Jumper W9                                      |       |

| Grounding and Shielding                        |       |

| Jumper W12<br>Gain Selection                   |       |

| Hardware Installation                          |       |

| Signal Connections                             |       |

| The Front Connector                            |       |

| Front Connector Signal Connection Descriptions |       |

| Analog Input Channels                          |       |

| Digital Input                                  |       |

| Terminal Block and Connector and Shell         |       |

| Connector and Shell                            | .2-15 |

| Terminal Block                                 | .2-16 |

| Cable Connection                               | .2-16 |

| The Rear Signal Connector                      |       |

| Rear Signal Connector Pin Descriptions         | .2-19 |

| Analog Output Signal Connections               | .2-20 |

| Digital I/O Signal Connections                 | .2-21 |

| Timing Requirements and Communication Protocol |       |

| Timing Signals                                 | .2-23 |

| Communication Signals                          | .2-26 |

# Chapter 3

| Theory of Operation                           |     |

|-----------------------------------------------|-----|

| Functional Overview                           | 3-1 |

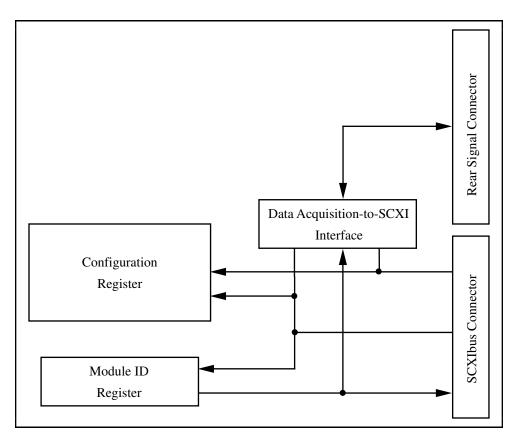

| Digital Interface                             |     |

| SCXIbus Connector                             |     |

| SCXIbus Connector Signal Descriptions         | 3-5 |

| Digital Control Circuitry                     |     |

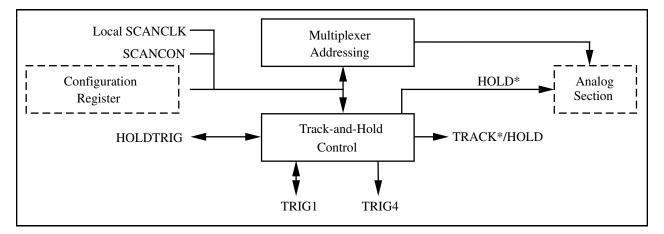

| Timing Control Circuitry                      |     |

| Multiplexer Addressing                        |     |

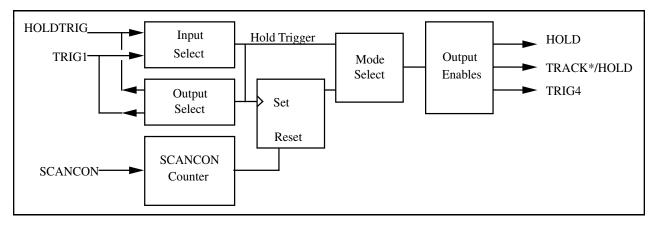

| Track-and-Hold Control Circuitry              |     |

| Analog Circuitry                              |     |

| Scanning Modes                                |     |

| Single-Module Parallel Scanning               |     |

| Single-Module Multiplexed Scanning            |     |

| Single-Module Multiplexed Scanning (Direct)   |     |

| Single-Module Multiplexed Scanning (Indirect) |     |

| Multiple-Module Multiplexed Scanning          |     |

| Multiple-Chassis Scanning                     |     |

|                                               |     |

# Chapter 4

| Register Descriptions        | 4-1 |

|------------------------------|-----|

| Register Description         |     |

| Register Description Format  |     |

| SCXI-1140 Registers          | 4-1 |

| Module ID Register           |     |

| Configuration Register       | 4-3 |

| Slot 0 Register Descriptions |     |

| Slot-Select Register         |     |

| Hardscan Control Register    | 4-8 |

| FIFO Register                |     |

| e                            |     |

# Chapter 5

| Programming                                         | 5-1         |

|-----------------------------------------------------|-------------|

| Programming Considerations                          | 5-1         |

| Notation                                            | <b>j</b> -1 |

| Register Writes5                                    |             |

| Register Selection and Write Procedure              | j-2         |

| Initialization5                                     | 5-3         |

| Track-and-Hold Modes5                               |             |

| Level-Sensitive Hold Trigger5                       | 5-3         |

| Edge-Sensitive Hold Trigger5                        | j-4         |

| Single-Channel Measurements                         | j-4         |

| Putting the SCXI-1140 into Track or Hold Mode       |             |

| Using an MIO-16 Board5                              |             |

| Using a Lab-NB, Lab-PC, Lab-PC+, or Lab-LC Board5   |             |

| Using a PC-LPM-16 Board5                            | i-5         |

| Direct Measurements5                                | i-6         |

| Parallel Output5                                    | i-6         |

| Multiplexed Output5                                 | i-6         |

| Indirect Measurements                               |             |

| Measurements from Other Modules                     |             |

| Measurements from the SCXI-1140 via Another Module5 | <u>5-7</u>  |

| Scanning Measurements                            | 5-8  |

|--------------------------------------------------|------|

| 1. Data Acquisition Board Setup Programming      | 5-9  |

| Counter 1 and SCANDIV                            |      |

| 2. Module Programming                            | 5-12 |

| Single-Module Parallel Scanning                  | 5-12 |

| Single-Module Multiplexed Scanning (Direct)      |      |

| Single-Module Multiplexed Scanning (Indirect)    |      |

| Multiple-Module Multiplexed Scanning             |      |

| Multiple-Chassis Scanning                        |      |

| 3. Programming the Slot 0 Hardscan Circuitry     |      |

| 4. Acquisition Enable, Triggering, and Servicing |      |

| Scanning Examples                                |      |

| Example 1                                        |      |

| Example 2a                                       |      |

| Example 2b                                       |      |

| Example 3                                        |      |

# Chapter 6

| Calibration Procedures | 6-1 |

|------------------------|-----|

| Software Calibration   |     |

| Offset Adjustment      | 6-1 |

| Gain Adjustment        |     |

| Linearity Adjustment   | 6-2 |

| Hardware Calibration   | 6-2 |

# Appendix A

| Specifications                      | A-1 |

|-------------------------------------|-----|

| DC                                  | A-1 |

| ĀC                                  |     |

| Sampling                            |     |

| Power                               | A-2 |

| Physical                            | A-3 |

| Operating Environment               | A-3 |

| Storage Environment                 | A-3 |

|                                     |     |

| Appendix B                          |     |

| Appendix B<br>Boar Signal Connector | D 1 |

| Rear Signal C | Connector                      | B-1 |

|---------------|--------------------------------|-----|

| Rear Sign     | nal Connector Pin Descriptions | B-2 |

# Appendix C

| SCXIbus Connector | C-1 |

|-------------------|-----|

|                   | C-3 |

# Appendix D

| SCXI-1140 Front Connector                      | D-1 |

|------------------------------------------------|-----|

| Front Connector Signal Connection Descriptions | D-3 |

## Appendix E

| SCXI-1140 Cabling        | E-1 |

|--------------------------|-----|

| SCXI-1340 Cable Assembly | E-1 |

| SCXI-1340 Installation   |     |

| SCXI-1341 Lab-NB, Lab-PC, or Lab-PC+ Cable Assembly and             |            |

|---------------------------------------------------------------------|------------|

| SCXI-1344 Lab-LC Cable Assembly                                     | E-3        |

| SCXI-1341 or SCXI-1344 Installation                                 | E-5        |

| SCXI-1342 PC-LPM-16 Cable Assembly                                  | E-5        |

| SCXI-1342 Installation                                              | E-6        |

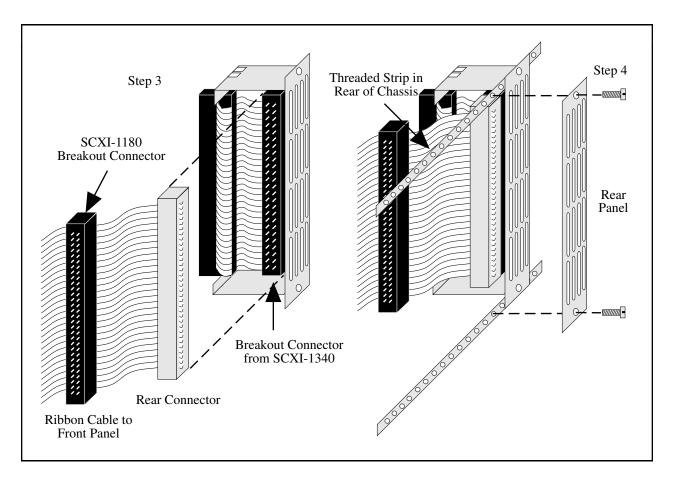

| SCXI-1180 Feedthrough Panel                                         | E-7        |

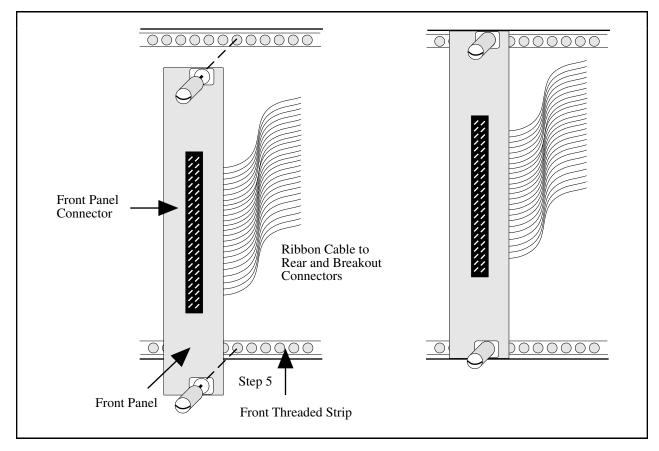

| SCXI-1180 Installation                                              | E-7        |

| SCXI-1302 50-Pin Terminal Block                                     | E-9        |

| SCXI-1302 Wiring Procedure                                          | E-9        |

| SCXI-1302 Installation                                              |            |

| SCXI-1351 One-Slot Cable Extender                                   | E-11       |

| SCXI-1351 Installation                                              | E-11       |

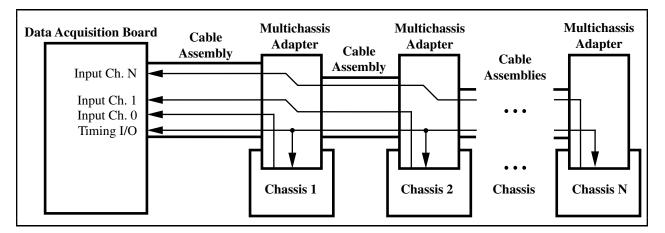

| Multiple-chassis Connections for the SCXI-1140                      | E-11       |

| SCXI-1350 Multichassis Adapter                                      |            |

| SCXI-1350 Installation                                              |            |

| SCXI-1343 Rear Screw Terminal Adapter                               | E-12       |

| SCXI-1343 Installation                                              | E-14       |

| Appendix F<br>Revision A and B Photograph and Parts Locator Diagram | F-1        |

| Appendix G<br>Customer Communication                                | G-1        |

| Glossary                                                            | Glossary-1 |

| Index                                                               | Index-1    |

# Figures

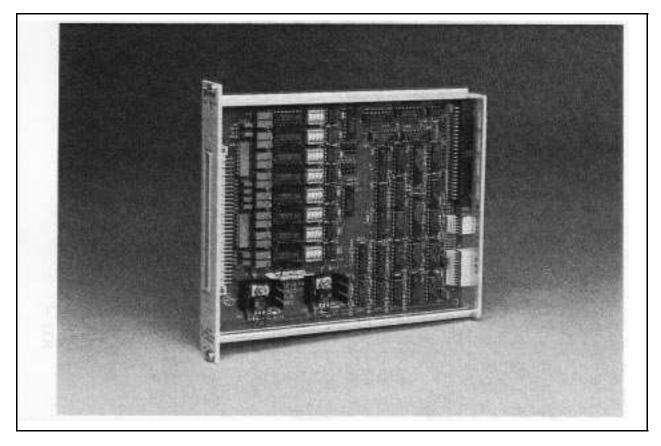

| Figure 1-1.  | SCXI-1140 Signal Conditioning Module                  | 1-1  |

|--------------|-------------------------------------------------------|------|

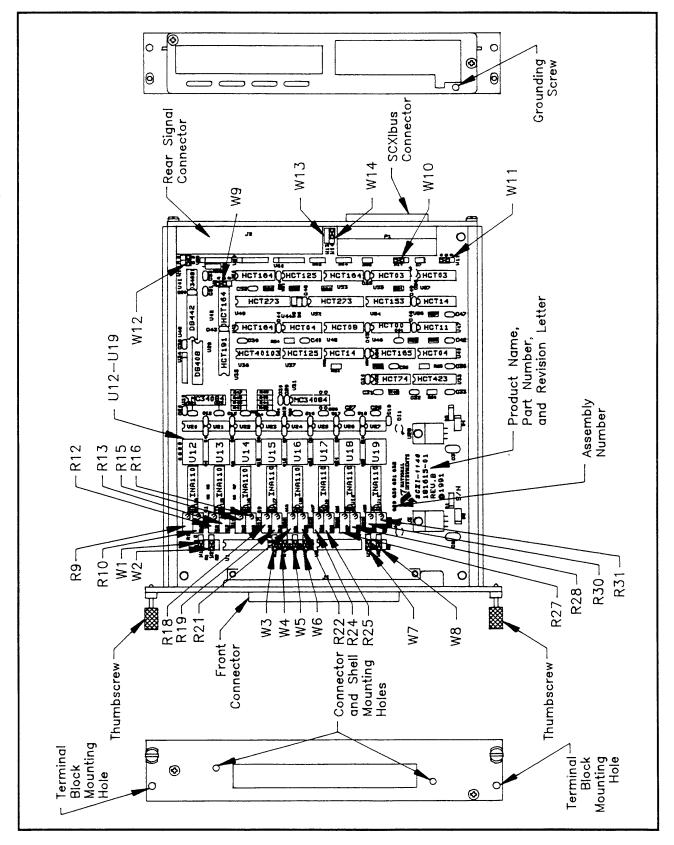

| Figure 2-1.  | SCXI-1140 Parts Locator Diagram                       | 2-2  |

| Figure 2-2.  | Analog Jumpers (Factory Setting)                      |      |

| Figure 2-3.  | Gain Switches for Each Channel                        | 2-7  |

| Figure 2-4.  | SCXI-1140 Front Connector Pin Assignment              |      |

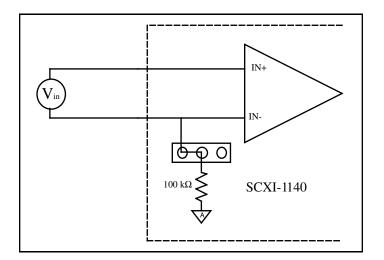

| Figure 2-5.  | Ground-Referenced Signal Connection                   |      |

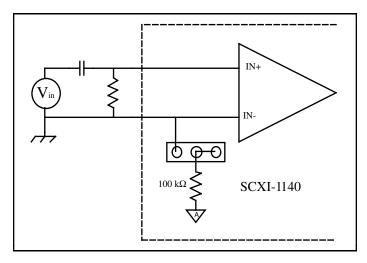

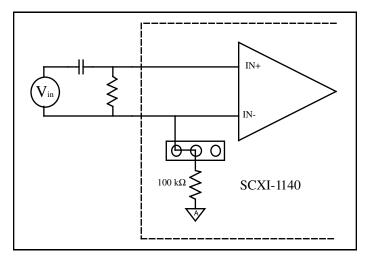

| Figure 2-6.  | Floating Signal Connection                            |      |

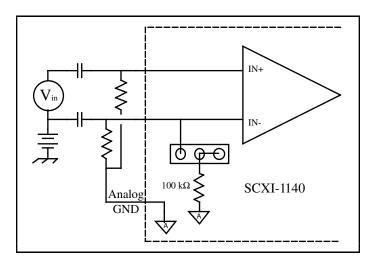

| Figure 2-7.  | Ground-Referenced AC-Coupled Signal Connection        | 2-13 |

| Figure 2-8.  | Ground-Offset AC-Coupled Signal Connection            |      |

| Figure 2-9.  | Floating AC-Coupled Signal Connection                 | 2-13 |

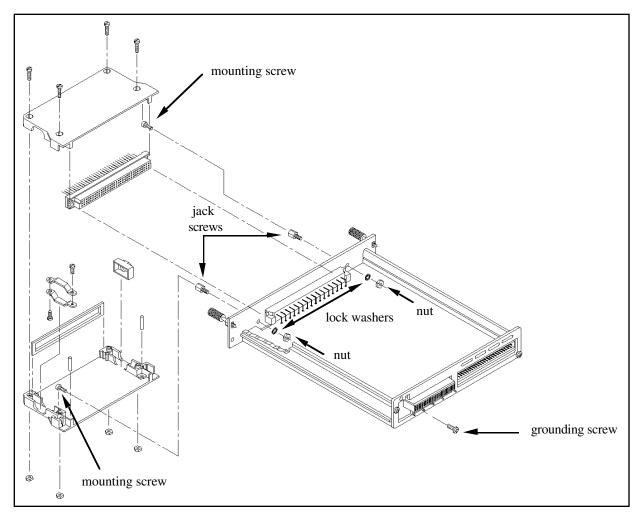

| Figure 2-10. | Assembling and Mounting the Connector and Shell       | 2-16 |

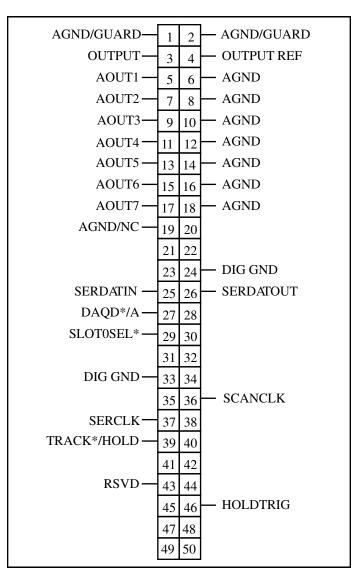

| Figure 2-11. | SCXI-1140 Rear Signal Connector Pin Assignment        | 2-18 |

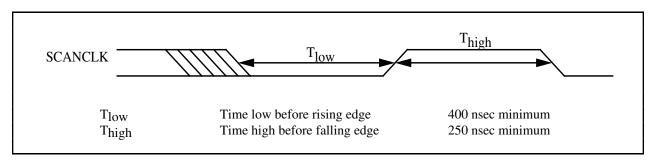

| Figure 2-12. | SCANCLK Timing Requirements                           |      |

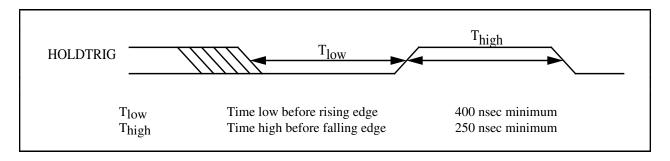

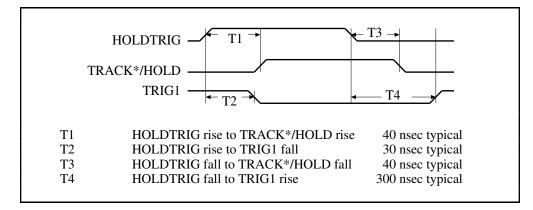

| Figure 2-13. | HOLDTRIG Timing Requirements                          | 2-23 |

| Figure 2-14. | Level-Sensitive Mode, HOLDTRIG Source                 |      |

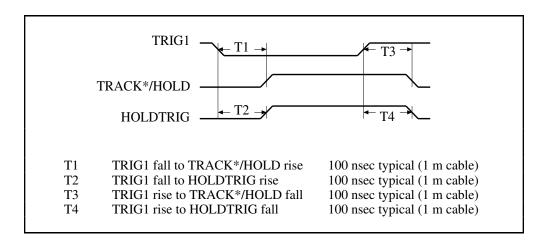

| Figure 2-15. | Level-Sensitive Mode, TRIG1 Source                    |      |

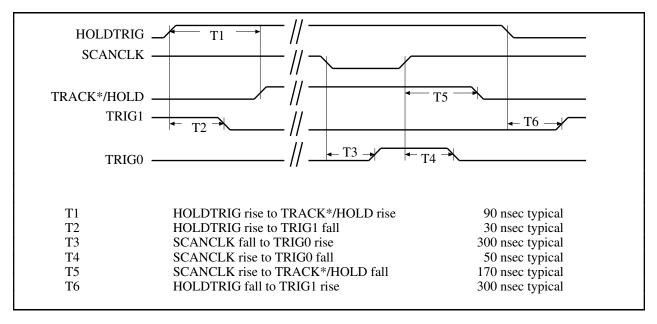

| Figure 2-16. | Edge-Triggered Mode, HOLDTRIG Source                  | 2-25 |

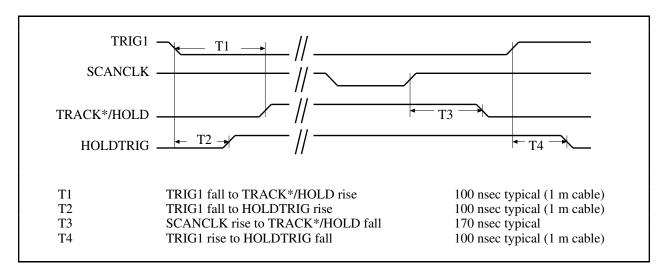

| Figure 2-17. | Edge-Triggered Mode, TRIG1 Source                     | 2-25 |

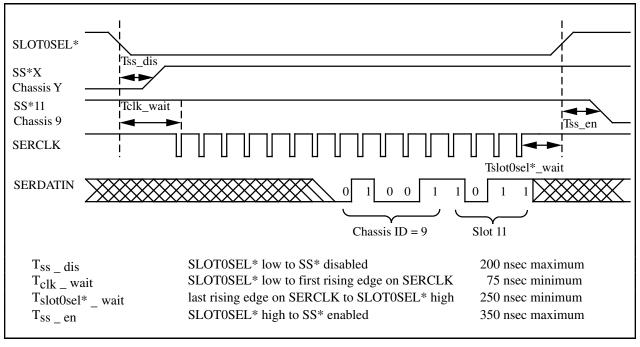

| Figure 2-18. | Slot-Select Timing Diagram                            | 2-27 |

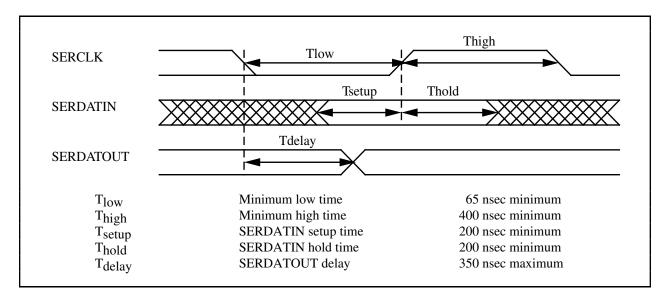

| Figure 2-19. | Serial Data Timing Diagram                            |      |

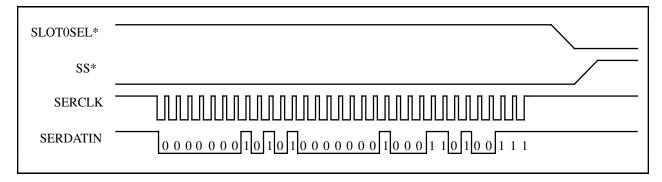

| Figure 2-20. | Configuration Register Write Timing Diagram           | 2-28 |

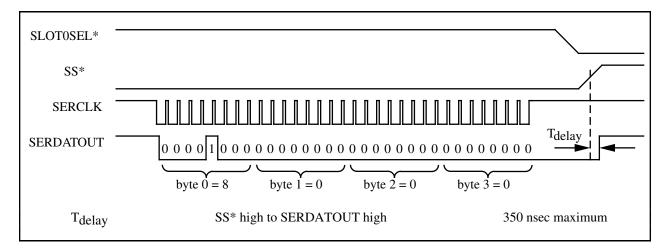

| Figure 2-21. | SCXI-1140 Module ID Register Timing Diagram           | 2-29 |

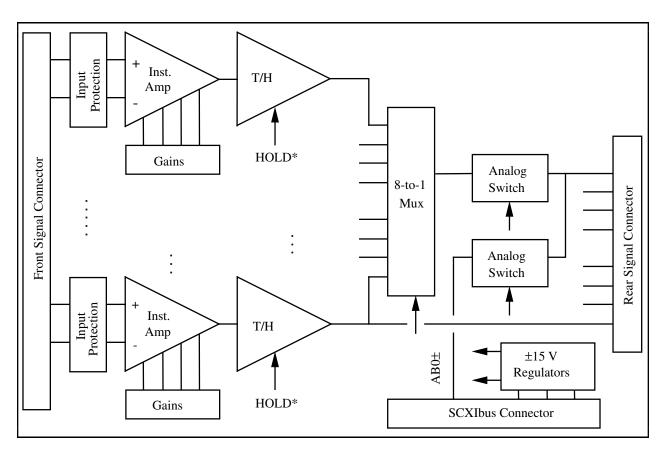

| Figure 3-1.  | SCXI-1140 Block Diagram                               |      |

| Figure 3-2.  | SCXI-1140 Digital Interface Circuitry Block Diagram   |      |

| Figure 3-3.  | SCXI-1140 SCXIbus Connector Pin Assignment            |      |

| Figure 3-4.  | SCXI-1140 Timing Control Circuitry Block Diagram      |      |

| Figure 3-5.  | SCXI-1140 Track-and-Hold Control                      | 3-9  |

| Figure 3-6.  | SCXI-1140 Analog Circuitry                            |      |

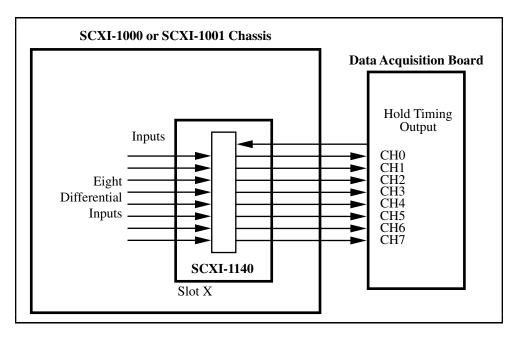

| Figure 3-7.  | Single-Module Parallel Scanning                       |      |

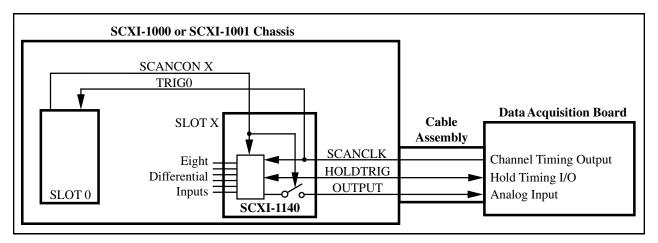

| Figure 3-8.  | Single-Module Multiplexed Scanning (Direct)           |      |

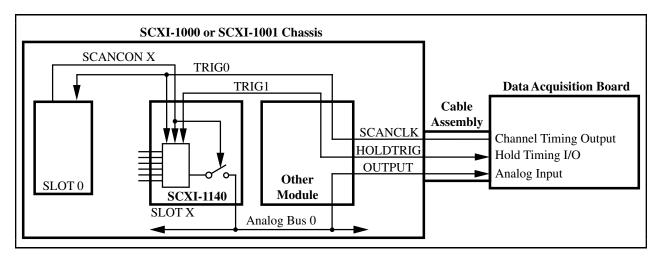

| Figure 3-9.  | Single-Module Multiplexed Scanning (Indirect)         | 3-14 |

| Figure 3-10. | Multiple-Module Multiplexed Scanning                  |      |

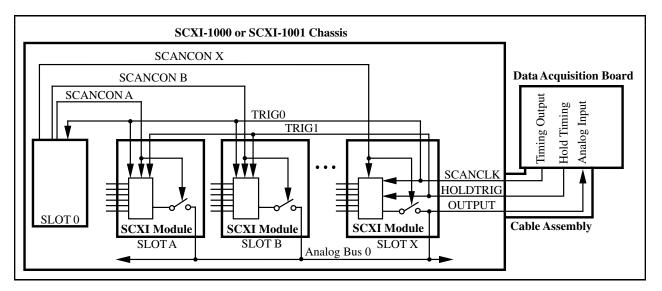

| Figure 3-11. | Multiple-Chassis Scanning                             | 3-15 |

| Figure B-1.  | SCXI-1140 Rear Signal Connector Pin Assignment        | B-1  |

| Figure C-1.  | SCXI-1140 SCXIbus Connector Pin Assignment            | C-2  |

| Figure D-1.  | SCXI-1140 Front Connector Pin Assignment              | D-2  |

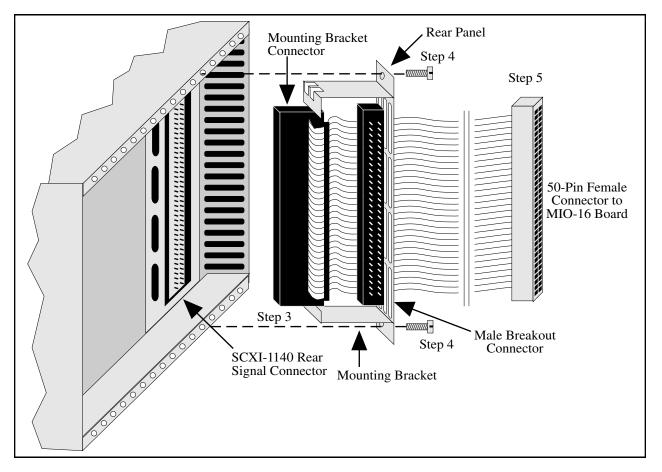

| Figure E-1.  | SCXI-1340 Installation                                | E-3  |

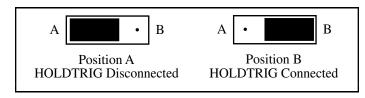

| Figure E-2.  | Jumper W1                                             |      |

| Figure E-3.  | SCXI-1180 Rear Connections                            | E-8  |

| Figure E-4.  | SCXI-1180 Front Panel Installation                    |      |

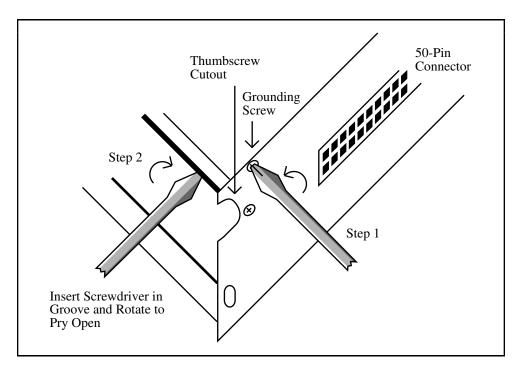

| Figure E-5.  | Cover Removal                                         |      |

| Figure F-1.  | Revision A and B SCXI-1140 Signal Conditioning Module | F-1  |

| Figure F-2.  | Revision A and B SCXI-1140 Parts Locator Diagram      | F-2  |

## Tables

| Table | 2-1. | Digital Jumper Settings                                              | .2-5  |

|-------|------|----------------------------------------------------------------------|-------|

| Table | 2-2. | Input Mode Selection Jumpers                                         |       |

| Table | 2-3. | Gain Switches for Each Channel                                       | .2-7  |

| Table | 2-4. | Switch Settings for Gain Selection                                   |       |

| Table | 2-5. | SCXIbus to SCXI-1140 Rear Signal Connector to Data Acquisition Board |       |

|       |      |                                                                      | .2-22 |

| Table | 3-1. | SCXIbus Equivalents for the Rear Signal Connector                    | .3-6  |

| Table | 5-1. | SCXI-1140 Rear Signal Connector Pin Equivalences                     | .5-2  |

| Table | 6-1. | Calibration Component Identification                                 | .6-3  |

| Table |      | SCXI-1140 and MIO-16 Pinout Equivalences                             | .E-2  |

| Table | E-2. | SCXI-1341 Pin Translations                                           | .E-4  |

| Table | E-3. | SCXI-1342 Pin Translations                                           | .E-6  |

| Table | E-4. | SCXI-1343 Pin Connections                                            | .E-12 |

# Chapter 1 Introduction

This chapter describes the SCXI-1140; lists the contents of your SCXI-1140 kit; describes the optional software, optional equipment, and custom cables; and explains how to unpack the SCXI-1140 kit.

The SCXI-1140 is a class I module that operates as an eight-channel simultaneously sampling differential-input gain block. The SCXI-1140 is an SCXIbus module for signal conditioning of high-level and low-level AC and DC signal sources. The SCXI-1140 operates with full functionality with the National Instruments MIO-16 boards. You can use the Lab-NB, the Lab-PC, the Lab-PC+, the Lab-LC, and the PC-LPM-16 boards with the SCXI-1140, but they cannot scan the module; these boards can only perform single-channel reads. You can control the SCXI-1140 with either the data acquisition board or the SCXIbus Slot 0 controller. Each SCXI-1140 module can multiplex its channels into a single data acquisition board channel, although separate outputs are available as well. You can multiplex several SCXI-1140s into a single channel, thus greatly increasing the number of analog input signals that can be digitized.

An additional shielded terminal block has screw terminals for easy signal attachment to the SCXI-1140. In addition to the analog input signal terminals, there is a terminal for a digital input signal that you can use to place the module into Hold mode and thus initiate a data acquisition sequence.

You can use the SCXI-1140 in a wide range of applications ranging from thermocouple and lowlevel DC measurement to phase measurement. With the SCXI-1140, the SCXI chassis can serve as a fast-scanning signal conditioner for laboratory testing, production testing, and industrial process monitoring.

A 50-pin male ribbon connector at the rear of the module connects the module to the MIO-16 boards. The Lab boards and the PC-LPM-16 require special adapters. At the front, a 96-pin DIN C connector connects the analog inputs to an optional terminal block. A mating DIN C connector and shell are also available.

# What Your Kit Should Contain

The contents of the SCXI-1140 kit (part number 776572-40) are listed as follows.

| Kit Component         | Part Number |

|-----------------------|-------------|

| SCXI-1140 Module      | 181705-01   |

| SCXI-1140 User Manual | 320410-01   |

If your kit is missing any of the components, contact National Instruments.

# **Optional Software**

This manual contains complete instructions for directly programming the SCXI-1140. You can order separate software packages for controlling the SCXI-1140 from National Instruments.

When you combine the PC, AT, and MC data acquisition boards with the SCXI-1140, you can use LabVIEW for Windows or LabWindows for DOS. LabVIEW and LabWindows are innovative program development software packages for data acquisition and control applications. LabVIEW uses graphical programming, whereas LabWindows enhances Microsoft C and QuickBASIC. Both packages include extensive libraries for data acquisition, instrument control, data analysis, and graphical data presentation.

Your National Instruments data acquisition board is shipped with the NI-DAQ software. NI-DAQ has a library of functions that can be called from your application programming environment. These functions include routines for analog input (A/D conversion), buffered data acquisition (high speed A/D conversion), analog output (D/A conversion), waveform generation, digital I/O, counter/timer, SCXI, RTSI, and self-calibration. NI-DAQ maintains a consistent software interface among its different versions so you can switch between platforms with minimal modifications to your code.

You can also use the SCXI-1140, together with the PC, AT, and MC data acquisition boards, with NI-DAQ software for DOS/Windows/LabWindows. NI-DAQ software for DOS/Windows/LabWindows comes with language interfaces for Professional BASIC, Turbo Pascal, Turbo C, Turbo C++, Borland C++, and Microsoft C for DOS; and Visual Basic, Turbo Pascal, Microsoft C with SDK, and Borland C++ for Windows. NI-DAQ software for DOS/Windows/LabWindows is on high-density 5.25 in. and 3.5 in. diskettes.

You can use the SCXI-1140, together with the NB Series data acquisition boards, with LabVIEW for Macintosh, a software system that features interactive graphics, a state-of-the-art user interface, and a powerful graphical programming language. The LabVIEW Data Acquisition VI Library, a series of VIs for using LabVIEW with National Instruments boards, is included with LabVIEW. The LabVIEW Data Acquisition VI Library is functionally equivalent to the NI-DAQ software for Macintosh.

You can also use the SCXI-1140, combined with the NB Series data acquisition boards, with NI-DAQ software for Macintosh. NI-DAQ software for Macintosh, which is shipped with all National Instruments Macintosh data acquisition boards, comes with language interfaces for MPW C, THINK C, Pascal, and Microsoft QuickBASIC. Any language that uses Device Manager Toolbox calls can access NI-DAQ software for Macintosh.

# **Optional Equipment**

| Equipment                                      | Part Number |

|------------------------------------------------|-------------|

| NB6 cable                                      |             |

| 0.5 m                                          | 181305-01   |

| 1.0 m                                          | 181305-10   |

| SCXI-1301 sample-and-hold terminal block       | 776573-01   |

| SCXI-1310 96-pin connector and shell           | 776573-10   |

| SCXI-1340 cable assembly                       | 776574-40   |

| SCXI-1341 Lab-NB/Lab-PC/Lab-PC+ cable assembly | 776574-41   |

| SCXI-1342 PC-LPM-16 cable assembly             | 776574-42   |

| SCXI-1343 rear screw terminal adapter          | 776574-43   |

| SCXI-1344 Lab-LC cable assembly                | 776574-44   |

| SCXI-1346 shielded multichassis cable adapter  | 776574-46   |

| SCXI-1347 SCXI shielded cable assembly         |             |

| with 1 m cable                                 | 776574-471  |

| with 2 m cable                                 | 776574-472  |

| with 5 m cable                                 | 776574-475  |

| with 10 m cable                                | 776574-470  |

| SCXI-1349 SCXI shielded cable assembly         |             |

| with 1 m cable                                 | 776574-491  |

| with 2 m cable                                 | 776574-492  |

| with 5 m cable                                 | 776574-495  |

| with 10 m cable                                | 776574-490  |

| SCXI-1350 multichassis adapter                 | 776575-50   |

| Standard ribbon cable                          |             |

| 0.5 m                                          | 180524-05   |

| 1.0 m                                          | 180524-10   |

Refer to the *Signal Connections* section in Chapter 2 and Appendix E, *SCXI-1140 Cabling*, for additional information on cabling, connectors, and adapters.

## **Custom Cables**

The SCXI-1140 rear signal connector is a 50-pin male ribbon-cable header. The manufacturer part number of the header National Instruments uses is as follows:

• AMP Inc. (part number 1-103310-0)

The mating connector for the SCXI-1140 rear signal connector is a 50-position polarized ribbonsocket connector with strain relief. National Instruments uses a polarized or keyed connector to prevent inadvertent upside-down connection to the SCXI-1140. Recommended manufacturer part numbers for this mating connector are as follows:

- Electronic Products Division/3M (part number 3425-7650)

- T&B/Ansley Corporation (part number 609-5041CE)

Part numbers of standard 50-conductor 28 AWG stranded ribbon cables that work with these connectors are as follows:

- Electronic Products Division/3M (part number 3365/50)

- T&B/Ansley Corporation (part number 171-50)

The SCXI-1140 front connector is a 96-pin DIN C male connector. Recommended manufacturer part numbers for this connector are as follows:

- Harting Electronik Inc. (part number 09-03-396-6921)

- Panduit Corporation (part number 100-096-033)

The mating connector for the SCXI-1140 front connector is a 96-pin DIN C female connector. The recommended manufacturer part number for this mating connector is as follows:

- AMP Inc. (part number 535020-1; right-angle pins)

- Panduit Corporation (part number 100-096-434; straight-solder eyelet pins)

# Unpacking

Your SCXI-1140 module is shipped in an antistatic package to prevent electrostatic damage to the module. Several components on the board can be damaged by electrostatic discharge. To avoid such damage in handling the module, take the following precautions:

- Touch the package to a metal part of your SCXI chassis before removing the module from the package.

- Remove the module from the package and inspect it for loose components or any other sign of damage. Notify National Instruments if the module appears damaged in any way. *Do not* install a damaged module into your SCXI chassis.

# **Chapter 2 Configuration and Installation**

This chapter describes the SCXI-1140 jumper configurations, DIP switch settings, installation of the SCXI-1140 into the SCXI chassis, signal connections to the SCXI-1140, and cable wiring.

# **Module Configuration**

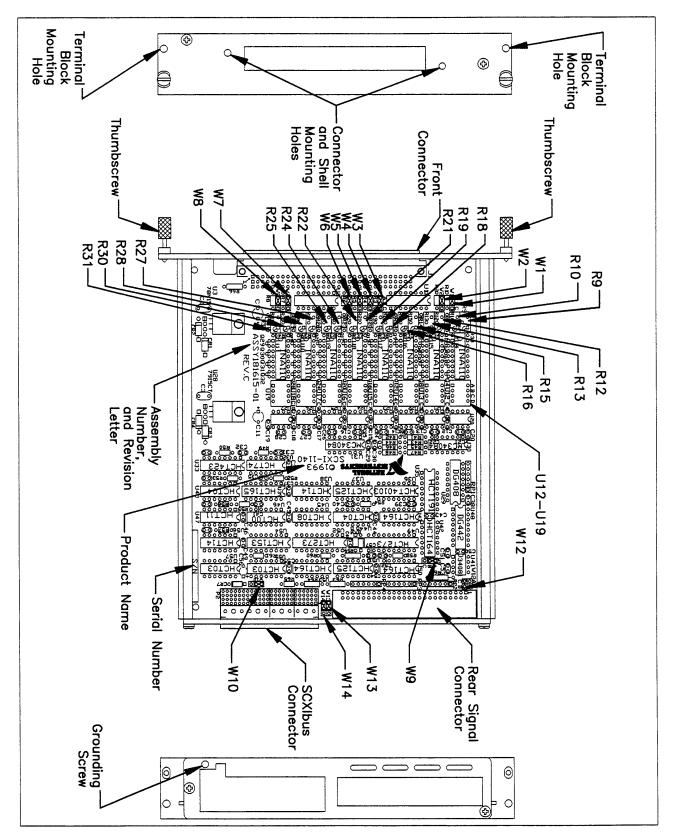

The SCXI-1140 includes 14 jumpers and eight DIP switches that are shown in the parts locator diagram in Figure 2-1.

Figure 2-1. SCXI-1140 Parts Locator Diagram

The jumpers are used as follows:

- Fixed jumpers

- Jumper W10 is reserved and you should not reconfigure it.

- On Revision A and B modules, jumper W11 carries the SLOTOSEL\* signal from the rear signal connector, after buffering, to the SCXIbus INTR\* line. Leave jumper W11 in the factory-set position (position A-B). On Revision C or later modules, jumper W11 does not exist.

- On Revision A and B modules, jumper W13 is unused and you should not connect it.

- User-configurable jumpers

- Jumpers W1 through W8 ground the negative inputs of each input through  $100 \text{ k}\Omega$  resistors for floating sources and transducers.

- Jumper W9 allows the module to connect to a single-ended data acquisition board instead of a full differential board.

- Jumper W12 determines the connections between the SCXIbus guard, chassis ground, and the data acquisition board analog ground.

- Jumper W14 carries the SCXIbus MISO line, after buffering, to the SERDATOUT signal on the rear signal connector.

- On Revision C and later modules, jumper W13 connects a pullup resistor to the SERDATOUT signal on the rear signal connector.

The module also includes eight four-position DIP switches that you use to set the gains of the eight channels. The DIP switches are shown in the parts locator diagram, Figure 2-1, as U12 through U19.

Further configuration of the module is software controlled and is discussed in Chapter 5, *Programming*.

## **Digital Signal Connections**

The SCXI-1140 has three jumpers dedicated for communication between the data acquisition board and the SCXIbus. These jumpers are W11, W13, and W14.

## Jumper W11

On Revision A and B modules, position A-B connects SLOT0SEL\* to the SCXIbus INTR\* line, after buffering. This is the factory-default setting and you should not change it. In this setting, the data acquisition board controls the SCXIbus INTR\* line. See the *Timing Requirements and Communication Protocol* section later in this chapter, and Chapter 5, *Programming*, for information on using the INTR\* line. See Appendix E, *SCXI-1140 Cabling*, for pin equivalences of the SCXI-1140 rear signal connector and the data acquisition board I/O connector.

Position B-C is reserved and you should not use it.

On Revision C or later modules, jumper W11 does not exist. SLOT0SEL\* is always buffered to the INTR\* line.

### Jumper W14

Position A-B connects the SCXIbus MISO line, after buffering, to the SERDATOUT pin of the rear signal connector. When jumper W14 is in Position A-B and jumper W13 is properly set, the data acquisition board can read the Module ID Register of the SCXI-1140. See the *Timing Requirements and Communication Protocol* section later in this chapter, and Chapter 5, *Programming*, for information on reading the Module ID Register. See Appendix E, *SCXI-1140 Cabling*, for the SCXI-1140 rear signal connector and the data acquisition board I/O connector pin equivalences.

Position B-C disconnects SERDATOUT from the SCXIbus MISO line.

### Jumper W13

On Revision A and B modules, jumper W13 should not be connected. On Revision C or later modules, position A-B connects a  $2.2k\Omega$  pullup resistor to the SERDATOUT line. Position B-C does not connect the pullup resistor to the SERDATOUT line.

### Using Jumpers W13 and W14

If the SCXI-1140 is not cabled to a data acquisition board, the positions of these jumpers do not matter, so leave them in their factory default positions (both in position A-B).

If the SCXI-1140 is cabled to a data acquisition board, and the SCXI chassis that the SCXI-1140 is in, is the only SCXI chassis cabled to that data acquisition board, leave the jumpers in their factory default positions (both in position A-B).

If the SCXI-1140 is cabled to a data acquisition board, and there are multiple SCXI chassis cabled to that data acquisition board with shielded cables (you are using SCXI-1346 shielded cable multi-chassis adapters), leave the jumpers in their factory default positions (both in position A-B).

If the SCXI-1140 is cabled to a data acquisition board, and there are multiple SCXI chassis cabled to that data acquisition board with ribbon cables (you are using SCXI-1350 multi-chassis adapters), leave jumper W14 in its factory default position (position A-B). On all but one of the SCXI-1140s that are cabled to the data acquisition board, move jumper W13 to position B-C. It does not matter which of the SCXI-1140 modules that are cabled to the data acquisition board has jumper W13 set to position A-B. If you have different types of modules cabled to the data acquisition board, those different modules will have jumpers similar to W14 and W13 of the SCXI-1140. Set those jumpers on the different modules using the same method described here for the SCXI-1140.

On Revision A and B SCXI-1140s, jumper W13 is not used. You set jumper W14 as explained in the cases above, except in the case of a multiple chassis ribbon cable system. In a multichassis ribbon cable system with Revision A and B SCXI-1140s cabled to the data acquisition board, you can access the MISO line in only one chassis. Pick one of the chassis and set jumper W14 to position A-B on the SCXI-1140 in that chassis that is cabled to the data acquisition board. On the SCXI-1140s that are in the other chassis and cabled to the data acquisition board, set jumper W14 to position B-C. Notice that you will only be able to access digital information from the chassis that has the SCXI-1140 with jumper W14 set to position A-B.

On Revision C and later modules, the SERDATOUT line is driven by an open-collector driver, which is a driver that actively drives low or goes to a high-impedance state, relying on a pullup resistor to make the signal line go high. When using a single chassis, leave W13 and W14 in position A-B (factory default) on the SCXI-1140 that is connected to the data acquisition board. In this configuration, jumper W13 connects the necessary pullup resistor to the SERDATOUT line, and the module drives MISO to SERDATOUT. When using multiple chassis, leave jumper W14 in position A-B on all of the SCXI-1140s that are cabled to the data acquisition board. You should set jumper W13 in position A-B on only one (it does not matter which one) of the SCXI-1140s that are cabled to the data acquisition board. If too many pullup resistors are attached to the SERDATOUT line, the drivers cannot drive the line low. See Table 2-1 for a description and configuration of the jumper settings.

| Jumper | Description                                                                  | Configuration |

|--------|------------------------------------------------------------------------------|---------------|

| W14    | Factory-default setting; connects MISO to SERDATOUT                          | A B C         |

| W14    | Parking position                                                             | A B C         |

| W10    | Factory-default setting                                                      |               |

| W11    | Factory-default setting (revisions A and B modules only)                     | A<br>B        |

| W13    | Factory-default setting; connects pullup to SERDATOUT (revision C and later) |               |

| W13    | Parking position (not connected on revisions A or B modules)                 | A B C         |

Table 2-1. Digital Jumper Settings

## **Analog Configuration**

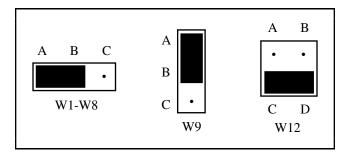

The SCXI-1140 has 10 analog configuration jumpers–W1 through W9, and W12–and eight gainsetting, four-position DIP switches–U12 through U19.

### **Input Mode Selection**

### Jumpers W1 through W8

Position A-B leaves the negative input of the instrumentation amplifier connected only to the front connector. This is the factory-default setting.

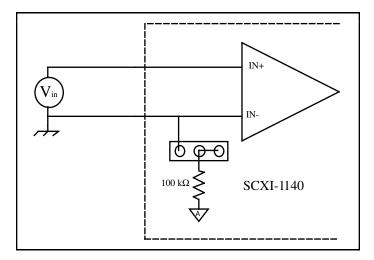

Position B-C connects the negative input of the instrumentation amplifier to the module analog ground through a 100 k $\Omega$  resistor. This setting is useful for keeping floating (non-ground referenced) sources from saturating the instrumentation amplifier. Table 2-2 shows the input mode jumper and channel selections.

| Channel | Use Jumper |

|---------|------------|

| 0       | W1         |

| 1       | W2         |

| 2       | W3         |

| 3       | W4         |

| 4       | W5         |

| 5       | W6         |

| 6       | W7         |

| 7       | W8         |

| Table 2-2. | Input Mode | Selection | Jumpers |

|------------|------------|-----------|---------|

|------------|------------|-----------|---------|

## **Output Selection**

Jumper W9

Position A-B leaves pin 19 (AIGND/NC) of the rear signal connector unconnected and is the factory-default setting.

Position B-C connects the module analog ground to pin 19 (AIGND/NC) of the rear signal connector. Use this position for MIO boards operating in NRSE mode.

## Grounding and Shielding

### Jumper W12

Position A-B connects the module analog ground to the analog bus guard.

Position A-C connects the module analog ground to pins 1 and 2 (AIGND/GUARD) of the rear signal connector. Use this position for all boards operating in RSE mode, and for the Lab-PC+ operating in NRSE mode.

Position B-D connects the data acquisition board analog ground to the analog bus guard.

Position C-D leaves the grounds disconnected and is the factory-default setting.

Figure 2-2. Analog Jumpers (Factory Setting)

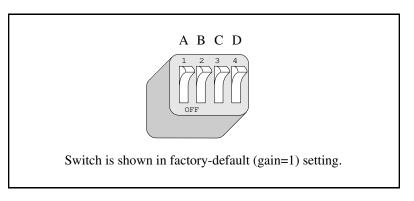

## Gain Selection

You can use each DIP switch to set the gain of its channel as shown in Table 2-3.

| Channel | Use DIP Switch |

|---------|----------------|

| 0       | U12            |

| 1       | U13            |

| 2       | U14            |

| 3       | U15            |

| 4       | U16            |

| 5       | U17            |

| 6       | U18            |

| 7       | U19            |

Table 2-3. Gain Switches for Each Channel

Leaving all four switches in the open (number side up) position selects a gain of one, as shown in Figure 2-3. This setting is the factory default.

Figure 2-3. Gain Switches for Each Channel

Closing switch A selects a gain of 500.

Closing switch B selects a gain of 200.

Closing switch C selects a gain of 100.

Closing switch D selects a gain of 10.

You can select other gains by closing more than one switch, as shown in Table 2-4.

| Desired Gain                                                                      | Close Switches                                                           |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| $ \begin{array}{r} 1\\ 10\\ 100\\ 200\\ 300\\ 500\\ 600\\ 700\\ 800 \end{array} $ | None<br>D<br>C<br>B<br>B and C<br>A<br>A and C<br>A and B<br>A, B, and C |

Table 2-4. Switch Settings for Gain Selection

# **Hardware Installation**

You can install the SCXI-1140 in any available SCXI chassis. After you have made any necessary changes and have verified and recorded the jumper and DIP switch settings (a form is included for this purpose in Appendix G, *Customer Communication*), you are ready to install the SCXI-1140. The following are general installation instructions, but consult the user manual of your SCXI chassis for specific instructions and warnings.

- 1. Turn off the computer that contains the data acquisition board.

- 2. Turn off the SCXI chassis. Do not insert the SCXI-1140 into a chassis that is turned on.

- 3. Insert the SCXI-1140 into the board guides. Gently guide the module into the back of the slot until the connectors make good contact. If a cable assembly has already been installed in the rear of the chassis, the module and cable assembly must be firmly engaged; however, *do not force* the module into place.

- 4. Screw the front mounting panel of the SCXI-1140 to the top and bottom threaded strips of your SCXI chassis.

- 5. If you are going to connect this module to an MIO-16 data acquisition board, attach the connector at the metal end of the SCXI-1340 cable assembly to the rear signal connector on the SCXI-1140 module. Screw the rear panel to the rear threaded strip. Attach the loose end of the cable to the MIO-16 board.

- **Notes:** If you already have another module in your chassis that is cabled to your data acquisition board, you generally do not need to connect additional cabling to the SCXI-1140. Typically, only one module in a chassis is cabled to a board. If your chassis has different types of modules, cable the data acquisition board to one of the SCXI-1140 modules.

For installation procedures with other SCXI accessories and data acquisition boards, consult Appendix E, *SCXI-1140 Cabling*.

- 6. Check the installation.

- 7. Turn on the SCXI chassis.

- 8. Turn on the computer.

The SCXI-1140 module is installed and ready for operation.

# **Signal Connections**

This section describes the input and output signal connections to the SCXI-1140 module via the SCXI-1140 front and rear signal connectors, and includes specifications and connection instructions for the SCXI-1140 connector signals.

**Warning:** Connections that exceed any of the maximum ratings of input or output signals on the SCXI-1140 can result in damage to the SCXI-1140 module, to the SCXIbus, to any connected data acquisition board, and to the computer in which the data acquisition board is installed. Maximum input ratings for each signal are given in this chapter under the discussion of that signal. National Instruments is *not* liable for any damages resulting from such signal connections.

# **The Front Connector**

Figure 2-4 shows the pin assignments for the SCXI-1140 front connector.

| 32 $IN0+$ $\circ$ $\circ$ $\circ$ $IN0-$ 30 $IN1+$ $\circ$ $\circ$ $\circ$ $IN1-$ 29 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 28 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 26 $IN2+$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $O$ $\circ$ $\circ$ $O$ $IN3-$ 24 $IN3+$ $\circ$ $\circ$ $O$ $IN3-$ 25 $O$ $\circ$ $O$ $O$ $IN3-$ 26 $IN3+$ $\circ$ $\circ$ $O$ $IN3-$ 27 $IN3+$ $\circ$ $\circ$ $O$ $IN4-$ 20 $IN4+$ $\circ$ $\circ$ $O$ $IN4-$ 10 $O$ $\circ$ $O$ $O$ $IN5-$ 16       AGND $\circ$ $\circ$ $O$ $O$ $IN7-$ 16       IN6+ $\circ$ $\circ$                                                                                                                                                                                                                                                                                                                                   | Pin<br>Number | Signal<br>Name | A             | Columr<br>B | <sup>1</sup> C | Signal<br>Name |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|----------------|---------------|-------------|----------------|----------------|

| 31       0       0       0       0         30 $IN1+$ 0       0       0       0         28 $AGND$ 0       0       0 $AGND$ 27       0       0       0       0 $IN1-$ 26 $IN2+$ 0       0 $O$ $IN2-$ 25       0       0       0 $IN3-$ 24 $IN3+$ 0 $O$ $O$ 22 $AGND$ $O$ $O$ $IN4-$ 19 $O$ $O$ $O$ $IN4-$ 19 $IN5+$ $O$ $O$ $IN5-$ 17 $O$ $O$ $O$ $IN5-$ 18 $IN5+$ $O$ $O$ $IN6-$ 15 $O$ $O$ $O$ $IN7-$ 16 $AGND$ $O$ $O$ $IN7-$ 14 $IN6+$ $O$ $O$ $O$ 12 $IN7+$ $O$ $O$ $O$ 10 $O$ $O$ $O$ $O$                                                                                                                                                                                                                                                                                                                                                                                                                         |               |                |               |             |                |                |

| 30 $IN1+$ $\circ$ $\circ$ $\circ$ $IN1-$ 29 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 28 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 26 $IN2+$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $O$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $O$ $IN2-$ 26 $IN2+$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $\circ$ $\circ$ $\circ$ $\circ$ $IN3-$ 24 $IN3+$ $\circ$ $\circ$ $\circ$ $IN4-$ 20 $IN4+$ $\circ$ $\circ$ $\circ$ $IN5-$ 18 $IN5+$ $\circ$ $\circ$ $\circ$ $IN6-$ 15 $\circ$ $\circ$ $\circ$ $\circ$ $IN7-$ 16       AGND $\circ$ $\circ$ $\circ$ $\circ$ </td <td>32</td> <td>IN0+</td> <td>+-0</td> <td>0</td> <td>•</td> <td>- INO-</td>                                                                                                                                                                                           | 32            | IN0+           | +-0           | 0           | •              | - INO-         |

| 29 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $AGND$ 27 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 26 $IN2+$ $\circ$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $\circ$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $AGND$ $\circ$ $\circ$ $\circ$ $IN3-$ 24 $IN3+$ $\circ$ $\circ$ $\circ$ $IN3-$ 25 $AGND$ $\circ$ $\circ$ $AGND$ $\circ$ $\circ$ 20 $IN4+$ $\circ$ $\circ$ $\circ$ $IN4 \circ$ $\circ$ $\circ$ $IN5-$ 17 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ $IN5 IN5 IN7 IN6 IN7 IN7 IN7 IN7 IN7 IN7 IN7 IN7 IN7 IN7-$                                                                                                                                                                                                                                                                                     | 31            |                | 0             | 0           | 0              |                |

| 28       AGND $\circ$ $\circ$ $\circ$ $AGND$ 27 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 26 $IN2+$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 24 $IN3+$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $\circ$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $\circ$ $\circ$ $\circ$ $\circ$ $AGND$ 24 $IN3+$ $\circ$ $\circ$ $\circ$ $AGND$ 25 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 20 $IN4+$ $\circ$ $\circ$ $\circ$ $IN4-$ 19 $O$ $\circ$ $\circ$ $O$ $IN5-$ 17 $O$ $\circ$ $\circ$ $O$ $O$ $IN5-$ 16 $AGND$ $\circ$ $\circ$ $\circ$ $IN6 IN7-$ 15 $\circ$ $\circ$ $\circ$ $\circ$ $O$ $O$ 10 $\circ$ $\circ$ <t< td=""><td>30</td><td>IN1+</td><td>+-0</td><td>0</td><td>•</td><td>- IN1-</td></t<>                                                                                                                                                                                                         | 30            | IN1+           | +-0           | 0           | •              | - IN1-         |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 29            |                | 0             | 0           | 0              |                |

| 26 $IN2+$ $\circ$ $\circ$ $\circ$ $IN2-$ 25 $IN3+$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $\circ$ $\circ$ $\circ$ $\circ$ $IN3-$ 23 $\circ$ $\circ$ $\circ$ $\circ$ $aGND$ 21 $\circ$ $\circ$ $\circ$ $AGND$ 20 $IN4+$ $\circ$ $\circ$ $\circ$ 18 $IN5+$ $\circ$ $\circ$ $IN5-$ 17 $\circ$ $\circ$ $\circ$ $AGND$ 16 $AGND$ $\circ$ $\circ$ $IN5-$ 17 $\circ$ $\circ$ $\circ$ $IN5-$ 16 $AGND$ $\circ$ $\circ$ $IN5-$ 17 $\circ$ $\circ$ $\circ$ $IN6-$ 13 $IN6+$ $\circ$ $\circ$ $IN7-$ 11 $IN7+$ $\circ$ $\circ$ $\circ$ 12 $IN7+$ $\circ$ $\circ$ $\circ$ 10 $\circ$ $\circ$ $\circ$ $\circ$ 10 $\circ$ $\circ$ $\circ$                                                                                                                                                                                                                                                                                                 | 28            | AGND           | +-0           | 0           | •              | - AGND         |

| 25       0       0       0       0         24       IN3+       0       0       0       IN3-         23       0       0       0       0       0         22       AGND       0       0       0       AGND         20       IN4+       0       0       0       IN4-         19       0       0       0       0       IN4-         19       0       0       0       0       IN5-         17       0       0       0       0       IN5-         16       AGND       0       0       0       IN5-         17       0       0       0       IN6-       IN6-         13       0       0       0       IN7-       IN7-         11       0       0       0       IN7-       IN7-         11       0       0       0       IN7-       IN7-         10       0       0       0       IN7-       IN7-         10       0       0       0       IN7-       IN7-         10       0       0       0       IN7-       IN7-       IN7- | 27            |                | 0             | 0           | 0              |                |

| 24 $N3+$ $\circ$ $\circ$ $\circ$ $N3-$ 23 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 21 $\circ$ $\circ$ $\circ$ $\circ$ $AGND$ 20 $IN4+$ $\circ$ $\circ$ $\circ$ $IN4-$ 19 $\circ$ $\circ$ $\circ$ $O$ $IN4-$ 19 $\circ$ $\circ$ $\circ$ $IN4-$ 19 $\circ$ $\circ$ $\circ$ $O$ 18 $IN5+$ $\circ$ $\circ$ $O$ 16 $AGND$ $\circ$ $\circ$ $AGND$ 15 $\circ$ $\circ$ $\circ$ $AGND$ 15 $\circ$ $\circ$ $\circ$ $O$ 14 $IN6+$ $\circ$ $\circ$ $O$ $IN7-$ 11 $\circ$ $\circ$ $\circ$ $\circ$ $O$ 10 $\circ$ $\circ$ $\circ$ $\circ$ $O$ 9 $DGND$ $\circ$ $\circ$ $\circ$ $O$ 7 $\circ$ $\circ$ $\circ$ $\circ$ $O$                                                                                                                                                                                                                                                                                                               | 26            | IN2+           | $\rightarrow$ | 0           | •              | - IN2-         |

| 23 $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$ $0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 25            |                | 0             | 0           | 0              |                |

| 22       AGND $\circ$ $\circ$ $\circ$ $AGND$ 21 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 20 $IN4+$ $\circ$ $\circ$ $\circ$ $IN4-$ 19 $\circ$ $\circ$ $\circ$ $\circ$ $IN4-$ 19 $\circ$ $\circ$ $\circ$ $\circ$ $IN4-$ 19 $\circ$ $\circ$ $\circ$ $\circ$ $IN5-$ 17 $\circ$ $\circ$ $\circ$ $\circ$ $IN5-$ 17 $\circ$ $\circ$ $\circ$ $\circ$ $AGND$ 16 $AGND$ $\circ$ $\circ$ $\circ$ $AGND$ 15 $\circ$ $\circ$ $\circ$ $\circ$ $AGND$ 15 $\circ$ $\circ$ $\circ$ $\circ$ $IN6-$ 13 $IN6+$ $\circ$ $\circ$ $\circ$ $IN7-$ 11 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 10 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 11 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$                                                                                                                                                                                                                                                             | 24            | IN3+           | +-•           | ο           | •              | - IN3-         |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23            |                | 0             | ο           | 0              |                |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 22            | AGND           | +-0           | ο           | •              | - AGND         |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21            |                | 0             | ο           | 0              |                |

| 18 $IN5+$ $\circ$ $\circ$ $o$ $o$ 17 $AGND$ $\circ$ $\circ$ $o$ $o$ 16 $AGND$ $\circ$ $\circ$ $o$ $AGND$ 15 $\circ$ $\circ$ $\circ$ $o$ $o$ 14 $IN6+$ $\circ$ $\circ$ $o$ $IN6-$ 13 $\circ$ $\circ$ $\circ$ $o$ $o$ 12 $IN7+$ $\circ$ $\circ$ $o$ $o$ 10 $\circ$ $\circ$ $\circ$ $o$ $o$ 9 $DGND$ $\circ$ $\circ$ $O$ $DGND$ 7 $\circ$ $\circ$ $\circ$ $\circ$ $O$ 8 $DGND$ $\circ$ $\circ$ $\circ$ $O$ 7 $\circ$ $\circ$ $\circ$ $\circ$ $O$ 6 $HOLDTRIG$ $\circ$ $\circ$ $\circ$ $\circ$ 3 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 2 $DGND$ $\circ$ $\circ$ $\circ$ $\circ$                                                                                                                                                                                                                                                                                                                                         | 20            | IN4+           | +-0           | 0           | •              | - IN4-         |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19            |                | 0             | 0           | 0              |                |

| 16       AGND $\circ$ $\circ$ $\circ$ AGND         15       IN6+ $\circ$ $\circ$ $\circ$ IN6-         14       IN6+ $\circ$ $\circ$ $\circ$ IN6-         13       IN7+ $\circ$ $\circ$ $\circ$ IN7-         11       IN7+ $\circ$ $\circ$ $\circ$ IN7-         10 $\circ$ $\circ$ $\circ$ $\circ$ $\circ$ 9       IGND $\circ$ $\circ$ $\circ$ IGND         7       IOGND $\circ$ $\circ$ IGND       IGND         6       HOLDTRIG $\circ$ $\circ$ $\circ$ IGND         5       IOGND $\circ$ $\circ$ $\circ$ IGND         3       IOGND $\circ$ $\circ$ $\circ$ $\circ$ 2       IOGND $\circ$ $\circ$ $\circ$ $\circ$                                                                                                                                                                                                                                                                                                | 18            | IN5+           | +-•           | ο           | •              | - IN5-         |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 17            |                | 0             | ο           | 0              |                |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 16            | AGND           | +-0           | 0           | •              | - AGND         |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 15            |                | 0             | 0           | 0              |                |

| 12       IN7+       •       •       •       IN7-         11       •       •       •       •       •         10       •       •       •       •       •         9       •       •       •       •       •         9       •       •       •       •       •         9       •       •       •       •       •         9       •       •       •       •       •         9       •       •       •       •       •         9       •       •       •       •       •       •         9       •       •       •       •       •       •       •         8       DGND       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •       •     | 14            | IN6+           | $+ \circ$     | 0           | •              | - IN6-         |

| 11       0       0       0         10       0       0       0         9       0       0       0         8       DGND       0       0       0         7       0       0       0       0         6       HOLDTRIG       0       0       0         5       0       0       0       0         3       0       0       0       0         2       DGND       0       0       0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 13            |                | 0             | 0           | 0              |                |

| $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 12            | IN7+           | $+ \circ$     | 0           | •              | - IN7-         |