#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

# **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

NI-9203

# **USER GUIDE AND SPECIFICATIONS**

# **NI cDAQ-9172**

Français Deutsch 日本語 한국어 简体中文 ni.com/manuals

# **Contents**

| Introduction                             | . 4  |

|------------------------------------------|------|

| Safety Guidelines                        | . 5  |

| Safety Guidelines for Hazardous Voltages | . 5  |

| Related Documentation                    |      |

| Device Documentation and Specifications  | . 9  |

| Training Courses                         | . 9  |

| Technical Support on the Web             | . 9  |

| Installing the Software                  | . 10 |

| Installing NI-DAQmx                      | . 10 |

| Installing Other Software                | . 10 |

| Installing the NI cDAQ-9172              |      |

| Mounting the NI cDAQ-9172                | . 12 |

| NI 9901 Desktop Mounting Kit             | . 12 |

| NI 9910 DIN-Rail Kit                     | . 13 |

| NI 9905 Panel Mount Kit                  | . 13 |

| Setting Up the NI cDAQ-9172              | . 15 |

| Understanding LED Indications            | . 17 |

| Active LED                               | . 17 |

| Ready LED                                | . 17 |

| Using the NI cDAQ-9172                   | . 18 |

| C Series I/O Modules                     | . 18 |

| Correlated vs. Static DIO Modules        | . 19 |

| cDAQ Module Interface                    | . 19 |

| USB-STC2                                 | . 19 |

| AI and AO Sample Timing                  | . 19 |

| Triggering Modes                         | . 19 |

| Independent Data Streams                 |      |

| PFI Signals                              |      |

| Flexible Counter/Timers                  | . 20 |

| Analog Input                                         | 20 |

|------------------------------------------------------|----|

| Analog Input Triggering                              | 20 |

| AI Start Trigger Signal                              | 21 |

| AI Reference Trigger Signal                          | 22 |

| AI Pause Trigger Signal                              | 24 |

| Analog Input Timing Signals                          | 24 |

| AI Sample Clock                                      |    |

| AI Sample Clock Timebase                             |    |

| Convert Behavior For Analog Input Modules            | 25 |

| Getting Started with AI Applications in Software     | 28 |

| Analog Output                                        |    |

| Analog Output Data Generation Methods                | 28 |

| Software-Timed Generations                           | 29 |

| Hardware-Timed Generations                           | 29 |

| Analog Output Triggering                             | 30 |

| Analog Output Timing Signals                         | 31 |

| AO Sample Clock                                      | 31 |

| AO Start Trigger Signal                              |    |

| AO Pause Trigger Signal                              |    |

| Minimizing Glitches on the Output Signal             |    |

| Getting Started with AO Applications in Software     |    |

| Digital I/O                                          |    |

| Correlated vs. Static DIO Modules                    |    |

| Static DIO                                           |    |

| Digital Waveform Acquisition (Correlated Input)      |    |

| DI Sample Clock Signal                               |    |

| Digital Waveform Generation (Correlated Output)      |    |

| Buffered Digital Waveform Generation                 |    |

| Change Detection Event                               |    |

| Routing Change Detection Event to an Output Terminal |    |

| Change Detection Acquisition                         |    |

| Digital Input/Output Configuration for NI 9401       |    |

| PFI                                                  |    |

| Counters                                             |    |

| Counter Input Applications                           |    |

| Counting Edges                                       |    |

| Pulse-Width Measurement                              |    |

| Period Measurement                                   |    |

| Semi-Period Measurement                              |    |

| Frequency Measurement                                |    |

| Position Measurement                                 |    |

| Two-Signal Edge-Separation Measurement               |    |

| Counter Output Applications                          |    |

| Simple Pulse Generation                              |    |

| Pulse Train Generation                               |    |

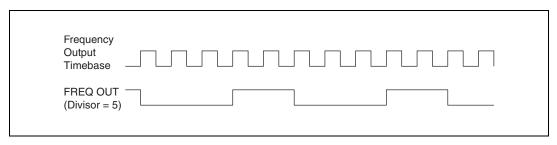

| Frequency Generation                                 |    |

| Frequency Division                                   | 63 |

| Counter Timing Signals                                           |    |

|------------------------------------------------------------------|----|

| Counter <i>n</i> Source Signal                                   |    |

| Counter <i>n</i> Gate Signal                                     |    |

| Counter n Aux Signal                                             |    |

| Counter $n$ A, Counter $n$ B, and Counter $n$ Z Signals          |    |

| Counter n Up_Down Signal                                         |    |

| Counter n HW Arm Signal                                          |    |

| Counter <i>n</i> Internal Output and Counter <i>n</i> TC Signals |    |

| Frequency Output Signal                                          |    |

| Default Counter/Timer Routing                                    |    |

| Counter Triggering                                               |    |

| Other Counter Features                                           |    |

| Cascading Counters                                               |    |

| Counter Filters                                                  |    |

| Prescaling                                                       |    |

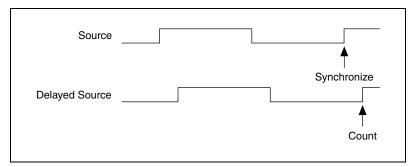

| Duplicate Count Prevention                                       | 71 |

| Synchronization Modes                                            | 73 |

| Digital Routing and Clock Generation                             | 75 |

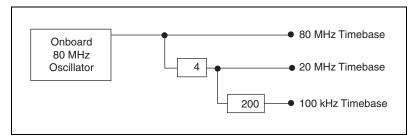

| Clock Routing                                                    | 76 |

| 80 MHz Timebase                                                  | 76 |

| 20 MHz Timebase                                                  | 76 |

| 100 kHz Timebase                                                 | 76 |

| Specifications                                                   | 77 |

| Analog Input                                                     | 77 |

| Analog Output                                                    | 77 |

| Digital Waveform Characteristics (Slots 1 through 4 Only)        | 78 |

| PFI Characteristics (Slots 5 and 6 Only)                         | 78 |

| General-Purpose Counter/Timers (Slots 5 and 6 Only)              | 79 |

| Frequency Generator (Slots 5 and 6 Only)                         | 80 |

| External Digital Triggers (Slots 5 and 6 or with Some            |    |

| AI Modules)                                                      | 80 |

| Module I/O States                                                | 80 |

| Power Requirements                                               | 80 |

| Bus Interface                                                    | 81 |

| Physical Characteristics                                         |    |

| Safety                                                           |    |

| Environmental                                                    | 82 |

| Shock and Vibration                                              | 82 |

| Electromagnetic Compatibility                                    |    |

| CE Compliance                                                    |    |

| Environmental Management                                         |    |

| Where to Go for Support                                          |    |

# Introduction

This user guide describes how to use the National Instruments cDAQ-9172 chassis and lists specifications. For an interactive demonstration of how to install the NI cDAQ-9172, go to ni.com/info and enter daqinstall.

The NI cDAQ-9172 is an eight-slot USB chassis designed for use with C Series I/O modules. The NI cDAQ-9172 chassis is capable of measuring a broad range of analog and digital I/O signals and sensors using a Hi-Speed USB 2.0 interface. For module specifications, refer to the documentation included with your C Series I/O module(s) or go to ni.com/manuals.

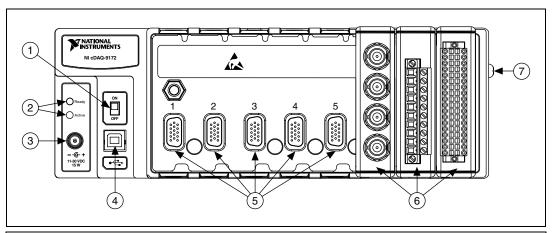

- 1 Power Switch

- 2 Ready/Active LEDs

- 3 Power Connector

- 4 USB Connector

- 5 Empty Module Slots

- 6 Installed C Series I/O Modules

- 7 Screw for Ground Connection

Figure 1. NI cDAQ-9172 Chassis

# **Safety Guidelines**

Operate the NI cDAQ-9172 chassis only as described in this user guide.

**Note** Because some C Series I/O modules may have more stringent certification standards than the NI cDAQ-9172 chassis, the combined system may be limited by individual component restrictions. Refer to the *Using the NI cDAQ-9172* section of this document for more details.

**Caution** The NI cDAQ-9172 chassis is *not* certified for use in hazardous locations.

**Hot Surface** This icon denotes that the component may be hot. Touching this component may result in bodily injury.

# Safety Guidelines for Hazardous Voltages

If *hazardous voltages* are connected to the module, take the following precautions. A hazardous voltage is a voltage greater than 42.4  $V_{pk}$  or 60 VDC to earth ground.

**Caution** Ensure that hazardous voltage wiring is performed only by qualified personnel adhering to local electrical standards.

**Caution** Do *not* mix hazardous voltage circuits and human-accessible circuits on the same module.

**Caution** Make sure that chassis and circuits connected to the module are properly insulated from human contact.

**Caution** The NI cDAQ-9172 chassis provides no isolation, but some modules offer isolation. Follow the safety guidelines for each module when using hazardous voltage.

# **Related Documentation**

Each application software package and driver includes information about writing applications for taking measurements and controlling measurement devices. Check ni.com/manuals for the most recent hardware documentation, and refer to Table 1 for a list of locations for driver and application software documentation. The following document location references assume you have NI-DAQmx 8.8 or later, and where applicable, version 7.1 or later of the NI application software.

**Table 1.** NI Driver and Application Software Documentation

| Software             | Document/Description                                                                                                                                                                                                                                                | Location/Topic                                                         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

| NI-DAQmx for Windows | DAQ Getting Started Guide—describes how to install and use the NI-DAQmx driver software for Windows and your data acquisition (DAQ) device, how to confirm the device is operating properly, and how to take an NI-DAQmx measurement.                               | Start»Programs» National Instruments» NI-DAQ»DAQ Getting Started Guide |

|                      | NI-DAQ Readme—includes information about NI-DAQmx and Traditional NI-DAQ (Legacy). Describes how to choose the API to use, new features, and a list of known issues, supported devices, and devices not supported. Also provides details about system requirements. | Start»Programs» National Instruments» NI-DAQ»NI-DAQ Readme             |

|                      | NI-DAQmx Help—explains how to get started in your OS and ADE; provides an NI-DAQmx overview; includes information about programming the most common measurement tasks with references to examples in CVI/C, C++, .NET.                                              | Start»Programs» National Instruments» NI-DAQ»NI-DAQmx Help             |

Table 1.

NI Driver and Application Software Documentation (Continued)

| Software | Document/Description Location/Topic                                                                                                                                                                                    |                                                                                                                                                   |  |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|--|

| LabVIEW  | Getting Started with LabVIEW—describes the LabVIEW graphical programming environment and the basic LabVIEW features you use to build data acquisition and instrument control application.                              | Start»All Programs» National Instruments» LabVIEW»LabVIEW Manuals or navigate to the labview\manuals directory and opening LV_Getting_Started.pdf |  |

|          | LabVIEW Help—provides information about LabVIEW programming concepts, step-by-step instructions for using LabVIEW, and reference information about LabVIEW VIs, functions, palettes, menus, and tools.                 | Help»Search the LabVIEW Help                                                                                                                      |  |

|          | LabVIEW Help Topics Specific to NI-DAQmx                                                                                                                                                                               |                                                                                                                                                   |  |

|          | Includes overview information and a tutorial to learn how to take an NI-DAQmx measurement in LabVIEW using the DAQ Assistant.                                                                                          | From the Contents tab, Getting Started»Getting Started with DAQ                                                                                   |  |

|          | Describes the LabVIEW NI-DAQmx VIs and properties.                                                                                                                                                                     | From the Contents tab, VI and Function Reference» Measurement I/O VIs and Functions                                                               |  |

|          | Contains the conceptual and how-to information you need to acquire and analyze measurement data in LabVIEW, including common measurements, measurement fundamentals, NI-DAQmx key concepts, and device considerations. | From the Contents tab, Taking Measurements                                                                                                        |  |

Table 1.

NI Driver and Application Software Documentation (Continued)

| Software                                              | Document/Description                                                                                                                                                      | Location/Topic                                                                                                             |

|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| LabWindows™/CVI™                                      | LabWindows/CVI Help Data Acquisition book—contains NI-DAQmx measurement concepts and step-by-step instructions about creating a measurement task using the DAQ Assistant. | Help»Contents, then select Using LabWindows/CVI» Data Acquisition»Taking an NI-DAQmx Measurement in LabWindows/CVI         |

|                                                       | LabWindows/CVI Help NI-DAQmx Library book—contains NI-DAQmx API overviews and function reference.                                                                         | LibraryReference»<br>NI-DAQmx Library                                                                                      |

| Measurement<br>Studio/Microsoft Visual<br>Studio .NET | Microsoft Visual Studio .NET Help/NI Measurement Studio Help—contains NI-DAQmx methods and properties.                                                                    | Measurement Studio» NI Measurement Studio Help and select NI-DAQmx .NET Class Library or NI-DAQmx Visual C++ Class Library |

| ANSI C without<br>NI Application Software             | NI-DAQmx Help                                                                                                                                                             | Start»All Programs» National Instruments» NI-DAQ»NI-DAQmx Help                                                             |

|                                                       | NI-DAQmx C Reference<br>Help—describes the<br>NI-DAQmx Library<br>functions.                                                                                              | Start»All Programs» National Instruments» NI-DAQ»NI-DAQmx C Reference Help                                                 |

Table 1. NI Driver and Application Software Documentation (Continued)

| Software                                           | Document/Description                                                                                        | Location/Topic                                                                                                                                |  |

|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|

| .NET Languages without<br>NI Application Software* | NI-DAQmx .NET Help—contains conceptual topics for using NI-DAQmx with Visual C# and Visual Basic .NET.      | -contains conceptual for using NI-DAQmx //isual C# and Visual National Instruments» NI-DAQ»NI-DAQmx .NET Reference Help. Expand               |  |

|                                                    | Visual Studio .NET Help—contains conceptual topics for using NI-DAQmx with Visual C# and Visual Basic .NET. | Help»Contents. Select Measurement Studio from the Filtered By drop-down list and follow the location instructions for the NI-DAQmx .NET Help. |  |

<sup>\*</sup> With the Microsoft .NET Framework version 1.1 or later, you can use NI-DAQmx to create applications using Visual C# and Visual Basic .NET without Measurement Studio. You need Microsoft Visual Studio .NET 2003 or Microsoft Visual Studio 2005 for the API documentation to be installed.

# **Device Documentation and Specifications**

Check ni.com/manuals for the most recent device and software documentation. If you do not have Web access, NI-DAQmx includes a Documentation CD that includes documentation available when NI-DAQmx released.

# **Training Courses**

If you need more help getting started developing an application with NI products, NI offers training courses. To enroll in a course or obtain a detailed course outline, refer to ni.com/training.

## **Technical Support on the Web**

For additional support, refer to ni.com/support or zone.ni.com.

# **Installing the Software**

# **Installing NI-DAQmx**

The DAQ Getting Started Guide, which you can download at ni.com/manuals, offers NI-DAQmx users step-by-step instructions for installing software and hardware, configuring channels and tasks, and getting started developing an application.

# **Installing Other Software**

If you are using other software, refer to the installation instructions that accompany your software.

# Installing the NI cDAQ-9172

19.0 mm 165.1 mm (6.50 in.) (0.75 in.) NATIONAL INSTRUMENTS 36.4 mm (1.43 in.) 88.1 mm (3.50 in.) @Activ 59.6 mm 51.7 mm (2.35 in.) **@** (2.04 in.) 4.10 mm 254.0 mm (0.16 in.) (10.00 in.) 23.7 mm (0.94 in.) 44.1 mm (1.74 in.) 20.3 mm (0.80 in.) 25.0 mm (0.98 in.) 53.8 mm 44.1 mm (2.12 in.) (1.74 in.) 63.1 mm 46.0 mm (2.49 in.) (1.81 in.) 24.8 mm (0.98 in.) 58.9 mm (2.32 in.) 31.7 mm (1.25 in.) 19.1 mm (0.75 in.) 23.2 mm (0.91 in.)

Figure 2 shows the dimensions of the NI cDAQ-9172 chassis.

Figure 2. NI cDAQ-9172 with Dimensions in Millimeters (Inches)

# Mounting the NI cDAQ-9172

You can mount the NI cDAQ-9172 chassis using a desktop, a 35 mm DIN-Rail, or a panel mount accessory kit. For accessory ordering information, refer to ni. com.

**Caution** Your installation must meet the following requirements:

- Allows 25.4 mm (1 in.) of clearance above and below the NI cDAQ-9172 chassis for air circulation.

- Allows at least 50.8 mm (2 in.) of clearance in front of the modules for common connector cabling such as the 10-terminal detachable screw terminal connector and, as needed, up to 88.9 mm (3.5 in.) of clearance in front of the modules for other types of cabling. For more information about mechanical dimensions, refer to ni.com/info and enter the info code cDAQMechanical. For more information about cable dimensions, refer to ni.com/info and enter the info code cDAQCable.

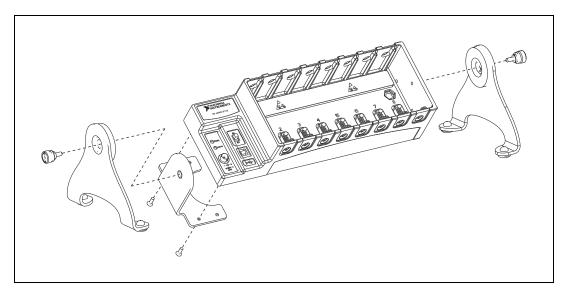

## NI 9901 Desktop Mounting Kit

The NI 9901 Desktop Mounting Kit includes two metal feet you can install on the sides of the NI cDAQ-9172 chassis for desktop use. With this kit, you can tilt the NI cDAQ-9172 chassis for convenient access to the I/O module connectors. When you install the two metal feet, the two existing screws on the power switch side of the chassis must be removed. After removing the screws, replace them with the two longer screws included in the NI 9901 Desktop Mounting Kit.

Figure 3. NI 9901 Desktop Mounting Kit

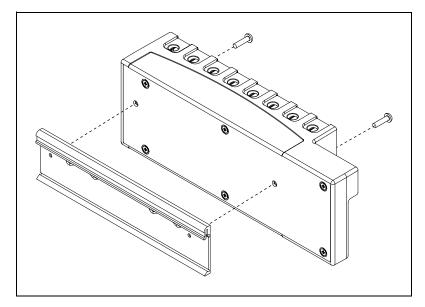

#### NI 9910 DIN-Rail Kit

The NI 9910 DIN-Rail Kit contains one clip for mounting the chassis on a standard 35 mm DIN-Rail. To mount the chassis on a DIN-Rail, fasten the DIN-Rail clip to the chassis using a number 2 Phillips screwdriver and two M4  $\times$  17 screws. The screws are included in the DIN-Rail kit. Make sure the DIN-Rail kit is installed as illustrated in Figure 4, with the larger lip of the DIN-RAIL positioned up. When the DIN-Rail kit is properly installed, the NI cDAQ-9172 chassis is centered on the DIN-Rail.

**Caution** Remove the I/O modules before removing the chassis from the DIN-Rail.

Figure 4. DIN-Rail Installation on the NI cDAQ-9172

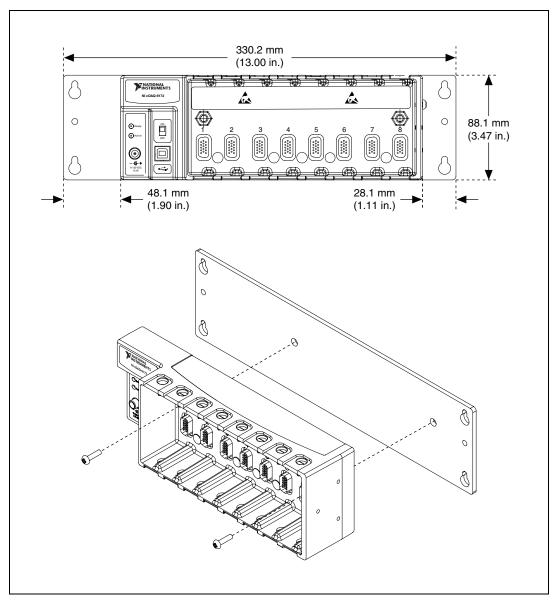

#### NI 9905 Panel Mount Kit

To mount the chassis on a panel, align the chassis on the panel mount accessory. Attach the chassis to the panel mount kit using two M4  $\times$  17 screws (as shown in Figure 5). National Instruments provides these screws with the panel mount kit. You *must* use these screws because they are the correct depth and thread for the panel. These slots in the panel mount kit

can be used with M4, M5, No. 8, or No.10 panhead screws. Figure 5 illustrates the panel dimensions and installation on the NI cDAQ-9172 chassis. Refer to the documentation included with the NI 9905 Panel Mount Kit for more detailed dimensions.

**Figure 5.** Panel Mount Dimensions and Installation on the NI cDAQ-9172

# Setting Up the NI cDAQ-9172

Complete the following steps to prepare the NI cDAQ-9172 chassis for use:

1. Before connecting the hardware, install the NI-DAQmx software. Refer to the *DAQ Getting Started Guide* for more information about software installation.

**Note** The NI-DAQmx software is included on the CD shipped with your kit and is available for download at ni.com/support. The *DAQ Getting Started Guide* is available after installation from **Start»All Programs»National Instruments»NI-DAQ»DAQ Getting Started Guide**. Other NI documentation is available from ni.com/manuals.

- 2. If you are not using any mounting accessories, attach the provided rubber standoffs to the back of the NI cDAQ-9172 chassis.

- 3. Make sure the NI cDAQ-9172 chassis power switch is turned off.

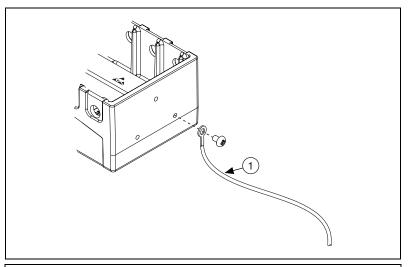

- 4. Attach a ring lug to a 14 AWG (1.6 mm) wire. Connect the ring lug to the ground terminal on the side of the chassis using the ground screw. Attach the other end of the wire to the system safety ground.

1 Attached to System Ground

**Figure 6.** Ring Lug Attached to Ground Terminal

**Note** Additionally, attach a wire with a ring lug to all other C Series I/O module cable shields. You *must* connect this wire to the ground terminal of the chassis using the ground screw.

5. Remove the plastic cover from the connector in any empty module slot.

- 6. Squeeze both C Series I/O module latches, insert the I/O module into the module slot, and press until both latches lock the module in place.

- 7. Connect the NI cDAQ-9172 chassis with the supplied USB cable to any available USB port on your computer.

- 8. Connect the power source to the NI cDAQ-9172 chassis. The NI cDAQ-9172 chassis requires an external power supply that meets the specifications in the *Power Requirements* section.

**Note** The NI cDAQ-9172 chassis uses a DC input jack with a locking ring. Use only this connector with the NI cDAQ-9172 chassis. Refer to the *Specifications* section for more information about the connector.

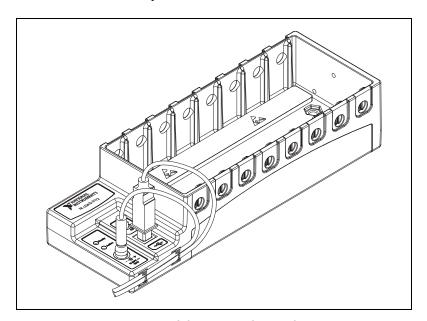

9. Secure the power supply and USB cables, as depicted in Figure 7, using the two tie wraps and adhesive tie wrap mounts included in the shipping kit. The tie wraps and adhesive mounts help secure the non-latching USB connection. They can also be used to route the cables to a desirable position.

Figure 7. cDAQ Chassis With Secured Cables

- 11. Double-click the **Measurement & Automation** icon, shown at left, on the desktop to open MAX.

- 12. Expand **Devices and Interfaces**, and then expand **NI-DAQmx Devices**.

- 13. Check that your device appears under **Devices and Interfaces**. If your device does not appear, press <F5> to refresh the view in MAX. If your device is still not recognized, refer to ni.com/support/install for troubleshooting information.

- 14. Right-click your device and select **Self-Test**.

If you need help during the self-test, select **Help»Help Topics» NI-DAQmx** and click **MAX Help for NI-DAQmx**.

When the self-test finishes, a message indicates successful verification or an error. If an error occurs, refer to ni.com/support/install for troubleshooting information.

**Note** When in use, the NI cDAQ-9172 chassis may become warm to the touch. This is normal.

# **Understanding LED Indications**

#### **Active LED**

The Active LED indicates whether the NI cDAQ-9172 chassis is communicating over the USB bus.

Table 2. Active LED

| LED   | Definition                                              |

|-------|---------------------------------------------------------|

| Amber | Power is applied, but USB connection is not established |

| Green | USB traffic present                                     |

| Off   | No USB traffic present                                  |

# **Ready LED**

The Ready LED is lit when the NI cDAQ-9172 chassis is ready for use. The color indicates whether the USB connection is Full-Speed or Hi-Speed.

**Table 3.** Ready LED

| LED   | Definition                        |  |

|-------|-----------------------------------|--|

| Amber | Hi-Speed (480 Mbit/sec)           |  |

| Green | Full-Speed (12 Mbit/sec)          |  |

| Off   | USB connection is not established |  |

# Using the NI cDAQ-9172

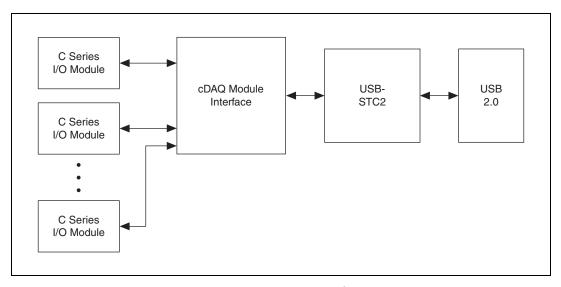

The cDAQ system consists of three parts: C Series I/O modules, the cDAQ module interface, and the USB-STC2. These components digitize signals, perform D/A conversions to generate analog output signals, measure and control digital I/O signals, and provide signal conditioning.

Figure 8. NI cDAQ-9172 Block Diagram

#### C Series I/O Modules

National Instruments C Series I/O modules provide built-in signal conditioning and screw terminal, spring terminal, BNC, D-SUB, or RJ-50 connectors. A wide variety of I/O types are available, allowing you to customize the cDAQ system to meet your application needs.

C Series I/O modules are hot-swappable and automatically detected by the NI cDAQ-9172 chassis. I/O channels are accessible using the NI-DAQmx driver software.

Because the modules contain built-in signal conditioning for extended voltage ranges or industrial signal types, you can usually make your wiring connections directly from the C Series I/O modules to your sensors/actuators. In most cases, the C Series I/O modules provide isolation from channel-to-earth ground.

For more information about which C Series I/O modules are compatible with the NI cDAQ-9172 chassis, refer to the KnowledgeBase document, C Series Modules Supported in the NI cDAQ-9172 CompactDAQ.

To access this KnowledgeBase, go to ni.com/info and enter the info code rdcdag.

#### Correlated vs. Static DIO Modules

Digital I/O module capabilities are determined by the type of digital signals that the module is capable of measuring or generating. Static digital I/O modules are designed for signals that change slowly and are accessed by software-timed reads and writes. Correlated digital I/O modules are for signals that change rapidly and are updated by either software-timed or hardware-timed reads and writes. For more information about Digital I/O modules, refer to the *Digital I/O* section.

#### cDAQ Module Interface

The cDAQ Module Interface manages data transfers between the USB-STC2 and the C Series I/O modules. The interface also handles autodetection, signal routing, and synchronization.

#### **USB-STC2**

The USB-STC2 features independent high-speed data streams; flexible AI and AO sample timing; triggering; PFI signals for multi-device synchronization; flexible counter/timers with hardware gating; digital waveform acquisition and generation; and static DIO.

# Al and AO Sample Timing

The USB-STC2 contains advanced analog input and analog output timing engines. A wide range of timing and synchronization signals are available through the PFI lines. Refer to the *Analog Input Timing Signals* and *Analog Output Timing Signals* sections for more information about the configuration of these signals.

# **Triggering Modes**

The NI cDAQ-9172 supports different trigger modes, such as start trigger, reference trigger, and pause trigger with analog, digital, or software sources. Refer to the *Analog Input Triggering* and *Analog Output Triggering* sections for more information.

# **Independent Data Streams**

The NI cDAQ-9172 supports four independent high-speed data streams; allowing for up to four simultaneous hardware timed tasks, such as analog input, analog output, buffered counter/timers, and correlated digital input/output.

# **PFI Signals**

The PFI signals, available through correlated digital input and output modules installed in slots 5 and/or 6, provide access to advanced features such as triggering, synchronization, and counter/timers. Refer to the *PFI* section for more information.

The PFI pins have a digital filter circuit at the inputs that is configurable on a per-line basis. The filters allow the rejection of noise caused by noisy environments, bounces on switches, and so on.

## Flexible Counter/Timers

The NI cDAQ-9172 includes two general-purpose 32-bit counter/timers that can be used to count edges, measure pulse-widths, measure periods and frequencies, and perform position measurements (encoding). In addition, the counter/timers can generate pulses, pulse trains, and square waves with adjustable frequencies. You can access the counter inputs and outputs using correlated digital I/O modules in slots 5 and/or 6. Refer to the *Counters* section for more information.

# **Analog Input**

To perform analog input measurements, insert a supported analog input C Series I/O module into any slot on the cDAQ chassis. The measurement specifications, such as number of channels, channel configuration, sample rate, and gain, are determined by the type of C Series I/O module used. For more information and wiring diagrams, refer to the documentation included with your C Series I/O modules.

The NI cDAQ-9172 has one AI timing engine, which means that only one analog input task can be running at a time on a chassis. However, the analog input task can include channels from multiple analog input modules.

# **Analog Input Triggering**

A trigger is a signal that causes an action, such as starting or stopping the acquisition of data. When you configure a trigger, you must decide how you want to produce the trigger and the action you want the trigger to cause. The NI cDAQ-9172 chassis supports internal software, external digital triggering, and analog triggering.

Three triggers are available: start trigger, reference trigger, and pause trigger. An analog or digital trigger can initiate these three trigger actions. Any C Series correlated digital input module can supply a digital trigger when installed in slots 5 or 6, and some C Series analog modules can supply an analog or digital trigger in any slot. The start, reference, and pause

triggers can come from three separate modules if desired. To find your module triggering options, refer to the documentation included with your C Series I/O modules. For more information about using digital modules for triggering, refer to the *Digital I/O* section.

# **AI Start Trigger Signal**

Use the AI Start Trigger (ai/StartTrigger) signal to begin a measurement acquisition. A measurement acquisition consists of one or more samples. If you do not use triggers, begin a measurement with a software command. Once the acquisition begins, configure the acquisition to stop in one of the following ways:

- When a certain number of points is sampled (in finite mode)

- After a hardware reference trigger (in finite mode)

- With a software command (in continuous mode)

An acquisition that uses a start trigger (but not a reference trigger) is sometimes referred to as a posttriggered acquisition. That is, samples are measured only after the trigger.

When you are using an internal sample clock, you can specify a delay from the start trigger to the first sample.

#### **Using a Digital Source**

To use ai/StartTrigger with a digital source, specify a source and an edge. Use the following signals as the source:

- Any PFI terminal.

- Counter *n* Internal Output

The source also can be one of several other internal signals on your NI cDAQ-9172 chassis. Refer to the *Device Routing in MAX* topic in the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The NI-DAQmx Help is available after installation from Start» All Programs»National Instruments»NI-DAQ»NI-DAQmx Help. To view the LabVIEW Help, in version 8.0 or later, select Help» Search the LabVIEW Help in LabVIEW. Alternately, to download the LabVIEW Help, go to ni.com/manuals.

You also can specify whether the measurement acquisition begins on the rising edge or falling edge of ai/StartTrigger.

#### **Using an Analog Source**

Some C Series I/O modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event. When you use an analog trigger source for ai/StartTrigger, the acquisition begins on the first rising edge of the Analog Comparison Event signal.

#### **Routing AI Start Trigger to an Output Terminal**

You can route ai/StartTrigger to any output PFI terminal. The output is an active high pulse.

# Al Reference Trigger Signal

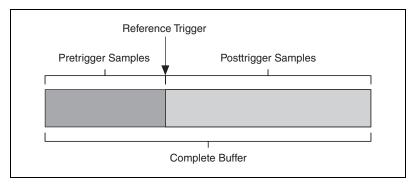

Use a reference trigger (ai/ReferenceTrigger) signal to stop a measurement acquisition. To use a reference trigger, specify a buffer of finite size and a number of pretrigger samples (samples that occur before the reference trigger). The number of posttrigger samples (samples that occur after the reference trigger) desired is the buffer size minus the number of pretrigger samples.

Once the acquisition begins, the NI cDAQ-9172 chassis writes samples to the buffer. After the NI cDAQ-9172 chassis captures the specified number of pretrigger samples, the NI cDAQ-9172 chassis begins to look for the reference trigger condition. If the reference trigger condition occurs before the NI cDAQ-9172 captures the specified number of pretrigger samples, the NI cDAQ-9172 ignores the condition.

If the buffer becomes full, the NI cDAQ-9172 continuously discards the oldest samples in the buffer to make space for the next sample. This data can be accessed (with some limitations) before the NI cDAQ-9172 chassis discards it. Refer to the KnowledgeBase document, *Can a Pretriggered Acquisition be Continuous?*, for more information. To access this KnowledgeBase, go to ni.com/info and enter the info code rdcanq.

When the reference trigger occurs, the NI cDAQ-9172 continues to write samples to the buffer until the buffer contains the number of posttrigger samples desired. Figure 9 shows the final buffer.

**Figure 9.** Reference Trigger Final Buffer

#### **Using a Digital Source**

To use ai/ReferenceTrigger with a digital source, specify a source and an edge. Either PFI or one of several internal signals on the NI cDAQ-9172 chassis can provide the source. Refer to the *Device Routing in MAX* topic in the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The *NI-DAQmx Help* is available after installation from **Start» All Programs»National Instruments»NI-DAQ»NI-DAQmx Help**. To view the *LabVIEW Help*, in version 8.0 or later, select **Help» Search the LabVIEW Help** in LabVIEW. Alternately, to download the *LabVIEW Help*, go to ni.com/manuals.

You also can specify whether the measurement acquisition stops on the rising edge or falling edge of ai/ReferenceTrigger.

#### Using an Analog Source

Some C Series I/O modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event.

When you use an analog trigger source, the acquisition stops on the first rising or falling edge of the Analog Comparison Event signal, depending on the trigger properties.

#### Routing Al Reference Trigger Signal to an Output Terminal

You can route ai/ReferenceTrigger to any output PFI terminal.

# Al Pause Trigger Signal

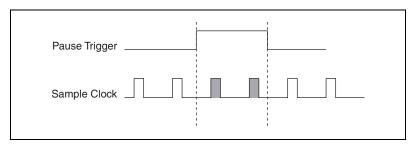

You can use the AI Pause Trigger (ai/PauseTrigger) signal to pause and resume a measurement acquisition. The internal sample clock pauses while the external trigger signal is active and resumes when the signal is inactive. You can program the active level of the pause trigger to be high or low.

#### **Using a Digital Source**

To use ai/PauseTrigger, specify a source and a polarity. The source can be either from PFI or one of several other internal signals on your NI cDAQ-9172 chassis. Refer to the *Device Routing in MAX* topic in the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The NI-DAQmx Help is available after installation from Start» All Programs»National Instruments»NI-DAQ»NI-DAQmx Help. To view the LabVIEW Help, in version 8.0 or later, select Help» Search the LabVIEW Help in LabVIEW. Alternately, to download the LabVIEW Help, go to ni.com/manuals.

#### **Using an Analog Source**

Some C Series I/O modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event.

When you use an analog trigger source, the internal sample clock pauses when the Analog Comparison Event signal is low and resumes when the signal goes high (or vice versa).

**Note** Pause triggers are only sensitive to the level of the source, not the edge.

# **Analog Input Timing Signals**

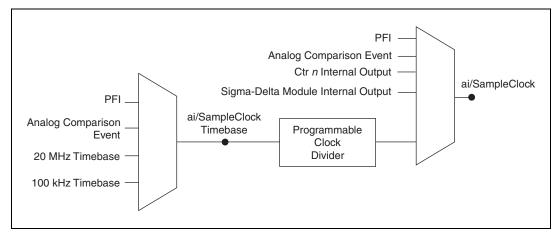

#### Al Sample Clock

A sample consists of one reading from each channel in the AI task. ai/SampleClock signals the start of a sample of all analog input channels in the task. ai/SampleClock can be generated from external or internal sources.

Figure 10. Sample Clock Timing Options

## **Routing AI Sample Clock to an Output Terminal**

You can route ai/SampleClock to any output PFI terminal.

# Al Sample Clock Timebase

The AI Sample Clock Timebase (ai/SampleClockTimebase) signal is divided down to provide a source for ai/SampleClock. ai/SampleClock Timebase can be generated from external or internal sources. ai/SampleClockTimebase is not available as an output from the chassis.

# Convert Behavior For Analog Input Modules Scanned

Scanned C Series analog input modules contain a single A/D converter and a multiplexer to select between multiple input channels. When the cDAQ Module Interface receives a Sample Clock pulse, it begins generating a Convert Clock for each scanned module in the current task. Each Convert Clock signals the acquisition of a single channel from that module. The Convert Clock rate depends on the module being used, the number of channels used on that module, and the system Sample Clock rate.

The driver chooses the fastest conversion rate possible based on the speed of the A/D converter for each module and adds 10 µs of padding between each channel to allow for adequate settling time. This scheme enables the channels to approximate simultaneous sampling. If the AI Sample Clock rate is too fast to allow for 10 µs of padding, NI-DAQmx selects a conversion rate that spaces the AI Convert Clock pulses evenly throughout the sample. NI-DAQmx uses the same amount of padding for all the modules in the task. To explicitly specify the conversion rate, use the

ActiveDevs and AI Convert Clock Rate properties using the DAQmx Timing property node or functions.

#### Simultaneous Sample-and-Hold

Simultaneous sample-and-hold (SSH) C Series analog input modules contain multiple A/D converters or circuitry that allows all the input channels to be sampled at the same time. These modules sample their inputs on every Sample Clock pulse.

#### Sigma-Delta

Sigma-delta C Series analog input modules function much like SSH modules, but use A/D converters that require a high-frequency oversample clock to produce accurate, synchronized data. Sigma-delta modules in the cDAQ chassis automatically share a single oversample clock to synchronize data from all sigma-delta modules.

This clock is used as the AI Sample Clock Timebase. While most modules supply a common oversample clock frequency (12.8 MHz), some modules, such as the NI 9234, supply a different frequency. When sigma-delta modules with different oversample clock frequencies are used in an analog input task, the AI Sample Clock Timebase can use any of the available frequencies; by default, the fastest available is used. The sampling rate of all modules in the system is an integer divisor of the frequency of the AI Sample Clock Timebase.

When one or more sigma-delta modules are in an analog input task, the sigma-delta modules also provide the signal used as the AI Sample Clock. This signal is used to cause A/D conversion for other modules in the system, just as the AI Sample Clock does when a sigma-delta module is not being used.

When sigma-delta modules are in an AI task, the chassis automatically issues a synchronization pulse to each sigma-delta modules that resets their ADCs at the same time. Both the synchronization pulse and the oversample clock can be routed from or to any PFI line to allow synchronization between multiple chassis. Because of the filtering used in sigma-delta A/D converters, these modules usually exhibit a fixed input delay relative to non-sigma-delta modules in the system. This input delay is specified in the C Series I/O module documentation.

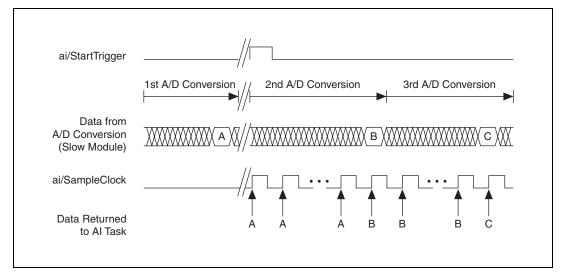

#### **Slow Sample Rate Modules**

Some C Series analog input modules are specifically designed for measuring signals that vary slowly, such as temperature. Because of their slow rate, it is not appropriate for these modules to constrain the AI Sample Clock to operate at or slower than their maximum rate. When using such a module in the cDAQ chassis, the maximum Sample Clock rate can run faster than the maximum rate for the module. When operating at a rate faster than these slow rate modules can support, the slow rate module returns the same point repeatedly, until a new conversion completes. The first point is acquired when the task is committed. The second point is acquired after the start trigger.

Figure 11. Sample Clock Timing Example

For example, if running an AI task at 1 kHz using a module with a maximum rate of 10 Hz, the slow module returns 100 samples of the first point, followed by 100 samples of the second point, etc. Other modules in the task will return 1,000 new data points per second, which is normal. When performing a single-point acquisition, no points are repeated.

Refer to the KnowledgeBase document, *C Series Modules Supported in the NI cDAQ-9172 CompactDAQ*, for more information. To access this KnowledgeBase, go to ni.com/info and enter the info code rdcdaq.

## **Getting Started with AI Applications in Software**

You can use the NI cDAQ-9172 chassis in the following analog input applications:

- Single-Point

- Finite

- Continuous

For more information about programming analog input applications and triggers in software, Refer to the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The NI-DAQmx Help is available after installation from Start» All Programs»National Instruments»NI-DAQ»NI-DAQmx Help. To view the LabVIEW Help, in version 8.0 or later, select Help» Search the LabVIEW Help in LabVIEW. Alternately, to download the LabVIEW Help, go to ni.com/manuals.

# **Analog Output**

To generate analog output, insert an analog output C Series I/O module in any slot on the NI cDAQ-9172 chassis. The generation specifications, such as the number of channels, channel configuration, update rate, and output range, are determined by the type of C Series I/O module used. For more information, refer to the documentation included with your C Series I/O modules.

You can run one hardware-timed (waveform) analog output task at a time on the NI cDAQ-9172 chassis, with up to 16 waveform channels. At the same time, you can also run one or more software-timed (single-point or immediate) tasks.

For each analog output module, you can either:

- Assign all of the channels on the module to the hardware-timed task.

- Assign all of the channels on the module to one or more software-timed tasks.

On a single AO module, you cannot assign some channels to a hardware-timed task and other channels (on the same module) to a software-timed task.

# **Analog Output Data Generation Methods**

When performing an analog output operation, you either can perform software-timed or hardware-timed generations. Hardware-timed generations must be buffered.

#### Software-Timed Generations

With a software-timed generation, software controls the rate at which data is generated. Software sends a separate command to the hardware to initiate each DAC conversion. In NI-DAQmx, software-timed generations are referred to as on-demand timing. Software-timed generations are also referred to as immediate or static operations. They are typically used for writing out a single value, such as a constant DC voltage.

The following considerations apply to software-timed generations:

- If any AO channel on a module is used in a hardware-timed (waveform) task, no channels on that module can be used in a software-timed task.

- You can configure software-timed generation to simultaneously update.

- Only one simultaneous update task can run at a time.

- Simultaneous update is not restricted to 16 channels.

- A hardware-timed AO task and a simultaneous update AO task cannot run at the same time.

#### **Hardware-Timed Generations**

With a hardware-timed generation, a digital hardware signal controls the rate of the generation. This signal can be generated internally on the chassis or provided externally.

Hardware-timed generations have several advantages over software-timed acquisitions:

- The time between samples can be much shorter.

- The timing between samples is deterministic.

- Hardware-timed acquisitions can use hardware triggering.

Hardware-timed AO operations on the NI cDAQ-9172 chassis must be buffered.

#### **Buffered Analog Output**

A buffer is a temporary storage in computer memory for generated samples. In a buffered generation, data is moved from a host buffer to the NI cDAQ-9172 onboard FIFO before it is written to the C Series I/O modules.

One property of buffered I/O operations is sample mode. The sample mode can be either finite or continuous:

- Finite—Finite sample mode generation refers to the generation of a specific, predetermined number of data samples. After the specified number of samples is written out, the generation stops.

- Continuous—Continuous generation refers to the generation of an

unspecified number of samples. Instead of generating a set number of

data samples and stopping, a continuous generation continues until

you stop the operation. There are three different continuous generation

modes that control how the data is written. These modes are

regeneration, onboard regeneration, and non-regeneration:

- In regeneration mode, you define a buffer in host memory. The

data from the buffer is continually downloaded to the FIFO to be

written out. New data can be written to the host buffer at any time

without disrupting the output.

- With onboard regeneration, the entire buffer is downloaded to the FIFO and regenerated from there. After the data is downloaded, new data cannot be written to the FIFO. To use onboard regeneration, the entire buffer must fit within the FIFO size. The advantage of using onboard regeneration is that it does not require communication with the main host memory once the operation is started, which prevents problems that may occur due to excessive bus traffic or operating system latency.

- With non-regeneration, old data is not repeated. New data must continually be written to the buffer. If the program does not write new data to the buffer at a fast enough rate to keep up with the generation, the buffer underflows and causes an error.

# **Analog Output Triggering**

Analog output supports two different triggering actions:

- Start trigger

- Pause trigger

An analog or digital trigger can initiate these actions. Any C Series correlated digital module in slots 5 and/or 6 can supply a digital trigger, and some C Series analog modules can supply an analog trigger. For more information refer to the *AO Start Trigger Signal* section of this document or to the documentation included with your C Series I/O module(s).

# **Analog Output Timing Signals**

The NI cDAQ-9172 chassis features the following AO (waveform generation) timing signals:

- AO Sample Clock

- AO Start Trigger

- AO Pause Trigger

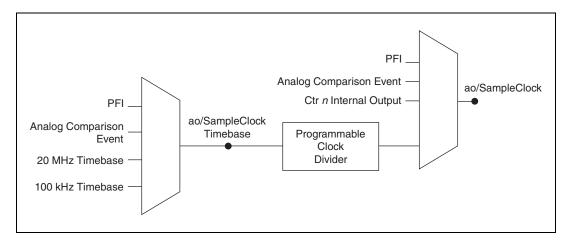

# **AO Sample Clock**

The AO sample clock (ao/SampleClock) signals when all the analog output channels in the task update. ao/SampleClock can be generated from external or internal sources.

Figure 12. Analog Output Timing Options

#### **Routing AO Sample Clock to an Output Terminal**

You can route ao/SampleClock to any output PFI terminal.

#### **AO Sample Clock Timebase Signal**

The AO Sample Clock Timebase (ao/SampleClockTimebase) signal is divided down to provide a source for ao/SampleClock. ao/SampleClockTimebase can be generated from external or internal sources, and is not available as an output from the chassis.

# **AO Start Trigger Signal**

Use the AO Start Trigger (ao/StartTrigger) signal to initiate a waveform generation. If you do not use triggers, you can begin a generation with a software command. If you are using an internal sample clock, you can specify a delay from the start trigger to the first sample. For

more information, refer to the *NI-DAQmx Help*. The *NI-DAQmx Help* is available after installation from **Start»All Programs»National Instruments»NI-DAQ»NI-DAQmx Help**.

#### **Using a Digital Source**

To use ao/StartTrigger, specify a source and a rising or falling edge. The source can be one of the following signals:

- A pulse initiated by host software

- Any PFI terminal

- ai/ReferenceTrigger

- ai/StartTrigger

The source also can be one of several internal signals on the NI cDAQ-9172 chassis. Refer to the *Device Routing in MAX* topic in the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The *NI-DAQmx Help* is available after installation from **Start**» **All Programs**»**National Instruments**»**NI-DAQ**»**NI-DAQmx Help**. To view the *LabVIEW Help*, in version 8.0 or later, select **Help**» **Search the LabVIEW Help** in LabVIEW. Alternately, to download the *LabVIEW Help*, go to ni .com/manuals.

You also can specify whether the waveform generation begins on the rising edge or falling edge of ao/StartTrigger.

#### **Using an Analog Source**

Some C Series I/O modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event, depending on the trigger properties.

When you use an analog trigger source, the waveform generation begins on the first rising or falling edge of the Analog Comparison Event signal, depending on the trigger properties. The analog trigger circuit must be configured by a simultaneously running analog input task.

# Routing AO Start Trigger Signal to an Output Terminal

You can route ao/StartTrigger to any output PFI terminal. The output is an active high pulse.

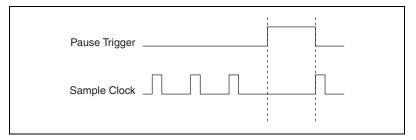

# **AO Pause Trigger Signal**

Use the AO Pause trigger signal (ao/PauseTrigger) to mask off samples in a DAQ sequence. When ao/PauseTrigger is active, no samples occur, but ao/PauseTrigger does not stop a sample that is in progress. The pause does not take effect until the beginning of the next sample.

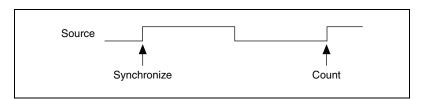

When you generate analog output signals, the generation pauses as soon as the pause trigger is asserted. If the source of the sample clock is the onboard clock, the generation resumes as soon as the pause trigger is deasserted, as shown in Figure 13.

Figure 13. ao/PauseTrigger with the Onboard Clock Source

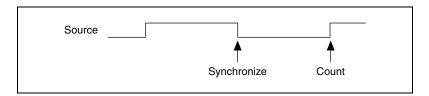

If you are using any signal other than the onboard clock as the source of the sample clock, the generation resumes as soon as the pause trigger is deasserted and another edge of the sample clock is received, as shown in Figure 14.

Figure 14. ao/PauseTrigger with Other Signal Source

#### **Using a Digital Source**

To use ao/PauseTrigger, specify a source and a polarity. The source can be a PFI signal or one of several other internal signals on the NI cDAQ-9172 chassis.

You also can specify whether the samples are paused when ao/PauseTrigger is at a logic high or low level. Refer to the *Device Routing in MAX* topic in the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The *NI-DAQmx Help* is available after installation from **Start**» **All Programs**»**National Instruments**»**NI-DAQ**»**NI-DAQmx Help**. To view the *LabVIEW Help*, in version 8.0 or later, select **Help**»**Search the LabVIEW Help** in LabVIEW. Alternately, to download the *LabVIEW Help*, go to ni.com/manuals.

#### **Using an Analog Source**

Some C Series I/O modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event, depending on the trigger properties.

When you use an analog trigger source, the samples are paused when the Analog Comparison Event signal is at a high or low level, depending on the trigger properties. The analog trigger circuit must be configured by a simultaneously running analog input task.

# Minimizing Glitches on the Output Signal

When you use a DAC to generate a waveform, you may observe glitches on the output signal. These glitches are normal; when a DAC switches from one voltage to another, it produces glitches due to released charges. The largest glitches occur when the most significant bit of the DAC code changes. You can build a lowpass deglitching filter to remove some of these glitches, depending on the frequency and nature of the output signal. Go to ni.com/support for more information about minimizing glitches.

# **Getting Started with AO Applications in Software**

You can use the NI cDAQ-9172 chassis in the following analog output applications:

- Single-Point (On-Demand) Generation

- Finite Generation

- Continuous Generation

- Waveform Generation

For more information about programming analog output applications and triggers in software, refer the *LabVIEW Help*, in version 8.0 or later, or to the *NI-DAQmx Help*.

The NI-DAQmx Help is available after installation from Start» All Programs»National Instruments»NI-DAQ»NI-DAQmx Help. To view the LabVIEW Help, in version 8.0 or later, select Help» Search the LabVIEW Help in LabVIEW. Alternately, to download the LabVIEW Help, go to ni.com/manuals.

# Digital I/O

To use digital I/O, insert a digital I/O C Series module into any slot on the NI cDAQ-9172 chassis. The I/O specifications, such as number of lines, logic levels, update rate, and line direction, are determined by the type of C Series I/O module used. For more information, refer to the documentation included with your C Series I/O modules.

#### Correlated vs. Static DIO Modules

Digital I/O module capabilities are determined by the type of digital signals that the module is capable of measuring or generating. Static digital I/O modules are designed for signals that change slowly and are accessed by software-timed reads and writes. Correlated digital I/O modules are for signals that change rapidly and are updated by either software-timed or hardware-timed reads and writes. Correlated digital I/O modules can perform the following tasks:

- Used in any slot—Software-timed reads and writes

- Used in slots 1 though 4—Digital waveform generation and acquisition (correlated input/output)

- Used in slots 5 and 6—Counter/timer

- Used in slots 5 and 6—Access PFI signals

To determine the capability of digital I/O modules supported by the NI cDAQ-9172 chassis, refer to the KnowledgeBase document, *C Series Modules Supported in the NI cDAQ-9172 CompactDAQ*. To access this KnowledgeBase document, go to ni.com/info and enter the info code rdcdaq.

Available features, such as trigger and counter/timer, are determined by the slot containing the digital I/O C Series module and the capabilities of the module.

| Slots | Static DIO | PFI¹ | Counter/Timer <sup>1</sup> | Digital<br>Waveform/Change<br>Detection <sup>1</sup> |

|-------|------------|------|----------------------------|------------------------------------------------------|

| 1     | Yes        | _    | _                          | Yes                                                  |

| 2     | Yes        | _    | _                          | Yes                                                  |

| 3     | Yes        | _    | _                          | Yes                                                  |

| 4     | Yes        | _    | _                          | Yes                                                  |

**Table 4.** Digital Module Slot Features

**Table 4.** Digital Module Slot Features (Continued)

| Slots | Static DIO | PFI <sup>1</sup> | Counter/Timer <sup>1</sup> | Digital<br>Waveform/Change<br>Detection <sup>1</sup> |

|-------|------------|------------------|----------------------------|------------------------------------------------------|

| 5     | Yes        | Yes              | Yes                        | _                                                    |

| 6     | Yes        | Yes              | Yes                        | _                                                    |

| 7     | Yes        |                  | _                          | _                                                    |

| 8     | Yes        | _                | _                          | _                                                    |

|       | Yes        | _                | _                          | _                                                    |

<sup>&</sup>lt;sup>1</sup> Requires the use of a correlated digital I/O module.

#### Static DIO

Each of the DIO lines can be used as a static DI or DO line. You can use static DIO lines to monitor or control digital signals on some C Series I/O modules. Each DIO line can be individually configured as a digital input (DI) or digital output (DO), depending on the C Series I/O module being used.

All samples of static DI lines and updates of static DO lines are software-timed.

# **Digital Waveform Acquisition (Correlated Input)**

You can acquire digital waveforms using correlated digital modules in slots 1 through 4. The DI waveform acquisition FIFO stores the digital samples. The NI cDAQ-9172 chassis samples the DIO lines on each rising or falling edge of the di/SampleClock signal.

## DI Sample Clock Signal

Use the DI Sample Clock (di/SampleClock) signal to sample digital I/O on slots 1 through 4, using correlated digital modules, and store the result in the DI waveform acquisition FIFO. The NI cDAQ-9172 chassis does not have an independent DI Sample Clock circuit. Therefore, you must route an external signal or one of many internal signals from another subsystem to function as the DI Sample Clock. For example, you can correlate digital and analog samples in time by setting the AI Sample Clock or AO Sample Clock as the source of the DI Sample Clock. To sample a digital signal independent of an AI, AO, or DO operation, you can configure a counter to generate the desired DI Sample Clock or use an external signal as the source of the DI Sample Clock.

If the NI cDAQ-9172 chassis receives a di/SampleClock signal when the FIFO is full, it reports an overflow error to the host software.

#### **Using an Internal Source**

To use di/SampleClock with an internal source, specify the signal source and the polarity of the signal. Use the following signals as the source:

- AI Sample Clock

- AI Convert Clock

- AO Sample Clock

- Counter *n* Internal Output

- Frequency Output

- DI Change Detection Output

Several other internal signals can be routed to di/SampleClock. Refer to the *Device Routing in MAX* topic in the *NI-DAQmx Help* or the *LabVIEW Help* in version 8.0 or later for more information.

The NI-DAQmx Help is available after installation from **Start**» **All Programs**»**National Instruments**»**NI-DAQ**»**NI-DAQmx Help**. To view the *LabVIEW Help*, in version 8.0 or later, select **Help**» **Search the LabVIEW Help** in LabVIEW. Alternately, to download the *LabVIEW Help*, go to ni.com/manuals.

#### **Using an External Source**

You can route the following signals as di/SampleClock:

- Any PFI terminal

- Analog Comparison Event (an analog trigger)

You can sample data on the rising or falling edge of di/SampleClock.

#### **Routing DI Sample Clock to an Output Terminal**

You can route di/SampleClock to any output PFI terminal. The PFI circuitry inverts the polarity of di/SampleClock before driving the PFI terminal.

## **Digital Waveform Generation (Correlated Output)**

With a hardware-timed generation, a digital hardware signal controls the rate of the generation. This signal can be generated internally on the chassis or provided externally.

Hardware-timed generations have several advantages over software-timed acquisitions:

- The time between samples can be much shorter.

- The timing between samples can be deterministic.

Hardware-timed operations must be buffered.

## **Buffered Digital Waveform Generation**

A buffer is a temporary storage in computer memory for generated samples. In a buffered generation, data is moved from a host buffer to the NI cDAQ-9172 onboard FIFO before it is written to the C Series I/O modules. Buffered generations typically allow for much faster transfer rates than nonbuffered generations because data is moved in large blocks, rather than one point at a time. The DO sample clock causes all lines in the task to update at the same time.

One property of buffered I/O operations is the sample mode. The sample mode can be either finite or continuous:

- Finite—Finite sample mode generation refers to the generation of a specific, predetermined number of data samples. After the specified number of samples has been written out, the generation stops.

- Continuous—Continuous generation refers to the generation of an unspecified number of samples. Instead of generating a set number of data samples and stopping, a continuous generation continues until you stop the operation. There are several different methods of continuous generation that control what data is written. These methods are regeneration, onboard regeneration, and non-regeneration modes:

- In regeneration mode, you define a buffer in host memory. The

data from the buffer is continually downloaded to the FIFO to be

written out. New data can be written to the host buffer at any time

without disrupting the output.

- With onboard regeneration, the entire buffer is downloaded to the FIFO and regenerated from there. After the data is downloaded, new data cannot be written to the FIFO. To use onboard regeneration, the entire buffer must fit within the FIFO size. The advantage of using on board regeneration is that it does not require communication with the main host memory once the operation is started, thereby preventing any problems that may occur due to excessive bus traffic or operating system latency.

- With non-regeneration, old data is not repeated. New data must be continually written to the buffer. If the program does not write new data to the buffer at a fast enough rate to keep up with the generation, the buffer underflows and causes an error.

# **Change Detection Event**

The Change Detection Event is the signal generated when a change on the rising or falling edge lines is detected by the change detection task.

# Routing Change Detection Event to an Output Terminal

You can route ChangeDetectionEvent to any output PFI terminal.

## **Change Detection Acquisition**

You can configure lines on correlated digital modules in slots 1 through 4 to detect rising or falling edges. When one or more of these lines sees the edge specified for that line, the NI cDAQ-9172 chassis samples all the lines in the task. The rising and falling edge lines do not necessarily have to be in the task.

Change detection acquisitions can be buffered or nonbuffered:

- Nonbuffered Change Detection Acquisition—In nonbuffered acquisitions, correlated digital input modules in any slot may be in the task, but the rising/falling edge detection lines must be in slots 1 through 4.

- Buffered Change Detection Acquisition—A buffer is a temporary storage in computer memory for acquired samples. In a buffered acquisition, data is stored in the NI cDAQ-9172 onboard FIFO then transferred to a PC buffer. Buffered acquisitions typically allow for much faster transfer rates than nonbuffered acquisitions because data accumulates and is transferred in blocks, rather than one sample at a time. With buffered acquisitions, all modules in the task must be in slots 1 through 4.

## **Digital Input/Output Configuration for NI 9401**

When you change the configuration of lines on a NI 9401 digital I/O module between input and output, NI-DAQmx temporarily reserves all of the lines on the module for communication to send the module a line configuration command. If another task or route is actively using the module, to avoid interfering with the other task, NI-DAQmx generates an error instead of sending the line configuration command. During the line configuration command, the output lines are maintained without glitching.

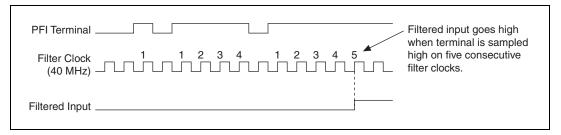

## PFI

You can configure channels of a correlated digital module in slots 5 and 6 as Programmable Function Interface (PFI) terminals.

You can configure each PFI individually as the following:

- Static digital input

- Static digital output

- Timing input signal for AI, AO, DI, DO, or counter/timer functions

- Timing output signal from AI, AO, DI, DO, or counter/timer functions

Each PFI input also has a programmable digital filter circuit that is configurable on a per-line basis. The filters allow the rejection of noise caused by noisy environments, bounces on switches, and so on. Refer to the *NI-DAQmx Help* for more information. The *NI-DAQmx Help* is available after installation from **Start\*All Programs\*National Instruments\* NI-DAQ\*NI-DAQmx Help**.

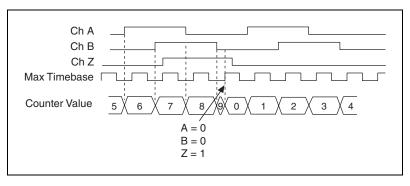

## **Counters**

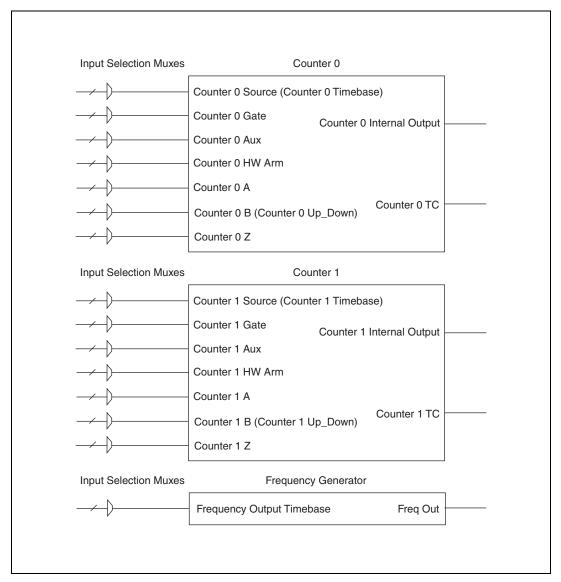

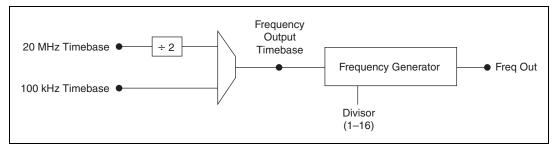

The NI cDAQ-9172 chassis has two general-purpose 32-bit counter/timers and one frequency generator, as shown in Figure 15. The general-purpose counter/timers can be used for many measurement and pulse generation applications.

Some counter/timer signals may be routed to PFI signals. To access PFI signals, you must use a correlated digital I/O C Series module in slot 5 and/or 6.

**Note** For more information about C Series signal connections for counters, refer to the *NI-DAQmx Help*. The *NI-DAQmx Help* is available after installation from **Start**» **All Programs»National Instruments»NI-DAQ»NI-DAQmx Help**.

Figure 15. NI cDAQ-9172 Counters

Counters have seven input signals, although in most applications only a few inputs are used.

For information about connecting the counter signals, refer to the *Default Counter/Timer Routing* section. The following sections describe various counter applications.

# **Counter Input Applications**

# **Counting Edges**

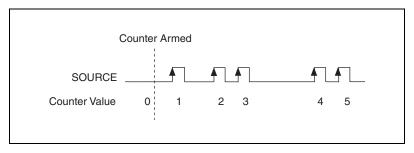

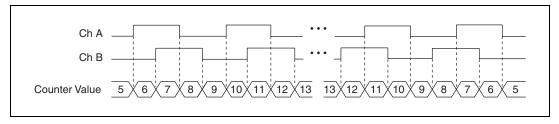

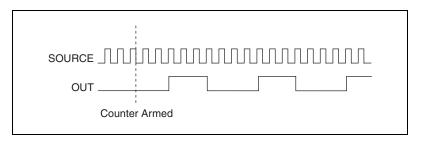

In edge counting applications, the counter counts edges on its Source after the counter is armed. You can configure the counter to count rising or falling edges on its Source input. You also can control the direction of counting (up or down).

The counter values can be read on demand or with a sample clock.

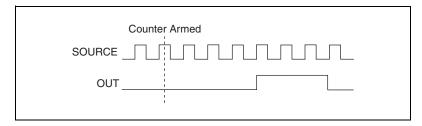

## Single-Point (On-Demand) Edge Counting

With single-point (on-demand) edge counting, the counter counts the number of edges on the Source input after the counter is armed. *On-demand* refers to the fact that software can read the counter contents at any time without disturbing the counting process. Figure 16 shows an example of single-point edge counting.

Figure 16. Single-Point (On-Demand) Edge Counting

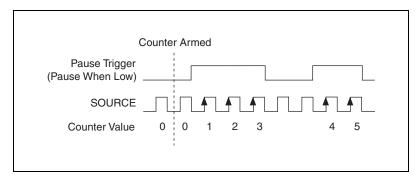

You also can use a pause trigger to pause (or gate) the counter. When the pause trigger is active, the counter ignores edges on its Source input. When the pause trigger is inactive, the counter counts edges normally.

You can route the pause trigger to the Gate input of the counter. You can configure the counter to pause counting when the pause trigger is high or when it is low. Figure 17 shows an example of on-demand edge counting with a pause trigger.

Figure 17. Single-Point (On-Demand) Edge Counting with Pause Trigger

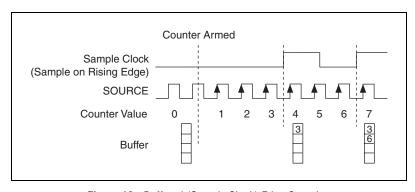

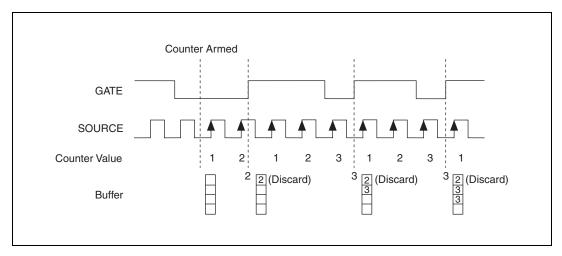

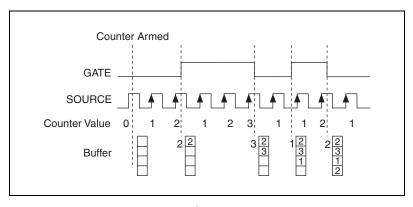

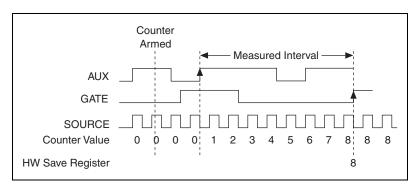

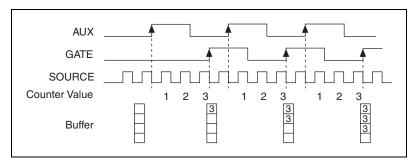

#### **Buffered (Sample Clock) Edge Counting**

With buffered edge counting (edge counting using a sample clock), the counter counts the number of edges on the Source input after the counter is armed. The value of the counter is sampled on each active edge of a sample clock. The NI cDAQ-9172 transfers the sampled values to host memory.

The count values returned are the cumulative counts since the counter armed event. That is, the sample clock does not reset the counter.

You can route the counter sample clock to the Gate input of the counter. You can configure the counter to sample on the rising or falling edge of the sample clock.

Figure 18 shows an example of buffered edge counting. Notice that counting begins when the counter is armed, which occurs before the first active edge on Gate.

Figure 18. Buffered (Sample Clock) Edge Counting

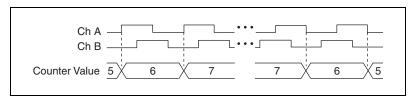

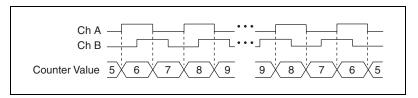

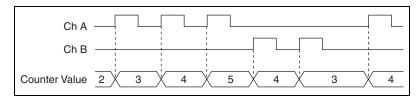

#### **Controlling the Direction of Counting**

In edge counting applications, the counter can count up or down. You can configure the counter to do the following:

- · Always count up

- Always count down

- Count up when the Counter *n* B input is high; count down when it is low

For information on connecting counter signals, refer to the *Default Counter/Timer Routing* section.

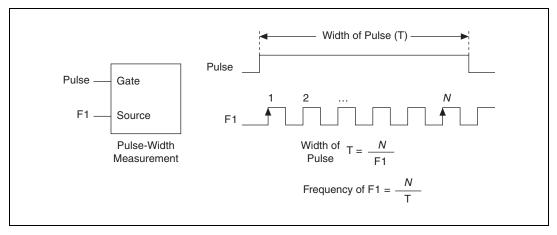

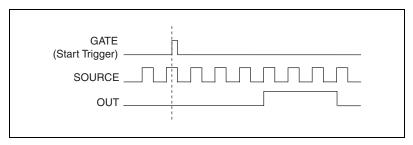

#### **Pulse-Width Measurement**

In pulse-width measurements, the counter measures the width of a pulse on its Gate input signal. You can configure the counter to measure the width of high pulses or low pulses on the Gate signal.

You can route an internal or external periodic clock signal (with a known period) to the Source input of the counter. The counter counts the number of rising (or falling) edges on the Source signal while the pulse on the Gate signal is active.

You can calculate the pulse width by multiplying the period of the Source signal by the number of edges returned by the counter.

A pulse-width measurement is accurate even if the counter is armed while a pulse train is in progress. If a counter is armed while the pulse is in the active state, it waits for the next transition to the active state to begin the measurement.

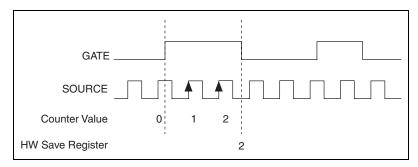

## Single Pulse-Width Measurement

With single pulse-width measurement, the counter counts the number of edges on the Source input while the Gate input remains active. When the Gate input goes inactive, the counter stores the count in a hardware save register and ignores other edges on the Gate and Source inputs. The software then reads the stored count.

Figure 19 shows an example of a single pulse-width measurement.

Figure 19. Single Pulse-Width Measurement

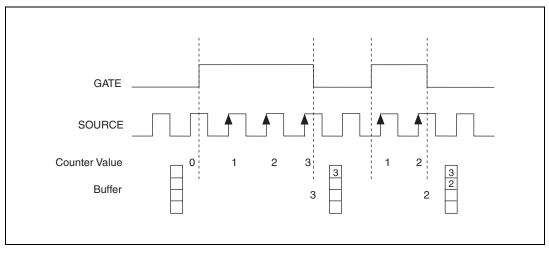

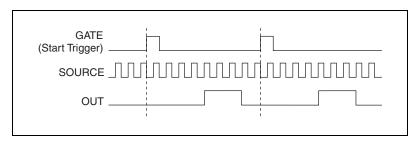

#### **Buffered Pulse-Width Measurement**

Buffered pulse-width measurement is similar to single pulse-width measurement, but buffered pulse-width measurement takes measurements over multiple pulses.

The counter counts the number of edges on the Source input while the Gate input remains active. On each trailing edge of the Gate signal, the counter stores the count in a hardware save register. The NI cDAQ-9172 transfers the stored values to host memory.

Figure 20 shows an example of a buffered pulse-width measurement.

Figure 20. Buffered Pulse-Width Measurement

**Note** If you are using an external signal as the Source, at least one Source pulse should occur between each active edge of the Gate signal. This condition ensures that correct values are returned by the counter. If this condition is not met, consider using duplicate count prevention, described in the *Duplicate Count Prevention* section.

For information on connecting counter signals, refer to the *Default Counter/Timer Routing* section.

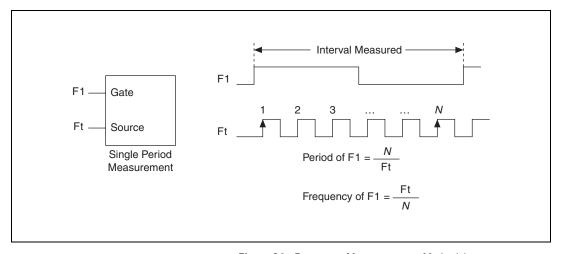

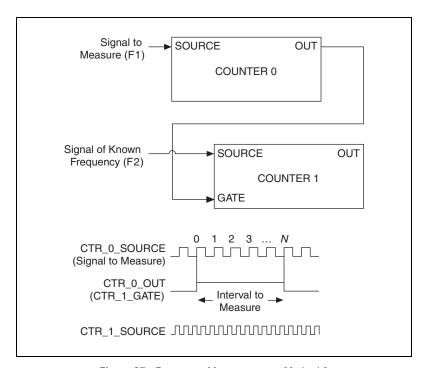

#### Period Measurement

In period measurements, the counter measures a period on its Gate input signal after the counter is armed. You can configure the counter to measure the period between two rising edges or two falling edges of the Gate input signal.

You can route an internal or external periodic clock signal (with a known period) to the Source input of the counter. The counter counts the number of rising (or falling) edges occurring on the Source input between the two active edges of the Gate signal.

You can calculate the period of the Gate input by multiplying the period of the Source signal by the number of edges returned by the counter.

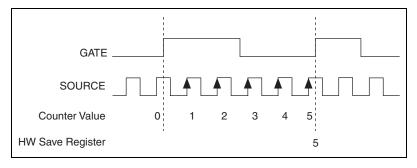

#### **Single Period Measurement**

With single period measurement, the counter counts the number of rising (or falling) edges on the Source input occurring between two active edges of the Gate input. On the second active edge of the Gate input, the counter stores the count in a hardware save register and ignores other edges on the Gate and Source inputs. The software then reads the stored count.

Figure 21 shows an example of a single period measurement.

Figure 21. Single Period Measurement

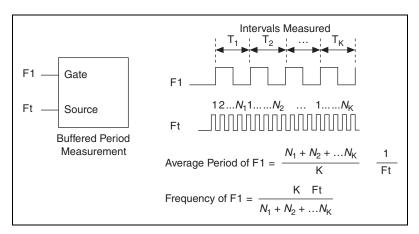

#### **Buffered Period Measurement**

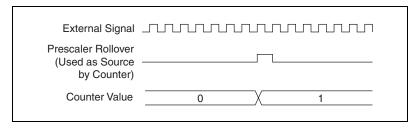

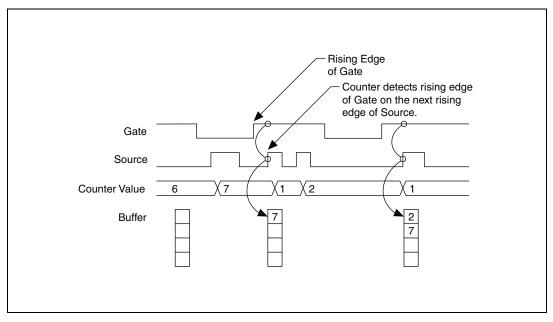

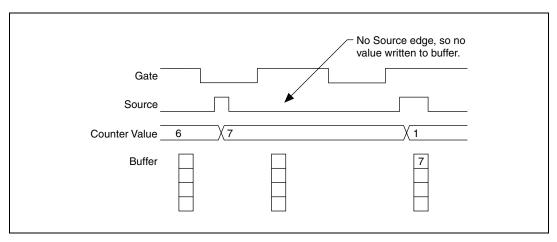

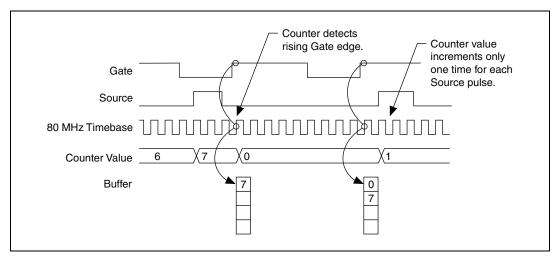

Buffered period measurement is similar to single period measurement, but buffered period measurement measures multiple periods.