### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

### SELL YOUR SURPLUS

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE PXI-4220

# PXI

NI PXI-4204 User Manual

June 2007 373529C-01

#### Worldwide Technical Support and Product Information

ni.com

#### National Instruments Corporate Headquarters

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 1800 300 800, Austria 43 662 457990-0, Belgium 32 (0) 2 757 0020, Brazil 55 11 3262 3599, Canada 800 433 3488, China 86 21 5050 9800, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 385 (0) 9 725 72511, France 01 57 66 24 24, Germany 49 89 7413130, India 91 80 41190000, Israel 972 3 6393737, Italy 39 02 413091, Japan 81 3 5472 2970, Korea 82 02 3451 3400, Lebanon 961 (0) 1 33 28 28, Malaysia 1800 887710, Mexico 01 800 010 0793, Netherlands 31 (0) 348 433 466, New Zealand 0800 553 322, Norway 47 (0) 66 90 76 60, Poland 48 22 3390150, Portugal 351 210 311 210, Russia 7 495 783 6851, Singapore 1800 226 5886, Slovenia 386 3 425 42 00, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 (0) 8 587 895 00, Switzerland 41 56 2005151, Taiwan 886 02 2377 2222, Thailand 662 278 6777, Turkey 90 212 279 3031, United Kingdom 44 (0) 1635 523545

For further support information, refer to the *Technical Support Information* document. To comment on National Instruments documentation, refer to the National Instruments Web site at ni.com/info and enter the info code feedback.

© 2003–2007 National Instruments Corporation. All rights reserved.

#### Warranty

The NI PXI-4204 is warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOPORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### Trademarks

National Instruments, NI, ni.com, and LabVIEW are trademarks of National Instruments Corporation. Refer to the *Terms of Use* section on ni.com/legal for more information about National Instruments trademarks.

Other product and company names mentioned herein are trademarks or trade names of their respective companies.

Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents

For patents covering National Instruments products, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your CD, or ni.com/patents.

### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILY INJURY AND DEATH) SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS, BECAUSE EACH END-USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS' TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

## Conventions

The following conventions are used in this manual: Angle brackets that contain numbers separated by an ellipsis represent <> a range of values associated with a bit or signal name—for example, AO <3..0>. The » symbol leads you through nested menu items and dialog box options » to a final action. The sequence File»Page Setup»Options directs you to pull down the File menu, select the Page Setup item, and select Options from the last dialog box. This icon denotes a note, which alerts you to important information. This icon denotes a caution, which advises you of precautions to take to avoid injury, data loss, or a system crash. When this symbol is marked on a product, refer to the Read Me First: Safety and Radio-Frequency Interference for information about precautions to take. When symbol is marked on a product, it denotes a warning advising you to take precautions to avoid electrical shock. When symbol is marked on a product, it denotes a component that may be hot. Touching this component may result in bodily injury. bold Bold text denotes items that you must select or click in the software, such as menu items and dialog box options. Bold text also denotes parameter names. italic Italic text denotes variables, emphasis, a cross-reference, or an introduction to a key concept. Italic text also denotes text that is a placeholder for a word or value that you must supply. Text in this font denotes text or characters that you should enter from the monospace keyboard, sections of code, programming examples, and syntax examples. This font is also used for the proper names of disk drives, paths, directories, programs, subprograms, subroutines, device names, functions, operations, variables, filenames, and extensions.

### Chapter 1 About the NI PXI-4204

| What You Need to Get Started                                    | 1-2 |

|-----------------------------------------------------------------|-----|

| National Instruments Documentation                              | 1-2 |

| Installing the Application Software, NI-DAQ, and the DAQ Device | 1-3 |

| Installing the NI PXI-4204                                      |     |

| LED Pattern Descriptions                                        |     |

### Chapter 2 Connecting Signals

| Connecting Signals to the NI PXI-4204                    | 2-1  |

|----------------------------------------------------------|------|

| Front Signal Connector                                   | 2-3  |

| Analog Input Connections                                 | 2-5  |

| Floating Signal Source Connection                        | 2-6  |

| Shielded Floating Signal Source Connection (Recommended) | 2-7  |

| Ground-Referenced Signal Connection                      | 2-8  |

| Shielded Ground-Referenced                               |      |

| Signal Connection (Recommended)                          | 2-9  |

| Alternative Shielded Ground-Referenced Connection        | 2-10 |

| High CMV Connection                                      | 2-11 |

| Shielded High CMV Connection                             | 2-12 |

|                                                          |      |

### Chapter 3 Using the NI PXI-4204

| Theory of Operation                     | 3-1  |

|-----------------------------------------|------|

| Signal Conditioning Functional Overview | 3-3  |

| Measurement Considerations              | 3-4  |

| Differential Signals                    | 3-4  |

| Input Impedance                         |      |

| Common-Mode Rejection Ratio             |      |

| Normal-Mode Rejection                   |      |

| Effective CMR                           |      |

| Timing and Control Functional Overview  | 3-7  |

| Programmable Function Inputs            |      |

| Device and PXI Clocks                   |      |

| Developing Your Application             | 3-11 |

| Typical Program Flow Chart              |      |

|                                         |      |

#### Contents

| General Discussion of Typical Flow Chart                | 2 1 2 |

|---------------------------------------------------------|-------|

| General Discussion of Typical Flow Chart                |       |

| Creating a Task Using DAQ Assistant or Programmatically | 3-13  |

| Adjusting Timing and Triggering                         | 3-14  |

| Configuring Channel Properties                          | 3-14  |

| Acquiring, Analyzing, and Presenting                    | 3-15  |

| Completing the Application                              | 3-15  |

| Developing an Application Using LabVIEW                 | 3-16  |

| Using a DAQmx Channel Property Node in LabVIEW          | 3-17  |

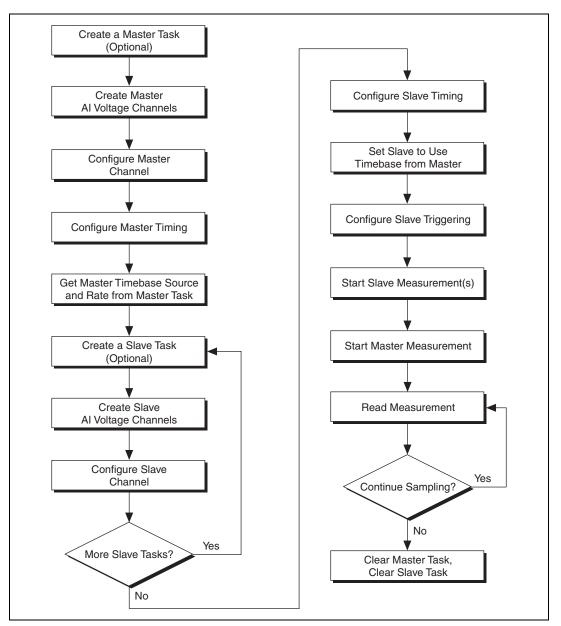

| Synchronization and Triggering                          | 3-19  |

| Synchronizing the NI PXI-4204                           | 3-19  |

| Synchronizing the NI PXI-4204 Using LabVIEW             | 3-21  |

| Other Application Documentation and Material            | 3-22  |

| Calibrating the NI PXI-4204                             | 3-23  |

| Loading Calibration Constants                           |       |

| Self-Calibration                                        |       |

| External Calibration                                    | 3-24  |

|                                                         |       |

### Appendix A Specifications

Appendix B Timing Signal Information

Appendix C Removing the NI PXI-4204

### Appendix D Common Questions

### Glossary

### Index

### Figures

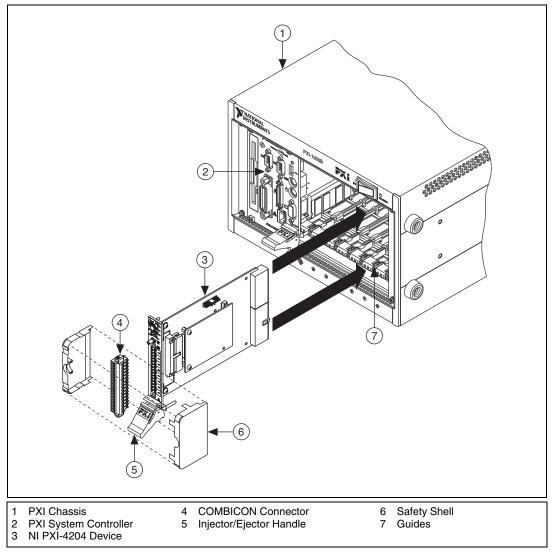

| Figure 2-1. Installing the NI PXI-4204 Device                        | -2 |

|----------------------------------------------------------------------|----|

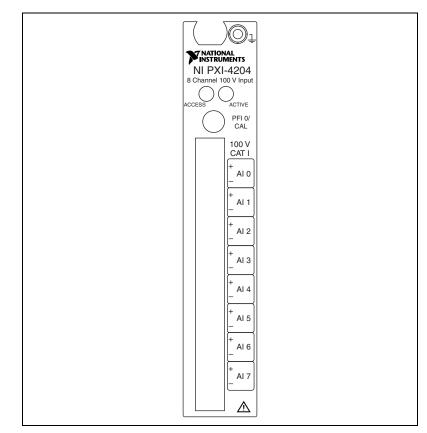

| Figure 2-2. NI PXI-4204 Screw Terminals                              | -4 |

| Figure 2-3. NI PXI-4204 Front Label                                  |    |

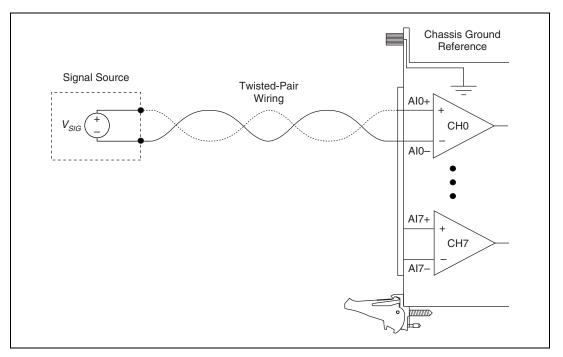

| Figure 2-4. Floating Signal Source Connection                        |    |

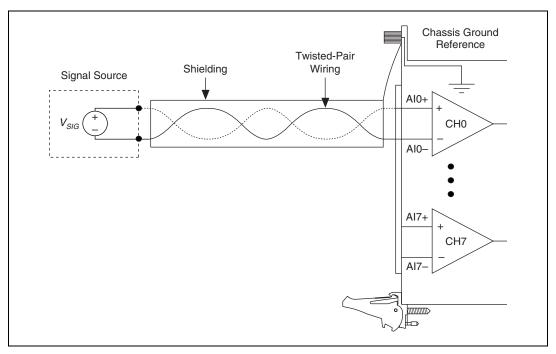

| Figure 2-5. Shielded Floating Signal Source Connection (Recommended) |    |

| Figure 2-6.                                                                                                             | Ground-Referenced Signal Connection                                                                                                                                                                                                                                                                                                    |

|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 2-7.                                                                                                             | Recommended Shielded Ground-Referenced Signal Connection2-10                                                                                                                                                                                                                                                                           |

| Figure 2-8.                                                                                                             | Alternative Shielded Ground Referenced Signal Connection2-11                                                                                                                                                                                                                                                                           |

| Figure 2-9.                                                                                                             | High CMV Connection                                                                                                                                                                                                                                                                                                                    |

| Figure 2-10.                                                                                                            | Shielded High CMV Connection                                                                                                                                                                                                                                                                                                           |

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                        |

| Figure 3-1.                                                                                                             | Block Diagram of NI PXI-4204                                                                                                                                                                                                                                                                                                           |

| Figure 3-2.                                                                                                             | Effect of Input Impedance on Signal Measurements                                                                                                                                                                                                                                                                                       |

| Figure 3-3.                                                                                                             | AI CONV CLK Signal Routing                                                                                                                                                                                                                                                                                                             |

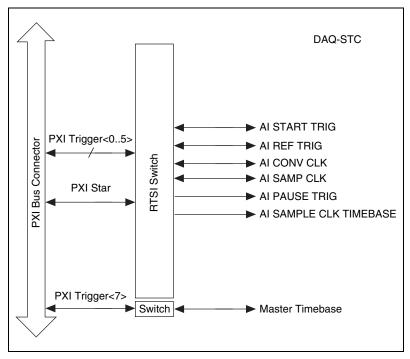

| Figure 3-4.                                                                                                             | NI PXI-4204 PXI Trigger Bus Signal Connection                                                                                                                                                                                                                                                                                          |

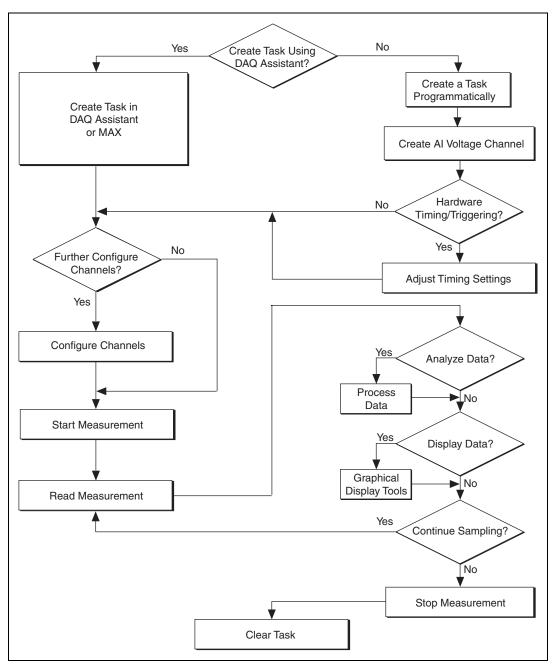

| Figure 3-5.                                                                                                             | Typical Program Flowchart                                                                                                                                                                                                                                                                                                              |

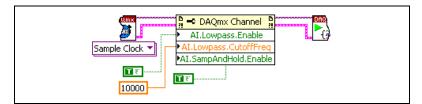

| Figure 3-6.                                                                                                             | LabVIEW Channel Property Node with Filtering Enabled                                                                                                                                                                                                                                                                                   |

|                                                                                                                         | at 10 kHz and SS/H Enabled                                                                                                                                                                                                                                                                                                             |

| Figure 3-7.                                                                                                             | General Synchronizing Flowchart                                                                                                                                                                                                                                                                                                        |

|                                                                                                                         |                                                                                                                                                                                                                                                                                                                                        |

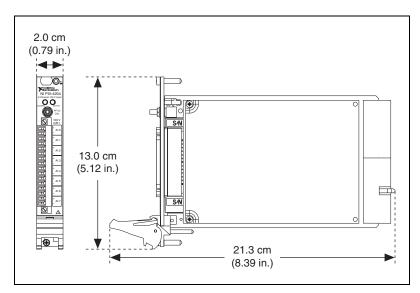

| Figure A-1.                                                                                                             | NI PXI-4204 DimensionsA-6                                                                                                                                                                                                                                                                                                              |

| _                                                                                                                       |                                                                                                                                                                                                                                                                                                                                        |

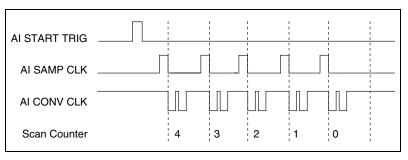

| Figure B-1.                                                                                                             | Typical Posttriggered Sequence                                                                                                                                                                                                                                                                                                         |

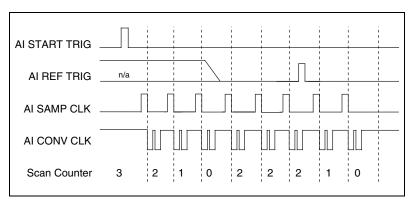

| Figure B-2.                                                                                                             | Typical Pretriggered SequenceB-2                                                                                                                                                                                                                                                                                                       |

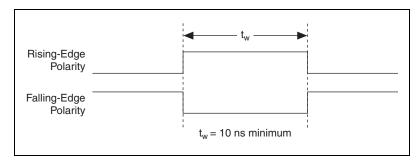

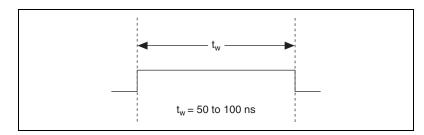

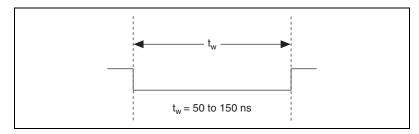

| Figure B-3.                                                                                                             | AI START TRIG Input Signal TimingB-3                                                                                                                                                                                                                                                                                                   |

| <b>D' D</b> 4                                                                                                           |                                                                                                                                                                                                                                                                                                                                        |

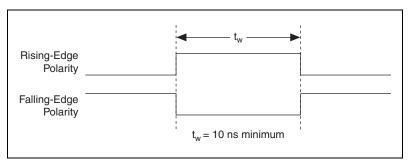

| Figure B-4.                                                                                                             | AI START TRIG Output Signal TimingB-3                                                                                                                                                                                                                                                                                                  |

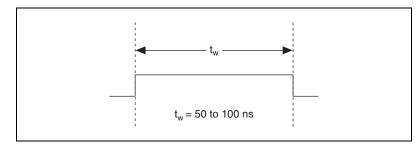

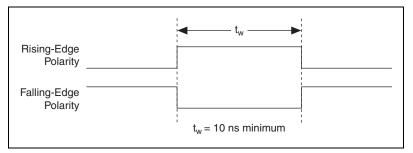

| Figure B-5.                                                                                                             | AI START TRIG Output Signal TimingB-3<br>AI REF TRIG Input Signal TimingB-4                                                                                                                                                                                                                                                            |

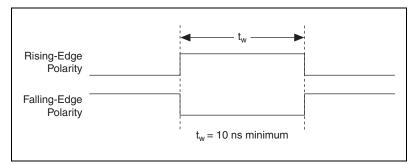

| Figure B-5.<br>Figure B-6.                                                                                              | AI START TRIG Output Signal TimingB-3<br>AI REF TRIG Input Signal TimingB-4<br>AI REF TRIG Output Signal TimingB-5                                                                                                                                                                                                                     |

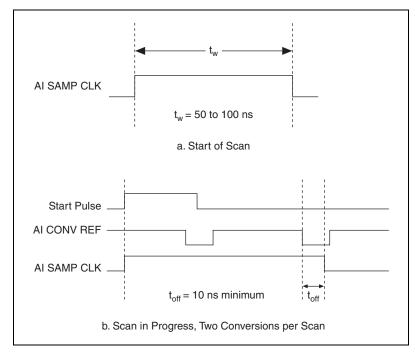

| Figure B-5.<br>Figure B-6.<br>Figure B-7.                                                                               | AI START TRIG Output Signal TimingB-3<br>AI REF TRIG Input Signal TimingB-4                                                                                                                                                                                                                                                            |

| Figure B-5.<br>Figure B-6.                                                                                              | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6                                                                                                                                                   |

| Figure B-5.<br>Figure B-6.<br>Figure B-7.                                                                               | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6AI CONV CLK Input Signal Timing.B-7                                                                                                                |

| Figure B-5.<br>Figure B-6.<br>Figure B-7.<br>Figure B-8.                                                                | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6AI CONV CLK Input Signal Timing.B-7                                                                                                                |

| Figure B-5.<br>Figure B-6.<br>Figure B-7.<br>Figure B-8.<br>Figure B-9.                                                 | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6                                                                                                                                                   |

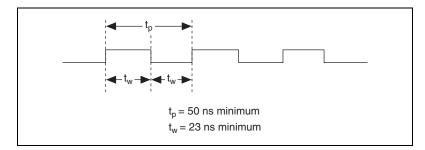

| Figure B-5.<br>Figure B-6.<br>Figure B-7.<br>Figure B-8.<br>Figure B-9.<br>Figure B-10.                                 | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6AI CONV CLK Input Signal Timing.B-7AI CONV CLK Output Signal Timing.B-8                                                                            |

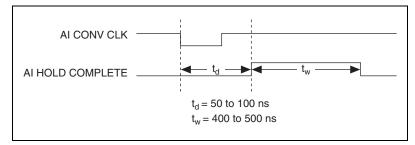

| Figure B-5.<br>Figure B-6.<br>Figure B-7.<br>Figure B-8.<br>Figure B-9.<br>Figure B-10.<br>Figure B-11.<br>Figure B-12. | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6AI CONV CLK Input Signal Timing.B-7AI CONV CLK Output Signal Timing.B-8AI SAMPLE CLK TIMEBASE Signal Timing.B-9AI HOLD COMPLETE Signal Timing.B-10 |

| Figure B-5.<br>Figure B-6.<br>Figure B-7.<br>Figure B-8.<br>Figure B-9.<br>Figure B-10.<br>Figure B-11.                 | AI START TRIG Output Signal Timing.B-3AI REF TRIG Input Signal Timing.B-4AI REF TRIG Output Signal Timing.B-5AI SAMP CLK Input Signal Timing.B-6AI SAMP CLK Output Signal Timing.B-6AI CONV CLK Input Signal Timing.B-7AI CONV CLK Output Signal Timing.B-8AI SAMPLE CLK TIMEBASE Signal Timing.B-9                                    |

### Tables

| Table 3-1. | Signal Conditioning Functional Blocks       | 3-3 |

|------------|---------------------------------------------|-----|

| Table 3-2. | PXI Trigger Bus Timing Signals              |     |

| Table 3-3. | NI-DAQmx Properties                         |     |

| Table 3-4. | Programming a Task in LabVIEW               |     |

| Table 3-5. | Synchronizing the NI PXI-4204 Using LabVIEW |     |

| Table A-1. | Maximum Sampling Rates                      | A-1 |

## About the NI PXI-4204

The NI PXI-4204 is part of the PXI-4200 series of data acquisition (DAQ) devices with integrated signal conditioning. The PXI-4200 series reduces measurement setup and configuration complexity by integrating signal conditioning and DAQ on the same product.

The NI PXI-4204 is a full-featured measurement device with programmable filter and gain settings per channel, ensuring maximum accuracy over the entire ±100 V input range. The NI PXI-4204 features the National Instruments (NI) programmable gain instrumentation amplifier (PGIA), an instrumentation-class amplifier that guarantees fast settling times at all gain settings.

The NI PXI-4204 is an eight-channel device for measuring voltages up to  $\pm 100$  volts. The NI PXI-4204 has the following features:

- Eight differential analog input (AI) channels

- 16-bit resolution

- 200 kS/s aggregate sampling rate

- 22 kS/s per channel when simultaneously sampling all channels

- Input ranges of  $\pm 100$ ,  $\pm 50$ ,  $\pm 5$ , and  $\pm 0.5$  V

- Two-pole software programmable Butterworth filters with software selectable filter settings of 6 Hz and 10 kHz per channel

- Instrumentation amplifier per channel

- Track-and-hold (T/H) circuitry providing simultaneous sample-and-hold (SS/H) capability

- Synchronization with other DAQ devices through the PXI trigger bus

- Direct connectivity through a removable COMBICON connector

You can configure most settings on a per-channel basis through software. The NI PXI-4204 is configured using Measurement & Automation Explorer (MAX) or through function calls to NI-DAQmx.

### What You Need to Get Started

To set up and use the NI PXI-4204, you need the following:

- □ Hardware

- NI PXI-4204 device

- Safety shell (provided)

- COMBICON screw terminal connector (provided)

- PXI or PXI/SCXI combination chassis

- □ Software

- NI-DAQ 7.0 or later

- One of the following:

- LabVIEW

- Measurement Studio

- LabWindows<sup>TM</sup>/CVI<sup>TM</sup>

- Documentation

- NI PXI-4204 User Manual

- Read Me First: Safety and Radio-Frequency Interference

- DAQ Getting Started Guide

- PXI or PXI/SCXI combination chassis user manual

- Documentation for your software

- Tools

- 1/8 in. flathead screwdriver

You can download NI documents from ni.com/manuals.

### National Instruments Documentation

The *NI PXI-4204 User Manual* is one piece of the documentation set for your DAQ system. You could have any of several types of manuals, depending on the hardware and software in your system. Use the documentation you have as follows:

• DAQ Getting Started Guide—This document describes how to install DAQ devices and the NI-DAQ driver software. Install NI-DAQ before you install the SCXI module.

- *SCXI Quick Start Guide*—This document describes how to set up an SCXI chassis, install SCXI modules and terminal blocks, and configure the SCXI system in MAX.

- PXI or PXI/SCXI combination chassis manual—Read this manual for maintenance information about the chassis and for installation instructions.

- Accessory installation guides or manuals—If you are using accessory products, read the terminal block installation guides. It explain how to physically connect the relevant pieces of the system. Consult this guide when you are making the connections.

- Software documentation—You may have both application software and NI-DAQmx software documentation. NI application software includes LabVIEW, Measurement Studio, and LabWindows/CVI. After you set up the hardware system, use either your application software documentation or the NI-DAQmx documentation to help you write your application. If you have a large, complicated system, it is worthwhile to look through the software documentation before you configure the hardware.

# Installing the Application Software, NI-DAQ, and the DAQ Device

Refer to the *DAQ Getting Started Guide*, packaged with the NI-DAQ software, to install your application software and NI-DAQ driver software.

NI-DAQ 7.0 or later is required to configure and program the NI PXI-4204 device. If you do not have NI-DAQ 7.0 or later, you can either contact an NI sales representative to request it on a CD or download the latest NI-DAQ version from ni.com.

### Installing the NI PXI-4204

**Note** Refer to the *Read Me First: Safety and Radio-Frequency Interference* document before removing equipment covers or connecting or disconnecting any signal wires.

Refer to the *DAQ Getting Started Guide* to unpack, install, and configure the NI PXI-4204 in a PXI chassis and then to the *SCXI Quick Start Guide* if you are using a PXI/SCXI combination chassis.

### **LED Pattern Descriptions**

The following LEDs on the NI PXI-4204 front panel confirm the system is functioning properly:

- The *ACCESS* LED is normally green and blinks yellow for a minimum of 100 ms during the NI PXI-4204 configuration.

- The *ACTIVE* LED is normally green and blinks yellow for a minimum of 100 ms during data acquisition.

# **Connecting Signals**

This chapter provides information about the NI PXI-4204 front signal connector and how to connect signals to the NI PXI-4204.

### **Connecting Signals to the NI PXI-4204**

After you have verified that the NI PXI-4204 is installed correctly and self-tested the device, refer to the following sections to connect signals to the device.

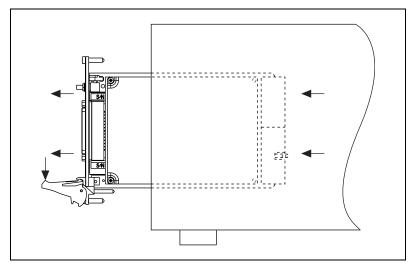

**Caution** You *must* clamp the safety shell over the COMBICON connector to prevent accidental contact with hazardous voltages. Refer to Figure 2-1 for information about how to properly install the NI PXI-4204 and safety shell.

2

Figure 2-1. Installing the NI PXI-4204 Device

**Caution** Refer to the *Read Me First: Safety and Radio-Frequency Interference* document before removing equipment covers or connecting/disconnecting any signal wires.

### **Front Signal Connector**

The NI PXI-4204 is a direct-connect device. The connection interface consists of a 16-pin COMBICON connector and one SMB connector. Figure 2-2 shows the pin assignments for the signals. Figure 2-3 shows the front label of the NI PXI-4204, with each set of screw terminals labeled according to the corresponding differential input signal. To connect a signal to the NI PXI-4204, complete the following steps while referring to Figures 2-2 and 2-3:

- 1. Remove power from the signal lines. If this is not possible, complete the following steps while referring to Figures 2-2, and 2-3.

- a. Remove the COMBICON connector from the NI PXI-4204.

- b. Attach the signal sources according to the instructions in steps 2 through 4.

- c. Ensure the NI PXI-4204 is powered on.

- d. Reinstall the COMBICON connector.

- 2. Strip 7 mm (0.25 in.) of insulation from the ends of the signal wires.

- 3. Insert the wires into the screw terminals.

- 4. Tighten the screws to  $0.5-0.6 \text{ N} \cdot \text{m} (4.4-5.3 \text{ lb} \cdot \text{in.})$  of torque.

Connect a timing or triggering signal to the PFI0/CAL SMB connector using a cable with an SMB signal connector.

**Caution** The PFI0/CAL SMB connector is for low-voltage timing and calibration signals *only*. Voltages greater than  $\pm 15$  V can damage the device.

| PFI 0/ | $\bigcirc$ |  |

|--------|------------|--|

| CAL    |            |  |

| AI0+   | 1          |  |

| AI0-   | 2          |  |

| Al1+   | 3          |  |

| Al1–   | 4          |  |

| Al2+   | 5          |  |

| Al2–   | 6          |  |

| Al3+   | 7          |  |

| AI3–   | 8          |  |

| Al4+   | 9          |  |

| Al4–   | 10         |  |

| AI5+   | 11         |  |

| AI5-   | 12         |  |

| Al6+   | 13         |  |

| AI6-   | 14         |  |

| AI7+   | 15         |  |

| AI7-   | 16         |  |

|        |            |  |

Figure 2-2. NI PXI-4204 Screw Terminals

Figure 2-3. NI PXI-4204 Front Label

### **Analog Input Connections**

The following sections provide a definition of the signal source characteristics, descriptions of various ways to connect signals to the NI PXI-4204, and electrical diagrams showing the signal source and connections. Whenever possible, use shielded twisted-pair field wiring to reduce the effects of unwanted noise sources.

In the electrical diagrams, two different ground symbols are used. These symbols indicate that you cannot assume that the indicated grounds are at the same potential. Refer to Appendix A, *Specifications*, for maximum working voltage specifications.

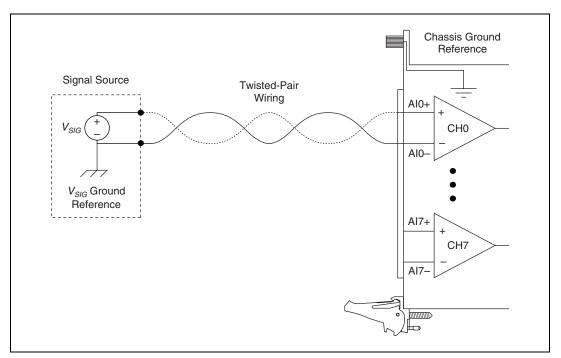

### **Floating Signal Source Connection**

Figure 2-4 illustrates the floating signal source connection. In this configuration, the signal source being measured is a floating signal source, such as a battery.

To connect a floating signal source connection to the NI PXI-4204, the signal ( $V_{SIG}$ +) is connected to the NI PXI-4204 channel (AIX+). The signal reference ( $V_{SIG}$ -) is connected to the channel reference (AIX-). The lack of shielding on the field wiring can cause this configuration to be susceptible to electrically coupled noise.

This configuration has only one ground connection—at the instrument—so there is no potential difference between grounds to introduce error in your measurements. The NI PXI-4204 input attenuators provide a ground reference for floating signal sources; therefore, external grounding bias resistors are not required.

Figure 2-4. Floating Signal Source Connection

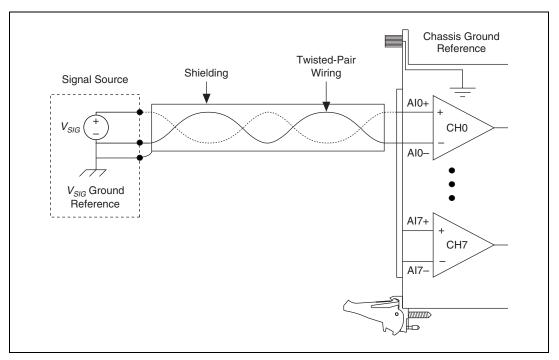

# Shielded Floating Signal Source Connection (Recommended)

The signal source shown in Figure 2-5 is identical to the one shown in Figure 2-4. The only difference is the addition of shielding around the field wiring.

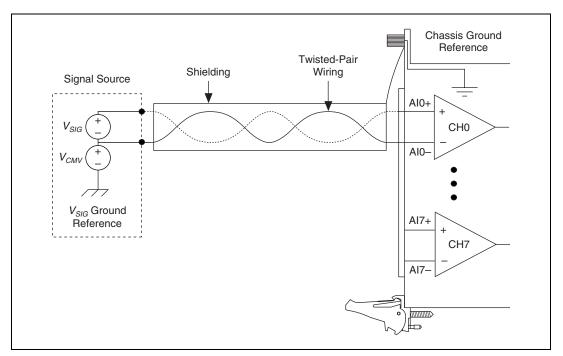

You can improve the noise susceptibility of the floating signal source connection, shown in Figure 2-4, by using a shielded cable to connect the signal source to the instrument, as shown in Figure 2-5. This is the recommended shielding configuration for floating signal sources. The shielding is grounded at only one point to the NI PXI-4204 chassis ground reference. Connect the signal ( $V_{SIG}$ +) to the NI PXI-4204 channel (AIX+). Connect the signal reference ( $V_{SIG}$ -) to the channel reference (AIX-).

Figure 2-5. Shielded Floating Signal Source Connection (Recommended)

$\mathbb{N}$

### **Ground-Referenced Signal Connection**

Figure 2-6 illustrates the ground-referenced signal connection. In this configuration, the voltage source being measured is referenced to its own ground reference that is connected through some conductive path to the instrument ground reference. For example, the path can be through a common earth ground or through the power line ground.

**Note** This connection is a characteristic of the signal source and no additional wiring should be added to connect the signal source ground reference to the NI PXI-4204 ground reference.

To connect a ground-reference signal source to the NI PXI-4204, the signal  $(V_{SIG}+)$  is connected to the NI PXI-4204 channel (AIX+). The signal reference  $(V_{SIG}-)$  is connected to the channel reference (AIX-). The signal ground reference ( $V_{SIG}$  Ground Reference) is referenced to the NI PXI-4204 chassis ground reference inherently through some conductive path that you do not physically connect.

This configuration is very simple to connect, but it also can be susceptible to capacitive or electrically coupled noise. Also, the difference in ground potential between the signal source ground and instrument ground creates an unwanted signal that can introduce an error into the measurement. This error is presented as a common-mode voltage (CMV) to the differential front end of the NI PXI-4204, and is reduced by the common-mode rejection (CMR) of the differential instrumentation amplifier. The effectiveness of the CMR is affected by the source resistance of the signal being measured. For more information about the effect of source resistance on CMR, refer to the *Measurement Considerations* section of Chapter 3, *Using the NI PXI-4204*.

Figure 2-6. Ground-Referenced Signal Connection

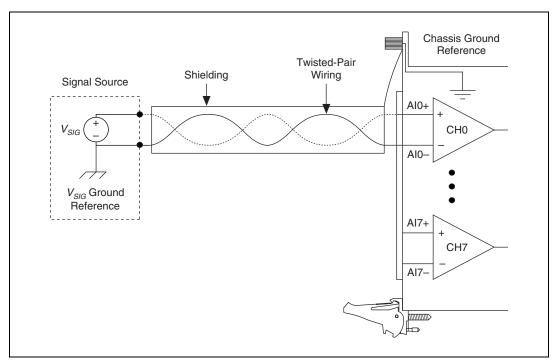

# Shielded Ground-Referenced Signal Connection (Recommended)

Figure 2-7 illustrates a shielded ground-referenced signal connection. The connection to this signal source is identical to the ground-referenced signal connection with the addition of shielding around the field wiring. The ground-referenced signal source in Figure 2-7 is identical to the signal source in Figure 2-6.

The shielding is grounded at only one point to the signal source ground ( $V_{SIG}$  Ground Reference). Connect the signal ( $V_{SIG}$ +) to the NI PXI-4204 channel (AIX+). Connect the signal reference ( $V_{SIG}$ -) to the channel reference (AIX-).

This shielding scheme is effective at reducing capacitive or electrically coupled noise. The same concerns regarding the difference in ground potentials, discussed in the *Ground-Referenced Signal Connection* section, also apply to this configuration.

Figure 2-7. Recommended Shielded Ground-Referenced Signal Connection

### Alternative Shielded Ground-Referenced Connection

Figure 2-8 illustrates an alternative shielded ground-referenced signal connection. The ground-referenced signal source in Figure 2-8 is identical to the signal source in Figure 2-7. The only difference is where you wire the shielded ground connection.

The shielded ground connection in Figure 2-7 is the most effective configuration for reducing electrically induced noise in a ground-referenced measurement. However, if connecting the shielding to the signal source ground is cumbersome or inconvenient, use the connection shown in Figure 2-8 to reduce electrically coupled noise. The shielding is grounded at only one point to the NI PXI-4204 chassis ground reference. Connect the signal ( $V_{SIG}$ +) to the NI PXI-4204 channel (AIX+). Connect the signal reference ( $V_{SIG}$ -) to the channel reference (AIX-).

The same concerns regarding the difference in ground potentials, discussed in the *Ground-Referenced Signal Connection* section, also apply to this configuration.

Figure 2-8. Alternative Shielded Ground Referenced Signal Connection

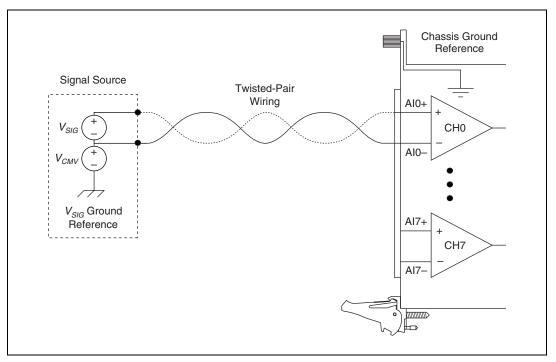

### **High CMV Connection**

Figure 2-9 shows a signal source with a high CMV present. With this configuration, the signal rides on an offset voltage called the CMV. The CMV is not of interest to the measurement and can appear as an error in the voltage measurement. This type of connection can be treated as a ground-referenced signal source with a large difference between the signal source reference and the NI PXI-4204 chassis ground reference.

To connect a signal source with high CMV to the NI PXI-4204, connect the signal ( $V_{SIG}$ +) to the NI PXI-4204 channel (AIX+). Connect the signal reference ( $V_{SIG}$ -) to the channel reference (AIX-).

The balanced front end of the NI PXI-4204 rejects CMV, making it possible to measure signal sources in the presence of a large CMV. The only constraint for the NI PXI-4204 is that the combined signal and CMV must not exceed  $\pm 100$  V. The maximum allowed combination of signal voltage and CMV is specified as the maximum working voltage.

Figure 2-9. High CMV Connection

### **Shielded High CMV Connection**

The signal source with a high CMV in Figure 2-10 is identical to the signal source in Figure 2-9. The only difference is the addition of shielding around the field wiring.

To connect a signal source with high CMV to the NI PXI-4204, connect the signal ( $V_{SIG}$ +) to the NI PXI-4204 channel (AIX+). Connect the signal reference ( $V_{SIG}$ -) to the channel reference (AIX-). The shielding is grounded at only one point to the NI PXI-4204 chassis ground reference.

This shielding scheme is effective at reducing capacitive or electrically coupled noise.

**Caution** If possible, ground the shielding at the NI PXI-4204, and *not* at the signal source. Grounding the shielding at the signal source in the presence of a high CMV can create a safety hazard by energizing the shield.

Figure 2-10. Shielded High CMV Connection

For more information about the function of the NI PXI-4204 and other measurement considerations, refer to Chapter 3, *Using the NI PXI-4204*.

# 3

# Using the NI PXI-4204

This chapter describes the theory of operation, measurement considerations, timing information, programming, creating program applications in LabVIEW, and calibration.

### **Theory of Operation**

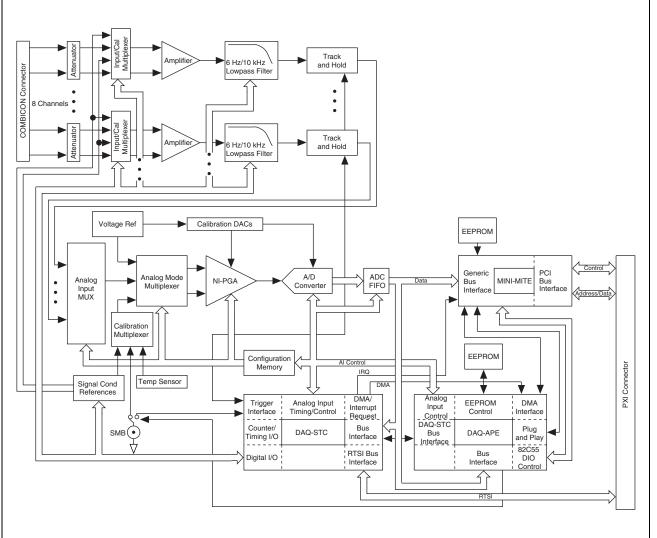

Figure 3-1 illustrates the key functional components of the NI PXI-4204, including the DAQ and integrated signal conditioning circuitry.

### Signal Conditioning Functional Overview

The NI PXI-4204 is part of the NI PXI-4200 series of DAQ devices designed to provide application-specific signal conditioning, DAQ, and integrated field wiring connectivity on the same product. The NI PXI-4204 signal conditioning circuitry is designed to provide attenuation, amplification, filtering, and SS/H capability as described in Table 3-1.

| Signal Conditioning Component | Description                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Divide-by-Ten Attenuator      | Each NI PXI-4204 channel front end has a balanced divide-by-ten attenuator. The attenuation is provided by a resistor-divider network that provides 1 M $\Omega$ input impedance. The balanced attenuator followed by an instrumentation amplifier provides rejection of common-mode signals and enables the NI PXI-4204 to measure voltages up to ±100 V. |

| Input Multiplexer             | Each channel of the NI PXI-4204 includes an analog<br>multiplexer. You can use this multiplexer to<br>programmatically route internal test signals to the<br>NI PXI-4204 instrumentation amplifiers for self-calibration<br>and self-test.                                                                                                                 |

| Instrumentation Amplifier     | The instrumentation amplifier following the attenuation stage<br>of the NI PXI-4204 provides a very high-load impedance to<br>the previous stage, rejection of common-mode signals, and<br>converts differential signals to single-ended signals that are<br>then fed to the filter stage.                                                                 |

| Table 3-1. Signal Conditioning Functional Blo |

|-----------------------------------------------|

|-----------------------------------------------|

| Signal Conditioning Component | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Lowpass Filter                | The NI PXI-4204 includes a 2-pole Butterworth filter per<br>channel with two software-selectable cutoff frequencies to<br>reduce signal noise and improve accuracy. You can<br>programmatically configure the filter bandwidths on a per<br>channel basis for cutoff frequencies of 6 Hz or 10 kHz. The<br>6 Hz filter setting attenuates differentially connected 60 Hz<br>signals by 40 dB.                                                                                                                                 |

| T/H Circuitry                 | You can enable the NI PXI-4204 track-and-hold circuitry to<br>enable SS/H. This allows you to acquire synchronized<br>measurements across multiple channels. You cannot enable<br>or disable SS/H on a per channel basis. It is disabled by<br>default. Enabling SS/H results in slower maximum sample<br>rates and slightly degraded accuracy.                                                                                                                                                                               |

|                               | With SS/H disabled, the NI PXI-4204 uses a multiplexed<br>architecture that enables the measurement of multiple<br>channels using a single analog-to-digital converter (ADC).<br>The multiplexing architecture of the NI PXI-4204 results in<br>measurements between channels that are separated in time.<br>The time delay between channels is determined by the sample<br>rate at which you acquire measurements. For most<br>low-frequency measurement applications, this time delay or<br>phase delay is not significant. |

**Table 3-1.** Signal Conditioning Functional Blocks (Continued)

### **Measurement Considerations**

This section provides more information about the type of signal connection made to the NI PXI-4204 and important factors that can affect your measurement.

### **Differential Signals**

All of the analog inputs of the NI PXI-4204 are differential. In general, a differential measurement system is preferable because it rejects not only ground loop-induced errors and common-mode voltages, but also the noise picked up in the environment to a certain degree.

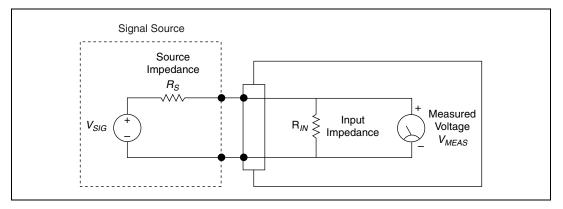

### **Input Impedance**

Figure 3-2 illustrates the input impedance of an NI PXI-4204 and its effect on the measurement of a circuit under test. If you know the source impedance of the circuit under test, you can correct for the attenuation caused by the NI PXI-4204 in software. Since  $R_{IN}$  is relatively large, 1 M $\Omega$ , it requires a large source impedance,  $R_S$ , to cause a significant change in the measured voltage,  $V_{MEAS}$ . In general, a source impedance of less than 200  $\Omega$  does not interfere with the accuracy of the measurement. For example, a 200  $\Omega$  source impedance results in a 0.02% gain error.

$$V_{MEAS} = \frac{V_{SIG}R_{IN}}{R_S + R_{IN}}$$

Figure 3-2. Effect of Input Impedance on Signal Measurements

### **Common-Mode Rejection Ratio**

The ability of a measurement device to reject voltages that are common to both input terminals is referred to as the common-mode rejection ratio (CMRR) and is usually stated in decibels at a given frequency or over a given frequency band of interest. Common-mode signals can arise from a variety of sources and can be induced through conductive or radiated means. One of the most common sources of common-mode interference is due to 50 or 60 Hz powerline noise.

The minimum NI PXI-4204 CMRR is 60 dB. This results in a reduction of CMV by a factor of 1000. The measured signal source impedance can reduce the NI PXI-4204 CMR. Specifically, if the signal source has an imbalanced source impedance like the one in Figure 3-2, then an imbalance is introduced into the NI PXI-4204 front-end. This imbalance causes a reduction in the CMRR. The reduction in CMRR due to source impedance

can be approximated by taking the ratio of the source impedance and the NI PXI-4204 input impedance, and combining it with the minimum CMRR of the NI PXI-4204.

For example, consider the following ratio of signal source and input impedance:

$$\frac{1 \text{ k}\Omega}{1 \text{ M}\Omega} = 0.001$$

Converting the NI PXI-4204 60 db CMRR specification from decibels to a ratio yields:

$$\frac{1}{10^{\frac{60}{20}}} = 0.001$$

The two terms are then added together to yield 0.002. Expressing this result in decibels yields:

$$20\log_{10}(0.002) = -54$$

dB

### **Normal-Mode Rejection**

Normal-mode rejection (NMR) refers to the ability of the NI PXI-4204 to reject a differentially (normally) applied signal when the NI PXI-4204 filters are set to 6 Hz. The NMR is a function of the lowpass filter characteristics and is quantified in the normal-mode rejection ratio (NMRR) specification, which specifies the capability of the NI PXI-4204 to reject a differentially applied unwanted 60 Hz signal. In the case of the NI PXI-4204, this specification is 40 db at 60 Hz with a 6 Hz filter setting. This NMR is usually only applicable when taking DC measurements. The NMRR is specified at the powerline frequency because this is typically where most measurement noise arises.

### **Effective CMR**

When the frequency of a common-mode signal is known and outside of the measurement frequency band of interest, you can use an analog or digital filter, or both, to further reduce the residual error left from the finite CMRR of the instrument. The combined CMR of the instrument and the filter attenuation results in an effective CMR. When expressed in decibels, the effective CMR is equal to the sum of the CMRR and the attenuation due to the filter at a specified frequency.

### **Timing and Control Functional Overview**

The NI PXI-4204 is based on the NI E Series DAQ device architecture. This architecture uses the NI data acquisition system timing controller (DAQ-STC) for time-related functions. The DAQ-STC consists of two timing groups that control AI and general-purpose counter/timer functions. These groups include a total of seven 24-bit and three 16-bit counters and a maximum timing resolution of 50 ns. The DAQ-STC makes possible applications such as equivalent time sampling, and seamless changing of the sampling rate.

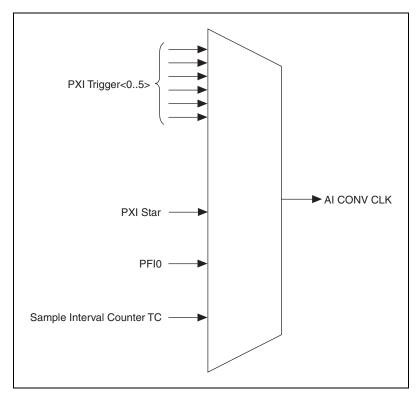

The NI PXI-4204 uses the PXI trigger bus to easily synchronize several measurement functions to a common trigger or timing event. The PXI trigger bus is connected through the rear signal connector to the PXI chassis backplane. The DAQ-STC provides a flexible interface for connecting timing signals to other devices or external circuitry. The NI PXI-4204 uses the PXI trigger bus to interconnect timing signals between PXI devices and the programmable function input (PFI) pin on the front SMB connector to connect the device to external circuitry. These connections are designed to enable the device to both control and be controlled by other devices and circuits.

The DAQ-STC has internal timing signals you can control by an external source. These timing signals also can be controlled by signals internally generated to the DAQ-STC, and these selections are software configurable. Figure 3-3 shows an example of the signal routing multiplexer controlling the AI CONV CLK signal.

Figure 3-3. AI CONV CLK Signal Routing

Figure 3-3 shows that AI CONV CLK can be generated from a number of sources, such as the external signals PFI0, PXI\_Trig<0..5>, and PXI Star, and the internal signals sample interval (SI2) counter TC.

### **Programmable Function Inputs**

PFI0 is connected to the front SMB connector of the NI PXI-4204. Software can select PFI0 as the external source for a given timing signal. Any timing signal can use the PFI0 pin as an input, and multiple timing signals can simultaneously use the same PFI. This flexible routing scheme reduces the need to change physical connections to the I/O connector for different applications. You can enable PFI0 to output the AI START TRIG signal.

### **Device and PXI Clocks**

Many functions performed by the NI PXI-4204 require a frequency timebase to generate the necessary timing signals for controlling A/D conversions, digital-to-analog converter (DAC) updates, or general-purpose signals at the I/O connector.

The NI PXI-4204 can use either its internal 20 MHz master timebase or a timebase received over the PXI trigger bus on the PXI clock line. This timebase is software configurable. If you configure the device to use the internal timebase, you can program the device to drive its internal timebase over the PXI trigger bus to another device programmed to receive this timebase signal. This clock source, whether local or from the PXI trigger bus, is used directly by the device as the primary frequency source. The default configuration is to use the internal timebase without driving the PXI trigger bus timebase signal. The NI PXI-4204 can use the PXI\_Trig 7 line to synchronize Master Timebase with other devices.

For the NI PXI-4204, PXI Trig<0..5> and PXI Star connect through the NI PXI-4204 backplane. The PXI Star Trigger line allows the NI PXI-4204 to receive triggers from any Star Trigger controller plugged into slot 2 of the chassis. The NI PXI-4204 can only receive signals on the PXI Star Trigger line. For more information about the Star Trigger, refer to the *PXI Hardware Specification, Revision 2.1* and *PXI Software Specification, Revision 2.1*.

Figure 3-4 shows this signal connection scheme.

Figure 3-4. NI PXI-4204 PXI Trigger Bus Signal Connection

Table 3-2 provides more information about each of the timing signals available on the PXI trigger bus. For more detailed timing signal information, refer to Appendix B, *Timing Signal Information*.

| Signal        | Direction                                                                                                                | Description                                                                                            | Availability on<br>PFI0 SMB | Availability on<br>PXI Trigger<br>Bus |

|---------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|

| AI START TRIG | Input                                                                                                                    | This is the source for the analog input digital start trigger, the trigger that begins an acquisition. | Input                       | Input                                 |

|               | Output                                                                                                                   | This sends out the actual analog input start trigger.                                                  | Output                      | Output                                |

| AI REF TRIG   | RIG         Input         This is the trigger that creates the reference<br>point between the pretrigger samples and the |                                                                                                        | Input                       | Input                                 |

|               | Output                                                                                                                   | posttrigger samples.                                                                                   |                             | Output                                |

Table 3-2. PXI Trigger Bus Timing Signals

| Signal                    | Direction       | Description                                                                                                                                      | Availability on<br>PFI0 SMB | Availability on<br>PXI Trigger<br>Bus |

|---------------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------------|

| AI SAMP CLK               | Input<br>Output | This clock controls the time interval between<br>samples. Each time the sample clock<br>produces a pulse, one sample per channel<br>is acquired. | Input                       | Input<br>Output                       |

| AI CONV CLK               | Input<br>Output | This clock directly causes analog-to-digital conversions.                                                                                        | Input                       | Input<br>Output                       |

| AI PAUSE TRIG             | Input           | This signal can pause and resume acquisition.                                                                                                    | Input                       | Input                                 |

| AI SAMPLE CLK<br>TIMEBASE | Input           | This timebase provides the master clock from which the sample clocks are derived.                                                                | Input                       | Input                                 |

Table 3-2. PXI Trigger Bus Timing Signals (Continued)

### **Developing Your Application**

This section describes the software and programming steps necessary to use the NI PXI-4204. For more information about a particular software or programming process, refer to your ADE documentation.

### **Typical Program Flow Chart**

Figure 3-5 shows a typical program flow chart for creating an AI voltage channel, taking a measurement, and clearing the data.

**Note** Many example programs ship with NI-DAQmx. For more information about how to create tasks and channels, refer to the example programs.

Figure 3-5. Typical Program Flowchart

#### **General Discussion of Typical Flow Chart**

The following sections briefly discuss some considerations for a few of the steps in Figure 3-5. The purpose of these sections is to provide an overview of some of the options and features available when programming with NI-DAQmx.

#### Creating a Task Using DAQ Assistant or Programmatically

When creating an application, you must first decide whether to create the appropriate task using the DAQ Assistant or programmatically in the ADE.

Developing your application using NI-DAQmx gives you the ability to configure most settings, such as measurement type, selection of channels, input limits, task timing, and task triggering using the DAQ Assistant tool. You can access the DAQ Assistant either through MAX or through your NI ADE. Choosing to use the DAQ Assistant can simplify the development of your application. NI recommends creating tasks using the DAQ Assistant for ease of use, when using a sensor that requires complex scaling, or when many properties differ between channels in the same task.

If you are using an ADE other than an NI ADE, or if you want to explicitly create and configure a task for a certain type of acquisition, you can programmatically create the task from your ADE using function or VI calls. If you create a task using the DAQ Assistant, you can still further configure the individual properties of the task programmatically using function calls or property nodes in your ADE. NI recommends creating a task programmatically if you need explicit control of programmatically adjustable properties of the DAQ system. Programmatically creating tasks is also recommended if you are synchronizing multiple devices using master and slave tasks. Refer to the *Synchronizing the NI PXI-4204* section for more information about synchronizing multiple NI PXI-4204 devices.

Programmatically adjusting properties for a task created in the DAQ Assistant overrides the original settings only for that session. The changes are *not* saved to the task configuration. The next time you load the task, the task uses the settings originally configured in the DAQ Assistant.

# Adjusting Timing and Triggering

There are several timing properties that you can configure either through the DAQ Assistant or programmatically using function calls or property nodes in your application. If you create a task in the DAQ Assistant, you still can modify the timing properties of the task programmatically in your application.

When programmatically adjusting timing settings, you can set the task to acquire continuously, acquire a buffer of samples, or acquire one point at a time. For continuous and buffered acquisitions, you can set the acquisition rate and the number of samples to read. By default, the clock settings are automatically set by an internal clock based on the requested sample rate. You also can select advanced features, such as clock settings, that specify an external clock source, internal routing of the clock source, or select the active edge of the clock signal.

### **Configuring Channel Properties**

All of the different ADEs used to configure the NI PXI-4204 access an underlying set of NI-DAQmx properties. Table 3-3 lists some of the properties that configure the NI PXI-4204. You can use this list to determine what kinds of properties you need to set to configure the device for your application. If you created the task and channels using the DAQ Assistant, you can still modify the channel properties programmatically. For a complete list of NI-DAQmx properties, refer to your ADE help file.

| Property                                                                          | Short Name            | Description                                                                                                                              |  |  |

|-----------------------------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Analog Input»<br>General Properties»<br>Input Configuration»<br>Coupling Property | AI.Coupling           | DC—Allows NI-DAQmx to<br>measure the input signal.<br>GND—Removes the signal<br>source from the measurement<br>and measures only ground. |  |  |

| Analog Input»General<br>Properties»Filter»Analog<br>Lowpass»Cutoff Frequency      | AI.Lowpass.CutoffFreq | Specifies in hertz the frequency corresponding to the $-3$ dB cutoff of the filter. You can specify either 6.0 or 10000.0.               |  |  |

| Table 3-3. NI-DAQmx Properties |

|--------------------------------|

|--------------------------------|

| Property                                                                                  | Short Name            | Description                                                                                                  |

|-------------------------------------------------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------|

| Analog Input»General<br>Properties»Advanced»<br>Sample and Hold Enable                    | AI.SampAndHold.Enable | Specifies whether to enable the sample and hold circuitry of the device.                                     |

| Analog Input»General<br>Properties»Advanced»<br>High Accuracy Settings»<br>Auto Zero Mode | AI.AutoZeroMode       | Specifies when to measure<br>ground. NI-DAQmx subtracts the<br>measured ground voltage from<br>every sample. |

Table 3-3. NI-DAQmx Properties (Continued)

**Note** This is *not* a complete list of NI-DAQmx properties. It is a representative sample of important properties you can adjust in analog input measurements with the NI PXI-4204. For a complete list of NI-DAQmx properties and more information about NI-DAQmx properties, refer to your ADE help file.

# Acquiring, Analyzing, and Presenting

After configuring the task and channels, you can start your acquisition, read measurements, analyze the data returned, and display it according to the needs of your application. Typical methods of analysis include digital filtering, averaging data, performing harmonic analysis, applying a custom scale, or adjusting measurements mathematically.

NI provides powerful analysis toolsets for each NI ADE to help you perform advanced analysis on the data without requiring a programming background. After you acquire the data and perform any required analysis, it is useful to display the data in a graphical form or log it to a file. NI ADEs provide easy-to-use tools for graphical display, such as charts, graphs, slide rules, and gauge indicators. NI ADEs have tools that allow you to save the data to files such as spread sheets for easy viewing, ASCII files for universality, or binary files for smaller file sizes.

# **Completing the Application**

After you have completed the measurement, analysis, and presentation of the data, it is important to stop and clear the task. This releases any memory used by the task and frees up the DAQ hardware for use in another task.

#### **Developing an Application Using LabVIEW**

This section describes in more detail the steps shown in the typical program flowchart in Figure 3-5, such as how to create a task in LabVIEW and configure the channels of the NI PXI-4204. For more information or further instructions, select **Help\*VI**, **Function**, **& How-To Help** from the LabVIEW menu bar.

**Note** Except where otherwise stated, the VIs in Table 3-4 are located on the **Functions**» **All Functions**»**NI Measurements**»**DAQmx - Data Acquisition** subpalette and accompanying subpalettes in the default LabVIEW palette view.

| Flowchart Step                                  | VI or Program Step                                                                                                                                                                                                                          |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Create Task in DAQ Assistant                    | Create a DAQmx Task Name Constant located on the<br>Controls»All Controls»I/O»DAQmx Name Controls<br>subpalette, right-click it, and select New Task (DAQ<br>Assistant).                                                                    |

| Create a Task<br>Programmatically<br>(optional) | DAQmx Create Task.vi—This VI is optional if you created<br>and configured your task using the DAQ Assistant. However, if<br>you use it in LabVIEW, any changes you make to the task will not<br>be saved to a task in MAX.                  |

| Create AI Voltage Channel<br>(optional)         | DAQmx Create Virtual Channel.vi (AI Voltage by default)—This VI is optional if you created and configured your task and channels using the DAQ Assistant.                                                                                   |

| Adjust Timing Settings<br>(optional)            | DAQmx Timing.vi (Sample Clock by default)—This VI is optional if you created and configured your task using the DAQ Assistant.                                                                                                              |

| Configure Channels<br>(optional)                | DAQmx Channel Property Node—Refer to the Using a DAQmx<br>Channel Property Node in LabVIEW section for more<br>information. This step is optional if you created and fully<br>configured the channels in your task using the DAQ Assistant. |

| Start Measurement                               | DAQmx Start Task.vi                                                                                                                                                                                                                         |

| Read Measurement                                | DAQmx Read.vi                                                                                                                                                                                                                               |

#### **Table 3-4.** Programming a Task in LabVIEW

| Flowchart Step    | VI or Program Step                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Analyze Data      | Some examples of data analysis include filtering, scaling,<br>harmonic analysis, and level checking. Some data analysis tools<br>are located on the <b>Functions</b> » <b>Signal Analysis</b> subpalette and on<br>the <b>Functions</b> » <b>All Functions</b> » <b>Analyze</b> subpalette.                                                                         |  |  |  |

| Display Data      | You can use graphical tools, such as charts, gauges, and graphs<br>to display your data. Some display tools are located on the<br><b>Controls»Numeric Indicators</b> subpalette and <b>Controls»</b><br><b>All Controls»Graph</b> subpalette.                                                                                                                       |  |  |  |

| Continue Sampling | For continuous sampling, use a While Loop. If you are using<br>hardware timing, you also need to set the DAQmx Timing.vi<br>sample mode to Continuous Samples. To do this, right-click the<br>terminal of the DAQmx Timing.vi labeled <b>sample mode</b> and<br>click <b>Create*Constant</b> . Click the box that appears and select<br><b>Continuous Samples</b> . |  |  |  |

| Stop Measurement  | DAQmx Stop Task.vi—This VI is optional. Clearing the task will automatically stop the task.                                                                                                                                                                                                                                                                         |  |  |  |

| Clear Task        | DAQmx Clear Task.vi                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| Table 3-4. | Programming a Task in LabVIEW | (Continued) | ) |

|------------|-------------------------------|-------------|---|

|            |                               | (Continuou) | 1 |

#### Using a DAQmx Channel Property Node in LabVIEW

**Note** With the NI PXI-4204, you must use property nodes to change filter settings and to enable SS/H.

You can use property nodes in LabVIEW to manually configure your channels. To create a LabVIEW property node, complete the following steps:

- 1. Launch LabVIEW.