#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

#### **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

PXI-4461

# **NI Dynamic Signal Acquisition**

**NI Dynamic Signal Acquisition User Manual**

Français Deutsch 日本語 한국어 简体中文 ni.com/manuals

#### **Worldwide Technical Support and Product Information**

ni.com

#### **National Instruments Corporate Headquarters**

11500 North Mopac Expressway Austin, Texas 78759-3504 USA Tel: 512 683 0100

#### **Worldwide Offices**

Australia 1800 300 800, Austria 43 662 457990-0, Belgium 32 (0) 2 757 0020, Brazil 55 11 3262 3599, Canada 800 433 3488, China 86 21 5050 9800, Czech Republic 420 224 235 774, Denmark 45 45 76 26 00, Finland 358 (0) 9 725 72511, France 01 57 66 24 24, Germany 49 89 7413130, India 91 80 41190000, Israel 972 3 6393737, Italy 39 02 41309277, Japan 0120-527196, Korea 82 02 3451 3400, Lebanon 961 (0) 1 33 28 28, Malaysia 1800 887710, Mexico 01 800 010 0793, Netherlands 31 (0) 348 433 466, New Zealand 0800 553 322, Norway 47 (0) 66 90 76 60, Poland 48 22 328 90 10, Portugal 351 210 311 210, Russia 7 495 783 6851, Singapore 1800 226 5886, Slovenia 386 3 425 42 00, South Africa 27 0 11 805 8197, Spain 34 91 640 0085, Sweden 46 (0) 8 587 895 00, Switzerland 41 56 2005151, Taiwan 886 02 2377 2222, Thailand 662 278 6777, Turkey 90 212 279 3031, United Kingdom 44 (0) 1635 523545

For further support information, refer to the *Technical Support and Professional Services* appendix. To comment on National Instruments documentation, refer to the National Instruments Web site at ni.com/info and enter the Info Code feedback.

© 2004–2010 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

The NI USB-4431/4432, NI 4461/4462, NI 4472/4472B/4474, and NI 4492/4495/4496/4497/4498/4499 are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this document is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

Except as specified herein, National Instruments makes no warranties, express or implied, and specifically disclaims any warranty of merchantability or fitness for a particular purpose. Customer's right to recover damages caused by fault or negligence on the part of National Instruments shall be lability of the amount therefore near particular purpose. The customer. National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments with apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

National Instruments respects the intellectual property of others, and we ask our users to do the same. NI software is protected by copyright and other intellectual property laws. Where NI software may be used to reproduce software or other materials belonging to others, you may use NI software only to reproduce materials that you may reproduce in accordance with the terms of any applicable license or other legal restriction.

#### Trademarks

CVI, LabVIEW, National Instruments, NI, ni.com, the National Instruments corporate logo, and the Eagle logo are trademarks of National Instruments Corporation. Refer to the *Trademark Information* at ni.com/trademarks for other National Instruments trademarks.

The mark LabWindows is used under a license from Microsoft Corporation. Windows is a registered trademark of Microsoft Corporation in the United States and other countries. Other product and company names mentioned herein are trademarks or trade names of their respective companies. Members of the National Instruments Alliance Partner Program are business entities independent from National Instruments and have no agency, partnership, or joint-venture relationship with National Instruments.

#### Patents 4 8 1

For patents covering National Instruments products/technology, refer to the appropriate location: **Help»Patents** in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents.

#### WARNING REGARDING USE OF NATIONAL INSTRUMENTS PRODUCTS

(1) NATIONAL INSTRUMENTS PRODUCTS ARE NOT DESIGNED WITH COMPONENTS AND TESTING FOR A LEVEL OF RELIABILITY SUITABLE FOR USE IN OR IN CONNECTION WITH SURGICAL IMPLANTS OR AS CRITICAL COMPONENTS IN ANY LIFE SUPPORT SYSTEMS WHOSE FAILURE TO PERFORM CAN REASONABLY BE EXPECTED TO CAUSE SIGNIFICANT INJURY TO A HUMAN.

(2) IN ANY APPLICATION, INCLUDING THE ABOVE, RELIABILITY OF OPERATION OF THE SOFTWARE PRODUCTS CAN BE IMPAIRED BY ADVERSE FACTORS, INCLUDING BUT NOT LIMITED TO FLUCTUATIONS IN ELECTRICAL POWER SUPPLY, COMPUTER HARDWARE MALFUNCTIONS, COMPUTER OPERATING SYSTEM SOFTWARE FITNESS, FITNESS OF COMPILERS AND DEVELOPMENT SOFTWARE USED TO DEVELOP AN APPLICATION, INSTALLATION ERRORS, SOFTWARE AND HARDWARE COMPATIBILITY PROBLEMS, MALFUNCTIONS OR FAILURES OF ELECTRONIC MONITORING OR CONTROL DEVICES, TRANSIENT FAILURES OF ELECTRONIC SYSTEMS (HARDWARE AND/OR SOFTWARE), UNANTICIPATED USES OR MISUSES, OR ERRORS ON THE PART OF THE USER OR APPLICATIONS DESIGNER (ADVERSE FACTORS SUCH AS THESE ARE HEREAFTER COLLECTIVELY TERMED "SYSTEM FAILURES"). ANY APPLICATION WHERE A SYSTEM FAILURE WOULD CREATE A RISK OF HARM TO PROPERTY OR PERSONS (INCLUDING THE RISK OF BODILLY INJURY AND DEATH), SHOULD NOT BE RELIANT SOLELY UPON ONE FORM OF ELECTRONIC SYSTEM DUE TO THE RISK OF SYSTEM FAILURE. TO AVOID DAMAGE, INJURY, OR DEATH, THE USER OR APPLICATION DESIGNER MUST TAKE REASONABLY PRUDENT STEPS TO PROTECT AGAINST SYSTEM FAILURES, INCLUDING BUT NOT LIMITED TO BACK-UP OR SHUT DOWN MECHANISMS. BECAUSE EACH END-USER SYSTEM IS CUSTOMIZED AND DIFFERS FROM NATIONAL INSTRUMENTS TESTING PLATFORMS AND BECAUSE A USER OR APPLICATION DESIGNER MAY USE NATIONAL INSTRUMENTS PRODUCTS IN COMBINATION WITH OTHER PRODUCTS IN A MANNER NOT EVALUATED OR CONTEMPLATED BY NATIONAL INSTRUMENTS, THE USER OR APPLICATION DESIGNER IS ULTIMATELY RESPONSIBLE FOR VERIFYING AND VALIDATING THE SUITABILITY OF NATIONAL INSTRUMENTS PRODUCTS WHENEVER NATIONAL INSTRUMENTS PRODUCTS ARE INCORPORATED IN A SYSTEM OR APPLICATION, INCLUDING, WITHOUT LIMITATION, THE APPROPRIATE DESIGN, PROCESS AND SAFETY LEVEL OF SUCH SYSTEM OR APPLICATION.

# **Compliance**

### **Electromagnetic Compatibility Guidelines**

This product was tested and complies with the regulatory requirements and limits for electromagnetic compatibility (EMC) as stated in the product specifications. These requirements and limits are designed to provide reasonable protection against harmful interference when the product is operated in its intended operational electromagnetic environment.

This product is intended for use in industrial locations. There is no guarantee that harmful interference will not occur in a particular installation, when the product is connected to a test object, or if the product is used in residential areas. To minimize the potential for the product to cause interference to radio and television reception or to experience unacceptable performance degradation, install and use this product in strict accordance with the instructions in the product documentation.

Furthermore, any changes or modifications to the product not expressly approved by National Instruments could void your authority to operate it under your local regulatory rules.

Caution To ensure the specified EMC performance, operate this product only with shielded cables and accessories.

**Caution** This product may become more sensitive to electromagnetic disturbances in the operational environment when test leads are attached or when connected to a test object.

**Caution** Emissions that exceed the regulatory requirements may occur when this product is connected to a test object.

# **Contents**

Chantar 1

| Gliapiei i                                                                          |     |

|-------------------------------------------------------------------------------------|-----|

| Getting Started                                                                     |     |

| Installing the Software                                                             | 1-1 |

| NI-DAQmx                                                                            |     |

| Other Software                                                                      | 1-2 |

| Example Programs                                                                    | 1-2 |

| Installing the Hardware                                                             |     |

| Device Pinouts                                                                      |     |

| Information Resources                                                               | 1-2 |

| Measurement System Overview                                                         | 1-3 |

| Sensors and Transducers                                                             | 1-3 |

| Dynamic Signal Acquisition Device Concepts  Nyquist Frequency and Nyquist Bandwidth |     |

| Noise                                                                               |     |

| Analog Input                                                                        |     |

| Analog Input Channel Configurations                                                 |     |

| Choosing Channel Configurations                                                     | 2-2 |

| Input Coupling                                                                      | 2-3 |

| TEDS (Transducer Electronic Data Sheet)                                             | 2-4 |

| IEPE                                                                                | 2-5 |

| Overload Detection                                                                  | 2-5 |

| ADC                                                                                 | 2-7 |

| Analog Input Filters                                                                | 2-7 |

| Anti-Alias Filters                                                                  | 27  |

Filter Delay ......2-10

Choosing Channel Configurations .......2-11

FIFO and PCI Data Transfer ......2-10

DAC 2-13

Analog Output Filters 2-13

Analog Output (NI USB-4431 and NI 4461 Only).....2-11

|            | FIFO and PCI Data Transfer                                | 2-16 |

|------------|-----------------------------------------------------------|------|

|            | Power Off and Power Loss                                  | 2-16 |

| Trigger    | ing                                                       | 2-17 |

|            | Digital Triggering                                        | 2-18 |

|            | Analog Triggering                                         | 2-18 |

|            | Analog Edge Triggering                                    |      |

|            | Analog Edge Triggering With Hysteresis                    |      |

|            | Window Triggering                                         |      |

|            | Triggering and Filter Delay                               |      |

|            | Filter Delay Removal                                      | 2-21 |

| Timing     | and Synchronization                                       |      |

| C          | Timing Signals                                            |      |

|            | Frequency Timebase                                        |      |

|            | Reference Clock                                           |      |

|            | Oversample Clock                                          | 2-22 |

|            | Sample Clock Timebase                                     |      |

|            | Sync Pulse                                                |      |

|            | Start Trigger                                             |      |

|            | Sample Rate and Update Rate, Accuracy and Coercion        |      |

|            | Calculating the Coerced Rate                              |      |

|            | Example of Calculating a Coerced Sample Rate              |      |

|            | Synchronization                                           |      |

|            | Reference Clock Synchronization (PXI/PXIe Only)           |      |

|            | Master Sample Clock Timebase Synchronization              |      |

| Chapter 3  | v 5                                                       |      |

| Developing | Your Dynamic Signal Acquisition Application               |      |

| Creating   | g a Task Using the DAQ Assistant                          | 3-1  |

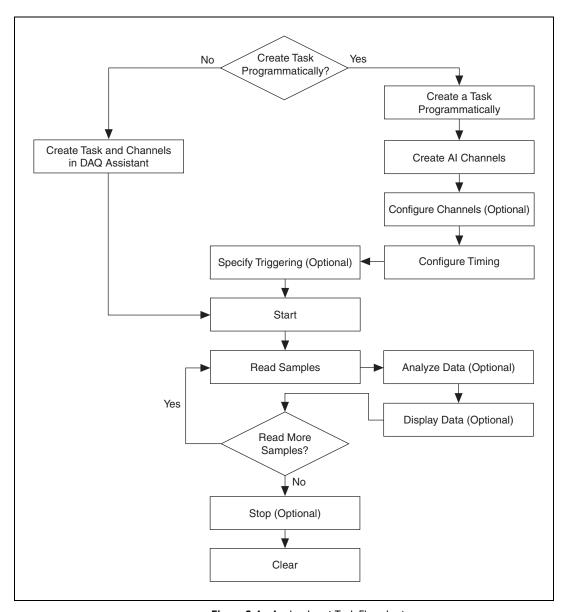

| Analog     | Input Applications                                        | 3-1  |

|            | Analog Input Application Overview                         | 3-1  |

|            | Analog Input Application Examples                         | 3-4  |

|            | LabVIEW Examples                                          | 3-4  |

|            | LabWindows/CVI Examples                                   | 3-4  |

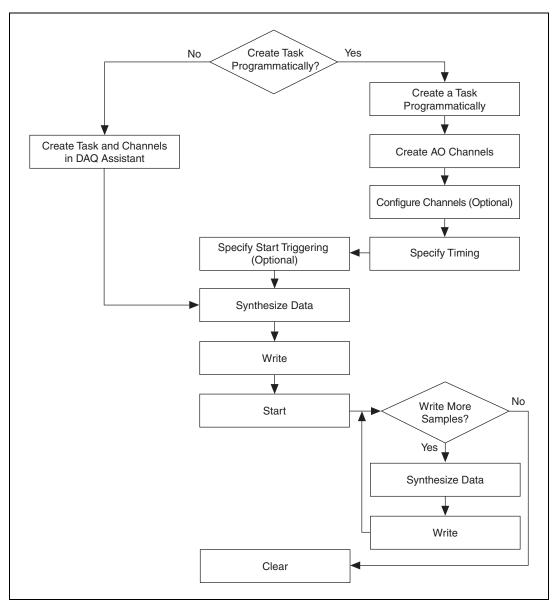

|            | Analog Output Applications (NI USB-4431 and NI 4461 Only) | 3-4  |

|            | Analog Output Application Overview                        | 3-4  |

|            | Analog Output Application Examples                        | 3-7  |

|            | LabVIEW Example                                           |      |

|            | LabWindows/CVI Example                                    |      |

| Synchro    | onization Applications                                    |      |

| ·          | Synchronization Application Overview                      |      |

|            | Synchronization Application Examples                      |      |

|            | LabVIEW Examples                                          |      |

|            | LabWindows/CVI Example                                    |      |

|            |                                                           |      |

# Appendix A Device-Specific Information

| NI 443x Devices                             | A-1  |

|---------------------------------------------|------|

| NI 443x Features                            | A-1  |

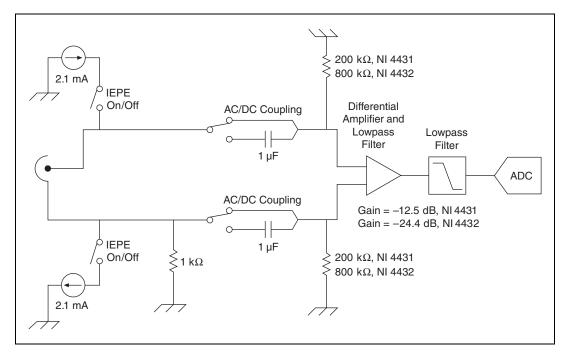

| NI 443x Analog Input Features               | A-2  |

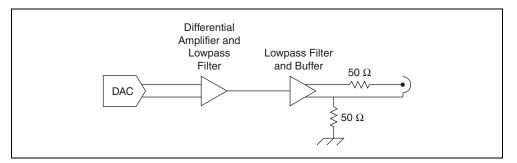

| NI 4431 Analog Output Features              |      |

| NI 443x Block Diagrams                      |      |

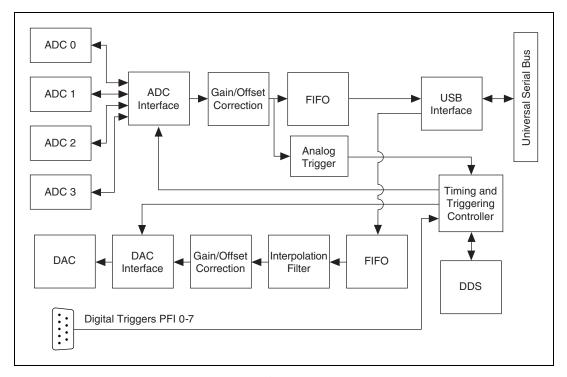

| NI 4431 Block Diagram                       |      |

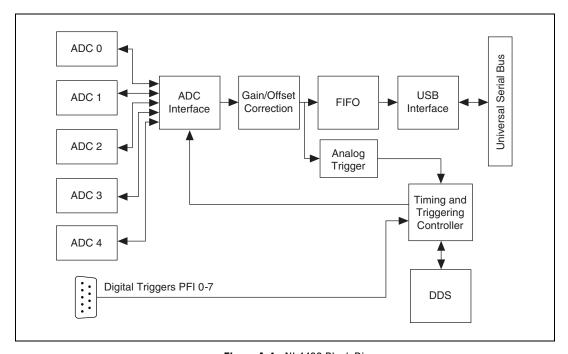

| NI 4432 Block Diagram                       | A-5  |

| Connecting Signals to NI 443x Devices       |      |

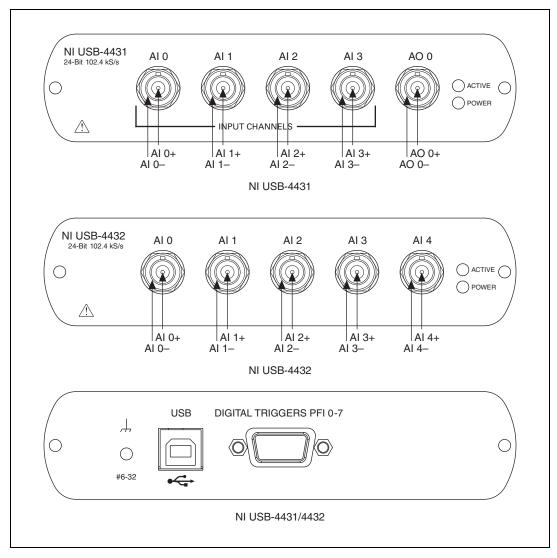

| NI 443x Front and Rear Panels               | A-6  |

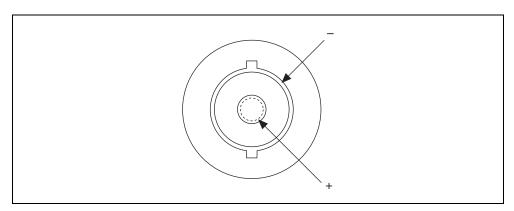

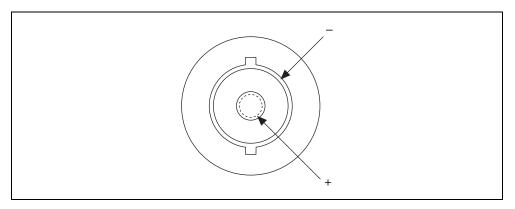

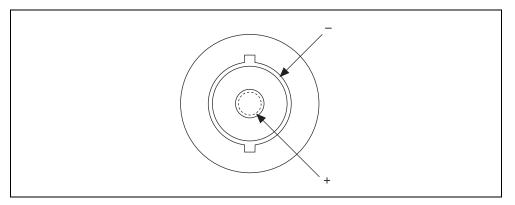

| BNC Connector Polarity                      | A-7  |

| NI 443x Anti-Aliasing Filter Response       | A-7  |

| NI 443x Specifications                      | A-9  |

| NI 446x Devices                             | A-9  |

| NI 446x Features                            | A-9  |

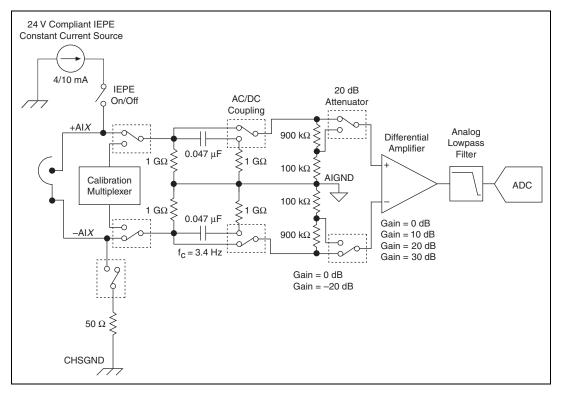

| NI 446x Analog Input Features               | A-10 |

| NI 4461 Analog Output Features              | A-11 |

| NI 446x Gain and Attenuation                | A-11 |

| NI 446x Block Diagrams                      | A-13 |

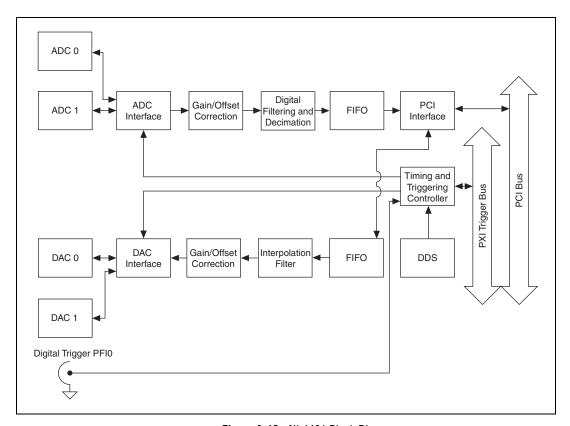

| NI 4461 Block Diagram                       | A-13 |

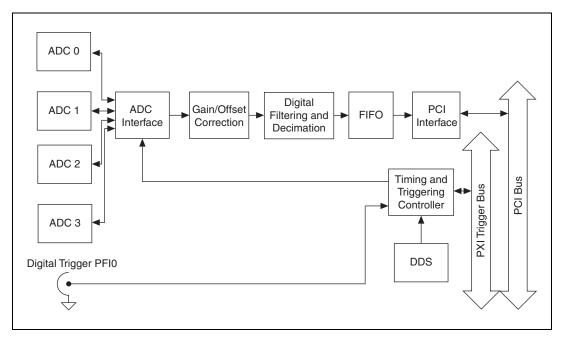

| NI 4462 Block Diagram                       | A-14 |

| Connecting Signals to NI 446x Devices       | A-15 |

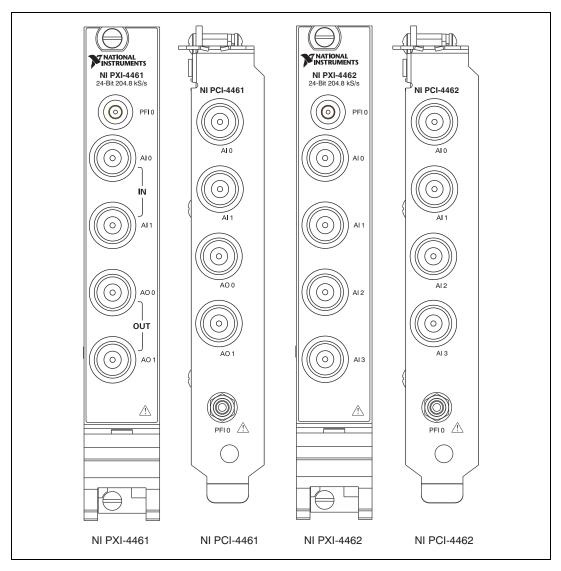

| NI 446x Front Panels                        | A-15 |

| BNC Connector Polarity                      | A-16 |

| NI 446x Input Connections                   | A-16 |

| NI 4461 Output Connections                  | A-17 |

| NI 446x Anti-Aliasing Filter Response       | A-18 |

| NI PXI-446x Reference Clock Synchronization |      |

| NI 446x Specifications                      | A-21 |

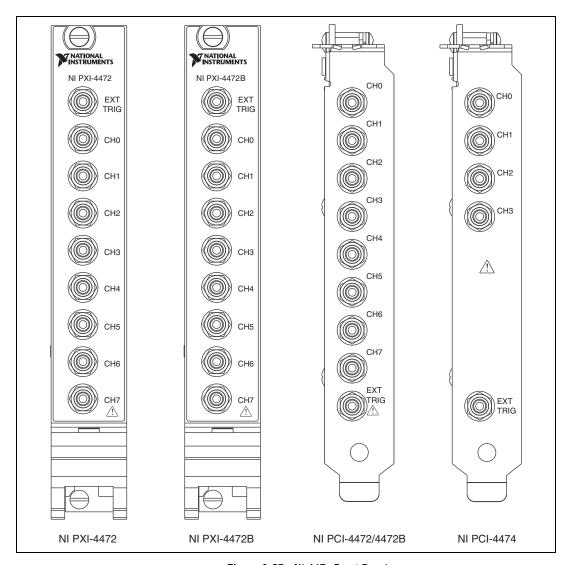

| NI 447x Devices                             | A-21 |

| NI 447x Features                            | A-21 |

| NI 447x Analog Input Features               | A-22 |

| NI 447x Block Diagram                       | A-23 |

| Connecting Signals to NI 447x Devices       |      |

| NI 447x Front Panels                        | A-24 |

| NI 447x Input Connections                   | A-25 |

| NI 447x Anti-Aliasing Filter Response       | A-26 |

| NI 447x Specifications                      | A-28 |

| NI 449x Devices                             |      |

| NI 449x Features                            | A-29 |

| NI 449x Analog Input Features               | A-30 |

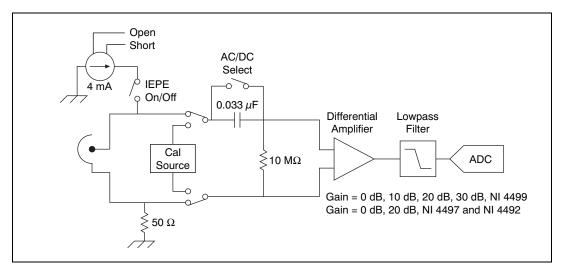

| NI 449x Block Diagram                       | A-32 |

| NI 44            | NI 449x Front Panels                                    | A-32<br>A-35<br>A-36 |

|------------------|---------------------------------------------------------|----------------------|

|                  | 49x Specifications                                      |                      |

|                  | VI 9234 Devices                                         |                      |

| 111 7255 dild 1  | 11 7234 Devices                                         | 11 37                |

| Appendix B       |                                                         |                      |

| • •              | ort and Professional Services                           |                      |

| recillical Suppo | iit aliu Fiviessiviiai seivives                         |                      |

| F:               |                                                         |                      |

| Figures          |                                                         |                      |

| Figure 2-1.      | NI 446x Harmonic Aliases                                |                      |

| Figure 2-2.      | Sampled Signal                                          |                      |

| Figure 2-3.      | Signal After Digital Filter                             |                      |

| Figure 2-4.      | Images After DAC Filter                                 |                      |

| Figure 2-5.      | Signal After DAC                                        |                      |

| Figure 2-6.      | Signal After Analog Filters                             |                      |

| Figure 2-7.      | Power Off and Power Loss Behavior                       |                      |

| Figure 2-8.      | Analog Trigger Level                                    |                      |

| Figure 2-9.      | Analog Edge Triggering with Hysteresis on Rising Slope  |                      |

| Figure 2-10.     | Analog Edge Triggering with Hysteresis on Falling Slope |                      |

| Figure 2-11.     | Window Triggering                                       | 2-20                 |

| F' 2 1           | Analysis I and Table 1 The silver                       | 2.2                  |

| Figure 3-1.      | Analog Input Task Flowchart                             |                      |

| Figure 3-2.      | NI USB-4431 and NI 4461 Analog Output Task Flowchart .  | 3-3                  |

| Figure A-1.      | NI 443x Analog Input Block Diagram                      | A-2                  |

| Figure A-2.      | NI 4431 Analog Output Block Diagram                     |                      |

| Figure A-3.      | NI 4431 Block Diagram                                   |                      |

| Figure A-4.      | NI 4432 Block Diagram                                   |                      |

| Figure A-5.      | NI 443 <i>x</i> Front and Rear Panels                   |                      |

| Figure A-6.      | BNC Connector Polarity for NI 443x Devices              |                      |

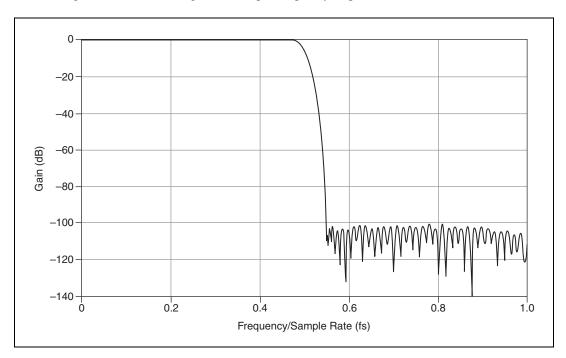

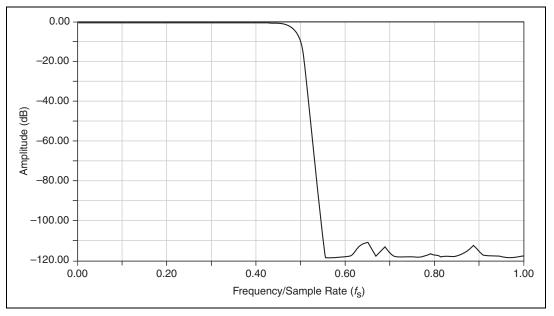

| Figure A-7.      | NI 443x Digital Filter Input Frequency Response         |                      |

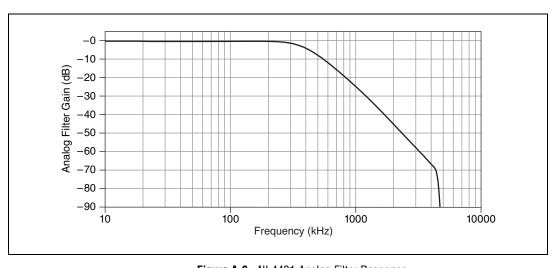

| Figure A-8.      | NI 4431 Analog Filter Response                          |                      |

| Figure A-9.      | NI 4432 Analog Filter Response                          |                      |

| Figure A-10.     | NI 446x Analog Input Block Diagram                      |                      |

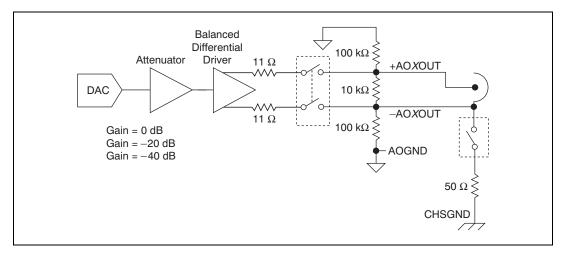

| Figure A-11.     | NI 4461 Analog Output Block Diagram                     |                      |

| Figure A-12.     | NI 4461 Block Diagram                                   |                      |

| Figure A-13.     | NI 4462 Block Diagram                                   |                      |

| Figure A-14.     | NI 446x Front Panels                                    |                      |

| Figure A-15.     | BNC Connector Polarity for NI 446x Devices              |                      |

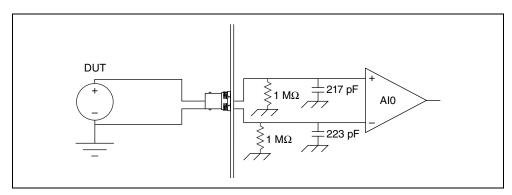

| Figure A-16.     | NI 446x Input Connection in Differential Mode           | A-16                 |

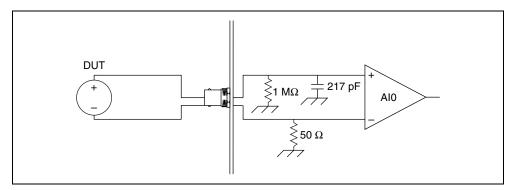

|       | Figure A-17. | NI 446x Terminal Configuration in Pseudodifferential Mode        | A-17 |

|-------|--------------|------------------------------------------------------------------|------|

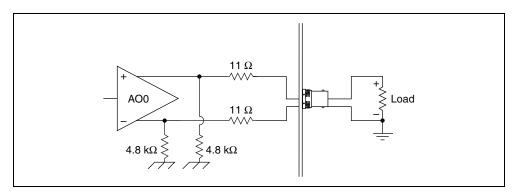

|       | Figure A-18. | NI 4461 Output Connection with Terminal Configuration in         |      |

|       |              | Differential Mode                                                | A-17 |

|       | Figure A-19. | NI 4461 Output Connection with Terminal Configuration in         |      |

|       |              | Pseudodifferential Mode                                          | A-18 |

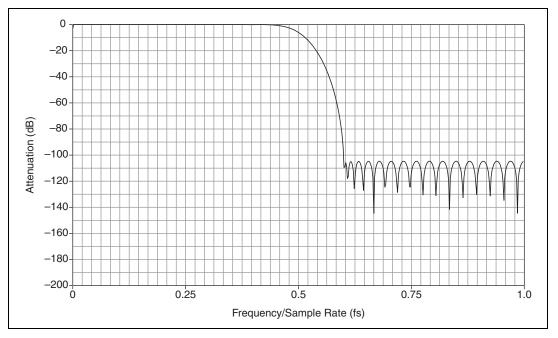

|       | Figure A-20. | NI 446x Digital Filter Input Frequency Response with             |      |

|       |              | Low-Frequency Alias Rejection Enabled                            | A-18 |

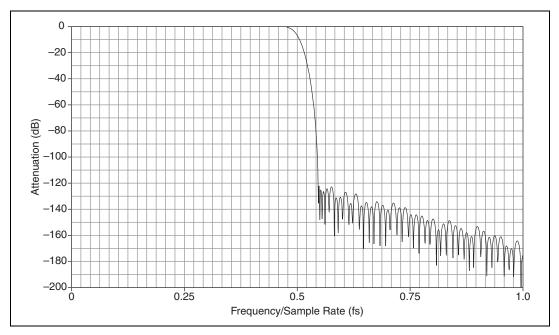

|       | Figure A-21. | NI 446x Digital Filter Input Frequency Response with             |      |

|       |              | Low-Frequency Alias Rejection Disabled                           | A-19 |

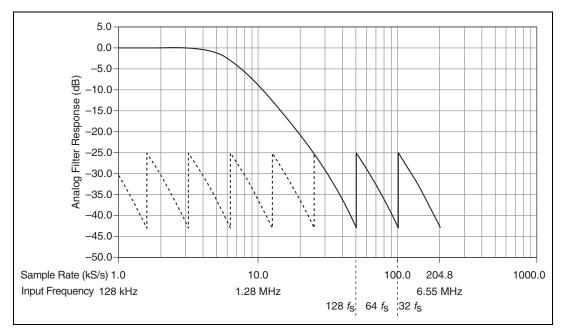

|       | Figure A-22. | NI 446x Analog Filter Response                                   | A-20 |

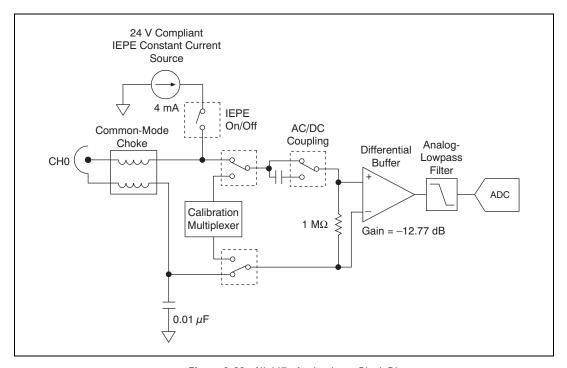

|       | Figure A-23. | NI 447x Analog Input Block Diagram                               | A-22 |

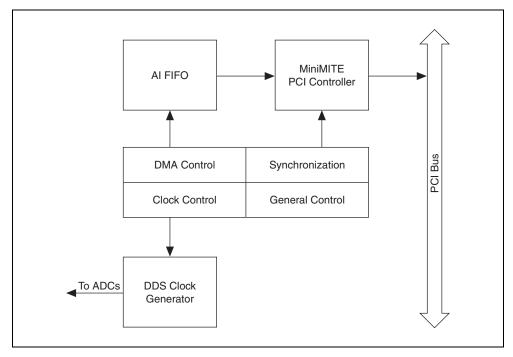

|       | Figure A-24. | NI 447x Digital Function Block Diagram                           | A-23 |

|       | Figure A-25. | NI 447x Front Panels                                             | A-24 |

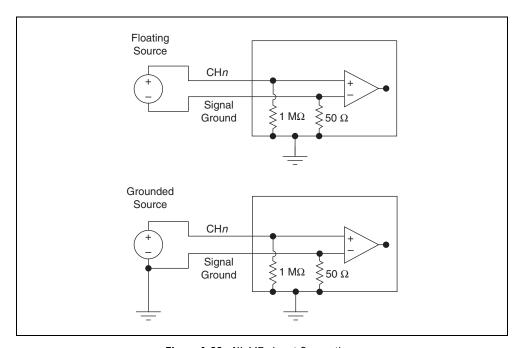

|       | Figure A-26. | NI 447x Input Connections                                        | A-25 |

|       | Figure A-27. | NI 447x Digital Filter Input Frequency Response                  | A-26 |

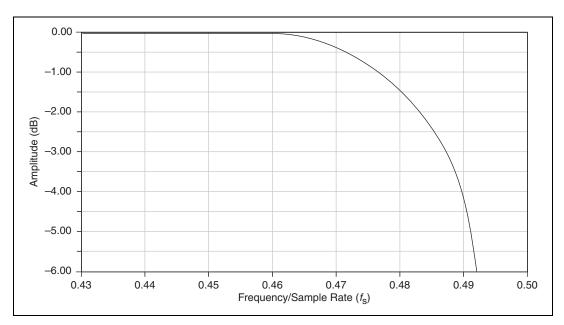

|       | Figure A-28. | NI 447x Digital Filter Frequency Response Near the Cut-off Point | A-27 |

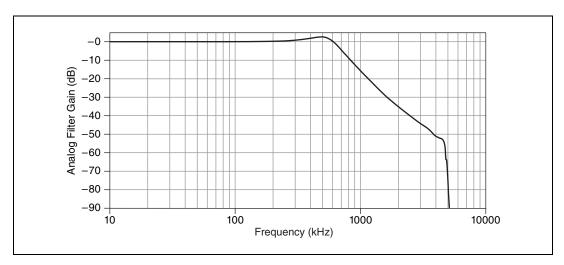

|       | Figure A-29. | NI 447x Analog Filter Response                                   |      |

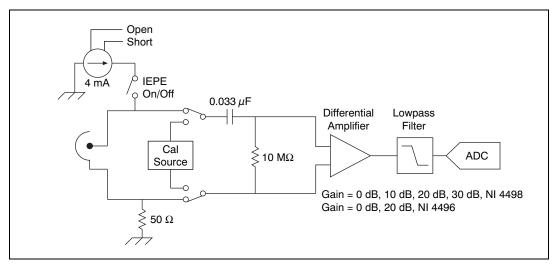

|       | Figure A-30. | NI 4499, NI 4497, and NI 4492 Analog Input Block Diagram         | A-30 |

|       | Figure A-31. | NI 4498 and NI 4496 Analog Input Block Diagram                   |      |

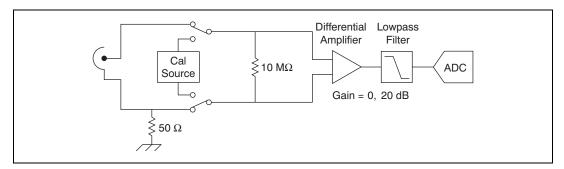

|       | Figure A-32. | NI 4495 Analog Input Block Diagram                               | A-31 |

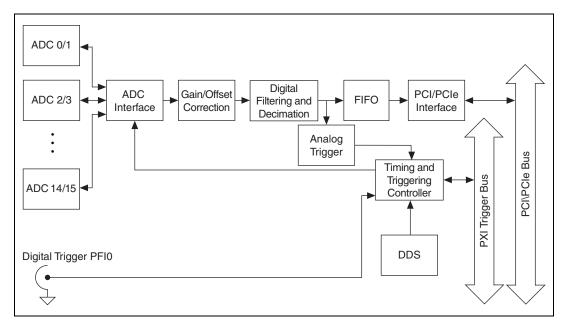

|       | Figure A-33. | NI 449x Block Diagram                                            | A-32 |

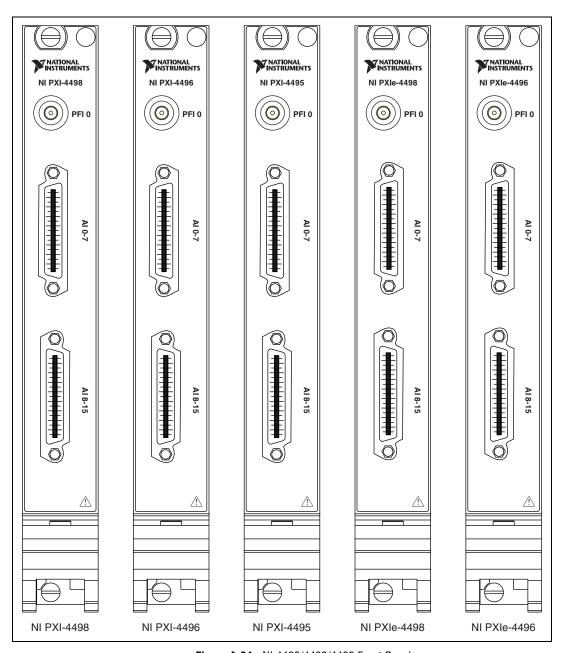

|       | Figure A-34. | NI 4498/4496/4495 Front Panels                                   | A-33 |

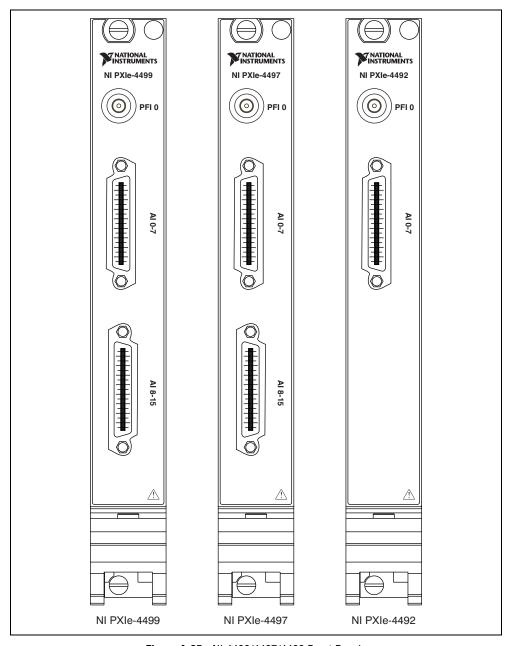

|       | Figure A-35. | NI 4499/4497/4492 Front Panels                                   | A-34 |

|       | Figure A-36. | BNC Connector Polarity for NI 449x Devices                       | A-35 |

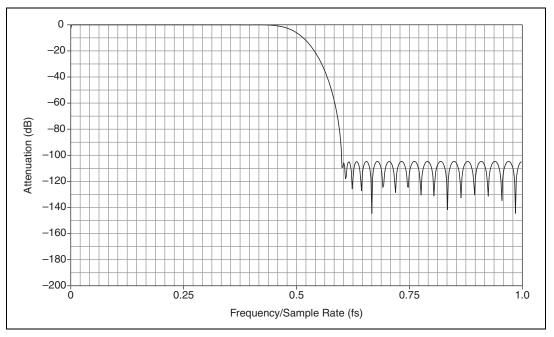

|       | Figure A-37. | NI 449x Digital Filter Input Frequency Response with             |      |

|       | _            | Low-Frequency Alias Rejection Enabled                            | A-36 |

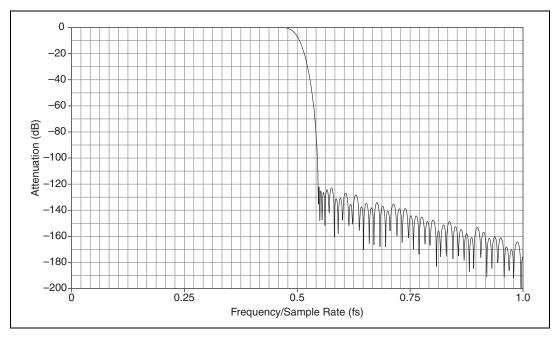

|       | Figure A-38. | NI 449x Digital Filter Input Frequency Response with             |      |

|       | _            | Low-Frequency Alias Rejection Disabled                           | A-37 |

|       | Figure A-39. | NI 449x Analog Filter Response                                   | A-38 |

|       |              |                                                                  |      |

| Table | es es        |                                                                  |      |

|       | Table 2-1.   | Analog Input                                                     | 2-3  |

|       | Table 2-2.   | Decimation Factors for Given Sample Rates                        | 2-9  |

|       | Table 2-3.   | Analog Output                                                    | 2-12 |

|       | Table 2-4.   | Output Impedance                                                 | 2-12 |

|       | Table 2-5.   | NI 4461 Interpolation Factor and Output Filter Delay             | 2-15 |

|       | Table 2-6.   | NI 4431 Interpolation Factor and Output Filter Delay             | 2-16 |

|       | Table 2-7.   | Rate Multipliers for NI 443x                                     | 2-25 |

|       | Table 2-8.   | Rate Multipliers for NI 446x                                     | 2-25 |

|       | Table 2-9.   | Rate Multipliers for NI 447 <i>x</i>                             |      |

|       | Table 2-10.  | Rate Multipliers for NI 449x                                     | 2-26 |

|       | Table 2-11.  | Clock Properties On DSA Devices                                  | 2-27 |

|       | Table 2-12.  | Coerced Sample and Update Rates on DSA Devices (kS/s)            | 2-28 |

| Table 2-13. | Supported DSA Device Synchronization Configuration | 2-31 |

|-------------|----------------------------------------------------|------|

| Table 3-1.  | Analog Input Application Steps                     | 3-3  |

| Table 3-2.  | Analog Output Application Steps                    | 3-6  |

| Table A-1.  | Gain Setting Sources                               | A-12 |

| Table A-2.  | NI 449x features                                   | A-29 |

**Getting Started**

This manual contains information about using National Instruments Dynamic Signal Acquisition (DSA) devices. These devices have 24-bit resolution and support sample rates of up to 204.8 kS/s. With excellent dynamic range, noise and distortion performance, and simultaneous sampling and synchronization capabilities, the DSA devices are well suited for many applications including, but not limited to:

- Audio testing

- Acoustic measurements

- Environmental noise testing

- Vibration analysis

- Noise, vibration, and harshness measurements

- Machine condition monitoring

- Rotating machinery evaluation

# **Installing the Software**

**Note** Before installing the DSA device, you must install the software you plan to use with the device.

#### NI-DA0mx

Software support for the NI Dynamic Signal Acquisition products is provided by NI-DAQmx. The *DAQ Getting Started* guides, which you can download at ni.com/manuals, offer step-by-step NI-DAQmx instructions for installing software and hardware, configuring channels and tasks, and getting started developing an application. For detailed NI software version support, refer to the NI-DAQmx readme.

#### **Other Software**

If you are using other software, refer to the installation instructions that accompany your software.

#### **Example Programs**

The NI-DAQmx media contains example programs that you can use to get started programming with the NI Dynamic Signal Acquisition devices. Refer to the *DAQ Getting Started* guide that shipped with your device, and is also accessible from **Start**\*All **Programs**\*National Instruments\*NI-DAQ, for more information.

## Installing the Hardware

The *DAQ Getting Started* guides contains general information about how to install DSA devices, accessories, and cables.

#### **Device Pinouts**

Refer to the *NI-DAQmx Help* for DSA device pinout information. Select **Start**»**All Programs**»**National Instruments**»**NI-DAQ**»**NI-DAQmx Help**.

#### **Information Resources**

Refer to ni.com/manuals for the most recent documentation.

The following documentation might be useful when using NI Dynamic Signal Acquisition devices:

- The NI USB-443x Specifications contains all specifications for the NI USB-4431 and NI USB-4432 devices.

- The *NI 446x Specifications* contains all specifications for the NI PCI-4461, NI PXI-4461, NI PCI-4462, and NI PXI-4462 devices.

- The NI 447x Specifications contains all specifications for the NI PCI-4472, NI PXI-4472, NI PCI-4474, NI PCI-4472B, and NI PXI-4472B devices.

- The NI 449x Specifications contains all specifications for the NI PXIe-4492, NI PXI-4495, NI PXI/PXIe-4496, NI PXIe-4497, NI PXI/PXIe-4498, and NI PXIe-4499 devices.

# **Measurement System Overview**

A measurement system can consist of several components. Refer to the *DAQ Getting Started* guides for a measurement system overview of measurement applications.

#### **Sensors and Transducers**

A sensor or transducer is a device that outputs an electrical signal in response to a measured physical phenomenon such as pressure or temperature. The most common sensors for use with DSA devices include microphones for measuring sound pressure and accelerometers for measuring linear acceleration or vibration.

Refer to Chapter 2, *Dynamic Signal Acquisition Device Concepts*, for more information about typical DSA device measurements. You also can refer to the *NI-DAQmx Help* or the *LabVIEW Help* for more information about microphones, accelerometers, eddy current proximity probe sensors, or piezoelectric force sensors.

# Dynamic Signal Acquisition Device Concepts

This chapter contains information about Dynamic Signal Acquisition (DSA) device concepts, including Nyquist frequency and bandwidth, noise, analog input and output, timing and triggering, and synchronization.

# **Nyquist Frequency and Nyquist Bandwidth**

Any sampling system, such as an ADC, is limited in the bandwidth of the signals it can measure. Specifically, a sampling rate of  $f_s$  can represent only signals with frequencies lower than  $f_s/2$ . This maximum frequency is known as the *Nyquist frequency*. The bandwidth from 0 Hz to the Nyquist frequency is the *Nyquist bandwidth*.

#### Noise

**Caution** Electromagnetic interference can adversely affect the measurement accuracy of the DSA products described in this document. The inputs and outputs of these products are not connected to chassis ground for functional reasons. Therefore, the outer conductor of any connected coaxial cable is not connected to chassis ground and the outer conductor will not act as a shield for unwanted noise. The shield can act as an antenna to transmit noise into the environment or receive noise from the environment that could affect measurement accuracy. To ensure proper shielding effectiveness of connected coaxial cables, the outer conductor must be directly connected to chassis or earth ground at the load end of the cable. In addition, snap-on ferrite beads or other remedial measures may be required to prevent unwanted emissions or immunity. Refer to the specifications of your product for more information about EMC performance.

DSA devices typically have a dynamic range of more than 110 dB. Several factors can degrade the noise performance of input channels, such as noise picked up from nearby electronic devices. DSA devices work best when kept as far away as possible from other plug-in devices, power supplies, disk drives, and computer monitors. Cabling is also critical. Use well-shielded coaxial or floating cables for all connections. Route the cables away from sources of interference such as computer monitors, switching power supplies, and fluorescent lights. Physical motion or deformation can induce noise on sensitive analog cables. Use a

transducer with a low output impedance to minimize system susceptibility to external noise sources and crosstalk.

You can reduce the effects of noise on your measurements by carefully choosing the sample rate to maximize the effectiveness of the anti-alias filtering. Computer monitor noise, for example, typically occurs at frequencies between 15 kHz and 65 kHz. If the signal of interest is restricted to below 10 kHz, for example, the anti-alias filters reject the monitor noise outside the frequency band of interest, and a sampling rate of at least 21.6 kS/s guarantees that any signal components in the 10 kHz bandwidth of interest are acquired without aliasing and without being attenuated by the digital filter. Refer to the *Analog Input Filters* section of this chapter for more information about anti-alias filtering.

When possible, use the differential configuration to minimize the effect of any noise produced by ground currents in the chassis and common-mode noise. If you have particularly noisy AC power, consider external filtering, such as a line conditioner or an uninterruptible power supply.

## **Analog Input**

#### **Analog Input Channel Configurations**

The NI 446x supports two terminal configurations for analog input: differential and pseudodifferential. The NI USB-443x, NI 447x and NI 449x support only the pseudodifferential channel configuration. The term pseudodifferential refers to the 50  $\Omega$  or 1 k $\Omega$  resistance between the outer connector shell and chassis ground.

**Note** Attach PXI/PXIe and PCI devices to the chassis with screws to provide a reliable ground connection. If you use a PXI/PXIe device, tighten the screws at the top and bottom of the front face of the device. If you use a PCI device, keep the screw that held the PCI slot cover to the computer chassis. Reinsert this screw to securely attach the device. For USB-443x devices, connect the ground terminal on the back of the USB case to the chassis of the host PC.

#### **Choosing Channel Configurations**

If the signal source is floating, use the pseudodifferential configuration. The pseudodifferential configuration provides a ground reference between the floating source and the DSA device by connecting either a 50  $\Omega$  or 1 k $\Omega$  resistor (depending on the DSA device) from the negative input to ground. Without this, the floating source can drift outside of the common-mode range of the DSA device being used.

If the signal source is grounded or ground referenced, both the pseudodifferential and differential input configurations are acceptable. However, the differential input configuration is preferred, since using the pseudodifferential input configuration on a grounded signal

source creates more than one ground-reference point. This condition may allow ground loop currents, which can introduce errors or noise into the measurement. The  $50~\Omega$  or  $1~k\Omega$  resistor between the negative input and ground is usually sufficient to reduce these errors to negligible levels, but results can vary depending on your system setup.

Configure the channels based on the signal source reference or DUT configuration. Refer to Table 2-1 to determine how to configure the channel.

Source Reference

Channel Configuration

Floating

Pseudodifferential

Grounded

Differential or pseudodifferential

Table 2-1. Analog Input

The NI 446x is automatically configured for differential mode when powered on.

#### **Input Coupling**

You can configure the NI USB-443x, NI 446x, NI 447x, and a subset of the NI 449x devices for either AC or DC coupling with the AI.Coupling property. If you select DC coupling, any DC offset present in the source signal is passed to the ADC. The DC-coupling configuration is usually best if the signal source has only small amounts of offset voltage or if the DC content of the acquired signal is important. If the source has a significant amount of unwanted offset, select AC coupling to take full advantage of the input dynamic range.

**Note** The NI 4496 and NI 4498 provide AC coupling only. The NI 4495 provides DC coupling only. The NI 4492, NI 4497, and NI 4499 provide selectable AC/DC coupling.

Selecting AC coupling enables a highpass resistor-capacitor (RC) filter into the signal conditioning path. The filter time constant is 47 ms for the NI 446x, NI 4472, and NI PCI-4474. The highpass RC filter settles to 0.5% accuracy in 0.25 s in response to a step input. It takes 0.782 s to settle to 24-bit accuracy in response to a step input. The settling time is somewhat dependent on the DUT impedance as well.

The NI 4472B and NI 449x have a larger time constant (330 ms). It takes 5.5 s to settle to 24-bit accuracy in response to a step input.

**Note** NI-DAQmx does not compensate for the settling time introduced by the RC filter when switching from DC to AC coupling. To compensate for the filter settling time, you can discard the samples taken during the settling time or force a delay before you restart the measurement. You must force the delay after the AI task is committed, but before the task starts.

Using AC coupling results in an attenuation of the low-frequency response of the AI circuitry. Refer to the *NI USB-443x Specifications*, *NI 446x Specifications*, *NI 447x Specifications*, and *NI 449x Specifications* for information about the cut-off frequency for each device.

#### **TEDS (Transducer Electronic Data Sheet)**

TEDS-capable sensors carry a built-in, self-identification EEPROM that stores a table of parameters and sensor information. TEDS sensors have two modes of operation: an analog mode that allows the sensors to operate as transducers measuring physical phenomena, and a digital mode that allows you to write and read information to and from the TEDS. The NI USB-443x, NI PCI-4461, NI PXI-4461 (Revision M or later), NI 4462, and NI 449x support modes for Class I TEDS sensors without any additional hardware<sup>1</sup>. The NI 447x devices require an accessory, such as the BNC-2096, to allow digital communication with the EEPROM on Class I TEDS sensors.

TEDS contains information about the sensor such as calibration, sensitivity, and manufacturer information. This information is accessible in Measurement & Automation Explorer (MAX), VIs in LabVIEW, or by calling the equivalent function calls in a text-based ADE.

Refer to the following installed help files for more information about TEDS:

- Measurement & Automation Explorer Help for NI-DAQmx—Contains information about configuring and testing data acquisition (DAQ) devices, RT Series DAQ devices, SCXI devices, SCC devices, TEDS carriers, and RTSI cables using MAX for NI-DAQmx, and special considerations for operating systems. Select Help»Help Topics»NI-DAQmx» MAX Help for NI-DAQmx in MAX.

- NI-DAQmx Help—Contains general information about measurement concepts, key NI-DAQmx concepts, and common applications that are applicable to all programming environments. Select Start»All Programs»National Instruments»NI-DAQ» NI-DAQmx Help.

- LabVIEW Help—Contains information about LabVIEW programming concepts, step-by-step instructions for using LabVIEW, and reference information about LabVIEW VIs, functions, palettes, menus, and tools.

You also can refer to the following pages on ni.com for more information. Go to ni.com/info and enter the Info Code.

- Smart Sensors—Info Code rdsenr

- What Are Plug & Play Sensors?—Info Code rdpnpy

- IEEE 1451.4 Sensor Templates Overview—Info Code rdted6

<sup>&</sup>lt;sup>1</sup> The NI 4495 does not support TEDS.

#### **IEPE**

If you attach an *IEPE* accelerometer or microphone that requires excitation to an AI channel of the DSA device, you must enable the IEPE excitation circuitry for that channel to generate the required excitation current. You can independently configure IEPE signal conditioning on a per channel basis on all DSA devices.

A DC voltage offset is generated equal to the product of the excitation current and sensor impedance when IEPE signal conditioning is enabled. To remove the unwanted offset, enable AC coupling. DC coupling can be used with IEPE excitation enabled without a loss of signal integrity only if the offset plus the peak of the AC signal of interest does not exceed the voltage range of the channel.

Common IEPE excitation values are 2.1 mA, 4 mA, and 10 mA. Refer to the *NI USB-443x Specifications*, *NI 446x Specifications*, *NI 447x Specifications*, and *NI 449x Specifications* for a list of supported IEPE current values for each device.

**Note** You must set the NI 446x inputs to pseudodifferential mode when IEPE is activated.

#### **Overload Detection**

When the signal voltage exceeds the input range, distortion caused by a clipped or overranged waveform can occur. The NI 446x devices include overload detection in both the analog domain (predigitization) and digital domain (postdigitization). The NI USB-443x, NI 447x, and NI 449x devices support digital domain overload detection. Use the OverloadedChansExist and OverloadedChans properties to access the overload detection feature.

An analog overrange can occur independently from a digital overrange, and vice versa. For example, an IEPE accelerometer might have a resonant frequency that, when stimulated, can produce an overrange in the analog signal. However, because the ADC delta-sigma technology uses very sharp anti-aliasing filters, the overrange is not passed into the digitized signal.

Conversely, a sharp transient on the analog side might not overrange, but the step response of the delta-sigma anti-aliasing filters might produce clipping in the digital data. The NI 446*x* analog overload detection circuitry detects a clipped or overloaded condition. You can programmatically poll the overload detection circuitry on a per channel basis to monitor for an overload condition. If an overload is detected, consider any data acquired at that time corrupt.

DSA devices perform digital overload detection as a percentage of the range. The overload detection occurs before the device applies gain and offset corrections. Detecting the overload before the gain and offset corrections catches an overflow condition in the delta-sigma modulator or ADC filter.

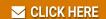

For instance, on NI 446x DSA devices, the analog overload point for the 0 dB gain range is approximately 10.7 V<sub>pk</sub>. This is the voltage at which the front-end circuitry begins showing signs of saturation. Figure 2-1 shows harmonic aliases caused by clipping with a 1.0 kHz sine wave at 10.8  $V_{pk}$ , versus the same signal at 8.9  $V_{pk}$ , which shows no clipping, on an NI 446x device. NI USB-443x, NI 447x, and NI 449x devices display similar behavior.

Figure 2-1. NI 446x Harmonic Aliases

**Caution** For NI 446x devices, overload detection is not supported for the  $\pm 42.4~V_{pk}$  input range setting. This setting attenuates the signal by a factor of 10. This attenuation factor implies that the ADC reaches the analog saturation point at 115  $V_{pk}$ . This level is greater than what the  $\pm 42.4~V_{pk}$  range can safely support. You risk damaging the input circuitry when measuring voltages capable of producing an overload condition when you use the  $\pm 42.4~V_{pk}$  range (–20 dB gain) setting.

Chapter 2

#### **ADC**

Each ADC in a DSA device uses a conversion method known as delta-sigma modulation. If the desired data rate is 51.2 kS/s, each ADC actually samples its input signal at 6.5536 MS/s, 128 times the data rate (or depending on the device and mode, it could be 256 times the data rate or another power of 2 multiple of the data rate), producing 1-bit samples that are sent to a digital filter. This filter rejects signal components greater than the Nyquist frequency of 25.6 kHz. The 1-bit, 6.5536 MS/s data stream from the ADC contains all of the information necessary to produce 24-bit samples at 51.2 kS/s. The delta-sigma ADC achieves this conversion from high speed to high resolution with a technique called noise shaping. The ADC adds random noise to the signal so that the resulting quantization noise, although large, is restricted to frequencies above the Nyquist frequency, 25.6 kHz in this case. This noise is not correlated with the input signal and is almost completely rejected by the digital filter.

The resulting output of the filter is a band-limited signal with a large dynamic range. One of the advantages of a delta-sigma ADC is that it uses a 1-bit DAC as an internal reference. As a result, the delta-sigma ADC is free from the differential nonlinearity (DNL) and associated noise inherent in high-resolution ADCs using other conversion techniques.

#### **Analog Input Filters**

#### **Anti-Alias Filters**

A digitizer or ADC might sample signals containing frequency components above the Nyquist limit. The undesirable effect of the digitizer modulating out-of-band components into the Nyquist bandwidth is aliasing. The greatest danger of aliasing is that you cannot determine whether aliasing occurred by looking at the ADC output. If an input signal contains several frequency components or harmonics, some of these components might be represented correctly while others contain aliased artifacts.

Lowpass filtering to eliminate components above the Nyquist frequency either before or during the digitization process can guarantee that the digitized data set is free of aliased components. DSA devices employ both digital and analog lowpass filters to achieve this protection.

The delta-sigma ADCs on DSA devices include an oversampled architecture and sharp digital filters with cut-off frequencies that track the sampling rate. Thus, the filter automatically adjusts to follow the Nyquist frequency. Although the digital filter eliminates almost all

out-of-band components, it is still susceptible to aliases from certain narrow frequency bands, defined by the following rules:

- When you select a sample rate greater than 102.4 kS/s and less than or equal to 204.8 kS/s, the susceptible areas are centered around 32, 64, 96, and other multiples of  $32 f_s$  (NI 446x and NI 449x only, because only the NI 446x and NI 449x devices support sample rates higher than 102.4 kS/s).

- When you select a sample rate greater than 51.2 kS/s and less than or equal to 102.4 kS/s, the susceptible areas are centered around 64, 128, 192, and other multiples of  $64 f_s$ .

- When you select a sample rate greater than or equal to the minimum rate for the specific DSA device and less than or equal to 51.2 kS/s, the susceptible areas are centered around 128, 256, 384 and other multiples of 128 f<sub>s</sub>.

**Note** On the NI USB-443x the susceptible areas are at multiples of 64  $f_s$  regardless of the sample rate.

The susceptible frequency band is always one  $f_s$  wide. For example, if  $f_s = 10,000$  S/s, the digital filter can admit aliases from analog components between 1.275 MHz and 1.285 MHz.

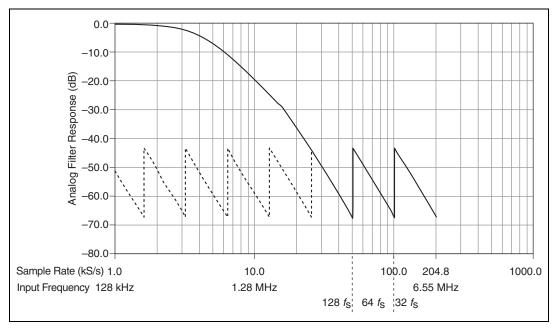

In addition to the ADC built-in digital filtering, DSA devices feature a fixed-frequency analog filter. The analog filter removes high-frequency components in the analog signal path before they reach the ADC. This filtering addresses the possibility of high-frequency aliasing from the narrow bands that are not covered by the digital filter. Each input channel on a DSA device is equipped with a multiple pole lowpass analog filter.

While the frequency response of the digital filter directly scales with the sample rate, the analog filter –3 dB point is fixed. The analog filter response produces good high-frequency alias rejection while maintaining a flat in-band frequency response. Because the analog filters are not high-order systems, the filter roll-off is not extremely sharp. The filter provides effective alias rejection at higher sampling rates, where only very high frequencies in the previously mentioned susceptible areas can pass through the digital filter. Some DSA devices support enhanced low-frequency alias rejection. The NI USB-443x, NI 446x, NI 447x, and NI 449x devices have different filter response curves that are available in Appendix A, *Device-Specific Information*.

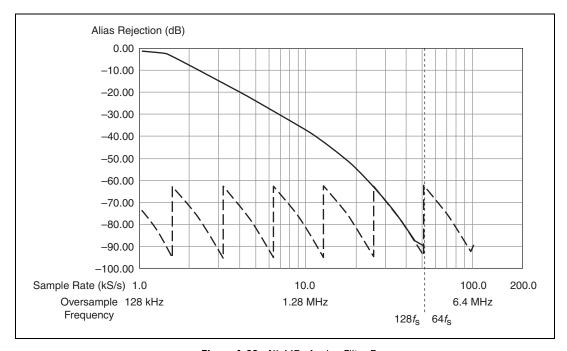

#### **Low-Frequency Alias Rejection**

At very low sample rates, between the minimum rate for the specific DSA device and 25.6 kS/s, the anti-aliasing filters of DSA device AI channels might not completely reject all out-of-band signals. The internal digital filter of the delta-sigma ADC cannot suppress signals with frequencies near the multiples of the oversample rate (sample rate multiplied by oversample factor). DSA devices also employ fixed cutoff analog lowpass anti-aliasing filters. At low sample rates, some multiples of the oversample rate can fall below the analog anti-aliasing filter cut-off frequency.

For example, for a device using ADCs with an oversample factor of  $128 f_s$  and sampling at a rate of 1 kS/s, the oversample rate is 128 kHz. Some multiples of that oversample rate fall below the cut-off frequency of the analog anti-aliasing filter. If the signal contains energy near these frequencies, aliasing can result.

You can minimize aliasing by raising the sample rate so that the first  $128\,f_s$  multiple falls above the cut-off frequency of the analog anti-aliasing filter. For example, a sample rate of 25.6 kS/s is not subject to substantial aliasing because the first  $128\,f_s$  multiple, 3.2 MHz, is well above the analog anti-aliasing filter cut-off frequency. You can also enable low-frequency alias rejection with the AI.EnhancedAliasRejectionEnable property. This property causes the DSA device to automatically oversample for sample rates between 1 kS/s and 25.6 kS/s. The resulting oversampled rate always falls in the 25.6 kS/s to 51.2 kS/s range. The data stream is then decimated down by the same multiple to produce samples at the specified sample rate. Low-frequency alias rejection improves alias rejection near multiples of the oversample rate. This comes at the expense of alias rejection at other frequencies. For example, when sampling at 1 kS/s on the NI 446x, a 2 kHz tone is not close to a multiple of the oversample rate. The tone is attenuated by more than 120 dB. With low-frequency alias rejection enabled, the tone is only attenuated by 104 dB.

Table 2-2 lists the decimation factors for given sample rates. Refer to the *NI-DAQmx Help* or the *LabVIEW Help* for more information about the AI.EnhancedAliasRejectionEnable property.

Sample Rate **Decimation Factor** 256\* $100 \text{ S/s} \le f_s \le 200 \text{ S/s}$  $200 \text{ S/s} < f_s \le 400 \text{ S/s}$ 128\* 64\*  $400 \text{ S/s} < f_s \le 800 \text{ S/s}$  $800 \text{ S/s} < f_s \le 1.6 \text{ kS/s}$ 32  $1.6 \text{ kS/s} < f_s \le 3.2 \text{ kS/s}$ 16  $3.2 \text{ kS/s} < f_s \le 6.4 \text{ kS/s}$ 8  $6.4 \text{ kS/s} < f_s \le 12.8 \text{ kS/s}$ 4  $12.8 \text{ kS/s} < f_s \le 25.6 \text{ kS/s}$ 2 \* These decimation factors apply only to NI 449x devices.

**Table 2-2.** Decimation Factors for Given Sample Rates

Not all DSA devices support low-frequency alias rejection. The following list provides more information about devices that support low-frequency alias rejection:

- NI 446x devices

- NI PXI-447x devices revision H and later

- NI PCI-447x devices revision F and later

- NI 449x devices

**Note** The AI.EnhancedAliasRejectionEnable property is enabled by default for NI 446x and disabled for NI 447x and NI 449x (for rates above 1 kS/s) devices.

#### **Filter Delay**

The filter delay is the time required for data to propagate through a converter. All DSA device channels have filter delays due to the presence of filter circuitry on both input and output channels. To understand how filter delay can affect your measurement, consider an ADC digital filter with a delay of 63 sample clock samples. At a 10 kS/s sample rate the signal experiences a delay equal to 6.3 ms.

The filter delay is an important factor for stimulus-response measurements, control applications, or any application where loop time is critical. Use the fastest allowable sample rate to minimize the effects of filter delay.

The input filter delay also makes an external digital trigger appear to occur earlier than expected. When acquiring from an ADC with a filter delay of 63 samples, and using a digital trigger to begin the acquisition, the first 63 samples of acquired data will have occurred before the digital trigger.

The NI 449x products support the AI.RemoveFilterDelay property. When enabled, the acquired data is automatically adjusted such that the first acquired sample is in line with the digital trigger. For more information, refer to the *Filter Delay Removal* section of this chapter.

Refer to the *NI USB-443x Specifications*, *NI 446x Specifications*, *NI 447x Specifications*, and *NI 449x Specifications* for information about filter delay for each device.

#### FIFO and PCI Data Transfer

DSA device input channels share a FIFO buffer, and the output channels share a separate FIFO buffer. The *NI USB-443x Specifications*, *NI 446x Specifications*, *NI 447x Specifications*, and *NI 449x Specifications* contain information about the buffer sample depth.

The devices have a flexible data transfer request condition. You can program the device to request DMA transfers according to a programmable FIFO condition. Refer to the *NI-DAQmx Help* or the *LabVIEW Help* for information about conditions available for specific devices.

**Note** USB devices do *not* allow setting the transfer request condition.

# Analog Output (NI USB-4431 and NI 4461 Only)

#### **Output Distortion**

You can minimize output distortion by connecting the outputs to external devices with a high input impedance. Each output channel of the NI 4461 is rated to drive a minimal load of 600  $\Omega$ . Each output channel of the NI USB-4431 is rated to drive a minimal load of 1 k $\Omega$ . However, you can achieve optimal performance with larger load resistances such as 10 k $\Omega$  or 100 k $\Omega$ . Refer to the *NI USB-443x Specifications* and *NI 446x Specifications* for more information.

#### **Analog Output Channel Configurations**

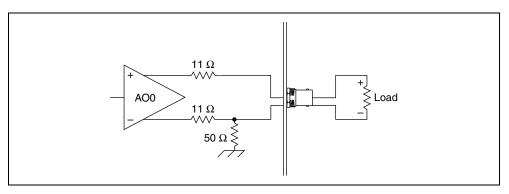

The NI 4461 supports two terminal configurations for analog output: differential and pseudodifferential. The term pseudodifferential refers to the fact that there is a 50  $\Omega$  resistor between the outer connector shell and chassis ground. The NI USB-4431 only supports pseudodifferential.

**Note** Attach PXI/PXIe, and PCI devices to the chassis with screws to provide a reliable ground connection. If you are using a PXI/PXIe device, be sure to tighten the screws at the top and bottom of the front face of the device. If you are using a PCI device, keep the screw that held the PCI slot cover to the computer chassis. Reinsert this screw to securely attach the device. For USB-4431 devices, connect the ground terminal on the back of the USB case to the chassis of the host PC.

#### **Choosing Channel Configurations**

If the DUT inputs are floating, use either the pseudodifferential or differential configuration.

If the DUT inputs are grounded or ground referenced, use the differential configuration. Using the pseudodifferential output configuration on a grounded DUT creates more than one ground-reference point. This condition may allow ground loop currents which can introduce errors or noise into the measurement. The 50  $\Omega$  or 1  $k\Omega$  resistor between the negative input and ground is usually sufficient to reduce these errors to negligible levels, but results can vary depending on your system setup.

Configure the channels based on the signal source reference or DUT configuration. Refer to Table 2-3 to determine how to configure the channel.

Table 2-3. Analog Output

| DUT Input Reference | Channel Configuration              |

|---------------------|------------------------------------|

| Floating            | Pseudodifferential or Differential |

| Grounded            | Differential                       |

The NI 446x is automatically configured for differential mode when powered on or powered off. This configuration protects the 50  $\Omega$  resistor on the negative pin.

#### **Output Impedance**

#### NI 4461

The differential output impedance between positive and negative signal legs is approximately 22  $\Omega$  when you generate a waveform. When you are not generating a waveform, configure the AO.IdleOutputBehavior property for one of the idle behavior options listed in Table 2-4.

Table 2-4. Output Impedance

| Idle Behavior Option    | Output Impedance<br>(Differential Mode Only) |

|-------------------------|----------------------------------------------|

| Maintain Existing Value | 22 Ω                                         |

| Zero Volts              | 22 Ω                                         |

| High Impedance          | 9 kΩ                                         |

#### NI USB-4431

The differential output impedance between positive and negative signal legs is approximately 50  $\Omega$ . There is no high impedance idle output channel configuration for the NI USB-4431. However the output can be configured to maintain its existing value when idle or return to zero when idle.

The delta-sigma DACs on the NI 4461 and NI USB-4431 function in a way analogous to delta-sigma ADCs. The digital data first passes through a digital interpolation filter, then to the DAC resampling filter, and finally to the delta-sigma modulator.

Chapter 2

In the DAC, the delta-sigma modulator converts high-resolution digital data to high-rate, 1-bit digital data. As in the ADC, the modulator frequency shapes the quantization noise so that almost all of the quantization noise energy is above the Nyquist frequency.

The digital 1-bit data is then passed to an inherently linear 1-bit DAC. The output of the DAC includes quantization noise at higher frequencies, and some images still remain near multiples of eight times the effective sample rate.

#### **Analog Output Filters**

#### **Anti-Imaging and Interpolation Filters**

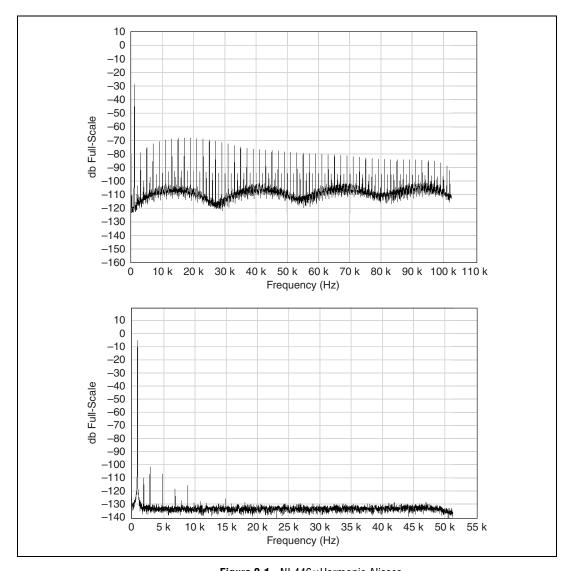

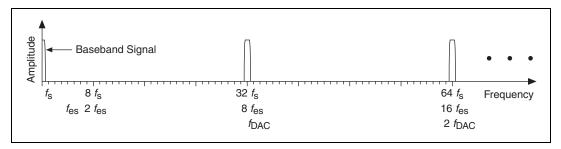

A sampled signal repeats itself throughout the frequency spectrum, as shown in Figure 2-2. This figure shows how the signal repetitions begin above one-half the sample rate,  $f_s$ , and, theoretically, continue up through the spectrum to infinity. Images remain in the sampled data because the data actually represents only the frequency components below one-half  $f_s$  (the baseband). The device filters out the extra images in the signal in three stages.

Figure 2-2. Sampled Signal

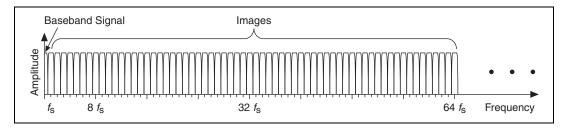

First, the data is digitally interpolated by a factor of  $2^n$ , where n is a positive integer from 0 to 6 (NI 443x) or 0 to 7 (NI 446x). Therefore, the effective sample rate ( $f_{es}$ ) is  $2^n \times f_s$ . The interpolation factor must be sufficient to move the effective sample rate into the 51.2 kS/s or higher range (NI 443x) or the 102.4 kS/s or higher range (NI 446x). Figure 2-3 shows an example of four-times interpolation and the resulting images. A linear-phase digital filter then removes almost all energy above one-half  $f_s$ .

Figure 2-3. Signal After Digital Filter

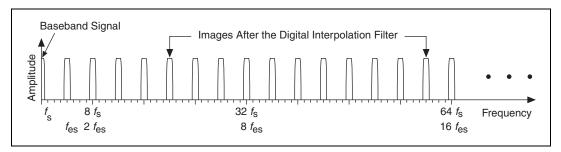

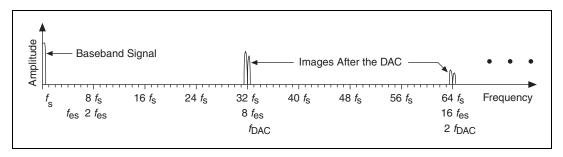

Second, the DAC resamples the data to a new frequency  $(f_{DAC})$ . The frequency  $f_{DAC}$  is eight times higher than  $f_{es}$ . Figure 2-4 shows the resulting images.

Figure 2-4. Images After DAC Filter

Some further (inherent) filtering occurs at the DAC because the data is digitally sampled and held at eight times  $f_{es}$ . This filtering has a  $\sin x/x$  response, yielding nulls at multiples of eight times  $f_s$ , as shown in Figure 2-5.

Figure 2-5. Signal After DAC

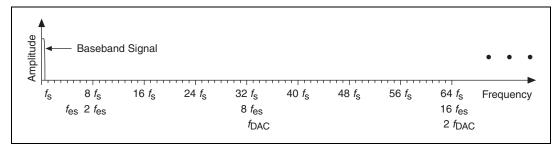

Third, a multi-pole analog filter with a fixed cut-off at 89 kHz (NI 4431) or 243 kHz (NI 4461) filters the remaining images, as shown in Figure 2-6.

Figure 2-6. Signal After Analog Filters

#### Filter Delay

Output filter delay—the time required for digital data to propagate through the DAC and interpolation digital filters—varies depending on the update rate for DACs. For example, the filter delay at 10 kS/s for the NI 4461 is 38.5 update clock cycles. This signal experiences a delay equal to 3.85 ms. This delay is an important factor for stimulus-response measurements, control applications, or any application where loop time is critical. You often might want to maximize the sample rate to minimize the time required for a specific number of update clock cycles to elapse, since it varies with frequency, as shown in Table 2-5 and Table 2-6.

The interpolation filter adds additional output filter delay depending on the update rate. Table 2-5 and Table 2-6 provide more information about how the interpolation filter affects the output filter delay.

| Update Rate<br>(kS/s)   | Interpolation<br>Factor | NI 4461 Output Filter<br>Delay (Samples) |

|-------------------------|-------------------------|------------------------------------------|

| $1.0 \le f_s \le 1.6$   | 128                     | 36.6                                     |

| $1.6 < f_s \le 3.2$     | 64                      | 36.8                                     |

| $3.2 < f_s \le 6.4$     | 32                      | 37.4                                     |

| $6.4 < f_s \le 12.8$    | 16                      | 38.5                                     |

| $12.8 < f_s \le 25.6$   | 8                       | 40.8                                     |

| $25.6 < f_s \le 51.2$   | 4                       | 43.2                                     |

| $51.2 < f_s \le 102.4$  | 2                       | 48.0                                     |

| $102.4 < f_s \le 204.8$ | 1                       | 32.0                                     |

**Table 2-5.** NI 4461 Interpolation Factor and Output Filter Delay

| Update Rate<br>(kS/s)    | Interpolation<br>Factor | NI 4461 Output Filter<br>Delay (Samples) |

|--------------------------|-------------------------|------------------------------------------|

| $0.8 \le f_s < 1.6$      | 64                      | 63.3                                     |

| $1.6 \le f_s < 3.2$      | 32                      | 62.6                                     |

| $3.2 \le f_s < 6.4$      | 16                      | 61.3                                     |

| $6.4 \le f_s < 12.8$     | 8                       | 58.5                                     |

| $12.8 \le f_s < 25.6$    | 4                       | 53                                       |

| $25.6 \le f_s < 51.2$    | 2                       | 42                                       |

| $51.2 \le f_s \le 102.4$ | 1                       | 20                                       |

**Table 2-6.** NI 4431 Interpolation Factor and Output Filter Delay

#### FIFO and PCI Data Transfer

DSA device input channels share a FIFO buffer, and the output channels share a separate FIFO buffer. The *NI USB-443x Specifications* and *NI 446x Specifications* contain information about the buffer sample depth.

The NI 4461 has a flexible data transfer request condition. You can program the device to request DMA transfers according to a programmable FIFO condition. Refer to the *NI-DAQmx Help* or the *LabVIEW Help* for information about conditions available for specific devices.

**Note** USB devices do *not* support setting the transfer request condition.

#### **Power Off and Power Loss**

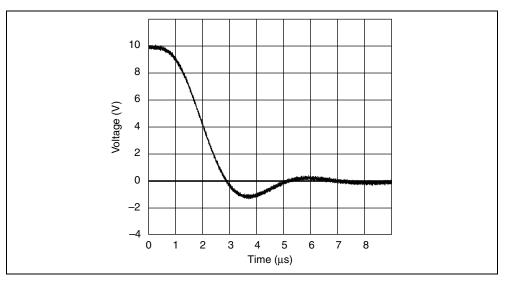

When the NI 4461 is powered off or loses power, the output channels assume a high-impedance state. The outputs of the NI 4461 drop to 0.0~V in approximately  $8~\mu s$ . Figure 2-7 illustrates the typical behavior of an NI 4461 generating 10~V when powered off or when the device loses power.

Figure 2-7. Power Off and Power Loss Behavior

# Triggering

DSA devices support two types of triggers: start triggers and reference triggers.

- When a DSA device is configured to use a start trigger, the returned data consists of samples that were acquired after the start trigger occurred.

- When a DSA device is configured to use a reference trigger, the returned data consists of samples that were acquired both before and after the trigger. Samples acquired before the reference trigger are called pretrigger samples, and samples acquired after the reference trigger are called posttrigger samples.

For example, a DSA device can be configured to use a digital start trigger, an analog reference trigger, and to acquire 100 pretrigger and 200 posttrigger samples. In this case, the device will start acquiring data after the digital start trigger occurs. It will acquire at least 100 samples, and then begin looking for the analog reference trigger. After the reference trigger occurs, the device will acquire 200 samples, and then stop. The returned data will consist of the 100 samples that occurred before the reference trigger, and the 200 samples that occurred after the reference trigger. Use the NI-DAQmx Trigger VIs to configure trigger properties.

The start and reference triggers can be configured independently, and can be set to use a variety of sources, both analog and digital. Triggers can be configured to occur on either the rising or falling edge of a signal. Moreover, analog triggers support other modes of operation, including triggering on edges with hysteresis, and triggering when a signal enters or leaves a predefined window. Since the start and reference triggers are configured independently, alternate edges of a single signal can be used to control an acquisition or generation.

During repetitive triggering on a waveform, you might observe jitter because of the uncertainty of where a trigger level falls compared to the actual digitized data. Although this trigger jitter is never greater than one sample period, it might be significant when the sample rate is only twice the bandwidth of interest. This jitter usually has no effect on data processing, and you can decrease this jitter by sampling at a higher rate.

#### **Digital Triggering**

You can configure DSA devices to trigger in response to a digital signal on the PFI 0 connector, located on the device front panel. This pin is labeled EXT TRIG on NI 447x devices, and it is labeled PFI0 on NI 446x and NI 449x devices. The trigger circuit can respond either to a rising or a falling edge. The trigger signal must comply to TTL voltage levels. Refer to the NI USB-443x Specifications, NI 446x Specifications, NI 447x Specifications, and NI 449x Specifications for additional trigger requirements.

PXI and PCI DSA devices also offer digital triggering in response to signals on the PXI/PXIe or RTSI trigger bus. Use any line from PXI\_Trig<0..6> or RTSI<0..6>. One exception applies—when synchronizing multiple NI PXI-447x devices, PXI\_Trig 5 is reserved for internal use. As with external digital triggering, you can program the device to respond to either the rising or falling signal edge.

**Note** The NI USB-443x devices have eight PFI lines for triggering. These PFI lines are located on the back of the device.

#### **Analog Triggering**

You can configure the DSA device analog trigger circuitry to monitor any input channel from which you acquire data. Choosing an input channel as the trigger channel does not influence the input channel acquisition capabilities.

The trigger circuit generates an internal digital trigger based on the input signal and the defined trigger levels. For example, you can configure the device to start acquiring samples after the input signal crosses a specific threshold. You also can route this internal trigger to the PXI/PXIe or RTSI trigger bus to synchronize the start of the acquisition operation by one device with the operation of other devices in the system.

You can use several analog triggering modes with DSA devices, including analog edge, analog edge with hysteresis, and window triggering.

#### **Analog Edge Triggering**

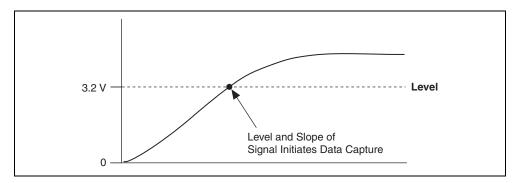

For analog edge triggering, configure the device to detect a certain signal **Level** and slope, either rising or falling. Figure 2-8 shows an example of rising edge analog triggering. The trigger asserts when the signal starts below **Level** and then crosses above **Level**.

Chapter 2

Figure 2-8. Analog Trigger Level

#### **Analog Edge Triggering With Hysteresis**

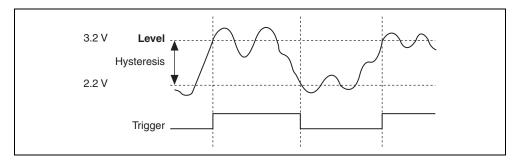

When you add hysteresis to analog edge triggering, you add a window above or below the trigger level. This trigger often is used to reduce false triggering due to noise or jitter in the signal. For example, if you add a hysteresis of 1 V to the example in Figure 2-8, which uses a level of 3.2 V, the signal must start at or drop below 2.2 V to arm the trigger. The trigger asserts when the signal rises above 3.2 V and deasserts when it falls below 2.2 V, as shown in Figure 2-9.

**Figure 2-9.** Analog Edge Triggering with Hysteresis on Rising Slope

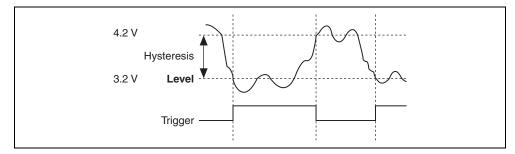

When using hysteresis with a falling slope, the trigger is armed when the signal starts above **Level**, plus the hysteresis value, and asserts when the signal crosses below **Level**. For example, if you add a hysteresis of 1 V to a level of 3.2 V, the signal must start at or rise above 4.2 V to arm the trigger. The trigger asserts as the signal falls below 3.2 V and deasserts when it rises above 4.2 V, as shown in Figure 2-10.

**Figure 2-10.** Analog Edge Triggering with Hysteresis on Falling Slope

#### Window Triggering

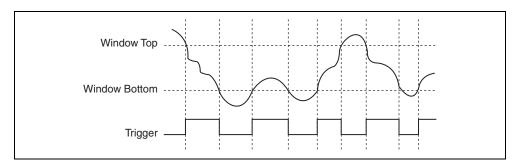

A window trigger occurs when an analog signal either passes into (enters) or passes out of (leaves) a window defined by two levels. Specify the levels by setting a value for the top and bottom window boundaries. Figure 2-11 demonstrates a trigger that acquires data when the signal enters the window. You can also program the trigger circuit to acquire data when the signal leaves the window.

Figure 2-11. Window Triggering

#### Triggering and Filter Delay

Analog and digital triggering exhibit different behaviors with respect to the filter delay in the ADC.

When you use digital triggering, the ADCs begin generating digital data immediately after receiving the digital trigger signal. However, the analog signal entering the ADCs is still

subject to the filter delay. This circumstance means that when the trigger is received, the analog levels at the front of the ADCs are not digitized until a certain number of sample intervals later. You can observe this behavior with an experiment. Connect the same TTL signal to the external digital trigger input and to an AI channel. Configure the acquisition to respond to a digital trigger. The rising edge of the trigger does not appear in the digitized waveform until a specific number of filter delay samples pass. Refer to the NI USB-443x Specifications, NI 446x Specifications, NI 447x Specifications, and NI 449x Specifications for more information about filter delay.

Analog triggering is performed on the digital output of the ADC. The analog trigger circuit on a DSA device is a digital comparator. Because the trigger is located after the ADC in the signal path, the filter delay is not evident in the acquired data. If the analog trigger is configured with a rising edge and a level of 1.0 V, the voltage of the first sample is just above 1.0 V.

**Note** (NI USB-4431 and NI 4461) You must also consider the AO filter delay in your application. The digital filter introduces a deterministic delay during AO operations.

#### **Filter Delay Removal**

NI 449*x* devices support the AI.RemoveFilterDelay property. When this feature is enabled, the NI 449*x* device will automatically compensate for the filter delay of its analog input path.

**Note** The AI.RemoveFilterDelay property cannot be used with an analog start trigger.

Suppose you have configured an NI 449x to sample at 204.8 kS/s, and to respond to a digital start trigger. At this sample rate, the filter delay is 64 samples. Without the filter delay removal feature, the first sample will appear to have been acquired roughly 64 samples before the start trigger. With the filter delay removal feature, the first sample is acquired within roughly one sample period of the start trigger.

The AI.RemoveFilterDelay property is especially useful when synchronizing NI 449*x* devices to other data acquisition devices that do not exhibit filter delay. With the filter delay removal feature enabled, the data acquired from all synchronized devices is aligned to within roughly one sample period.

If synchronizing multiple NI 449x devices, the filter delay removal feature must be enabled on all of them. Otherwise, the acquired data will not be aligned.

There is a caveat with the filter delay removal feature that comes into play when using an analog reference trigger, and synchronizing to another device by exporting the sample clock (for example, an NI X Series device). In this case, manually add the filter delay of the NI 449x device (rounded down to an integer) to the requested pretrigger samples, and subtract it from the posttrigger samples, of all devices importing the NI 449x sample clock. If this step is not performed, the devices importing the sample clock will never complete their acquisitions.

# **Timing and Synchronization**

#### **Timing Signals**

#### **Frequency Timebase**

DSA devices have high-accuracy oscillators on board. The oscillator feeds a direct digital synthesis (DDS) chip, which is used to generate the other on-board timing signals.

#### **Reference Clock**

PXI/PXIe chassis backplanes provide a common, 10 MHz reference clock to each peripheral slot. An independent buffer drives the clock signal to each device in the chassis.

DSA devices that support reference clock synchronization are able to lock their frequency timebases to this shared reference.

You can drive PXI\_CLK10 from an external source through the PXI\_CLK\_IN pin on the P2 connector of the star trigger slot on the chassis. Driving an external clock source on this pin automatically disables the 10 MHz source generated on the PXI/PXIe backplane.

#### **Oversample Clock**

The delta-sigma converters used on DSA devices acquire 1-bit samples at a rate that is much faster than the requested sample rate. The resulting 1-bit data stream is converted to a 24-bit data stream at the requested sample rate. The oversample clock drives the acquisition of 1-bit samples from the delta-sigma converter. The frequency of the oversample clock is a multiple of the requested sample rate.

#### Sample Clock Timebase

The sample clock timebase is the timing signal that is used to produce the oversample clock on DSA devices. All of the converters on a single DSA device share a common sample clock timebase.

When a DSA device is operating stand-alone (without synchronizing to other devices), a DDS chip produces the sample clock timebase. DDS is a method of generating a programmable clock with excellent frequency resolution. The DDS chips are capable of between 28- and 32-bits of resolution, and can produce between  $2^{28}$  and  $2^{32}$  frequency steps to create the sample clock timebase.

When synchronizing multiple DSA devices, each device must share a common sample clock timebase. When multiple devices share a common sample clock timebase, each is able to generate a phase-aligned version of the ADC and DAC oversample clocks. This allows for