#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

### **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

PXI-5422

#### **SPECIFICATIONS**

# PXI-5422

### 80 MHz Bandwidth, 16-Bit PXI Waveform Generator

These specifications apply to the 8 MB, 32 MB, 256 MB, and 512 MB PXI-5422.

### Contents

| Conditions                                               | 2  |

|----------------------------------------------------------|----|

| CH 0 Analog Output                                       | 2  |

| Output Voltage                                           |    |

| Amplitude and Offset.                                    |    |

| Maximum Output Voltage                                   | 3  |

| Accuracy                                                 | 4  |

| Output                                                   | 5  |

| Frequency and Transient Response.                        | 5  |

| Suggested Maximum Frequencies                            | 8  |

| Spectral Characteristics                                 | 9  |

| Sample Clock                                             | 16 |

| Sample Rate Range and Resolution                         | 16 |

| Sample Clock Delay Range and Resolution                  |    |

| System Phase Noise and Jitter (10 MHz Carrier)           |    |

| Sample Clock Exporting                                   |    |

| Onboard Clock (Internal VCXO)                            | 19 |

| Phase-Locked Loop (PLL) Reference Clock                  | 19 |

| CLK IN                                                   | 20 |

| PFI 0 and PFI 1                                          | 20 |

| DIGITAL DATA & CONTROL (DDC)                             | 21 |

| Output Signals (Data Outputs, DDC CLK OUT, and PFI <45>) | 22 |

| Input Signals (DDC CLK IN and PFI <23>)                  |    |

| DDC CLK OUT                                              | 23 |

| DDC CLK IN                                               | 23 |

| Start Trigger                                            | 23 |

| Markers                                                  | 24 |

| Arbitrary Waveform Generation Mode                       | 25 |

| Memory Limits                                            | 26 |

| Calibration                                              | 28 |

| Power                                                    | 28 |

| Physical                                                 | 29 |

| Environment                             | 29 |

|-----------------------------------------|----|

| Operating Environment                   | 30 |

| Storage Environment                     |    |

| Shock and Vibration                     | 30 |

| Compliance and Certifications           | 31 |

| Safety Compliance Standards             | 31 |

| Electromagnetic Compatibility           | 31 |

| CE Compliance                           | 31 |

| Product Certifications and Declarations | 31 |

| Environmental Management.               | 32 |

| 5                                       |    |

### **Conditions**

Specifications are valid under the following conditions unless otherwise noted:

- Analog filter enabled

- Signals terminated with 50  $\Omega$

- Direct path set to 1 V pk-pk

- Low-gain amplifier path set to 2 V pk-pk

- High-gain amplifier path set to 12 V pk-pk

- Sample rate set to 200 MS/s

- Sample Clock source set to Divide-by-N

Typical specifications are representative of an average unit and valid under the following conditions unless otherwise noted:

• Ambient operating temperature range of  $20 \pm 3$  °C

### CH 0 Analog Output

| Number of channels              | 1                                                      |

|---------------------------------|--------------------------------------------------------|

| Connector type                  | SMB jack                                               |

| Output Voltage                  |                                                        |

| Full-scale voltage              |                                                        |

| Main output path <sup>1</sup>   | 12.00 V pk-pk to 5.64 mV pk-pk into a 50 $\Omega$ load |

| Direct output path <sup>2</sup> | 1.000 V pk-pk to 0.707 V pk-pk                         |

| DAC resolution                  | 16 bits                                                |

When the main output path is selected, either the low-gain amplifier or the high-gain amplifier is used, depending on the value of the Gain property or NIFGEN ATTR GAIN attribute.

<sup>&</sup>lt;sup>2</sup> The direct path is optimized for intermediate frequency (IF) applications.

### Amplitude and Offset

Table 1. Amplitude Range<sup>3</sup>

| Path                | Load | Amplitude (V pk-pk) |         |

|---------------------|------|---------------------|---------|

|                     |      | Minimum             | Maximum |

| Direct              | 50 Ω | 0.707               | 1.00    |

|                     | 1 kΩ | 1.35                | 1.91    |

|                     | Open | 1.41                | 2.00    |

| Low-gain amplifier  | 50 Ω | 0.00564             | 2.00    |

|                     | 1 kΩ | 0.0107              | 3.81    |

|                     | Open | 0.0113              | 4.00    |

| High-gain amplifier | 50 Ω | 0.0338              | 12.0    |

|                     | 1 kΩ | 0.0644              | 22.9    |

|                     | Open | 0.0676              | 24.0    |

| Amplitude resolution      | <0.06% (0.004 dB) of Amplitude Range                                                      |

|---------------------------|-------------------------------------------------------------------------------------------|

| Offset range <sup>4</sup> | Span of ±50% of <i>Amplitude Range</i> with increments <0.0028% of <i>Amplitude Range</i> |

## Maximum Output Voltage

Table 2. Maximum Output Voltage<sup>5</sup>

| Path   | Load | Maximum Output Voltage (V) |

|--------|------|----------------------------|

| Direct | 50 Ω | ±0.500                     |

|        | 1 kΩ | ±0.953                     |

|        | Open | ±1.000                     |

<sup>&</sup>lt;sup>3</sup> Amplitude values assume the full scale of the DAC is utilized. If an amplitude smaller than the minimum value is desired, then waveforms less than full scale of the DAC can be used. NI-FGEN compensates for user-specified resistive loads.

<sup>&</sup>lt;sup>4</sup> Offset range is not available on the direct path.

<sup>&</sup>lt;sup>5</sup> The combination of amplitude and offset is limited by the maximum output voltage.

Table 2. Maximum Output Voltage<sup>5</sup> (Continued)

| Path                | Load | Maximum Output Voltage (V) |

|---------------------|------|----------------------------|

| Low-gain amplifier  | 50 Ω | ±1.000                     |

|                     | 1 kΩ | ±1.905                     |

|                     | Open | ±2.000                     |

| High-gain amplifier | 50 Ω | ±6.000                     |

|                     | 1 kΩ | ±11.43                     |

|                     | Open | ±12.00                     |

### Accuracy

**Table 3.** DC Accuracy<sup>6</sup>

| Path                | DC Accuracy                                                           |                                                                 |  |

|---------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------|--|

|                     | ±10 °C of Self-Calibration<br>Temperature                             | 0 °C to 55 °C                                                   |  |

| Low-gain amplifier  | $\pm 0.2\%$ of Amplitude Range $\pm 0.05\%$ of Offset $\pm 500~\mu V$ | $\pm 0.4\%$ of Amplitude Range $\pm$ 0.05% of Offset $\pm$ 1 mV |  |

| High-gain amplifier |                                                                       |                                                                 |  |

<sup>&</sup>lt;sup>5</sup> The combination of amplitude and offset is limited by the maximum output voltage.

<sup>6</sup> All paths are calibrated for amplitude and gain errors. The low-gain and high-gain amplifier paths are also calibrated for offset errors. DC accuracy is calibrated into a high-impedance load. Amplitude Range is defined as two times the gain setting. For example, a DC signal with a gain of 8 has an amplitude range of 16 V. If this signal has an offset of 1.5, DC accuracy is calculated by the following equation: ±0.2% \* (16 V) ± 0.05% \* (1.5 V) ± 500µV = ±33.25 mV

Table 3. DC Accuracy<sup>6</sup>

| Path   | Gain Accuracy                          |                       |

|--------|----------------------------------------|-----------------------|

|        | ±10 °C of Self-Calibration Temperature | 0 °C to 55 °C         |

| Direct | ±0.2% Amplitude Range                  | ±0.4% Amplitude Range |

| DC offset error <sup>7</sup>       | ±30 mV                                                                        |

|------------------------------------|-------------------------------------------------------------------------------|

| AC amplitude accuracy <sup>8</sup> | (+2.0% + 1 mV), (-1.0% - 1 mV)<br>(+0.8% + 0.5 mV), (-0.2% - 0.5 mV), typical |

### Output

| Output impedance        | Software-selectable: 50 $\Omega$ or 75 $\Omega$ , nominal                                                                                |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| Output coupling         | DC                                                                                                                                       |

| Output enable           | Software-selectable <sup>9</sup>                                                                                                         |

| Maximum output overload | CH 0 can be connected to a 50 $\Omega$ , $\pm 12$ V ( $\pm 8$ V for the direct path) source without sustaining any damage. <sup>10</sup> |

| Waveform summing        | Supported <sup>11</sup>                                                                                                                  |

### Frequency and Transient Response

| Analog filter <sup>12</sup> | Software-selectable: 7-pole elliptical filter for |

|-----------------------------|---------------------------------------------------|

|                             | image suppression                                 |

<sup>&</sup>lt;sup>6</sup> All paths are calibrated for amplitude and gain errors. The low-gain and high-gain amplifier paths are also calibrated for offset errors. DC accuracy is calibrated into a high-impedance load. Amplitude Range is defined as two times the gain setting. For example, a DC signal with a gain of 8 has an amplitude range of 16 V. If this signal has an offset of 1.5, DC accuracy is calculated by the following equation:  $\pm 0.2\%$  \* (16 V)  $\pm 0.05\%$  \* (1.5 V)  $\pm 500\mu$ V =  $\pm 33.25$  mV

<sup>&</sup>lt;sup>7</sup> Within 0 °C to 55 °C.

<sup>&</sup>lt;sup>8</sup> With a 50 kHz sine wave and terminated with high impedance.

<sup>&</sup>lt;sup>9</sup> When the output path is disabled, CH 0 is terminated to ground with a 1 W resistor with a value equal to the selected output impedance.

No damage occurs if CH 0 is shorted to ground indefinitely.

<sup>11</sup> The output terminals of multiple PXI-5422 waveform generators can be connected directly

<sup>&</sup>lt;sup>12</sup> Available on low-gain amplifier and high-gain amplifier paths.

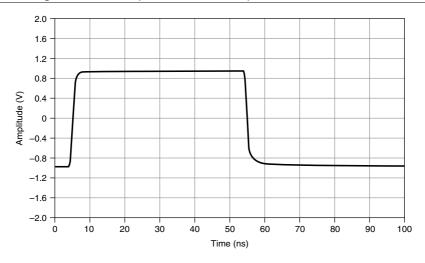

Table 4. Pulse Response<sup>13</sup>

| Path                | Rise/Fall Time (ns), Typical | Aberration (%), Typical |

|---------------------|------------------------------|-------------------------|

| Direct              | 1.0                          | 16                      |

| Low-gain amplifier  | 2.1                          | 6                       |

| High-gain amplifier | 4.8                          | 8                       |

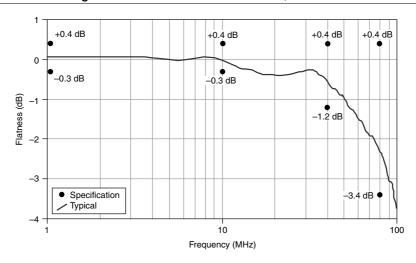

Figure 1. Normalized Passband Flatness, Direct Path

$<sup>^{13}</sup>$  Analog filter disabled. Measured with a 1 m RG-223 cable.

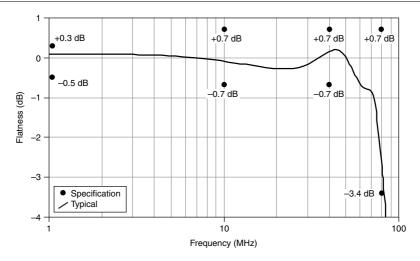

Figure 2. Normalized Passband Flatness, Low-Gain Amplifier Path

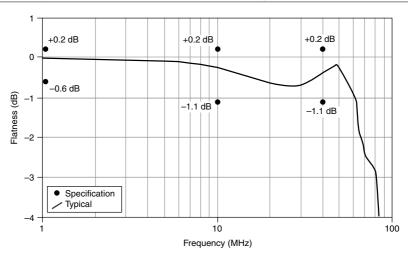

Figure 3. Normalized Passband Flatness, High-Gain Amplifier Path

Figure 4. Pulse Response, Low-Gain Amplifier Path with a 50  $\Omega$  Load

## Suggested Maximum Frequencies

Table 5. Suggested Maximum Frequencies for Common Functions<sup>14</sup>

| Path                | Frequency (MHz) |                                                               |  |    |

|---------------------|-----------------|---------------------------------------------------------------|--|----|

|                     | Sine            | Square <sup>15</sup> Ramp <sup>15</sup> Triangle <sup>1</sup> |  |    |

| Direct              | 80              | Not recommended                                               |  | ed |

| Low-gain amplifier  |                 | 50                                                            |  | 10 |

| High-gain amplifier | 43              | 25                                                            |  |    |

$<sup>^{14}</sup>$  The minimum frequency is <1 mHz. The value depends on memory size and module configuration.

Disable the analog filter for square, ramp, and triangle functions.

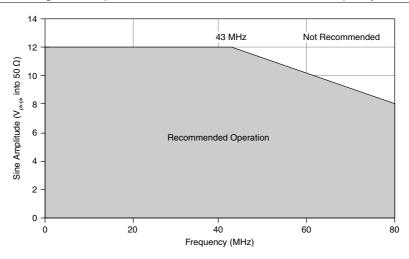

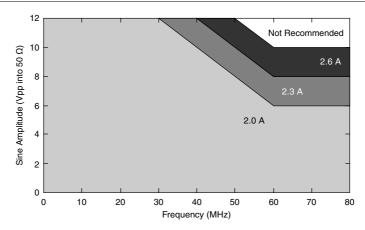

Figure 5. Amplitude Versus Recommended Sine Wave Frequency

### **Spectral Characteristics**

Table 6. Spurious-Free Dynamic Range (SFDR) with Harmonics<sup>16</sup>

| Table of openious ( Test 2) training ( e. 2 t.) training ( |                                   |                         |                          |  |

|------------------------------------------------------------|-----------------------------------|-------------------------|--------------------------|--|

| Frequency                                                  | SFDR with Harmonics (dB), Typical |                         |                          |  |

|                                                            | Direct Path                       | Low-Gain Amplifier Path | High-Gain Amplifier Path |  |

| 1 MHz                                                      | 70                                | 65                      | 66                       |  |

| 5 MHz                                                      |                                   |                         | 58                       |  |

| 10 MHz                                                     |                                   |                         | 52                       |  |

| 20 MHz                                                     | 63                                | 64                      | 49                       |  |

| 30 MHz                                                     | 57                                | 60                      | 43                       |  |

$<sup>^{16}</sup>$  At amplitude of -1 dBFS and measured from DC to 100 MHz. All values include aliased harmonics. Dynamic range is defined as the difference between the carrier level and the largest spur.

**Table 6.** Spurious-Free Dynamic Range (SFDR) with Harmonics<sup>16</sup> (Continued)

| Frequency | SFDR with Harmonics (dB), Typical |                         |                          |

|-----------|-----------------------------------|-------------------------|--------------------------|

|           | Direct Path                       | Low-Gain Amplifier Path | High-Gain Amplifier Path |

| 40 MHz    | 48                                | 53                      | 39                       |

| 50 MHz    |                                   |                         | _                        |

| 60 MHz    | 47                                | 52                      |                          |

| 70 MHz    |                                   |                         |                          |

| 80 MHz    | 41                                |                         |                          |

Table 7. Spurious-Free Dynamic Range (SFDR) without Harmonics<sup>16</sup>

| Frequency | SFDR without Harmonics (dB), Typical |                         |                          |  |

|-----------|--------------------------------------|-------------------------|--------------------------|--|

|           | Direct Path                          | Low-Gain Amplifier Path | High-Gain Amplifier Path |  |

| 1 MHz     | 84                                   | 79                      | 76                       |  |

| 5 MHz     |                                      |                         |                          |  |

| 10 MHz    | 79                                   |                         |                          |  |

| 20 MHz    |                                      |                         |                          |  |

| 30 MHz    | 72                                   | 70                      | 67                       |  |

| 40 MHz    | 47                                   | 57                      | 54                       |  |

| 50 MHz    |                                      | 52                      | _                        |  |

| 60 MHz    | 46                                   | 51                      |                          |  |

| 70 MHz    |                                      |                         |                          |  |

| 80 MHz    | 40                                   |                         |                          |  |

At amplitude of -1 dBFS and measured from DC to 100 MHz. All values include aliased harmonics. Dynamic range is defined as the difference between the carrier level and the largest spur.

**Table 8.** Average Noise Density<sup>17</sup>, Direct Path

| Amplitude Range |         | Av                                   | rerage Noise Densi | ty, Typical |

|-----------------|---------|--------------------------------------|--------------------|-------------|

|                 |         | $\frac{\text{nV}}{\sqrt{\text{Hz}}}$ | dBm/Hz             | dBFS/Hz     |

| 1.00 V pk-pk    | 4.0 dBm | 19.9                                 | -141               | -145        |

Table 9. Average Noise Density<sup>17</sup>, Low-Gain Amplifier Path

| Amplitude Range |           | Ave                                  | rage Noise Densi | ty, Typical |

|-----------------|-----------|--------------------------------------|------------------|-------------|

|                 |           | $\frac{\text{nV}}{\sqrt{\text{Hz}}}$ | dBm/Hz           | dBFS/Hz     |

| 0.06 V pk-pk    | -20.5 dBm | 1.3                                  | -148             | -144        |

| 0.10 V pk-pk    | -16.0 dBm | 2.2                                  |                  |             |

| 0.40 V pk-pk    | -4.0 dBm  | 8.9                                  |                  |             |

| 1.00 V pk-pk    | 4.0 dBm   | 22.3                                 | -140             |             |

| 2.00 V pk-pk    | 10.0 dBm  | 44.6                                 | -134             |             |

Table 10. Average Noise Density<sup>17</sup>, High-Gain Amplifier Path

| Amplitude Range |                        | Aver                                 | age Noise Densi | ty, Typical |

|-----------------|------------------------|--------------------------------------|-----------------|-------------|

|                 |                        | $\frac{\text{nV}}{\sqrt{\text{Hz}}}$ | dBm/Hz          | dBFS/Hz     |

| 4.00 V pk-pk    | 16.0 dBm               | 93.8                                 | -128            | -144        |

| 12.00 V pk-pk   | 12.00 V pk-pk 25.6 dBm |                                      | -118            |             |

Average noise density at small amplitudes is limited by a -148 dBm/Hz noise floor.

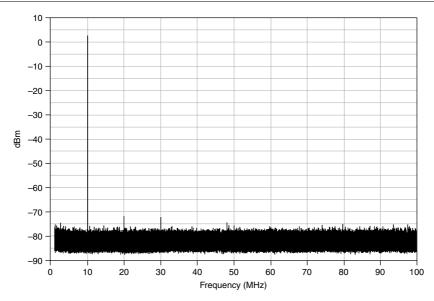

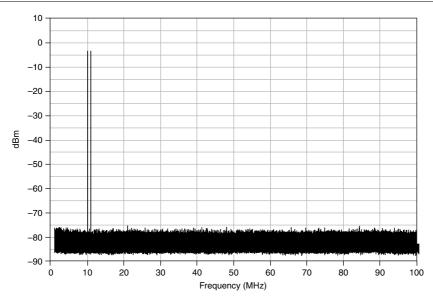

Figure 6. 10 MHz Single-Tone Spectrum<sup>18</sup>, Direct Path, 200 MS/s, Typical

<sup>18</sup> The noise floor in this figure is limited by the measurement device. Refer to *Table 8*. on page 11 for more information about this limit.

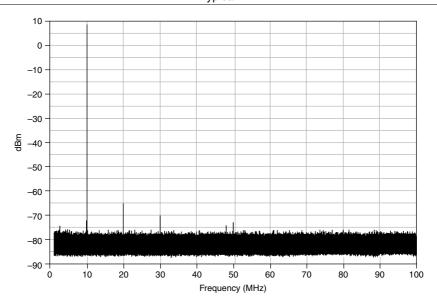

Figure 7. 10.00001 MHz Single-Tone Spectrum<sup>18</sup>, Low-Gain Amplifier Path, 200 MS/s, Typical

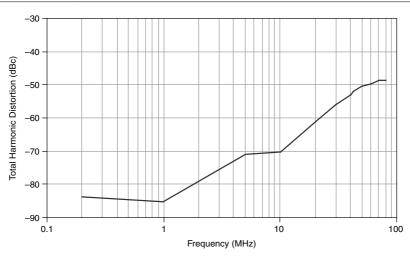

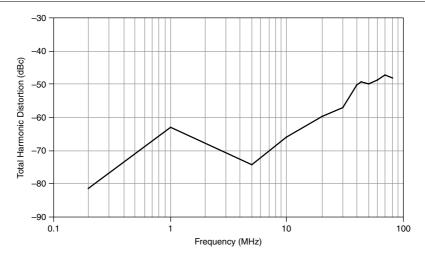

Figure 8. Total Harmonic Distortion, Direct Path, Typical

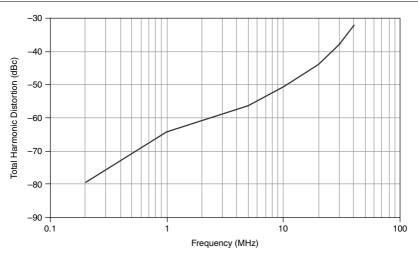

Figure 9. Total Harmonic Distortion, Low-Gain Amplifier Path, Typical

Figure 10. Total Harmonic Distortion, High-Gain Amplifier Path, Typical

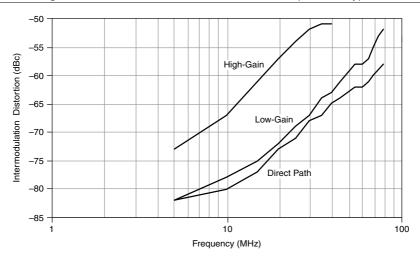

Figure 11. Intermodulation Distortion, 200 kHz Separation, Typical

Figure 12. Direct Path, Two-Tone Spectrum<sup>18</sup>, Typical

# Sample Clock

| Internal | Divide-by- $N (N \ge 1)$               |

|----------|----------------------------------------|

|          | DDS-based, High-Resolution             |

| External | CLK IN (SMB front panel connector)     |

|          | DDC CLK IN (DIGITAL DATA &             |

|          | CONTROL front panel connector)         |

|          | PXI Star Trigger (backplane connector) |

|          | PXI Trig <07> (backplane connector)    |

### Sample Rate Range and Resolution

Table 11. Sample Rate Range

| Sample Clock Source | Sample Rate Range (MS/s) |  |

|---------------------|--------------------------|--|

| Divide-by-N         | 5 to 200                 |  |

| High-Resolution     | 5 to 100                 |  |

|                     | >100 to 200              |  |

| CLK IN              | 5 to 200                 |  |

| DDC CLK IN          |                          |  |

| PXI Star Trigger    | 5 to 105                 |  |

| PXI_Trig <07>       | 5 to 20                  |  |

Table 12. Sample Rate Resolution

| Sample Clock Source | Sample Rate Resolution                                  |

|---------------------|---------------------------------------------------------|

| Divide-by-N         | Configurable to $(200 \text{ MS/s})/N (1 \le N \le 40)$ |

| High-Resolution     | 1.06 μHz                                                |

|                     | 4.24 μHz                                                |

<sup>&</sup>lt;sup>19</sup> Refer to the *Onboard Clock* section for more information about internal clock sources.

Table 12. Sample Rate Resolution (Continued)

| Sample Clock Source | Sample Rate Resolution                                          |

|---------------------|-----------------------------------------------------------------|

| CLK IN              | Resolution determined by external clock source. External Sample |

| DDC CLK IN          | Clock duty cycle tolerance 40% to 60%.                          |

| PXI Star Trigger    |                                                                 |

| PXI_Trig <07>       |                                                                 |

## Sample Clock Delay Range and Resolution

Table 13. Delay Adjustment Range

| Sample Clock Source | Delay Adjustment Range |

|---------------------|------------------------|

| Divide-by-N         | ±1 Sample Clock period |

| High-Resolution     |                        |

| CLK IN              | 0 ns to 7.6 ns         |

| DDC CLK IN          |                        |

| PXI Star Trigger    |                        |

| PXI_Trig <07>       |                        |

Table 14. Delay Adjustment Resolution

| Sample Clock Source      | Delay Adjustment Resolution |

|--------------------------|-----------------------------|

| Divide-by-N              | <5 ps                       |

| High-Resolution ≤100 MHz | Sample Clock period/16,384  |

| High-Resolution >100 MHz | Sample Clock period/4,096   |

| CLK IN                   | <15 ps                      |

| DDC CLK IN               |                             |

| PXI Star Trigger         |                             |

| PXI_Trig <07>            |                             |

### System Phase Noise and Jitter (10 MHz Carrier)

Table 15. System Phase Noise Density Offset<sup>20</sup>

| Sample Clock Source                    | System Phase Noise Density Offset (dBc/Hz), Typical |       |        |

|----------------------------------------|-----------------------------------------------------|-------|--------|

|                                        | 100 Hz                                              | 1 kHz | 10 kHz |

| Divide-by-N                            | -110                                                | -122  | -138   |

| High-Resolution <sup>21</sup> 100 MS/s | -109                                                | -120  | -120   |

| High-Resolution <sup>21</sup> 200 MS/s | -108                                                |       | -122   |

| CLK IN                                 | -116                                                | -130  | -143   |

| PXI Star Trigger <sup>22</sup>         | -111                                                | -128  | -136   |

Table 16. System Output Jitter <sup>23</sup>

| Sample Clock Source                    | System Output Jitter (ps rms), Typical |

|----------------------------------------|----------------------------------------|

| Divide-by-N                            | 1.5                                    |

| High-Resolution <sup>21</sup> 100 MS/s | 4.0                                    |

| High-Resolution <sup>21</sup> 200 MS/s | 4.2                                    |

| CLK IN                                 | 1.1                                    |

| PXI Star Trigger <sup>22</sup>         | 2.1                                    |

| External Sample Clock input jitter tolerance |                  |

|----------------------------------------------|------------------|

| Cycle-cycle jitter                           | ±150 ps, typical |

| Period jitter                                | ±1 ns, typical   |

### Sample Clock Exporting

Destinations<sup>24</sup>

PFI <0..1> (SMB front panel connectors) DDC CLK OUT (DIGITAL DATA & CONTROL front panel connector) PXI Trig <0..6> (backplane connector)

<sup>&</sup>lt;sup>20</sup> Specified at two times DAC oversampling.

<sup>&</sup>lt;sup>21</sup> High-Resolution specifications vary with sample rate.

<sup>&</sup>lt;sup>22</sup> PXI Star Trigger specification is valid when the Sample Clock source is locked to PXI\_CLK10.

<sup>&</sup>lt;sup>23</sup> Specified at two times DAC oversampling. Integrated from 100 Hz to 100 kHz.

Exported Sample Clocks can be divided by integer K ( $1 \le K \le 4,194,304$ ).

#### Maximum frequency

| PFI <01>      | 200 MHz            |  |

|---------------|--------------------|--|

| DDC CLK OUT   | 200 MHz            |  |

| PXI_Trig <06> | 20 MHz             |  |

| Jitter        |                    |  |

| PFI 0         | 6 ps rms, typical  |  |

| PFI 1         | 12 ps rms, typical |  |

| DDC CLK OUT   | 60 ps rms, typical |  |

| Duty cycle    |                    |  |

| PFI <01>      | 25% to 65%         |  |

| DDC CLK OUT   | 35% to 65%         |  |

|               |                    |  |

# Onboard Clock (Internal VCXO)

| Source             | Internal Sample Clocks can either be locked to |

|--------------------|------------------------------------------------|

|                    | a Reference Clock using a phase-locked loop    |

|                    | or derived from the onboard VCXO frequency     |

|                    | reference.                                     |

| Frequency accuracy | ±25 ppm                                        |

# Phase-Locked Loop (PLL) Reference Clock

| Sources <sup>25</sup>         | PXI_CLK10 (backplane connector) CLK IN (SMB front panel connector)                                                                          |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency accuracy            | When using the PLL, the frequency accuracy of the PXI-5422 is solely dependent on the frequency accuracy of the PLL Reference Clock source. |

| Lock time                     | ≤200 ms, typical                                                                                                                            |

| Frequency range <sup>26</sup> | 5 MHz to 20 MHz in increments of 1 MHz <sup>27</sup>                                                                                        |

| Duty cycle range              | 40% to 60%                                                                                                                                  |

| Destinations                  | PFI <01> (SMB front panel connectors)<br>PXI_Trig <06> (backplane connector)                                                                |

|                               |                                                                                                                                             |

<sup>&</sup>lt;sup>25</sup> The PLL Reference Clock provides the reference frequency for the PLL.

<sup>&</sup>lt;sup>26</sup> The PLL Reference Clock frequency must be accurate to  $\pm 50$  ppm.

<sup>&</sup>lt;sup>27</sup> The default is 10 MHz.

# **CLK IN**

| Connector type                       | SMB jack                                       |

|--------------------------------------|------------------------------------------------|

| Direction                            | Input                                          |

| Destinations                         | Sample Clock<br>PLL Reference Clock            |

| Frequency range                      |                                                |

| Sample Clock destination             | 5 MHz to 200 MHz                               |

| PLL Reference Clock destination      | 5 MHz to 20 MHz                                |

| Input voltage range into 50 $\Omega$ |                                                |

| Sine wave                            | 0.65 V pk-pk to 2.8 V pk-pk (0 dBm to +13 dBm) |

| Square wave                          | 0.2 V pk-pk to 2.8 V pk-pk                     |

| Maximum input overload               | ±10 V                                          |

| Input impedance                      | 50 Ω                                           |

| Input coupling                       | AC                                             |

# PFI 0 and PFI 1

| Connector type         | SMB jack (x2) |

|------------------------|---------------|

| Direction              | Bidirectional |

| Frequency range        | DC to 200 MHz |

| As an input (trigger)  |               |

| Destinations           | Start Trigger |

| Maximum input overload | -2 V to +7 V  |

| V IH                   | 2.0 V         |

| V IL                   | 0.8 V         |

| Input impedance        | 1 kΩ          |

#### As an output (event)

| Sources                                   | Sample Clock divided by integer            |

|-------------------------------------------|--------------------------------------------|

|                                           | $K(1 \le K \le 4,194,304)$                 |

|                                           | Sample Clock Timebase (200 MHz) divided by |

|                                           | integer $M$ ( $4 \le M \le 4,194,304$ )    |

|                                           | PLL Reference Clock                        |

|                                           | Marker                                     |

|                                           | Exported Start Trigger (Out Start Trigger) |

| Output impedance                          | 50 Ω                                       |

| Maximum output overload                   | -2 V to +7 V                               |

| Minimum V OH <sup>28</sup>                |                                            |

| Open load                                 | 2.7 V                                      |

| $50 \Omega$ load                          | 1.3 V                                      |

| Maximum V OL <sup>28</sup>                |                                            |

| Open load                                 | 0.6 V                                      |

| $50 \Omega$ load                          | 0.2 V                                      |

| Rise/fall time (20% to 80%) <sup>29</sup> | ≤2.0 ns                                    |

|                                           |                                            |

# DIGITAL DATA & CONTROL (DDC)

| 68-pin VHDCI female receptacle |

|--------------------------------|

| 16                             |

| DDC CLK OUT (clock output)     |

| DDC CLK IN (clock input)       |

| PFI 2 (input)                  |

| PFI 3 (input)                  |

| PFI 4 (output)                 |

| PFI 5 (output)                 |

| 23 pins                        |

|                                |

Output drivers are +3.3 V TTL compatible.

Load of 10 pF.

# Output Signals (Data Outputs, DDC CLK OUT, and PFI <4..5>)

| Low-voltage differential signal (LVDS) <sup>30</sup> |                                                                                                                                                              |

|------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V OH                                                 | 1.3 V, typical<br>1.7 V, maximum                                                                                                                             |

| V OL                                                 | 0.8 V, minimum<br>1.0 V, typical                                                                                                                             |

| Differential output voltage                          | 0.25 V, minimum<br>0.45 V, maximum                                                                                                                           |

| Output common-mode voltage                           | 1.125 V, minimum<br>1.375 V, maximum                                                                                                                         |

| Rise/fall time (20% to 80%)                          | 0.8 ns, typical<br>1.6 ns, maximum                                                                                                                           |

| Output skew <sup>31</sup>                            | 1 ns, typical<br>2 ns, maximum                                                                                                                               |

| Output enable/disable                                | Controlled through the software on all data output signals and control signals collectively. When disabled, the output signals go to a high-impedance state. |

| Maximum output overload                              | -0.3 V to +3.9 V                                                                                                                                             |

### Input Signals (DDC CLK IN and PFI <2..3>)

| Signal type                  | Low-voltage differential signal (LVDS) |

|------------------------------|----------------------------------------|

| Input differential impedance | 100 Ω                                  |

| Maximum output overload      | -0.3 V to +3.9 V                       |

| Differential input voltage   | 0.1 V, minimum<br>0.5 V, maximum       |

| Input common mode voltage    | 0.2 V, minimum<br>2.2 V, maximum       |

<sup>&</sup>lt;sup>30</sup> Tested with a 100 Ω differential load, measured with an SHC68-C68-D3 LVDS cable (188143B-01), and driver and receiver comply with ANSI/TIA/EIA-644.

<sup>31</sup> Skew between any two output signals on the DIGITAL DATA & CONTROL (DDC) front panel connector.

### DDC CLK OUT

| Clocking format | Data outputs and markers change on the falling edge of DDC CLK OUT. |

|-----------------|---------------------------------------------------------------------|

| Frequency range | Refer to the <i>Sample Clock</i> section for more information.      |

| Duty cycle      | 35% to 65%                                                          |

| Jitter          | 60 ps rms, typical                                                  |

### **DDC CLK IN**

| Clocking format            | DDC data output signals change on the rising edge of DDC CLK IN. |

|----------------------------|------------------------------------------------------------------|

| Frequency range            | 10 Hz to 200 MHz                                                 |

| Input duty cycle tolerance | 40% to 60%                                                       |

# Start Trigger

| Sources                                         | PFI <01> (SMB front panel connectors) PFI <23> (DIGITAL DATA & CONTROL front panel connector) PXI_Trig <07> (backplane connector) PXI Star Trigger (backplane connector) Software (use node or function call) Immediate (does not wait for a trigger) <sup>32</sup> |

|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Trigger modes                                   | Single<br>Continuous<br>Stepped<br>Burst                                                                                                                                                                                                                            |

| Edge detection                                  | Rising                                                                                                                                                                                                                                                              |

| Minimum pulse width                             | 25 ns                                                                                                                                                                                                                                                               |

| Delay from Start Trigger to CH 0 analog output  | 65 Sample Clock periods + 110 ns                                                                                                                                                                                                                                    |

| Delay from Start Trigger to digital data output | 41 Sample Clock periods + 110 ns                                                                                                                                                                                                                                    |

|                                                 |                                                                                                                                                                                                                                                                     |

<sup>32</sup> The default is Immediate.

| Destinations                 | A signal used as a trigger can be routed out to any destination listed in the <i>Destinations</i> specification of the <i>Markers</i> section. |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| Exported trigger delay       | 65 ns, typical                                                                                                                                 |

| Exported trigger pulse width | >150 ns                                                                                                                                        |

#### **Related Information**

For information about trigger timing, visit ni.com/info and enter the Info Code pxi-5422trigger-timing.

### Markers

| Destinations                             | PFI <01> (SMB front panel connectors) PFI <45> (DIGITAL DATA & CONTROL front panel connector) PXI_Trig <06> (backpane connector) |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Quantity                                 | One marker per segment                                                                                                           |

| Quantum                                  | Marker position must be placed at an integer multiple of four samples.                                                           |

| Width                                    | >150 ns                                                                                                                          |

| Skew with respect to analog output       |                                                                                                                                  |

| PFI <01>                                 | ±2 Sample Clock periods                                                                                                          |

| PXI_Trig <06>                            | ±2 Sample Clock periods                                                                                                          |

| Skew with respect to digital data output |                                                                                                                                  |

| PFI <45>                                 | <2 ns                                                                                                                            |

| Jitter                                   | 40 ps rms, typical                                                                                                               |

|                                          |                                                                                                                                  |

#### **Related Information**

For information about marker events, visit ni.com/info and enter the Info Code marker-events.

## Arbitrary Waveform Generation Mode

| Memory usage        | The PXI-5422 uses the Synchronization and  |

|---------------------|--------------------------------------------|

|                     | Memory Core (SMC) technology in which      |

|                     | waveforms and instructions share onboard   |

|                     | memory. Parameters—such as number of       |

|                     | segments in sequence list, maximum number  |

|                     | of waveforms in memory, and number of      |

|                     | samples available for waveform storage—are |

|                     | flexible and user-defined.                 |

| Onboard memory size |                                            |

| 8 MB standard       | 8,388,608 bytes                            |

| 32 MB option        | 33,554,432 bytes                           |

| 256 MB option       | 268,435,456 bytes                          |

| 512 MB option       | 536,870,912 bytes                          |

| Output modes        | Arbitrary waveform <sup>33</sup>           |

| -                   | Arbitrary sequence <sup>34</sup>           |

|                     |                                            |

<sup>33</sup> In arbitrary waveform mode, a single waveform is selected from the set of waveforms stored in onboard memory and generated.

<sup>&</sup>lt;sup>34</sup> In arbitrary sequence mode, a sequence directs the PXI-5422 to generate a set of waveforms in a specific order. Elements of the sequence are referred to as segments. Each segment is associated with a set of instructions. The instructions identify which waveform is selected from the set of waveforms in memory, how many loops (iterations) of the waveform are generated, and at which sample in the waveform a marker output signal is sent.

Table 17. Minimum Waveform Size

| Trigger Mode | Minimum Waveform Size (Samples)                              |             |                          |

|--------------|--------------------------------------------------------------|-------------|--------------------------|

|              | Arbitrary Waveform Mode Arbitrary Sequence Mode <sup>3</sup> |             | uence Mode <sup>35</sup> |

|              |                                                              | At >50 MS/s | At ≤50 MS/s              |

| Single       | 16                                                           |             |                          |

| Continuous   | 32                                                           | 192         | 96                       |

| Stepped      |                                                              |             |                          |

| Burst        |                                                              |             |                          |

Loop count

1 to 16,777,215

Burst trigger: Unlimited

Quantum

Waveform size must be an integer multiple of four samples.

# Memory Limits<sup>36</sup>

Table 18. Maximum Waveform Memory

| Onboard Memory | Maximum Waveform Memory (Samples) |                                       |

|----------------|-----------------------------------|---------------------------------------|

|                | Arbitrary Waveform Mode           | Arbitrary Sequence Mode <sup>37</sup> |

| 8 MB standard  | 4,194,176                         | 4,194,048                             |

| 32 MB option   | 16,777,088                        | 16,776,960                            |

| 256 MB option  | 134,217,600                       | 134,217,472                           |

| 512 MB option  | 268,435,328                       | 268,435,200                           |

Table 19. Maximum Waveforms in Arbitrary Sequence Mode<sup>37</sup>

| Onboard Memory | Maximum Waveforms    |

|----------------|----------------------|

| 8 MB standard  | 65,000               |

|                | Burst trigger: 8,000 |

<sup>35</sup> The minimum waveform size is sample rate dependent in arbitrary sequence mode.

<sup>&</sup>lt;sup>36</sup> All trigger modes except where noted.

One or two segments in a sequence.

**Table 19.** Maximum Waveforms in Arbitrary Sequence Mode<sup>37</sup> (Continued)

| Onboard Memory | Maximum Waveforms      |

|----------------|------------------------|

| 32 MB option   | 262,000                |

|                | Burst trigger: 32,000  |

| 256 MB option  | 2,097,000              |

|                | Burst trigger: 262,000 |

| 512 MB option  | 4,194,000              |

|                | Burst trigger: 524,000 |

Table 20. Maximum Segments in a Sequence in Arbitrary Sequence Mode<sup>38</sup>

| Onboard Memory | Maximum Segments in a Sequence |

|----------------|--------------------------------|

| 8 MB standard  | 104,000                        |

|                | Burst trigger: 65,000          |

| 32 MB option   | 418,000                        |

|                | Burst trigger: 262,000         |

| 256 MB option  | 3,354,000                      |

|                | Burst trigger: 2,090,000       |

| 512 MB option  | 6,708,000                      |

|                | Burst trigger: 4,180,000       |

<sup>38</sup> Waveform memory is <4,000 samples.

## Calibration

| Self-calibration     | An onboard, 24-bit ADC and precision voltage reference are used to calibrate the DC gain and offset. The self-calibration is initiated by the user through the software and takes approximately 90 seconds to complete. |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| External calibration | External calibration calibrates the VCXO, voltage reference, DC gain, and offset.  Appropriate constants are stored in nonvolatile memory.                                                                              |

| Calibration interval | Specifications valid within two years of external calibration.                                                                                                                                                          |

| Warm-up time         | 15 minutes                                                                                                                                                                                                              |

### Power

Table 21. Power

|           | Power                           |                                  |

|-----------|---------------------------------|----------------------------------|

|           | Typical Operation <sup>39</sup> | Overload Operation <sup>40</sup> |

| +3.3 V DC | 2 A                             |                                  |

| +5 V DC   | Refer to Figure 13. on page 29. | 2.7 A                            |

| +12 V DC  | 0.46 A                          |                                  |

| -12 V DC  | 0.01 A                          |                                  |

| Total     | 12.2 W + 5 V × 5 V current      | 25.7 W                           |

$<sup>^{39}</sup>$  Typical operation includes the following conditions:

<sup>·</sup> Sine output

Analog filter enabled

<sup>50</sup> Ω termination

<sup>• 200</sup> MS/s High-Resolution Sample Clock

Digital pattern enabled and terminated

Sample Clock routed to PFI 0 and terminated

$<sup>^{40}</sup>$  Occurs when CH 0 is shorted to ground.

Figure 13. 5 V Current Versus Frequency and Amplitude

### **Physical**

| Dimensions | 3U, one-slot, PXI/cPCI module <sup>41</sup><br>21.6 cm × 2.0 cm × 13.0 cm<br>(8.5 in. × 0.8 in. × 5.1 in.) |

|------------|------------------------------------------------------------------------------------------------------------|

| Weight     | 352 g (12.4 oz)                                                                                            |

### **Environment**

| Maximum altitude | 2,000 m (at 25 °C ambient temperature) |

|------------------|----------------------------------------|

| Pollution Degree | 2                                      |

Indoor use only.

<sup>&</sup>lt;sup>41</sup> PXI-5422 modules of revision B or later are equipped with a modified PXI Express-compatible backplane connector. This modified connector allows the PXI-5422 to be supported by hybrid slots in a PXI Express chassis. To determine the revision of a PXI-5422, read the label on the underside of the PXI-5422 module. The label will list an assembly number of the format 191946x-01, where x is the revision.

### **Operating Environment**

| 0 °C to 55 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2.) 0 °C to 45 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2.) when installed in a PXI-101x or PXI-1000B chassis |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10% to 90%, noncondensing (Tested in accordance with IEC 60068-2-56.)                                                                                                                                   |

|                                                                                                                                                                                                         |

| -25 °C to 85 °C (Tested in accordance with IEC 60068-2-1 and IEC 60068-2-2.)                                                                                                                            |

| 5% to 95%, noncondensing (Tested in accordance with IEC 60068-2-56.)                                                                                                                                    |

|                                                                                                                                                                                                         |

|                                                                                                                                                                                                         |

| 30 g peak, half-sine, 11 ms pulse (Tested in accordance with IEC 60068-2-27. Test profile developed in accordance with MIL-PRF-28800F.)                                                                 |

| 50 g peak, half-sine, 11 ms pulse (Tested in accordance with IEC 60068-2-27. Test profile developed in accordance with MIL-PRF-28800F.)                                                                 |

|                                                                                                                                                                                                         |

| 5 Hz to 500 Hz, 0.31 g <sub>rms</sub> (Tested in accordance with IEC 60068-2-64.)                                                                                                                       |

| 5 Hz to 500 Hz, 2.46 $g_{rms}$ (Tested in accordance with IEC 60068-2-64. Test profile exceeds the requirements of MIL-PRF-28800F, Class 3.)                                                            |

|                                                                                                                                                                                                         |

<sup>&</sup>lt;sup>42</sup> Spectral and jitter specifications could degrade.

### Compliance and Certifications

### Safety Compliance Standards

This product is designed to meet the requirements of the following electrical equipment safety standards for measurement, control, and laboratory use:

- IEC 61010-1, EN 61010-1

- UL 61010-1, CSA C22.2 No. 61010-1

**Note** For UL and other safety certifications, refer to the product label or the Product Certifications and Declarations section.

### Electromagnetic Compatibility

This product meets the requirements of the following EMC standards for electrical equipment for measurement, control, and laboratory use:

- EN 61326-1 (IEC 61326-1): Class A emissions; Basic immunity

- EN 55011 (CISPR 11): Group 1, Class A emissions

- AS/NZS CISPR 11: Group 1, Class A emissions

- FCC 47 CFR Part 15B: Class A emissions

- ICES-001: Class A emissions

**Note** In the United States (per FCC 47 CFR), Class A equipment is intended for use in commercial, light-industrial, and heavy-industrial locations. In Europe, Canada, Australia, and New Zealand (per CISPR 11), Class A equipment is intended for use only in heavy-industrial locations.

**Note** Group 1 equipment (per CISPR 11) is any industrial, scientific, or medical equipment that does not intentionally generate radio frequency energy for the treatment of material or inspection/analysis purposes.

**Note** For EMC declarations and certifications, refer to the *Online Product* Certification section.

# CE Compliance ( E

This product meets the essential requirements of applicable European Directives, as follows:

- 2014/35/EU; Low-Voltage Directive (safety)

- 2014/30/EU; Electromagnetic Compatibility Directive (EMC)

#### Product Certifications and Declarations

Refer to the product Declaration of Conformity (DoC) for additional regulatory compliance information. To obtain product certifications and the DoC for NI products, visit ni.com/

*certification*, search by model number or product line, and click the appropriate link in the Certification column.

### **Environmental Management**

NI is committed to designing and manufacturing products in an environmentally responsible manner. NI recognizes that eliminating certain hazardous substances from our products is beneficial to the environment and to NI customers.

For additional environmental information, refer to the *Minimize Our Environmental Impact* web page at *ni.com/environment*. This page contains the environmental regulations and directives with which NI complies, as well as other environmental information not included in this document

### Waste Electrical and Electronic Equipment (WEEE)

X

**EU Customers** At the end of the product life cycle, all NI products must be disposed of according to local laws and regulations. For more information about how to recycle NI products in your region, visit *ni.com/environment/weee*.

#### 电子信息产品污染控制管理办法(中国 RoHS)

**中国客户** National Instruments 符合中国电子信息产品中限制使用某些有害物质指令(RoHS)。关于 National Instruments 中国 RoHS 合规性信息,请登录ni.com/environment/rohs\_china。(For information about China RoHS compliance, go to ni.com/environment/rohs\_china.)

Information is subject to change without notice. Refer to the *NI Trademarks and Logo Guidelines* at ni.com/trademarks for information on NI trademarks. Other product and company names mentioned herein are trademarks or trade names of their respective companies. For patents covering NI products/technology, refer to the appropriate location: Help»Patents in your software, the patents.txt file on your media, or the *National Instruments Patent Notice* at ni.com/patents. You can find information about end-user license agreements (EULAs) and third-party legal notices in the readme file for your NI product. Refer to the *Export Compliance Information* at ni.com/legal/export-compliance for the NI global trade compliance policy and how to obtain relevant HTS codes, ECCNs, and other import/export data. NI MAKES NO EXPRESS OR IMPLIED WARRANTIES AS TO THE ACCURACY OF THE INFORMATION CONTAINED HEREIN AND SHALL NOT BE LIABLE FOR ANY ERRORS. U.S. Government Customers: The data contained in this manual was developed at private expense and is subject to the applicable limited rights and restricted data rights as set forth in FAR 52.227-14, DFAR 252.227-7014, and DFAR 252.227-7015.