#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

Sell For Cash Get Credit Receive a Trade-In Deal

# **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

PXIe-5665

#### CALIBRATION PROCEDURE

# PXIe-5645

### Reconfigurable 6 GHz RF Vector Signal Transceiver with I/Q Interface

This document contains the verification and adjustment procedures for the PXIe-5645 vector signal transceiver.

Refer to *ni.com/calibration* for more information about calibration solutions.

**Caution** Do not disconnect the cable that connects CAL IN to CAL OUT. Removing the cable from or tampering with the CAL IN or CAL OUT front panel connectors voids the product calibration and specifications are no longer warranted.

### Contents

| Required Software                           | 2  |

|---------------------------------------------|----|

| Related Documentation                       | 3  |

| Test Equipment.                             | 3  |

| RF Test Equipment                           | 3  |

| I/Q Test Equipment                          | 11 |

| Test Conditions.                            | 14 |

| Initial Setup                               | 15 |

| RF Test System Characterization.            | 15 |

| Zeroing the Power Sensor                    | 15 |

| Characterizing Power Splitter Balance       |    |

| Characterizing Power Splitter Loss          |    |

| I/Q Test System Characterization            |    |

| I/Q Calibration Fixture Connections         |    |

| Characterizing Relay Impedance              | 33 |

| Characterizing Cable Impedance              | 34 |

| Characterizing Impedance                    |    |

| Characterizing Flatness                     |    |

| Characterizing Matching                     |    |

| Characterizing Gain                         |    |

| Self-Calibrating the PXIe-5645.             |    |

| As-Found and As-Left Limits.                | 39 |

| RF Verification.                            |    |

| Verifying Internal Frequency Reference      |    |

| Verifying RF Input Spectral Purity          |    |

| Verifying RF Output Spectral Purity         |    |

| Verifying Input Absolute Amplitude Accuracy |    |

| Verifying Input Frequency Response          |    |

| Verifying Input Average Noise Density                                 | 53  |

|-----------------------------------------------------------------------|-----|

| Verifying Input Nonharmonic Spurs                                     | 54  |

| Verifying Output Power Level Accuracy                                 | 55  |

| Verifying Output Frequency Response                                   | 59  |

| Verifying Output Noise Density                                        | 62  |

| Verifying Output Second Harmonics                                     | 64  |

| Verifying Output Nonharmonic Spurs                                    | 66  |

| Verifying Third-Order Output Intermodulation (IMD3)                   | 68  |

| Verifying Residual LO Power and Residual Sideband Image               | 70  |

| Verifying RF Input EVM (Functional Test)                              |     |

| Verifying RF Output EVM (Functional Test)                             | 75  |

| Verifying LO OUT (RF IN 0 and RF OUT 0) (Functional Test)             | 76  |

| I/Q Verification                                                      | 78  |

| Verifying I/Q Input DC Gain Error                                     | 78  |

| Verifying I/Q Input DC Offset Error                                   |     |

| Verifying I/Q Input AC Gain Accuracy and Passband Flatness            |     |

| Verifying I/Q Output DC Gain Error                                    |     |

| Verifying I/Q Output DC Offset Error                                  |     |

| Verifying I/Q Output AC Gain Accuracy and Passband Flatness           |     |

| Updating Calibration Date and Time                                    | 87  |

| Optional Verification.                                                |     |

| Verifying RF Input and RF Output Return Loss                          |     |

| Verifying RF Input IMD3 and Second-Order Input Intermodulation (IMD2) |     |

| RF Adjustment                                                         |     |

| Adjusting RF Internal Frequency Reference                             |     |

| Adjusting Input Absolute Amplitude Accuracy                           |     |

| Adjusting Output Power Level Accuracy                                 |     |

| Adjusting LO OUT (RF IN 0 and RF OUT 0)                               |     |

| I/Q Adjustment                                                        |     |

| Adjusting I/Q Input DC Gain                                           |     |

| Adjusting I/Q Input DC Offset                                         |     |

| Adjusting I/Q Input Passband Flatness                                 |     |

| Adjusting I/Q Input Gain and Phase Matching                           |     |

| Adjusting I/Q Input Impedance                                         |     |

| Adjusting I/Q Output Gain and Offset                                  |     |

| Adjusting I/Q Output Passband Flatness                                |     |

| Adjusting I/Q Output Impedance                                        |     |

| EEPROM Update                                                         |     |

| Reverification                                                        |     |

| Worldwide Support and Services                                        | 110 |

# Required Software

Calibrating the PXIe-5645 requires you to install the following software on the calibration system:

- LabVIEW 2012.1 Base/Full/Pro or later

- PXIe-5644/5645 Instrument Design Libraries 2012.1 or later

- NI-RFSA version 2.7 or later

- NI-RFSG version 1.9 or later

- Modulation Toolkit version 4.3.3 or later

- Spectral Measurements Toolkit version 2.6.3 or later

- PXIe-5645 Calibration Fixture API

You can download all required software, other than the PXIe-5645 Calibration Fixture API, from ni.com/downloads.

### **Related Documentation**

For additional information, refer to the following documents as you perform the calibration procedure:

- PXIe-5645 Getting Started Guide

- NI RF Vector Signal Transceivers Help

- PXIe-5645 Specifications

Visit *ni com/manuals* for the latest versions of these documents

# Test Equipment

## RF Test Equipment

National Instruments recommends that you use particular equipment for the RF performance verification and adjustment procedures.

If the recommended equipment is not available, select a substitute using the minimum requirements listed in the following table.

Table 1. Required Equipment Specifications for PXIe-5645 RF Calibration

| Equipment           | Recommended Model                                  | Where Used                                                                                                                                                                                                                                                                                                     | Minimum<br>Requirements                                                                                                                            |

|---------------------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| Frequency reference | Symmetricom 8040<br>Rubidium Frequency<br>Standard | Verifications:  Internal frequency reference  Nonharmonic spurs  Spectral purity  IMD3  IMD2  Output noise density  Output second harmonics  Adjustments:  Absolute amplitude accuracy  Output power level accuracy                                                                                            | Frequency: 10 MHz Frequency accuracy: ≤±1E-9 Output mode: sinusoid                                                                                 |

| Power sensor        | Rohde & Schwarz (R&S)<br>NRP-Z91                   | Test system characterization  Verifications:      Absolute amplitude     accuracy     Frequency response     Output power level     accuracy     LO OUT (RF IN 0     and RF OUT 0)  Adjustments:     Absolute amplitude     accuracy     Output power level     accuracy     LO OUT (RF IN 0     and RF OUT 0) | Range: -67 dBm to<br>+23 dBm  Frequency range: 65 MHz to 6 GHz  Absolute uncertainty: 0.174 dB  Power linearity: <0.1 dB  VSWR: <1.2:1 up to 6 GHz |

Table 1. Required Equipment Specifications for PXIe-5645 RF Calibration (Continued)

| Equipment               | Recommended Model | Where Used                                                                                                                                                                                                                                                                                      | Minimum<br>Requirements                                                                                                        |

|-------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Vector signal generator | PXIe-5673E        | Test system characterization  Verifications:  Internal frequency reference  Absolute amplitude accuracy  Frequency response  Input nonharmonic spurs  Input IMD3  Input EVM  Input IMD2  Adjustments:  Internal frequency reference  Absolute amplitude accuracy  LO OUT (RF IN 0 and RF OUT 0) | Frequency range: 65 MHz to 6 GHz Frequency resolution: <5 Hz Amplitude range: -70 dBm to 5 dBm Instantaneous bandwidth: 50 MHz |

Table 1. Required Equipment Specifications for PXIe-5645 RF Calibration (Continued)

| Equipment                                            | Recommended Model | Where Used                                                                                                                                                                                                                                                         | Minimum<br>Requirements                                                                                      |

|------------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Spectrum<br>analyzer or<br>vector signal<br>analyzer | PXIe-5665         | Test system characterization  Verifications:  Spectral purity  Output power level accuracy  Output frequency response  Output noise density  Output second harmonics  Output nonharmonic spurs  Output IMD3  Output EVM  Adjustments:  Output power level accuracy | Frequency range: 65 MHz to 12 GHz Instantaneous bandwidth: 50 MHz Phase noise at 20 kHz offset: <-125 dBm/Hz |

| Preamplifier                                         | PXI-5691          | Output noise density verification                                                                                                                                                                                                                                  | Frequency range:<br>65 MHz to 8 GHz<br>Noise floor at<br>6 GHz:<br><-158 dBm/Hz                              |

Table 1. Required Equipment Specifications for PXIe-5645 RF Calibration (Continued)

| Equipment                  | Recommended Model               | Where Used                                                                                                                                                                                                   | Minimum<br>Requirements                         |

|----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| Power splitter             | Aeroflex/Weinschel 1593         | Test system characterization                                                                                                                                                                                 | VSWR: ≤1.25:1 up<br>to 18 GHz                   |

|                            |                                 | Verifications:  • Frequency response  • Absolute amplitude accuracy  • Output power level accuracy  Adjustments:  • Absolute amplitude accuracy  • Output power level accuracy                               | Amplitude tracking: <0.25 dB                    |

| 6 dB<br>attenuator<br>(x2) | Anritsu 41KB-6 or Mini-Circuits | Test system characterization  Verifications:  • Frequency response  • Absolute amplitude accuracy  • Output power level accuracy  Adjustments:  • Absolute amplitude accuracy  • Output power level accuracy | Frequency range:<br>DC to 6 GHz<br>VSWR: ≤1.1:1 |

| 50 Ω SMA<br>terminator     | _                               | Test system characterization  Average noise density verification                                                                                                                                             | Frequency range:<br>DC to 6 GHz<br>VSWR: ≤1.1:1 |

Table 1. Required Equipment Specifications for PXIe-5645 RF Calibration (Continued)

| Equipment                       | Recommended Model                 | Where Used                                                                                                                                                                                                                                    | Minimum<br>Requirements                                                   |

|---------------------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| SMA (m)-to-<br>SMA (m)<br>cable | _                                 | All procedures                                                                                                                                                                                                                                | Frequency range:<br>DC to 6 GHz<br>Impedance: 50 Ω                        |

| SMA (m)-to-<br>N (f) adapter    | Huber+Suhner<br>32_SMA_N-50-1/1UE | Test system characterization  Verifications:  • Frequency response  • Absolute amplitude accuracy  • Output power level accuracy  • LO OUT (RF IN 0 and RF OUT 0)  Adjustments:  • Absolute amplitude accuracy  • Output power level accuracy | Frequency range:<br>DC to 6 GHz<br>Impedance: 50 Ω<br>Return loss: ≥23 dB |

| SMA (f)-to-                     | Huber+Suhner                      | LO OUT (RF IN 0 and RF OUT 0)  Test system                                                                                                                                                                                                    | Frequency range:                                                          |

| N (f) adapter                   | 31_N-SMA-50-1/1UE                 | characterization                                                                                                                                                                                                                              | DC to 6 GHz<br>Impedance: 50 Ω<br>Return loss: ≥23 dB                     |

Table 1. Required Equipment Specifications for PXIe-5645 RF Calibration (Continued)

| Equipment                               | Recommended Model                     | Where Used                                                                                                                                                                                                   | Minimum<br>Requirements                                                               |

|-----------------------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|

| 3.5 mm (m)-to-3.5 mm (m) adapter        | Huber+Suhner<br>32_PC35-50-0-2/199_NE | Test system characterization  Verifications:  • Frequency response  • Absolute amplitude accuracy  • Output power level accuracy  Adjustments:  • Absolute amplitude accuracy  • Output power level accuracy | Frequency range:<br>DC to 6 GHz<br>Impedance: 50 Ω<br>Return loss: ≥30 dB             |

| 3.5 mm (f)-<br>to-3.5 mm (f)<br>adapter | Huber+Suhner<br>32_PC35-50-0-1/199_UE | Test system characterization                                                                                                                                                                                 | Frequency range: DC to 6 GHz Impedance: $50 \Omega$ Return loss: $\geq 30 \text{ dB}$ |

The following table lists equipment required to perform optional verification for non warranted RF specifications of the PXIe-5645.

Table 2. Required Equipment Specifications for Optional PXIe-5645 RF Verification

| Equipment                                    | Recommended Model                                  | Where Used               | Minimum Requirements                                                                                          |

|----------------------------------------------|----------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------|

| CW signal generator                          | PXIe-5652                                          | Input IMD3 Input IMD2    | Frequency range: 65 MHz<br>to 6 GHz<br>Frequency resolution:<br><5 Hz<br>Amplitude range: -30 dBm<br>to 0 dBm |

| Power splitter                               | Mini-Circuits<br>ZFRSC-123+                        | Input IMD3 Input IMD2    | >20 dB reverse isolation at 6 GHz                                                                             |

| SMA (m)-to-SMA (m) cable (x2)                | _                                                  | Input IMD3 Input IMD2    | Frequency range: DC to 6 GHz                                                                                  |

| Frequency reference                          | Symmetricom 8040<br>Rubidium Frequency<br>Standard | Input IMD3<br>Input IMD2 | Frequency: 10 MHz Frequency accuracy: ≤±1E-9                                                                  |

| Two-port vector<br>network analyzer<br>(VNA) | PXIe-5630                                          | Return loss              | Frequency range: 65 MHz to 6 GHz                                                                              |

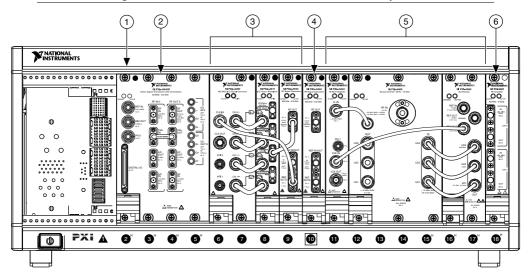

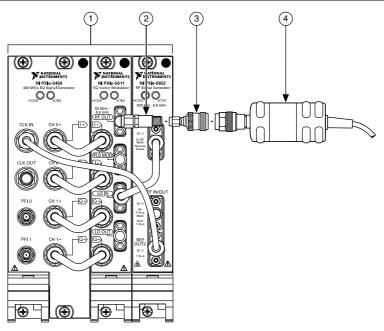

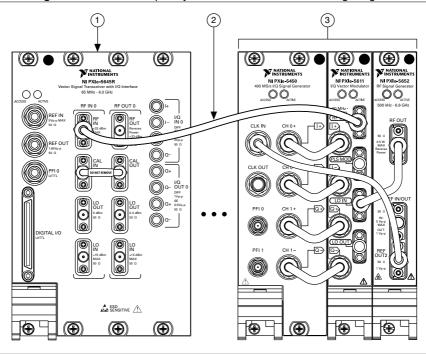

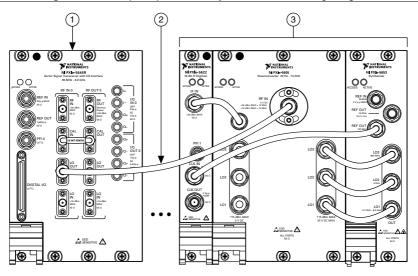

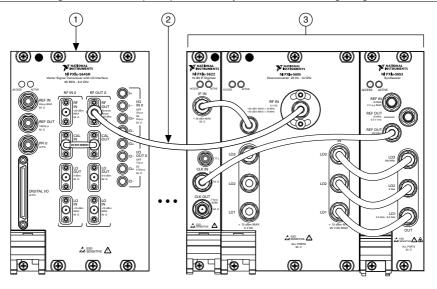

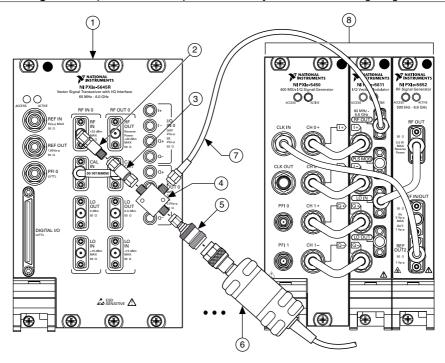

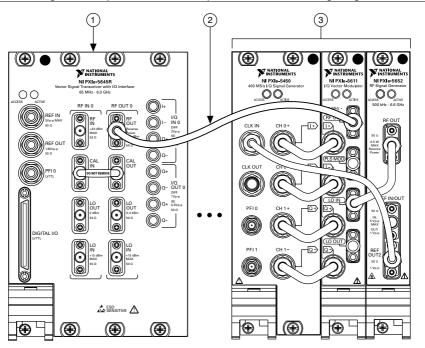

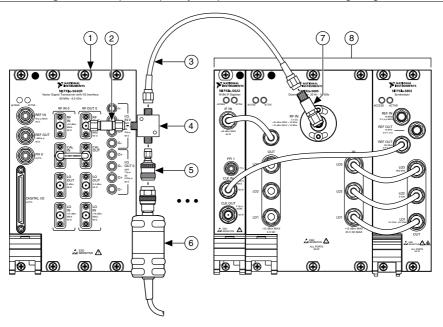

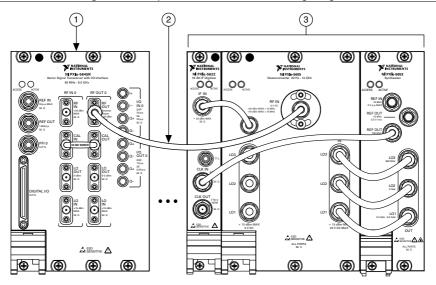

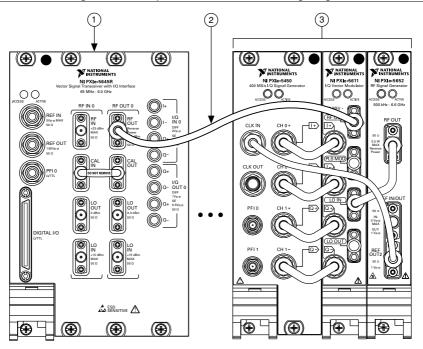

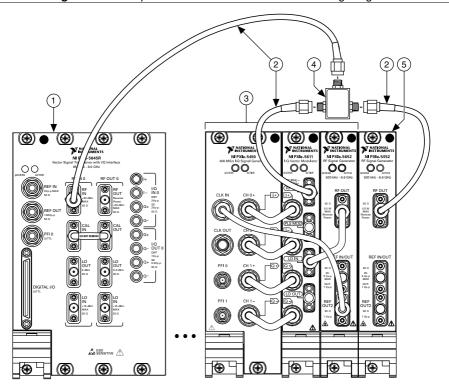

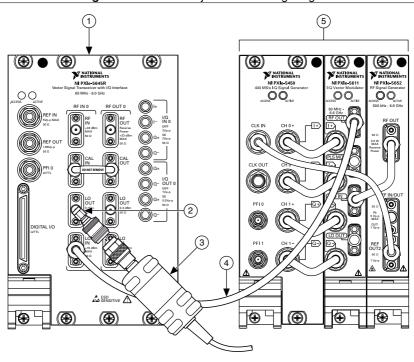

The following figure shows a recommended RF calibration system configuration for the PXIe-5645.

Figure 1. Recommended PXIe-5645 RF Calibration System

- 1. PXIe-1075 Chassis

- 2. Slots 2 through 5: PXIe-5645 (Device Under Test)

- 3. Slots 6 and 7: PXIe-5673E Vector Signal Generator

- 4. Slot 10: PXI-5652 RF Analog Signal Generator and CW Source or PXIe-5652 RF Analog Signal Generator and CW Source

- 5. Slots 11 through 17: PXIe-5665 Vector Signal Analyzer

- 6. Slot 18: PXI-5691 RF Amplifier

### I/Q Test Equipment

National Instruments recommends that you use particular equipment for the I/Q interface performance verification and adjustment procedures.

If the recommended equipment is not available, select a substitute using the minimum requirements listed in the following table.

Table 3. Required Equipment Specifications for PXIe-5645 I/Q Calibration

| Equipment                                                                         | Recommended Model                                                        | Where Used                                                                  | Minimum<br>Requirements                                                                                           |

|-----------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

| (2x) Calibration<br>fixtures; one for<br>verifications,<br>one for<br>adjustments | PXIe-5645 I/Q Calibration<br>Fixture (calibration<br>fixture), 782452-01 | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | _                                                                                                                 |

| Source measure unit (SMU)                                                         | PXI-4130                                                                 | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | DC voltage: 6 V DC current: 2A                                                                                    |

| Relay driver                                                                      | PXI-2567                                                                 | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments |                                                                                                                   |

| Digital<br>multimeter<br>(DMM)                                                    | PXI-4072                                                                 | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | Digits of precision: 6½                                                                                           |

| Power sensor                                                                      | Rohde & Schwarz (R&S)<br>NRP-Z91                                         | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | Range: -67 dBm to<br>+23 dBm<br>Frequency range:<br>65 MHz to 6 GHz<br>Accuracy: 0.5%<br>VSWR: <1.2:1 at<br>6 GHz |

| (8x) MCX (m)-<br>to-SMA (m)<br>cables                                             | 188377-01                                                                | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | Frequency range:<br>DC to 6 GHz<br>Impedance: 50 Ω                                                                |

Table 3. Required Equipment Specifications for PXIe-5645 I/Q Calibration (Continued)

| Equipment                         | Recommended Model                  | Where Used                                                                  | Minimum<br>Requirements                                                      |

|-----------------------------------|------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 78-pin DSUB cable                 | Included with relay driver module  | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | _                                                                            |

| (2x) SMA (m)-<br>to-N (f) adapter | Huber+Suhner<br>32_SMA_N-50-1/1UE  | I/Q test system<br>characterization<br>I/Q verifications<br>I/Q adjustments | Frequency range:<br>DC to 6 GHz<br>Impedance: 50 Ω<br>Return loss:<br>≥23 dB |

| (3x) MCX terminations             | Johnson Components<br>133-3801-801 | I/Q test system characterization                                            | Impedance: 50 Ω Frequency range: DC to 1 GHz                                 |

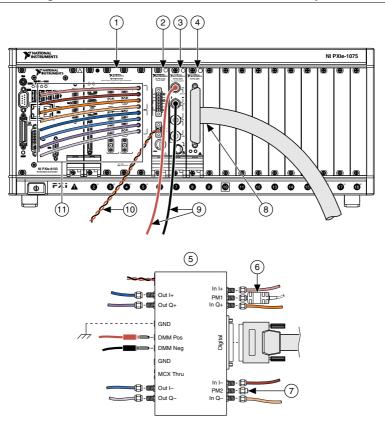

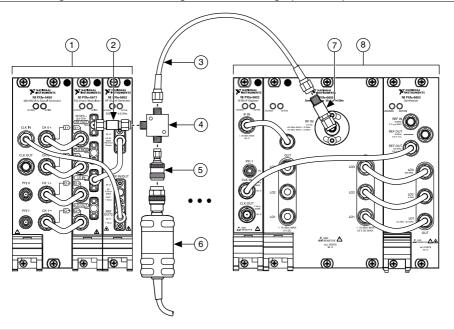

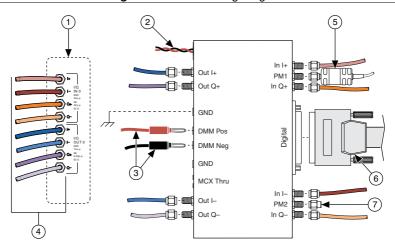

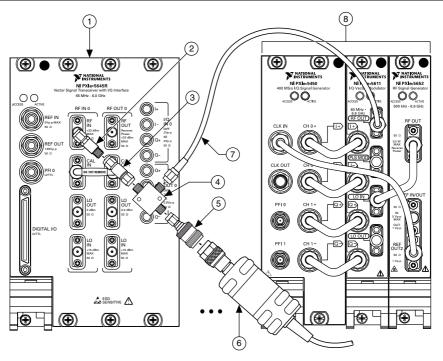

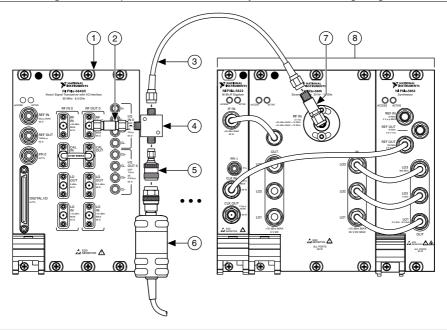

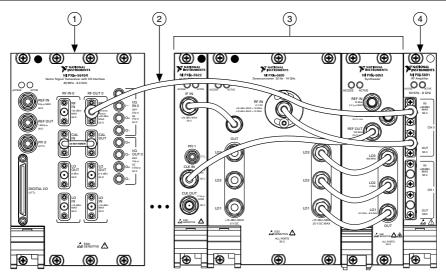

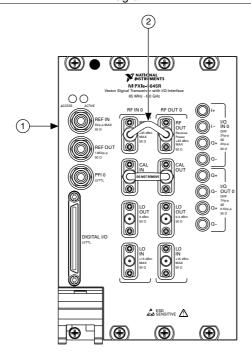

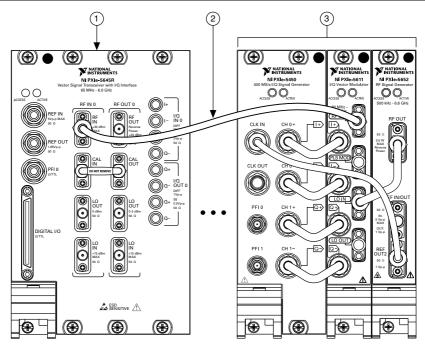

I/Q verification procedures and I/Q adjustment procedures each use a different calibration fixture; however, the calibration system configuration is identical for both verification and adjustment. The following figure shows a recommended PXIe-5645 I/Q calibration system.

Figure 2. Recommended PXIe-5645 I/Q Calibration System

- 1. PXIe-5645

- 2. PXI-4130 SMU

- 3. PXI-4072 DMM

- 4. PXI-2567 Relay Driver

- 5. PXIe-5645 I/Q Calibration Fixture (one of two)

- 6. Power Meter 1

- 7. MCX Termination

- 8. 78-Pin D-SUB Cable

- 9. Banana Cables

- 10. Twisted-Pair Cable

- 11. MCX (m)-to-SMA (m) Cables

### **Test Conditions**

The following setup and environmental conditions are required to ensure the PXIe-5645 meets published specifications.

- Keep cabling as short as possible. Long cables act as antennas, picking up extra noise that can affect measurements.

- Verify that all connections to the PXIe-5645, including front panel connections and screws, are secure.

- Maintain an ambient temperature of 23 °C  $\pm$  5 °C.

- Keep relative humidity between 10% and 90%, noncondensing.

- Allow a warm-up time of at least 30 minutes after the chassis is powered on and PXIe-5644/5645 Instrument Design Libraries is loaded and recognizes the PXIe-5645. The warm-up time ensures that the PXIe-5645 and test instrumentation are at a stable operating temperature.

- In each verification procedure, insert a delay between configuring all devices and acquiring the measurement. This delay may need to be adjusted depending on the instruments used but should always be at least 1,000 ms for the first iteration, 1,000 ms when the power level changes, and 100 ms for each other iteration.

- Ensure that the PXI chassis fan speed is set to HIGH, that the fan filters, if present, are clean, and that the empty slots contain filler panels. For more information about cooling, refer to the Maintain Forced-Air Cooling Note to Users document available at ni.com/ manuals.

# **Initial Setup**

Refer to the PXIe-5645 Getting Started Guide for information about how to install the software and the hardware and how to configure the device in Measurement & Automation Explorer (MAX).

# RF Test System Characterization

The following procedures characterize the test equipment used during RF verification and RF adjustment.

**Caution** The connectors on the device under test (DUT) and test equipment are fragile. Perform the steps in these procedures with great care to prevent damaging any DUTs or test equipment.

# Zeroing the Power Sensor

- 1. Ensure that the power sensor is not connected to any signals.

- Zero the power sensor using the built-in function, according to the power sensor documentation

### Characterizing Power Splitter Balance

You must zero the power sensor as described in the Zeroing the Power Sensor section prior to starting this procedure.

This procedure characterizes the balance between the two output terminals of the splitter. where the second terminal is terminated into an attenuator. The following procedures require the power splitter balance data:

- Verifying Input Absolute Amplitude Accuracy

- Verifying Input Frequency Response

- Adjusting Input Absolute Amplitude Accuracy

The verification and adjustment procedures use different test points for the splitter balance characterization. For characterization used in a verification procedure, use the test points in the Characterization Test Points for Verification Procedures table. For characterization used in an adjustment procedure, use 65 MHz to 6 GHz in 5 MHz steps for the test points.

- Connect the SMA (m) connector of the 6 dB attenuator to the RF OUT front panel 1. connector of the vector signal generator.

- 2. Connect the SMA (f) connector of the 6 dB attenuator to the input port of the power splitter using an SMA (m)-to-SMA (m) cable.

- 3. Connect the 50  $\Omega$  (m) terminator to one of the power splitter output ports. Refer to this port as *splitter output 1*.

- Connect the other power splitter output to the SMA (f) connector of the second 6 dB 4. attenuator using a 3.5 mm (m)-to-3.5 mm (m) adapter. Refer to the combined power splitter output and 6 dB attenuator as splitter output 2.

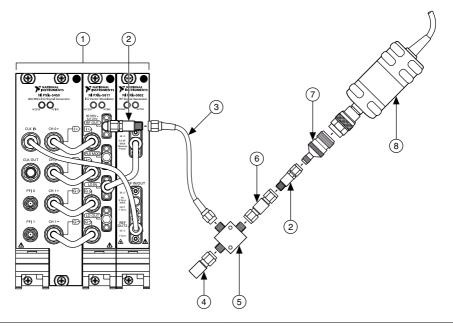

- 5. Connect the power sensor to splitter output 2 using the SMA (f)-to-N (f) adapter. The following figure illustrates the hardware setup.

Figure 3. Connection Diagram for Measuring at Splitter Output 2

- 1. Vector Signal Generator

- 2. 6 dB Attenuator

- 3. SMA (m)-to-SMA (m) Cable

- 4. 50 Ω Terminator

- 5. Power Splitter

- 6. 3.5 mm (m)-to-3.5 mm (m) Adapter

- 7. SMA (f)-to-N (f) Adapter

- 8. Power Sensor

- Configure the vector signal generator using the following settings: 6.

- Center frequency: For characterization used in a verification procedure, use the first test point in the following table. For characterization used in an adjustment procedure, use 65 MHz. For either procedure type, store as *frequency*.

- Power level: 0 dBm

Table 4. Characterization Test Points for Verification Procedures

| Test Points (MHz) | Step Size (MHz) |

|-------------------|-----------------|

| 80 to 100         | 5               |

| 250               | _               |

| 290 to 310        | 5               |

| 350 to 400        | 50              |

| 410 to 490        | 5               |

| 500               | _               |

Table 4. Characterization Test Points for Verification Procedures (Continued)

| Test Points (MHz) | Step Size (MHz) |

|-------------------|-----------------|

| 510 to 690        | 5               |

| 700 to 750        | 50              |

| 760 to 840        | 5               |

| 850 to 900        | 50              |

| 910 to 1,090      | 5               |

| 1,160 to 1,240    | 5               |

| 1,400             | _               |

| 1,510 to 1,690    | 5               |

| 1,800             | _               |

| 1,960 to 2,040    | 5               |

| 2,200 to 2,600    | 200             |

| 2,610 to 2,790    | 5               |

| 2,800             | _               |

| 2,960 to 3,040    | 5               |

| 3,200 to 3,600    | 200             |

| 3,760 to 3,840    | 5               |

| 3,910 to 4,090    | 5               |

| 4,200             | _               |

| 4,460 to 4,540    | 5               |

| 4,600 to 4,800    | 200             |

| 4,910 to 5,090    | 5               |

| 5,200 to 5,400    | 200             |

| 5,460 to 5,540    | 5               |

| 5,600 to 5,800    | 200             |

| 5,910 to 5,990    | 5               |

| 6,000             | _               |

<sup>7.</sup> Configure the power sensor to correct for *frequency* using the power sensor frequency correction function.

<sup>8.</sup> Use the power sensor to measure the power at the *frequency* from step 6.

Repeat steps 6 through 8 by updating frequency. For characterization used in a verification procedure, use the test points in the *Characterization Test Points for* Verification Procedures table. For characterization used in an adjustment procedure, use 65 MHz to 6 GHz in 5 MHz steps for the test points.

Record the resulting measurements as *splitter output 2 power*. Each frequency should have a corresponding value.

- 10. Disconnect the power sensor and 50  $\Omega$  terminator from the power splitter.

- 11. Connect the power sensor to splitter output 1 using an SMA (m)-to-N (f) adapter.

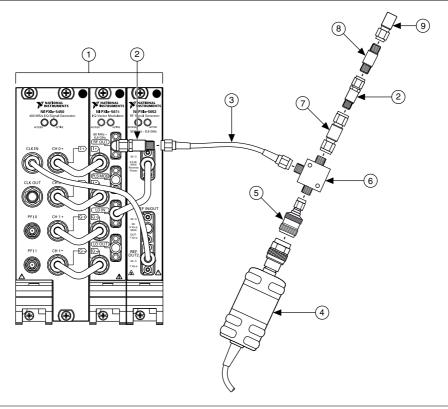

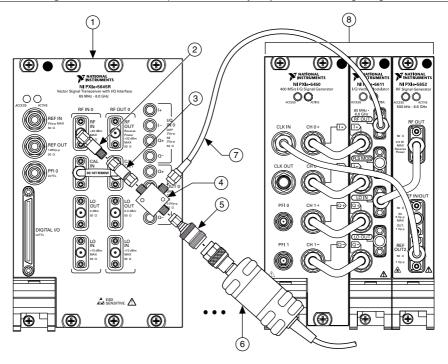

- 12. Connect the 50  $\Omega$  terminator to splitter output 2 using an SMA (f)-to-SMA (f) adapter. The following figure illustrates the hardware setup.

Figure 4. Connection Diagram for Measuring at Splitter Output 1

- 1. Vector Signal Generator

- 2. 6 dB Attenuator

- 3. SMA (m)-to-SMA (m) Cable

- 4. Power Sensor

- 5. SMA (m)-to-N (f) Adapter

- 6. Power Splitter

- 7. 3.5 mm (m)-to-3.5 mm (m) Adapter

- 8. 3.5 mm (f)-to-3.5 mm (f) Adapter

- 9. 50 Ω Terminator

- 13. Configure the vector signal generator using the following settings:

- Center frequency: For characterization used in a verification procedure, use the first test point in the Characterization Test Points for Verification Procedures table. For characterization used in an adjustment procedure, use 65 MHz. For either procedure type, store as frequency.

- Power level: 0 dBm

- 14. Configure the power sensor to correct for *frequency* using the power sensor frequency correction function.

- 15. Use the power sensor to measure the power.

- 16. Repeat steps 13 through 15 by updating frequency. For characterization used in a verification procedure, use the test points in the *Characterization Test Points for* Verification Procedures table. For characterization used in an adjustment procedure, use 65 MHz to 6 GHz in 5 MHz steps for the test points.

- Record the resulting measurements as splitter output 1 power. Each frequency should have a corresponding value.

- 17. Calculate the splitter balance for each frequency point using the following equation: splitter balance = splitter output 2 power - splitter output 1 power

### Characterizing Power Splitter Loss

This procedure characterizes the loss through the power splitter.

You must zero the power sensor as described in the Zeroing the Power Sensor section prior to starting this procedure.

The following procedures require the power splitter loss data:

- Verifying Output Power Level Accuracy

- Verifying Output Frequency Response

- Adjusting Output Power Level Accuracy

The verification and adjustment procedures use different test points for the splitter loss characterization. For characterization used in a verification procedure, use the test points in the Characterization Test Points for Verification Procedures table. For characterization used in an adjustment procedure, use 65 MHz to 6 GHz in 5 MHz steps for the test points.

- Connect the SMA (m) connector of the 6 dB attenuator to the RF OUT front panel connector of the vector signal generator.

- Connect the SMA (f) connector of the 6 dB attenuator to the power sensor using an SMA 2. (m)-to-N (f) adapter.

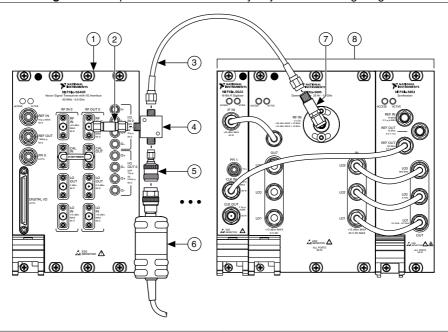

Figure 5. Connection Diagram for Measuring Splitter Input Power

- 1. Vector Signal Generator

- 2. 6 dB Attenuator

- 3. SMA (m)-to-N (f) Adapter

- 4. Power Sensor

- 3. Configure the vector signal generator to generate a tone using the following settings:

- Center frequency: For characterization used in a verification procedure, use the first test point in the Characterization Test Points for Verification Procedures table in the Characterizing Power Splitter Balance section. For characterization used in an adjustment procedure, use 65 MHz.

- Power level: Configured output power from transfer function A in the following table.

- Tone offset: 3.75 MHz

Table 5. Accuracy Transfer Definitions

| Transfer<br>Function | Supported Output<br>Power Level (dBm) | Configured Output<br>Power (dBm) | Configured<br>Reference Level<br>(dBm) |

|----------------------|---------------------------------------|----------------------------------|----------------------------------------|

| A                    | +10 to -20                            | 0                                | 10                                     |

| В                    | -20 to -40                            | -15                              | -30                                    |

- Configure the power sensor to correct for the center frequency from step 3 using the 4. power sensor frequency correction function.

- 5. Use the power sensor to measure the output power.

- 6. Repeat steps 3 through 5 for the remaining frequencies. For characterization used in a verification procedure, use the test points from the *Characterization Test Points for* Verification Procedures table in the Characterizing Power Splitter Balance section. For characterization used in an adjustment procedure, use 65 MHz to 6 GHz in 5 MHz steps for the test points.

- Record the resulting measurements as splitter input power. Each frequency should have a corresponding value.

- 7. Disconnect the power sensor from the 6 dB attenuator.

- 8. Connect the power splitter input port to the SMA (f) port of the 6 dB attenuator using an SMA (m)-to-SMA (m) adapter.

- 9. Connect the power sensor to one of the splitter output ports using the SMA (m)-to-N (f) adapter.

- Refer to this port as *splitter output 1* for the remainder of this procedure and all tests that use the resulting characterization data.

- 10. Connect the other output of the power splitter to the SMA (f) connector of a second 6 dB attenuator using an SMA (m)-to-SMA (m) cable.

- 11. Connect the SMA (m) connector of the second 6 dB attenuator to the RF IN front panel port of the spectrum analyzer.

- Refer to this port as *splitter output 2* for the remainder of this procedure and all tests that use the resulting characterization data.

- The following figure illustrates the hardware setup.

Figure 6. Connection Diagram for Measuring Splitter Output 1 Power

- 1. Vector Signal Generator

- 2. 6 dB Attenuator

- 3. SMA (m)-to-SMA (m) Adapter

- 4. Power Splitter

- 5. SMA (m)-to-N (f) Adapter

- 6. Power Sensor

- 7. SMA (m)-to-SMA (m) Cable

- 8. Spectrum Analyzer

**Note** If you use the PXIe-5665, as recommended, for the spectrum analyzer, disable the preamplifier and preselector options and set the FFT window type to Flat Top.

- 12. Configure the vector signal generator to generate a tone using the following settings:

- Center frequency: Center frequency from step 3.

- Power level: Configured output power from transfer function A in the Accuracy Transfer Definitions table.

- 13. Configure the spectrum analyzer using the following settings:

- Center frequency: Center frequency of the vector signal generator + tone offset from step 3.

- Reference level: Configured reference level from transfer function A in the Accuracy Transfer Definitions table.

- Span: 250 kHz

- Resolution bandwidth: 4 kHz

- Averaging mode: RMS

- Number of averages: 10

- 14. Use the spectrum analyzer to acquire the signal.

- 15. Measure the peak output power present in the signal from step 14. Store this value as splitter output 2 power.

- 16. Configure the power sensor to correct for the frequency from step 12 using the power sensor frequency correction function.

- 17. Use the power sensor to measure the output power. Store this value as *splitter output 1* power.

- 18. Repeat steps 12 through 17 for the remaining frequencies. For characterization used in a verification procedure, use the test points from the Characterization Test Points for Verification Procedures table in the Characterizing Power Splitter Balance section. For characterization used in an adjustment procedure, use 65 MHz to 6 GHz in 5 MHz steps for the test points.

- 19. Repeat steps 12 through 18 for transfer function B from the Accuracy Transfer Definitions table.

- 20. Calculate a table of splitter loss values for each frequency of each transfer function using the following equation:

```

splitter loss = splitter output 1 power - splitter input power

Store the results in a Splitter Loss table.

```

21. Calculate the accuracy transfer result for each frequency of each transfer function using the following equation:

```

accuracy transfer result = splitter output 1 - splitter output 2

Store the results in an RF Output Transfer Result table.

```

# I/Q Test System Characterization

The following procedures characterize the I/Q calibration fixtures used during I/Q verification and I/Q adjustment.

I/O verification procedures and I/O adjustment procedures each use a different calibration fixture; however, the characterization is identical for both calibration fixtures. The I/Q calibration fixture characterization produces data required to perform verifications and adjustments. You must characterize the designated I/Q calibration fixture once, prior to performing all verifications or adjustments.

The I/O calibration fixture characterization procedures automatically execute for the permutations of calibration fixture settings defined in the following tables. For each procedure, actions are performed based on the current permutation. For example, for each physical connection, iterate through all signal path configurations, for each signal path configuration, iterate through all terminations, and so on. The following list shows the hierarchy of settings.

- Iterate physical connection

- Iterate signal path configuration

- Iterate termination

- Iterate DMM source

Table 6. Physical Connection Iterations

| Iteration | Physical Connection                          |

|-----------|----------------------------------------------|

| 0         | Power meter direct                           |

| 1         | No connect                                   |

| 2         | No connect (cable measurements) <sup>1</sup> |

| 3         | Power meter to I                             |

| 4         | Power meter to Q                             |

| 5         | Swapped <sup>2</sup>                         |

| 6         | Thru <sup>3</sup>                            |

Table 7. Signal Path Configuration Iterations

| Iteration | Signal Path | Terminal Configuration |

|-----------|-------------|------------------------|

| 0         | No connect  | Single-ended           |

| 1         | No connect  | Differential           |

| 2         | Terminated  | Differential           |

| 3         | Terminated  | Single-ended           |

| 4         | Inline      | Single-ended           |

| 5         | Inline      | Differential           |

| 6         | Cross       | Differential           |

| 7         | Cross       | Single-ended           |

| 8         | Absolute I  | Single-ended           |

| 9         | Absolute I  | Differential           |

| 10        | Absolute Q  | Differential           |

| 11        | Absolute Q  | Single-ended           |

| 12        | Splitter I  | Single-ended           |

| 13        | Splitter I  | Differential           |

$<sup>\</sup>begin{array}{ll} ^{1} & \text{Use this connection only for the cable impedance characterization.} \\ ^{2} & \text{PXIe-5645 I+/- input to Q+/- output and Q+/- input to I+/- output.} \\ ^{3} & \text{PXIe-5645 I+/- input to I+/- output and Q+/- input to Q+/- output.} \\ \end{array}$

Table 7. Signal Path Configuration Iterations (Continued)

| Iteration | Signal Path | Terminal Configuration |

|-----------|-------------|------------------------|

| 14        | Splitter Q  | Differential           |

| 15        | Splitter Q  | Single-ended           |

Table 8. Termination Iterations

| Iteration | Termination          |

|-----------|----------------------|

| 0         | False (unterminated) |

| 1         | True (terminated)    |

Table 9. DMM Source Iterations

| Iteration | DMM Source               |

|-----------|--------------------------|

| 0         | None differential        |

| 1         | None single-ended        |

| 2         | I In differential        |

| 3         | I In single-ended        |

| 4         | Q In differential        |

| 5         | Q In single-ended        |

| 6         | I Out differential       |

| 7         | I Out single-ended       |

| 8         | Q Out differential       |

| 9         | Q Out single-ended       |

| 10        | Power meter differential |

| 11        | Power meter single-ended |

| 12        | I to I+                  |

| 13        | I to Q+                  |

| 14        | I to power meter+        |

| 15        | I to I-                  |

| 16        | I to Q-                  |

| 17        | I to power meter-        |

**Table 9.** DMM Source Iterations (Continued)

| Iteration | DMM Source        |

|-----------|-------------------|

| 18        | Q to I+           |

| 19        | Q to Q+           |

| 20        | Q to power meter+ |

| 21        | Q to I-           |

| 22        | Q to Q-           |

| 23        | Q to power meter- |

### I/Q Calibration Fixture Connections

Specific calibration fixture connections vary according to the current iteration of the I/Q calibration fixture characterization procedure.

The following cabling diagrams correspond to the iteration values for *Physical Connection* in the Physical Connection Iterations table in the I/Q Test System Characterization section.

#### **Power Meter Direct Connections**

- Connect power meter 1 to I+ (I/Q OUT 0) on the PXIe-5645.

- 2. Connect an MCX termination to I- (I/Q OUT 0) on the PXIe-5645.

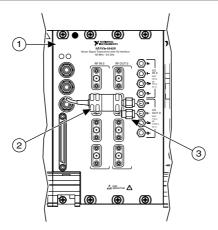

Figure 7. Power Meter Direct Cabling Diagram

- 1. PXIe-5645

- 2. Power Meter 1

- 3. MCX Termination

#### No Connect Connections

- Connect the PXI-4130 to the calibration fixture.

- 2 Connect the PXI-4072 to the DMM Pos and DMM Neg connectors on the calibration fixture.

- 3 Connect the PXI-2567 to the Digital connector on the calibration fixture.

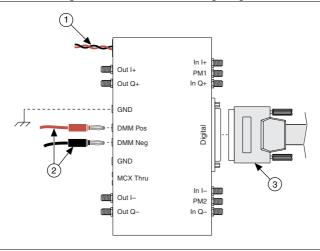

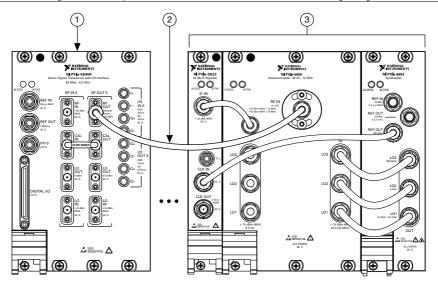

The following figure illustrates the hardware setup.

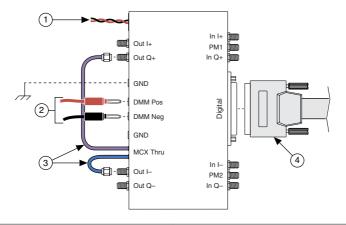

Figure 8. No Connect Cabling Diagram

- 1. PXI-4130 Connection

- 2. PXI-4072 Connection

- 3. PXI-2567 Connection

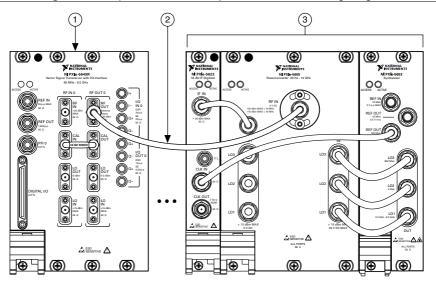

#### Cable Measurements Connections

- 1. Connect the PXI-4130 to the calibration fixture.

- 2. Connect the PXI-4072 to the DMM Pos and DMM Neg connectors on the calibration fixture.

- Connect an MCX (m)-to-SMA (m) cable from the Out Q+ connector to the nearest MCX 3. Thru connector on the calibration fixture.

- 4. Connect an MCX (m)-to-SMA (m) cable from the Out I- connector to the nearest MCX Thru connector on the calibration fixture.

- 5. Connect the PXI-2567 to the Digital connector on the calibration fixture.

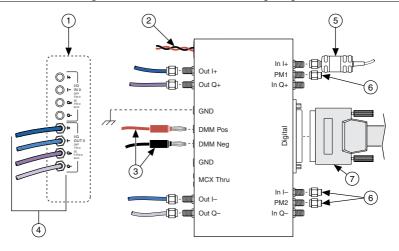

Figure 9. Cable Measurements Cabling Diagram

- 1. PXI-4130 Connection

- 2. PXI-4072 Connection

- 3. MCX (m)-to-SMA (m) Cable Connections

- 4. PXI-2567 Connection

#### Power Meter to I Connections

- Connect the PXI-4130 to the calibration fixture.

- 2. Connect the PXI-4072 to the DMM Pos and DMM Neg connectors on the calibration fixture.

- 3. Connect Out I+ on the calibration fixture to I+ (I/Q OUT 0) on the PXIe-5645.

- Connect Out Q+ on the calibration fixture to Q+ (I/Q OUT 0) on the PXIe-5645. 4.

- 5. Connect Out I- on the calibration fixture to I- (I/Q OUT 0) on the PXIe-5645.

- 6. Connect Out Q- on the calibration fixture to Q- (I/Q OUT 0) on the PXIe-5645.

- Connect power meter 1 to In I+ on the calibration fixture. 7.

- Connect MCX terminations to PM1, In I-, and PM2 on the calibration fixture. 8.

- Connect the PXI-2567 to the Digital connector on the calibration fixture. 9.

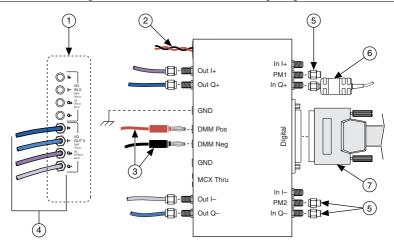

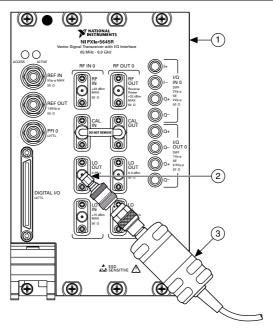

Figure 10. Power Meter to I Cabling Diagram

- 1. Zoomed View of PXIe-5645 I/Q Connectors

- 2. PXI-4130 Connection

- 3. PXI-4072 Connection

- 4. MCX (m)-to-SMA (m) Cables

- 5. Power Meter 1

- 6. MCX Terminations

- 7. PXI-2567 Connection

#### Power Meter to Q Connections

- Connect the PXI-4130 to the calibration fixture.

- 2 Connect the PXI-4072 to the DMM Pos and DMM Neg ports of the calibration fixture.

- 3. Connect I+ (I/Q OUT 0) on the PXIe-5645 to Out I+ on the calibration fixture.

- 4. Connect O+ (I/O OUT 0) on the PXIe-5645 to Out O+ on the calibration fixture.

- 5. Connect I- (I/Q OUT 0) on the PXIe-5645 to Out I- on the calibration fixture.

- 6. Connect O- (I/O OUT 0) on the PXIe-5645 to Out O- on the calibration fixture.

- 7. Connect power meter 1 to In Q+ on the calibration fixture.

- 8. Connect MCX terminations to PM1, PM2, and In O- on the calibration fixture.

- 9. Connect the PXI-2567 to the Digital connector on the calibration fixture.

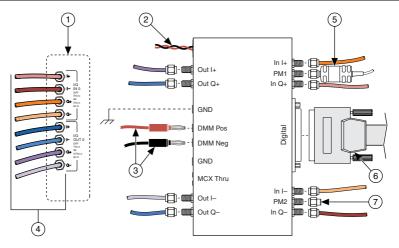

Figure 11. Power Meter to Q Cabling Diagram

- 1. Zoomed View of PXIe-5645 I/Q Connectors

- 2. PXI-4130 Connection

- 3. PXI-4072 Connection

- 4. MCX (m)-to-SMA (m) Cables

- 5. MCX Terminations

- 6. Power Meter 1

- 7. PXI-2567 Connection

#### Swapped Connections

- Connect the PXI-4130 to the calibration fixture.

- 2. Connect the PXI-4072 to the DMM Pos and DMM Neg connectors on the calibration fixture.

- 3. Connect I+ (I/Q IN 0) on the PXIe-5645 to In Q+ on the calibration fixture.

- 4 Connect I- (I/Q IN 0) on the PXIe-5645 to In I- on the calibration fixture.

- 5. Connect O+ (I/O IN 0) on the PXIe-5645 to In I+ on the calibration fixture.

- Connect Q- (I/Q IN 0) on the PXIe-5645 to In Q- on the calibration fixture. 6

- Connect I+ (I/Q OUT 0) on the PXIe-5645 to Out Q+ on the calibration fixture. 7.

- 8. Connect I- (I/Q OUT 0) on the PXIe-5645 to Out Q- on the calibration fixture.

- Connect Q+ (I/Q OUT 0) on the PXIe-5645 to Out I+ on the calibration fixture. 9.

- 10. Connect O- (I/O OUT 0) on the PXIe-5645 to Out I- on the calibration fixture.

- 11. Connect power meter 1 to PM1 on the calibration fixture.

- 12. Connect an MCX termination to PM2 on the calibration fixture.

- 13. Connect the PXI-2567 to the Digital connector on the calibration fixture.

Figure 12. Swapped Cabling Diagram

- 1. Zoomed View of PXIe-5645 I/Q Connectors

- 2. PXI-4130 Connection

- 3. PXI-4072 Connection

- 4. MCX (m)-to-SMA (m) Cables

- 5. Power Meter 1

- 6. PXI-2567 Connection

- 7. MCX Termination

#### Thru Connections

- Connect the PXI-4130 to the calibration fixture.

- 2 Connect the PXI-4072 to the DMM Pos and DMM Neg connectors on the calibration fixture.

- 3 Connect I+ (I/Q IN 0) on the PXIe-5645 to In I+ on the calibration fixture.

- 4. Connect I- (I/O IN 0) on the PXIe-5645 to In I- on the calibration fixture.

- 5. Connect Q+ (I/Q IN 0) on the PXIe-5645 to In Q+ on the calibration fixture.

- 6 Connect Q- (I/Q IN 0) on the PXIe-5645 to In Q- on the calibration fixture.

- 7. Connect I+ (I/O OUT 0) on the PXIe-5645 to Out I+ on the calibration fixture.

- 8 Connect I- (I/Q OUT 0) on the PXIe-5645 to Out I- on the calibration fixture.

- 9. Connect O+ (I/O OUT 0) on the PXIe-5645 to Out O+ on the calibration fixture.

- 10. Connect Q- (I/Q OUT 0) on the PXIe-5645 to Out Q- on the calibration fixture.

- 11. Connect power meter 1 to PM1 on the calibration fixture.

- 12. Connect an MCX termination to PM2 on the calibration fixture.

- 13. Connect the PXI-2567 to the Digital connector on the calibration fixture.

Figure 13. Thru Cabling Diagram

- 1. Zoomed View of PXIe-5645 I/Q Connectors

- 2. PXI-4130 Connection

- 3. PXI-4072 Connection

- 4. MCX (m)-to-SMA (m) Cables

- Power Meter 1

- 6. PXI-2567 Connection

- 7. MCX Termination

### Characterizing Relay Impedance

This procedure measures the resistance of each relay pair of the I/Q calibration fixture for a given measurement.

- If the current iteration has the following values, continue to step 2. Otherwise, proceed to the next characterization.

- Connection configuration: No connect

- Signal path: No connection or terminated

- Terminal configuration: Differential or single-ended

- DMM source: I In, I Out, Q In, or Q Out

- Ensure the calibration fixture is connected to the appropriate instrumentation based on the value of *connection configuration* in step 1 for the current iteration.

- 3. Use the following settings to configure the DMM for impedance measurements:

Function: 2-wire resistance

Digits of precision: 6 1/2

Range: 150 Ω

Aperture: 0.1 seconds

Auto zero: On

Offset compensated Ohms: On

Number of averages: 1

Powerline frequency: 60 Hz

- 4. Call the InitializeRelayCal VI and configure it using the following parameters:

- connection: Current iteration value for connection configuration

- **signal path**: Current iteration value for *signal path*

- terminal configuration: Current iteration value for terminal configuration

- **DMM source name**: Current iteration value for *DMM source*

- 5. Configure the I/Q calibration fixture based on the **IQ cal fixture cal** output of the IntializeRelayCal VI in step 4.

- 6. Measure the impedance using the DMM.

- 7. Pass the following values to the AdjustRelayCal VI:

- relay measurement type: relay measurement type output of the IntializeRelayCal VI in step 4

- **impedance**: Impedance value from step 6

### Characterizing Cable Impedance

This procedure removes the impedance of each of the connected cables and measures impedance of the cable pairs I Out, Q Out, I In, and Q In.

- 1. If the current iteration has the following values, continue to step 2. Otherwise, proceed to the next characterization.

- Connection configuration: No connect

- Signal path: No connection

- Terminal configuration: N/A

- DMM source: I In, I Out, Q In, or Q Out

- 2. Ensure the calibration fixture is connected to the appropriate instrumentation based on the value of *connection configuration* in step 1 for the current iteration.

- 3. Use the following settings to configure the DMM for impedance measurements:

- Function: 2-wire resistance

- Digits of precision: 6 1/2

- Range: 150 Ω

- Aperture: 0.1 seconds

- Auto zero: On

- Offset compensated Ohms: On

- Number of averages: 1

- Powerline frequency: 60 Hz

- 4. Call the InitializeCableCal VI and configure it using the following parameters:

- **connection**: Current iteration value for *connection configuration*

- **signal path**: Current iteration value for *signal path*

- **terminal configuration**: Current iteration value for *terminal configuration*

- DMM source name: Current iteration value for DMM source

- 5. Configure the I/Q calibration fixture based on the **IQ cal fixture cal** output of the IntializeCableCal VI in step 4.

- 6. Measure the impedance using the DMM.

- 7. Pass the impedance value from step 6 to the **impedance** input of the AdjustCableCal VI.

Repeat steps 2 through 7 for the remaining cable pairs: Q Out+/Q Out-, I In+/I In-, and Q In+/Q In -.

### Characterizing Impedance

This procedure measures the impedance for the input and output ports of the PXIe-5645 I/O calibration fixture.

- If the current iteration has the following values, continue to step 2, otherwise proceed to the next characterization.

- Connection configuration: Thru

- Signal path: No connection, inline, cross, absolute I, absolute Q, splitter I to I and power meter, or splitter I to Q and power meter

- Terminal configuration: Differential or single-ended

- DMM source: I In, I Out, Q In, or Q Out

- 2. Ensure the calibration fixture is connected to the appropriate instrumentation based on the value of *connection configuration* in step 1 for the current iteration.

- 3. Use the following settings to configure the DMM for impedance measurements:

- Function: 2-wire resistance

- Digits of precision: 6 1/2

- Range:  $150 \Omega$

- Aperture: 0.1 seconds

- Auto zero: On

- Offset compensated Ohms: On

- Number of averages: 1

- Powerline frequency: 60 Hz

- Call the InitializeImpedanceCal VI and configure it using the following parameters:

- **connection**: Current iteration value for *connection configuration*

- signal path: Current iteration value for signal path

- terminal configuration: Current iteration value for terminal configuration

- **DMM source name**: Current iteration value for *DMM source*

- 5. Configure the I/Q calibration fixture based on the IQ cal fixture cal output of the IntializeImpedanceCal VI in step 4.

- Measure the impedance using the DMM. 6.

- Pass the impedance value from step 6 to the **impedance** input of the AdjustCableCal VI. 7.

- 8. Repeat steps 3 through 7 for the remaining cable pairs: O Out+/O Out-, I In+/I In-, and Q In+/Q In -.

### Characterizing Flatness

This procedure measures the flatness of the PXIe-5645 I/Q calibration fixture.

- 1. If the current iteration has the following values, continue to step 2, otherwise proceed to the next characterization

- Connection configuration:

- Power meter on I Out

- Power meter on I In

- Power meter on O In

- Swapped

- Thru

- Signal path:

- Inline

- Cross

- Absolute I

- Absolute O

- Splitter I to I and power meter

- Splitter I to Q and power meter

- Terminal configuration: Differential or single-ended

- DMM source: None

- 2. Ensure the calibration fixture is connected to the appropriate instrumentation based on the value of *connection configuration* in step 1 for the current iteration.

- 3. Call the InitializeFlatnessCal VI and configure it using the following parameters:

- **connection**: Current iteration value for *connection configuration*

- **signal path**: Current iteration value for *signal path*

- **terminal configuration**: Current iteration value for *terminal configuration*

- 4. Configure the I/Q calibration fixture based on the **IQ cal fixture cal** output of the IntializeFlatnessCal VI in step 3.

- 5. Configure the PXIe-5645 to generate a -3 dBFS signal at a specified frequency offset signal using the following settings.

- Level  $(V_{pk-pk})$ : 1 if terminal configuration is differential, otherwise 0.5

- Tone amplitude: -3 dBFS

- Tone frequency: 500 kHz

- Offset (V): 0

- Common-mode (V): 0

- Load impedance: Default

- 6. Configure the power sensor to correct for the frequency from step 5 using the power sensor frequency correction function.

- 7. Measure the output power of the generated signal using the power sensor.

- Store the result as *fixture flatness* (*f*), where *f* is the frequency generated in step 5.

- 8. Repeat steps 5 through 7 for the remaining frequencies from 500 kHz to 42.5 MHz in 1 MHz steps.

9. Call the AdjustFlatnessCal VI. Pass the *fixture flatness* versus frequency from step 8 to the **flatness measurement** input.

### **Characterizing Matching**

This procedure measures the gain imbalance and phase matching for the input and output ports of the PXIe-5645 I/Q calibration fixture.

- 1. If the current iteration has the following values, continue to step 2, otherwise proceed to the next characterization.

- Connection configuration: Swapped or thru

- Signal path: Inline or cross

- Terminal configuration: Differential or single-ended

- DMM source: None

- 2. Ensure the calibration fixture is connected to the appropriate instrumentation based on the value of *connection configuration* in step 1 for the current iteration.

- 3. Call the InitializeMatchingCal VI and configure it using the following parameters:

- **connection**: Current iteration value for *connection configuration*

- **signal path**: Current iteration value for *signal path*

- **terminal configuration**: Current iteration value for *terminal configuration*

- 4. Configure the I/Q calibration fixture based on the **IQ cal fixture cal** output of the IntializeMatchingCal VI in step 3.

- 5. Use the following settings to configure the PXIe-5645 to generate a -3 dBFS signal at a specified frequency offset signal:

- Level (V<sub>pk-pk</sub>): 1 if terminal configuration is differential, otherwise 0.5

- Tone amplitude: -3 dBFS

- Tone frequency: start frequency from the following table

- Offset (V): 0

- Common-mode (V): 0

- Load impedance: Default

Table 10. Matching Characterization Test Frequencies

| Signal Path | Start Frequency (MHz) | Stop Frequency (MHz) | Step Size (kHz) |

|-------------|-----------------------|----------------------|-----------------|

| Inline      | -40.5                 | 40.5                 | 500             |

| Cross       | 40.5                  | -40.5                | 500             |

- 6. Use the following settings to configure the PXIe-5645 I/Q input to acquire a signal:

- Level (V<sub>pk-pk</sub>): 0.8 if terminal configuration is differential, otherwise 0.4

- Sample rate: 120 MS/s

- Acquisition size: 15,000 samples

- Measure the resulting generated signal using the PXIe-5645 I/Q input. Store the following values from the measurement:

Fixture Gain Imbalance =  $I_{magnitude}$  (f)/ $Q_{magnitude}$  (f)

Fixture Phase Mismatch =  $I_{phase}(f) - Q_{phase}(f)$

- 8. Repeat steps 5 through 7 for the remaining frequencies listed in the previous table for the current iteration.

- 9. Call the AdjustMatchingCal VI. Pass the *Fixture Gain Imbalance* versus frequency from step 8 to the **gain imbalance** input. Pass the *Fixture Phase Mismatch* versus frequency from step 8 to the **phase skew** input.

### **Characterizing Gain**

This procedure measures the gain for the input and output ports of the PXIe-5645 I/Q calibration fixture.

- 1. If the current iteration has the following values, continue to step 2, otherwise proceed to the next characterization.

- Connection configuration: Thru

- · Signal path:

- Inline

- Cross

- Absolute I

- Absolute O

- Splitter I to I and power meter

- Splitter I to Q and power meter

- Terminal configuration: Differential, or single-ended

- DMM source: I In, I Out, Q In, Q Out, or power meter

- 2. Ensure the calibration fixture is connected to the appropriate instrumentation based on the value of *connection configuration* in step 1 for the current iteration.

- 3. Call the InitializeGainCal VI and configure it using the following parameters:

- **connection**: Current iteration value for *connection configuration*

- **signal path**: Current iteration value for *signal path*

- terminal configuration: Current iteration value for terminal configuration

- **DMM source name**: Current iteration value for *DMM source*

- 4. Use the following settings to configure the DMM for a voltage measurement:

- Function: DC Volts

- Digits of precision: 6 1/2

- Range: 2 Volts

- Aperture: 0.1 seconds

- · Auto zero: On

- Offset compensated Ohms: On

- Number of averages: 2

- Powerline frequency: 60 Hz

- Use the following settings to configure the PXIe-5645 I/Q output to generate a DC value of 1 V:

- Level (V<sub>pk-pk</sub>): 1 if *Terminal Configuration* is differential, otherwise 0.5

- DC level: 1

- Offset (V): 0

- Common-mode voltage: 0

- Load impedance: Default

- 6 Measure the resulting signal using the DMM.

- Use the following settings to configure the PXIe-5645 I/Q output to generate a DC value of -1 V:

- Level (V<sub>pk-pk</sub>): 1 if *Terminal Configuration* is differential, otherwise 0.5

- DC level: -1

- Offset (V): 0

- Common-mode voltage: 0

- Load impedance: Default

- 8. Measure the resulting signal using the DMM.

- 9 Call the AdjustGainCal VI and pass (result of step 8 - result of step 5) to the **DMM** measurement input.

# Self-Calibrating the PXIe-5645

Allow a 30-minute warm-up time before you begin self-calibration.

**Note** The warm-up time begins after the PXI Express chassis is powered on and the operating system completely loads.

The PXIe-5645 includes precise internal circuits and references used during self-calibration to adjust for any errors caused by short-term fluctuations in the environment. You must call the self-calibration function to validate the specifications in the *Verification* section.

- Perform self-calibration using the installed self-calibration executable or the niVST Self-Calibrate VI. Open one of the following self-calibration tools:

- Navigate to Start»All Programs»National Instruments»Vector Signal Transceivers» VST Self-Calibrate or < Program Files > \National Instruments\NI VST\Self Calibration to launch the self-calibration executable.

- Add the niVST Self-Calibrate VI, located on the Functions»Instrument I/O» **Instrument Drivers**»NI VST Calibration palette, to a block diagram.

- 2 Run the self-calibration executable or VI.

### As-Found and As-Left Limits

The as-found limits are the published specifications for the PXIe-5645. NI uses these limits to determine whether the PXIe-5645 meets the specifications when it is received for calibration. Use the as-found limits during initial verification.

The as-left calibration limits are equal to the published NI specifications for the PXIe-5645, less guard bands for measurement uncertainty, temperature drift, and drift over time. NI uses these limits to reduce the probability that the instrument will be outside the published specification limits at the end of the calibration cycle. Use the as-left limits when performing verification after adjustment.

### **RF** Verification

The performance verification procedures assume that adequate traceable uncertainties are available for the calibration references.

### Verifying Internal Frequency Reference

This procedure verifies the frequency accuracy of the PXIe-5645 onboard frequency reference using a vector signal generator.

Connect the vector signal generator RF OUT front panel connector to the PXIe-5645 RF IN front panel connector.

Figure 14. Internal Frequency Reference Verification Cabling Diagram

- 1. PXIe-5645

- 2. SMA (m)-to-SMA (m) Cable

- 3. Vector Signal Generator

- 2. Connect an available 10 MHz rubidium frequency reference output to the vector signal generator REF IN front panel connector.

Configure the vector signal generator to generate a 2.22 GHz signal with a 0 dBm average output power, using the following settings:

Center frequency: 2.22 GHz

Output power: 0 dBm

Reference Clock source: External

Configure the PXIe-5645 to acquire and measure the signal generated in step 3, using the following settings:

Center frequency: 2.22 GHz Reference level: +10 dBm

Resolution bandwidth: 100 Hz

Span: 100 kHz

FFT window: Hanning Averaging type: RMS Number of averages: 20

Reference Clock source: Onboard

- 5. Measure the frequency of the peak acquired tone.

- Calculate the deviation using the following equation: 6

$$\Delta f = \left| \frac{f_{measuredGHz} - 2.2GHz}{2.2GHz} \right|$$

The result in step 6 should be less than the result of the following equation: 7.

initial accuracy + aging + temperature stability where

> initial accuracy =  $\pm 200 * 10^{-9}$  $aging = \pm 1 * 10^{-6} / year * number of years since last adjustment$ temperature stability =  $\pm 1 * 10^{-6}$

**Note** You can determine number of years since last adjustment programmatically using the PXIe-5644/5645 Instrument Design Libraries.

### Verifying RF Input Spectral Purity

This procedure verifies the RF input spectral purity of the PXIe-5645.

Connect the PXIe-5645 LO OUT (RF IN 0) front panel connector to the RF IN front panel connector of the spectrum analyzer.

Figure 15. RF Input Spectral Purity Verification Cabling Diagram

- 1. PXIe-5645

- 2. SMA (m)-to-SMA (m) Cable

- 3. Spectrum Analyzer

- Connect an available 10 MHz rubidium frequency reference output to the PXIe-5645 REF IN front panel connector.

- 3. Connect an available 10 MHz rubidium frequency reference output to the spectrum analyzer REF IN front panel connector.

- 4. Configure the PXIe-5645 to export the LO using the following settings:

- Center frequency: 1 GHz

- LO OUT: Enabled

- Reference Clock source: REF IN

- 5. Configure the spectrum analyzer to acquire a spectrum using the following settings:

- Center frequency: 1 GHz

- Reference level: 0 dBm

- Span: 100 Hz

- Resolution bandwidth: 10 Hz

- Reference Clock source: External

- Averaging type: RMS

- Number of averages: 20

- 6. Measure the peak power at the center frequency.

The measured value is the power, in dBm, of the generated tone.

- Configure the spectrum analyzer to acquire a spectrum using the following settings: 7.

- Center frequency: Center frequency from step 4 + 20 kHz

- Reference level: 0 dBm

- Span: 100 Hz

- Resolution bandwidth (RBW): 10 Hz

- Reference Clock source: External

- Averaging type: RMS

- Number of averages: 20

- Measure the power at a 20 kHz offset. Normalize the result to 1 Hz bin width by subtracting 10 \* log (RBW), where RBW is the setting specified in step 7.

The result of this step is in dBm/Hz.

Calculate the relative difference between the signal and noise using the following 9. equation:

SSB Phase Noise at 20 kHz (dBc/Hz) = step 8 measurement (dBc/Hz) - step 6 measurement (dBm)

The result of this step is in dBc/Hz.

10. Compare the results of step 9 to the specified limits in the following table.

**Table 11.** SSB Phase Noise at 20 kHz Offset (Low Loop Bandwidth)

| Frequency       | As-Found Limit (dBc/Hz) | As-Left Limit (dBc/Hz) |

|-----------------|-------------------------|------------------------|

| <3 GHz          | -99                     | -99                    |

| 3 GHz to 4 GHz  | -91                     | -91                    |

| >4 GHz to 6 GHz | -93                     | -93                    |

- 11. Repeat steps 4 through 10 for the following frequencies:

- 1 GHz

- 1.9 GHz

- 2.4 GHz

- 3 GHz

- 4.4 GHz

- 5.8 GHz

- 12. Repeat steps 4 through 11 for the configurations specified in the following tables.

**Table 12.** SSB Phase Noise at 20 kHz Offset (Medium-Loop Bandwidth)

| Frequency       | As-Found Limit (dBc/Hz) | As-Left Limit (dBc/Hz) |

|-----------------|-------------------------|------------------------|

| <3 GHz          | -99                     | -99                    |

| 3 GHz to 4 GHz  | -93                     | -93                    |

| >4 GHz to 6 GHz | -93                     | -93                    |

**Table 13.** SSB Phase Noise at 20 kHz Offset (High-Loop Bandwidth)

| Frequency       | As-Found Limit (dBc/Hz) | As-Left Limit (dBc/Hz) |  |

|-----------------|-------------------------|------------------------|--|

| <3 GHz          | -94                     | -94                    |  |

| 3 GHz to 4 GHz  | -91                     | -91                    |  |

| >4 GHz to 6 GHz | -87                     | -87                    |  |

### Verifying RF Output Spectral Purity

This procedure verifies the RF output spectral purity of the PXIe-5645.

1. Connect the PXIe-5645 RF OUT (RF IN 0) front panel connector to the RF IN front panel connector of the spectrum analyzer.

Figure 16. RF Output Spectral Purity Verification Cabling Diagram

- 1. PXIe-5645

- 2. SMA (m)-to-SMA (m) Cable

- 3. Spectrum Analyzer

- Connect an available 10 MHz rubidium frequency reference output to the PXIe-5645 REF IN front panel connector.

- 3. Connect an available 10 MHz rubidium frequency reference output to the spectrum analyzer REF IN front panel connector.

- 4. Configure the PXIe-5645 to generate an offset CW tone using the following settings:

- Center frequency: 1 GHz

- Output power: 0 dBm

Tone offset: 3.75 MHz

I/Q rate: 10 MS/s Loop bandwidth: Low

Fractional mode: Enabled Step size: 200 kHz

Reference Clock source: REF IN

Configure the spectrum analyzer to acquire a spectrum using the following settings: 5

Center frequency: 1 GHz + 3.75 MHz

Reference level: 0 dBm

Span: 100 Hz

Resolution bandwidth: 10 Hz Reference Clock source: External

Averaging type: RMS Number of averages: 20

6. Measure the peak power at the center frequency.

The measured power should match the power, in dBm, of the generated tone.

- 7. Configure the spectrum analyzer to acquire a spectrum using the following settings:

- Center frequency: Center frequency from step 5 + 20 kHz

- Reference level: 0 dBm

- Span: 100 Hz

- Resolution bandwidth: 10 Hz

- Reference Clock source: External

- Averaging type: RMS

- Number of averages: 20

- 8. Measure the power at a 20 kHz offset. Normalize the result to 1 Hz bin width by subtracting 10 \* log (RBW), where RBW is the setting specified in step 7.

The result of this step is in dBm/Hz.

9. Calculate the relative difference between the signal and noise using the following equation:

SSB Phase Noise at 20 kHz (dBm/Hz) = step 8 measurement (dBm/Hz) - step 6 *measurement* (dBm)

The result of this step is in dBm/Hz.

10. Compare the results of step 9 to the specified limits in the following table.

**Table 14.** SSB Phase Noise at 20 kHz Offset (Low-Loop Bandwidth)

| Frequency       | As-Found Limit (dBc/Hz) | As-Left Limit (dBc/Hz) |

|-----------------|-------------------------|------------------------|

| <3 GHz          | -99                     | -99                    |

| 3 GHz to 4 GHz  | -91                     | -91                    |

| >4 GHz to 6 GHz | -93                     | -93                    |

- 11. Repeat steps 4 through 10 for the following frequencies:

- 1 GHz

- 1.9 GHz

- 2.4 GHz

- 3 GHz

- 4.4 GHz

- 5 8 GHz

- 12. Repeat steps 4 through 11 for the configurations specified in the following tables.

Table 15. SSB Phase Noise at 20 kHz Offset (Medium-Loop Bandwidth)

| Frequency       | As-Found Limit (dBc/Hz) | As-Left Limit (dBc/Hz) |

|-----------------|-------------------------|------------------------|

| <3 GHz          | -99                     | -99                    |

| 3 GHz to 4 GHz  | -93                     | -93                    |

| >4 GHz to 6 GHz | -93                     | -93                    |

**Table 16.** SSB Phase Noise at 20 kHz Offset (High-Loop Bandwidth)

| Frequency       | As-Found Limit (dBc/Hz) | As-Left Limit (dBc/Hz) |

|-----------------|-------------------------|------------------------|

| <3 GHz          | -94                     | -94                    |

| 3 GHz to 4 GHz  | -91                     | -91                    |

| >4 GHz to 6 GHz | -87                     | -87                    |

### Verifying Input Absolute Amplitude Accuracy

This procedure verifies the absolute amplitude accuracy of the PXIe-5645 input channels.

This procedure requires the same attenuator and splitter positioning as used during the *Test System Characterization* procedures, as well as the data collected in the *Characterizing Power Splitter Balance* section. You must characterize the power splitter balance before running this procedure. Ensure you use the characterization data derived from test points in the *Characterization Test Points for Verification Procedures* table in the *Characterizing Power Splitter Balance* section.

You must zero the power sensor as described in the *Zeroing the Power Sensor* section prior to starting this procedure.

- 1. Connect the vector signal generator RF OUT front panel connector to the input terminal of the power splitter using a SMA (m)-to-SMA (m) cable.