#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE PXIe-6545

# SPECIFICATIONS NI PXIe-6544/6545/6547/6548

#### 100/200 MHz Digital Waveform Generator/Analyzer

このドキュメントには、日本語ページも含まれています。

This document provides the specifications for the NI PXIe-6544 (NI 6544), NI PXIe-6545 (NI 6545), NI PXIe-6547 (NI 6547), and NI PXIe-6548 (NI 6548).

*Maximum* and *minimum* specifications are warranted not to exceed these values within certain operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

*Typical* specifications are unwarranted values that are representative of a majority  $(3\sigma)$  of units within certain operating conditions and include the effects of temperature and uncertainty unless otherwise noted.

*Characteristic* specifications are unwarranted values that are representative of an average unit operating at room temperature.

*Nominal* specifications are unwarranted values that are relevant to the use of the product and convey the expected performance of the product.

All specifications are *Typical* unless otherwise noted. These specifications are valid within the operating temperature range. Specifications are subject to change without notice. For the most recent NI 6544/6545/6547/6548 specifications, visit ni.com/manuals. To access the NI 6544/6545/6547/6548 documentation, including the *NI Digital Waveform Generator/ Analyzer Getting Started Guide*, which contains functional descriptions of the NI 6544/6545/6547/6548 signals and the connector pinouts, navigate to **Start»Programs»National Instruments»NI-HSDIO»Documentation**.

**Hot Surface** If the NI 6544/6545/6547/6548 has been in use, it may exceed safe handling temperatures and cause burns. Allow time to cool before removing the NI 6544/6545/6547/6548 from the chassis.

**Note** All values were obtained using a 1 m cable (SHC68-C68-D4 recommended). Performance specifications are not guaranteed when using longer cables.

### Contents

| Channel Specifications                                       | 3  |

|--------------------------------------------------------------|----|

| Generation Channels (Data, DDC CLK OUT, and PFI <03>)        | 4  |

| Acquisition Channels (Data, STROBE, and PFI <03>)            | 6  |

| Timing Specifications                                        | 7  |

| Sample Clock                                                 | 7  |

| Generation Timing (Data, DDC CLK OUT, and PFI <03> Channels) | 9  |

| Generation Provided Setup and Hold Times                     | 13 |

| Acquisition Timing (Data, STROBE, and PFI <03> Channels)     | 16 |

| CLK IN (SMA Jack Connector)                                  | 19 |

| STROBE (DDC Connector)                                       | 21 |

| CLK OUT (SMA Jack Connector)                                 |    |

| DDC CLK OUT (DDC Connector)                                  |    |

| Reference Clock (PLL)                                        |    |

| Waveform Specifications                                      |    |

| Memory and Scripting                                         |    |

| Triggers (Inputs to the NI 6544/6545/6547/6548)              |    |

| Events (Generated from the NI 6544/6545/6547/6548)           |    |

| Miscellaneous                                                | 29 |

| Power                                                        | 29 |

| Physical                                                     | 29 |

| I/O Panel Connectors                                         |    |

| Software                                                     |    |

| Environment                                                  |    |

| Safety, Electromagnetic Compatibility, and CE Compliance     |    |

## **Channel Specifications**

| Specification                                                        | v                                  | alue                                                                                                                                                                                                                                                                                                                                                                                                                                     | Comments                                                                                                                                                          |

|----------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of data                                                       | NI 6544/6545                       | NI 6547/6548                                                                                                                                                                                                                                                                                                                                                                                                                             | Data rate                                                                                                                                                         |

| channels                                                             | 32 single data rate (SDR) channels | 32 single data rate (SDR)<br>channels<br>or<br>16 double data rate (DDR)                                                                                                                                                                                                                                                                                                                                                                 | multiplier is<br>software<br>selectable to be<br>SDR or DDR.<br>Using SDR,                                                                                        |

|                                                                      |                                    | <ul> <li>ro double data rate (DDR) channels per direction</li> <li>or</li> <li>24 channels when configured for extended data mode.</li> <li>This mode is used for hardware comparison and cycle-to-cycle tristate operations.</li> <li>Note: Generation and acquisition sessions may be independently configured for DDR operation on either the lower data channels (&lt;015&gt;) or the upper data channels (&lt;1631&gt;).</li> </ul> | data is clocked<br>using the rising<br>or falling edge<br>of the Sample<br>clock.<br>Using DDR,<br>data is clocked<br>using both<br>edges of the<br>Sample clock. |

| Direction<br>control of data<br>channels                             | Per channel, per operation         | Per channel, per cycle                                                                                                                                                                                                                                                                                                                                                                                                                   | Per cycle<br>direction<br>control is<br>supported when<br>in extended<br>data mode.                                                                               |

| Time to tristate (t <sub>PZ</sub> )                                  | 6.2 ns                             |                                                                                                                                                                                                                                                                                                                                                                                                                                          | Nominal into a $2 k\Omega$ and $15 pF$ load.                                                                                                                      |

| Number of<br>programmable<br>function<br>interface (PFI)<br>channels | 4                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                          | Refer to the<br>Waveform<br>Specifications<br>section for<br>more details.                                                                                        |

| Specification                           | Value               | Comments                                                                               |

|-----------------------------------------|---------------------|----------------------------------------------------------------------------------------|

| Direction<br>control of PFI<br>channels | Per channel         |                                                                                        |

| Number of<br>clock terminals            | 2 input<br>2 output | Refer to<br>the <i>Timing</i><br><i>Specifications</i><br>section for<br>more details. |

## Generation Channels (Data, DDC CLK OUT, and PFI <0..3>)

| Specification                                             | Valu                                                                                                                                                                                                                                        | e                                                                         | Comments                                    |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------|

| Generation<br>signal type                                 | Single-ended                                                                                                                                                                                                                                |                                                                           | —                                           |

| Number of<br>programmable<br>generation<br>voltage levels | 1 Voltage high level (V <sub>OH</sub> )<br>Generation Voltage Low Level (V <sub>O</sub><br><b>Note</b> : Generation and acquisition so<br>programmable voltage resource. Fo<br>acquisition thresholds must be set to<br>High Level setting. | NI 6547/<br>6548 only;<br>for all data,<br>PFI, and<br>clock<br>channels. |                                             |

| Generation<br>voltage range                               | 1.2 V to 3.3 V                                                                                                                                                                                                                              |                                                                           |                                             |

| Generation<br>voltage<br>resolution                       | 100 mV                                                                                                                                                                                                                                      |                                                                           |                                             |

| DC generation                                             | Typical                                                                                                                                                                                                                                     | Into 1 MΩ;                                                                |                                             |

| voltage<br>accuracy                                       | ±35 mV                                                                                                                                                                                                                                      | ±200 mV                                                                   | does not<br>include<br>system<br>crosstalk. |

| Specification                                     | Value                                                                           |                                                                 |           |                           |             | Comments                         |

|---------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------|-----------|---------------------------|-------------|----------------------------------|

| Generation<br>logic families                      | 1.2V, 1.5V, 1.8V<br>Generation and<br>resource. Simul<br>family.                | All devices;<br>for all data,<br>PFI, and<br>clock<br>channels. |           |                           |             |                                  |

| Generation                                        | Logic                                                                           | Voltage Lo                                                      | ow Levels | Voltage H                 | ligh Levels | Nominal                          |

| voltage levels                                    | Family                                                                          | Nominal                                                         | Мах       | Min                       | Nominal     | values have<br>±35 mV            |

|                                                   | 1.2V<br>(V <sub>OH</sub> = 1.2 V)                                               | 0.0 V                                                           | 0.2 V     | 1 V                       | 1.2 V       | typical<br>accuracy              |

|                                                   | 1.5V<br>(V <sub>OH</sub> = 1.5 V)                                               | 0.0 V                                                           | 0.2 V     | 1.3 V                     | 1.5 V       | with a<br>1 MΩ load.<br>Does not |

|                                                   | 1.8V<br>(V <sub>OH</sub> = 1.8 V)                                               | 0.0 V                                                           | 0.2 V     | 1.6 V                     | 1.8 V       | include<br>system                |

|                                                   | 2.5V<br>(V <sub>OH</sub> = 2.5 V)                                               | 0.0 V                                                           | 0.2 V     | 2.3 V                     | 2.5 V       | crosstalk.                       |

|                                                   | 3.3V<br>(V <sub>OH</sub> = 3.3 V)                                               | 0.0 V                                                           | 0.2 V     | 3.1 V                     | 3.3 V       |                                  |

| Output<br>impedance                               | 50 Ω                                                                            |                                                                 |           |                           |             | Nominal.                         |

| Maximum<br>allowed DC                             | Logic                                                                           | Family                                                          |           | Maximum All<br>Drive Stre | Nominal.    |                                  |

| drive strength<br>per channel                     | 1                                                                               | .2V                                                             |           | ±12 mA<br>±15 mA          |             |                                  |

|                                                   | 1                                                                               | .5V                                                             |           |                           |             |                                  |

|                                                   | 1                                                                               | .8V                                                             |           | ±18 m                     | A           |                                  |

|                                                   | 2                                                                               | .5V                                                             |           | ±25 m                     | А           |                                  |

|                                                   | 3.3V ±33 mA                                                                     |                                                                 |           |                           |             |                                  |

| Data channel<br>driver enable/<br>disable control | Per channel                                                                     |                                                                 |           |                           |             | Software-<br>selectable.         |

| Channel power-on state                            | Drivers disabled, 50 k $\Omega$ nominal input impedance                         |                                                                 |           |                           |             | _                                |

| Output<br>protection                              | The device can indefinitely sustain a short to any voltage between 0 V and 5 V. |                                                                 |           |                           |             | —                                |

#### Acquisition Channels (Data, STROBE, and PFI <0..3>)

| Specification                                          |                                                                                                                                                                                                                                                                          | Va             | alue           |        |         |                 | Comments                                                               |

|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------|--------|---------|-----------------|------------------------------------------------------------------------|

| Acquisition<br>signal type                             | Single-ended                                                                                                                                                                                                                                                             |                |                |        |         |                 | _                                                                      |

| Number of<br>programmable<br>acquisition<br>thresholds | 1 voltage threshold ( $V_{IH} = V_{IL}$ )<br><b>Note</b> : Generation and acquisition sessions share a common<br>programmable voltage resource. For simultaneous operations,<br>Generation Voltage High Level must be set to twice the Acquisition<br>Voltage Threshold. |                |                |        |         |                 | NI 6547/654<br>8 only; for<br>all data, PFI,<br>and clock<br>channels. |

| Acquisition<br>Voltage<br>Threshold<br>range           | 0.6 V to 1.65 V                                                                                                                                                                                                                                                          |                |                |        |         |                 |                                                                        |

| Acquisition<br>Voltage<br>Threshold<br>resolution      | 50 mV                                                                                                                                                                                                                                                                    |                |                |        |         |                 |                                                                        |

| DC Acquisition<br>Voltage                              | Туріс                                                                                                                                                                                                                                                                    | al             |                |        | Maximu  | Im              | Does not include                                                       |

| Threshold<br>accuracy                                  | ±150 n                                                                                                                                                                                                                                                                   | ıV             |                |        | ±30%    |                 | system<br>crosstalk.                                                   |

| Acquisition<br>logic families                          | 1.2V, 1.5V, 1.8V, 2.5<br><b>Note</b> : Generation an<br>resource. Simultaneo<br>family.                                                                                                                                                                                  | d acquisition  | n sessi        | ons sh |         | U               | All devices;<br>for all data,<br>PFI, and<br>clock<br>channels.        |

| Acquisition<br>Voltage                                 |                                                                                                                                                                                                                                                                          | Vol<br>Thresho | tage<br>olds L | ow     |         | age<br>Ids High | Does not<br>include                                                    |

| Thresholds                                             | Logic Family                                                                                                                                                                                                                                                             | Min            | Тур            | ical   | Typical | Max             | system<br>crosstalk.                                                   |

|                                                        | 1.2V<br>(V <sub>IH</sub> , V <sub>IL</sub> = 0.60 V)                                                                                                                                                                                                                     | 420 mV         | 450            | mV     | 750 mV  | 780 mV          | crossuik.                                                              |

|                                                        | $ \begin{array}{c c} 1.5V \\ (V_{IH},  V_{IL} \!=\! 0.75 \ V) \end{array} \hspace{0.2cm} 525 \ mV \hspace{0.2cm} 600 \ mV \hspace{0.2cm} 900 \ mV \hspace{0.2cm} 975 \ mV \end{array} $                                                                                  |                |                |        |         |                 |                                                                        |

|                                                        | $ \begin{array}{c c} 1.8V \\ (V_{IH}, V_{IL} = 0.90 \ V) \end{array} \begin{array}{c c} 630 \ mV \end{array} \begin{array}{c c} 750 \ mV \end{array} \begin{array}{c c} 1.05 \ V \end{array} \begin{array}{c} 1.17 \ V \\ \end{array} $                                  |                |                |        |         |                 |                                                                        |

|                                                        | 2.5V<br>(V <sub>IH</sub> , V <sub>IL</sub> = 1.25 V)                                                                                                                                                                                                                     | 875 mV         | 1.1            | 0 V    | 1.40 V  | 1.625 V         |                                                                        |

|                                                        | 3.3V<br>(V <sub>IH</sub> , V <sub>IL</sub> = 1.65 V)                                                                                                                                                                                                                     | 1.155 V        | 1.5            | 0 V    | 1.80 V  | 2.145 V         |                                                                        |

| Specification      | Value                  | Comments                                                                                        |

|--------------------|------------------------|-------------------------------------------------------------------------------------------------|

| Input<br>impedance | High-impedance (50 kΩ) | Nominal.                                                                                        |

| Input protection   | -1 V to 5 V            | Internal<br>diode clamps<br>may begin<br>conduction<br>outside the<br>-0.5 V to<br>3.5 V range. |

### **Timing Specifications**

### Sample Clock

| Specification                                | Value                                                                                                                                                                                             | Comments                                                                                            |

|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|

| Sample clock<br>sources                      | <ol> <li>On Board Clock (internal 800 MHz VCO with 32-bit DDS)</li> <li>CLK IN (SMA jack connector)</li> <li>STROBE (Digital Data &amp; Control (DDC) connector;<br/>acquisition only)</li> </ol> | _                                                                                                   |

| On Board<br>Clock<br>frequency<br>range      | NI 6544, NI 6547: 100 Hz to 100 MHz<br>NI 6545, NI 6548: 100 Hz to 200 MHz                                                                                                                        | _                                                                                                   |

| On Board<br>Clock<br>frequency<br>resolution | 0.2 Hz maximum<br><b>Note</b> : Varies with Sample clock frequency.                                                                                                                               | NI-HSDIO may<br>be queried for<br>the<br>programmed<br>frequency<br>value.                          |

| On Board<br>Clock<br>frequency<br>accuracy   | ±150 ppm + 5 ppm per year                                                                                                                                                                         | Accuracy may<br>be increased by<br>using a higher<br>performance<br>external<br>Reference<br>clock. |

| Specification                                                  | Va                                                                         | ue                                                                                                             | Comments                 |

|----------------------------------------------------------------|----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|

| CLK IN<br>frequency<br>range                                   | NI 6544, NI 6547: 20 kHz to 10<br>NI 6545, NI 6548: 20 kHz to 20           | Refer to the<br>CLK IN<br>(SMA Jack<br>Connector)<br>section for<br>restrictions<br>based on<br>waveform type. |                          |

| STROBE<br>frequency<br>range                                   | NI 6544, NI 6547: 100 Hz to 10<br>NI 6545, NI 6548: 100 Hz to 20           | Refer to the<br>STROBE (DDC<br>Connector)<br>section.                                                          |                          |

| Sample clock<br>relative delay<br>adjustment<br>range          | 0.0 to 1.0 Sample clock period (a 0.0 ns to 5.0 ns (generation session)    | You can apply a<br>delay or phase<br>adjustment to<br>the On Board                                             |                          |

| Sample clock<br>relative delay<br>adjustment<br>resolution     | 0.5 ps                                                                     | Clock to align<br>multiple<br>devices.                                                                         |                          |

| Exported<br>Sample clock<br>destinations                       | <ol> <li>DDC CLK OUT (DDC conn</li> <li>CLK OUT (SMA jack conne</li> </ol> | Internal Sample<br>clocks with<br>sources other<br>than STROBE<br>can be<br>exported.                          |                          |

| Exported<br>Sample clock<br>delay range                        | 0.0 to 1.0 Sample clock periods                                            | Resolution is<br>nonlinearly<br>dependent                                                                      |                          |

| Exported<br>Sample clock<br>delay<br>resolution ( $\delta_C$ ) | 117 ps to 143 ps, nominal                                                  | on clock<br>frequency and<br>may be queried<br>for by using<br>NI-HSDIO.                                       |                          |

| Exported                                                       | On Board Clock                                                             |                                                                                                                |                          |

| Sample Clock<br>delay<br>frequency                             | All supported frequencies                                                  | $Frequencies \geq 20 \text{ MHz}$                                                                              |                          |

| Exported                                                       | Period Jitter                                                              | Cycle-to-Cycle Jitter                                                                                          | Characteristic;          |

| Sample clock<br>jitter                                         | Sample clock 24 ps <sub>rms</sub> 43 ps <sub>rms</sub>                     |                                                                                                                | using On Board<br>Clock. |

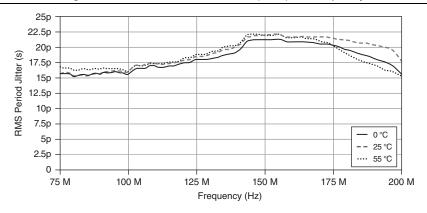

Figure 1. Characteristic Period Jitter (RMS) vs. Frequency

| Specification    | V            | Comments |                 |                                  |

|------------------|--------------|----------|-----------------|----------------------------------|

| Exported Sample  |              | DDC CI   | NI 6545/6548 at |                                  |

| clock duty cycle | Logic Family | Min      | Min Mox         | maximum clock<br>rate (200 MHz). |

|                  | 1.2V         | 37%      | 50%             | Not including the                |

|                  | 1.5V         | 41%      | 53%             | effects of system crosstalk.     |

|                  | 1.8V         | 42%      | 55%             |                                  |

|                  | 2.5V         | 45%      | 57%             |                                  |

|                  | 3.3V         | 48%      | 58%             |                                  |

## Generation Timing (Data, DDC CLK OUT, and PFI <0..3> Channels)

| Specification                       | Value   | Comments                                                                                                                                                 |

|-------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Data<br>channel-to-<br>channel skew | ±300 ps | Maximum<br>skew across all<br>data channels,<br>PFI channels,<br>and voltage<br>levels when<br>using the same<br>data position or<br>data delay<br>bank. |

| Specification                       |         | Value                                                                       | Comments                                                                 |          |                                           |

|-------------------------------------|---------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------|----------|-------------------------------------------|

| Maximum<br>data rate per<br>channel | NI 6544 | SDR: 100 Mbps<br>Supported for all logi                                     | Includes<br>maximum data<br>channel-to-                                  |          |                                           |

| chamer                              | NI 6545 | SDR: 200 Mbps<br>Supported for all logic families.                          |                                                                          |          | channel skew<br>and typical<br>crosstalk. |

|                                     | NI 6547 | SDR: 100 Mbps<br>DDR: 200 Mbps<br>Supported for all logi<br>voltage levels. | NI 6547/6548<br>devices<br>generate two<br>samples per<br>clock cycle in |          |                                           |

|                                     |         | Logic Family                                                                | SDR                                                                      | DDR      | DDR mode.                                 |

|                                     |         | 3.3V                                                                        | 200 Mbps                                                                 | 400 Mbps | •                                         |

|                                     |         | 2.5V                                                                        |                                                                          | 400 Mbps |                                           |

|                                     |         | 1.8V                                                                        |                                                                          | 375 Mbps |                                           |

|                                     |         | 1.5V                                                                        |                                                                          | 350 Mbps |                                           |

|                                     | NI 6548 | 1.2V                                                                        |                                                                          | 300 Mbps |                                           |

|                                     |         | Voltage Levels                                                              | SDR                                                                      | DDR      |                                           |

|                                     |         | 2.5 V to 3.3 V                                                              | 200 Mbps                                                                 | 400 Mbps |                                           |

|                                     |         | 1.8 V to 2.4 V                                                              |                                                                          | 375 Mbps |                                           |

|                                     |         | 1.5 V to 1.7 V                                                              |                                                                          | 350 Mbps |                                           |

|                                     |         | 1.2 V to 1.4 V                                                              |                                                                          | 300 Mbps |                                           |

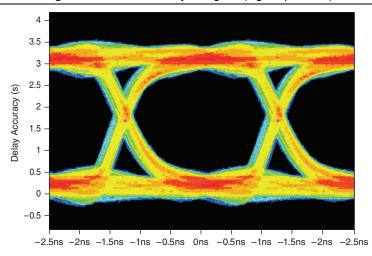

Figure 2 shows an eye diagram of a 400 Mbps pseudorandom bit sequence (PRBS) waveform in DDR mode at 3.3 V. This waveform was captured on DIO 0 at room temperature into high impedance.

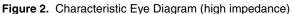

Figure 3 shows an eye diagram of a 400 Mbps PRBS waveform in DDR mode at 3.3 V. This waveform was captured on DIO 0 at room temperature into 50  $\Omega$  termination.

Figure 3. Characteristic Eye Diagram (50  $\Omega$  Termination)

| Specification                                   | Va                                                                                                                                              | Comments                                                                         |  |

|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| Data position<br>modes                          | Sample clock rising edge, Samp<br>Delay from Sample clock rising                                                                                | —                                                                                |  |

| Data delay<br>banks                             | NI 6544/6545: 1 bank for all ch<br>NI 6547/6548: 3 banks<br>Bank 0: DIO<03>, DIO<1619<br>Bank 1: DIO<47>, DIO<2022<br>Bank 2: DIO<815>, DIO<242 | Multibank data<br>delay is<br>supported<br>only in<br>NI-HSDIO 1.7<br>and later. |  |

| Generation data delay range $(\delta_G)$        | 0.0 to 1.0 Sample clock periods                                                                                                                 | Resolution is<br>nonlinearly<br>dependent                                        |  |

| Generation data delay resolution ( $\delta_G$ ) | 117 ps to 143 ps, nominal                                                                                                                       | on clock<br>frequency and<br>may be queried<br>for using                         |  |

| Generation data                                 | On Board Clock                                                                                                                                  | NI-HSDIO.                                                                        |  |

| delay<br>frequency                              | All supported frequencies                                                                                                                       | $Frequencies \geq 20 \text{ MHz}$                                                |  |

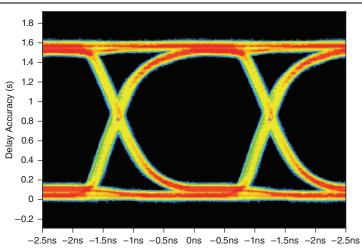

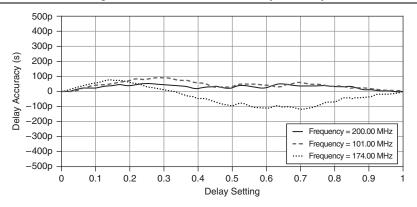

#### Figure 4. Characteristic Data Delay Accuracy

| Specification                                                                                 | Value                       | Comments                                                     |

|-----------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------------------------|

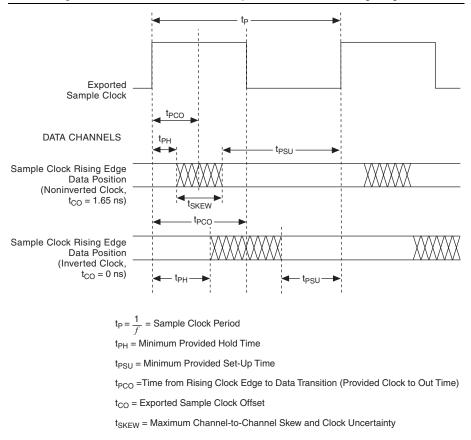

| Exported<br>Sample clock<br>offset (t <sub>CO</sub> )                                         | 0.0 ns or 1.65 ns (default) | Nominal;<br>Software-<br>selectable for<br>DDC_CLK_<br>OUT.  |

| Time delay<br>from Sample<br>clock (internal)<br>to DDC<br>connector<br>(t <sub>SCDDC</sub> ) | 8.1 ns                      | Characteristic;<br>Exported<br>Sample clock<br>offset = 0 ns |

#### Generation Provided Setup and Hold Times

| Exported Sample Clock<br>Offset (t <sub>PCO</sub> ) | Minimum Provided Setup<br>Time (t <sub>PSU</sub> ) | Minimum Provided Hold<br>Time (t <sub>PH</sub> ) |  |

|-----------------------------------------------------|----------------------------------------------------|--------------------------------------------------|--|

| 1.65 ns                                             | tp - 2.15 ns                                       | 1.15 ns                                          |  |

| 0.0 ns                                              | tp - 500 ps                                        | -500 ps                                          |  |

Compare the setup and hold times from the datasheet of your device under test (DUT) to the values in the table above. The provided setup and hold times must be greater than the setup and hold times required for the DUT. If you require more setup time, configure your exported Sample clock mode to Inverted and/or delay your clock or data relative to the Sample clock.

Refer to Figure 5 for a diagram illustrating the relationship between the exported Sample clock mode and the provided setup and hold times.

**Notes**: This table assumes the data position is set to Sample clock rising edge and the noninverted Sample clock is exported to the DDC connector.

This table includes worst-case effects of channel-to-channel skew and intersymbol interference.

**Note** Provided setup and hold times account for maximum channel-to-channel skew and jitter.

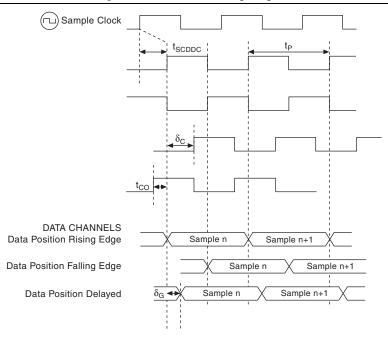

Figure 6. Generation Timing Diagram

$t_{\mbox{\scriptsize SCDDC}}$  : Time Delay from Sample Clock (Internal) to DDC Connector

$0 \leq \delta_C \leq 1$  : Exported Sample Clock Delay (Fraction of  $t_P)$

$0 \leq \delta_G \leq 1$  : Pattern Generation Data Delay (Fraction of  $t_P)$

$t_{P} = \frac{1}{f}$  = Period of Sample Clock

$t_{CO}$  = Exported Sample Clock Offset; 1.65 ns, Software-Selectable

## Acquisition Timing (Data, STROBE, and PFI <0..3> Channels)

| Specification               |                                                                                                                                           | Value                                                                       | •                                                                                   |          | Comments                                                                                                                                                 |

|-----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|-------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Channel-to-<br>channel skew | ±350 ps                                                                                                                                   |                                                                             |                                                                                     |          | Maximum<br>skew across all<br>data channels,<br>PFI channels,<br>and voltage<br>levels when<br>using the same<br>data position or<br>data delay<br>bank. |

| Maximum<br>data rate per    | NI 6544                                                                                                                                   | SDR: 100 Mbps<br>Supported for all logi                                     | c families                                                                          |          | Includes<br>maximum data                                                                                                                                 |

| channel                     | a rate per<br>nnel     NI 6511     Supported for all logic families.       NI 6545     SDR: 200 Mbps<br>Supported for all logic families. |                                                                             |                                                                                     |          | channel-to-<br>channel skew<br>and typical                                                                                                               |

|                             | NI 6547                                                                                                                                   | SDR: 100 Mbps<br>DDR: 200 Mbps<br>Supported for all logi<br>voltage levels. | crosstalk.<br>NI 6547/6548<br>devices<br>acquires<br>two samples<br>per clock cycle |          |                                                                                                                                                          |

|                             |                                                                                                                                           | Logic Family                                                                | SDR                                                                                 | DDR      | in DDR mode.                                                                                                                                             |

|                             |                                                                                                                                           | 3.3V                                                                        | 200 Mbps                                                                            | 300 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | 2.5V                                                                        |                                                                                     | 300 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | 1.8V                                                                        |                                                                                     | 250 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | 1.5V                                                                        |                                                                                     | 225 Mbps |                                                                                                                                                          |

|                             | NI 6548                                                                                                                                   | 1.2V                                                                        |                                                                                     | 200 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | Voltage<br>Threshold                                                        | SDR                                                                                 | DDR      |                                                                                                                                                          |

|                             |                                                                                                                                           | 1.25 V to 1.65 V                                                            | 200 Mbps                                                                            | 300 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | 0.90 V to 1.20 V                                                            |                                                                                     | 250 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | 0.75 V to 0.85 V                                                            |                                                                                     | 225 Mbps |                                                                                                                                                          |

|                             |                                                                                                                                           | 0.60 V to 0.70 V                                                            |                                                                                     | 200 Mbps |                                                                                                                                                          |

| Specification                           | Value                                                                                        |                 |                 |                            |                                              | Comments                                        |  |

|-----------------------------------------|----------------------------------------------------------------------------------------------|-----------------|-----------------|----------------------------|----------------------------------------------|-------------------------------------------------|--|

| Setup and                               | Hold Tir                                                                                     |                 | me (ths)        | e (ths) Setup Times (tsus) |                                              | Characteristic                                  |  |

| Hold Times to<br>STROBE                 | Threshold                                                                                    | <20 MHz         | ≥20 MHz         | <20 MHz                    | ≥20 MHz                                      | includes<br>maximum                             |  |

|                                         | 1.25 V to<br>1.65 V                                                                          | 2.4 ns          | 900 ps          | 2.8 ns                     | 1.15 ns                                      | data<br>channel-to-<br>channel skew             |  |

|                                         | 0.90 V to<br>1.20 V                                                                          |                 | 1.00 ns         |                            | 1.20 ns                                      | and<br>uncertainty,                             |  |

|                                         | 0.75 V to<br>0.85 V                                                                          |                 | 1.10 ns         |                            | 1.40 ns                                      | but does not<br>include<br>system               |  |

|                                         | 0.60 V to<br>0.70 V                                                                          |                 | 1.25 ns         |                            | 1.75 ns                                      | crosstalk.<br>Performance<br>may vary           |  |

|                                         |                                                                                              |                 |                 |                            |                                              | with system<br>crosstalk<br>performance.        |  |

| Data position<br>modes                  | Sample clock rising edge, Sample clock falling edge, or Delay from Sample clock rising edge. |                 |                 |                            | _                                            |                                                 |  |

| Data delay                              | NI 6544/654                                                                                  | 5: 1 bank for a | all channels an | d PFI lines                |                                              | Multibank                                       |  |

| banks                                   | NI 6547/6548                                                                                 | 3: 3 banks      |                 |                            |                                              | data delay is<br>supported                      |  |

|                                         |                                                                                              | , i             | ,               | DIO<2831>, PFI <03>        |                                              | only in                                         |  |

|                                         | Bank 1: DIO<                                                                                 |                 |                 |                            |                                              | NI-HSDIO<br>1.7 and later.                      |  |

|                                         | Bank 2: DIO<                                                                                 | <815>, DIO<     | <2427>          |                            |                                              |                                                 |  |

| Acquisition<br>data delay<br>range      | nonlinearl<br>dependent                                                                      |                 |                 |                            | Resolution is<br>nonlinearly<br>dependent on |                                                 |  |

| Acquisition<br>data delay<br>resolution | 117 ps to 143                                                                                | ps, nominal     |                 |                            |                                              | clock<br>frequency<br>and may be<br>queried for |  |

| Acquisition                             | On Board                                                                                     | d Clock         | External        | Clock and                  | STROBE                                       | by using<br>NI-HSDIO.                           |  |

| data delay<br>frequency                 | All supported                                                                                | frequencies     | Freq            | uencies $\geq 20$          | MHz                                          | M- <b>N</b> 5DIO.                               |  |

| Specification                                                      | Value  | Comments                                                                        |

|--------------------------------------------------------------------|--------|---------------------------------------------------------------------------------|

| Setup time to<br>sample clock<br>(t <sub>susc</sub> )              | 900 ps | Nominal;<br>does not<br>include                                                 |

| Hold time to<br>sample clock<br>(t <sub>HSC</sub> )                | 425 ps | channel-to-<br>channel<br>skew, t <sub>DDCSC</sub> ,<br>or t <sub>SCDDC</sub> . |

| Time delay<br>from DDC<br>connector to<br>internal<br>sample clock | 6.8 ns | Nominal.                                                                        |

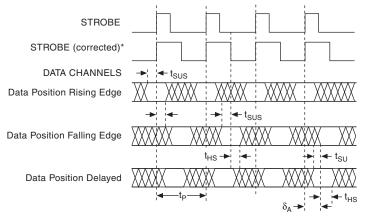

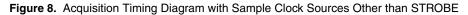

#### Figure 7. Acquisition Timing Diagram Using STROBE as the Sample Clock

t<sub>SUS</sub> = Set-Up Time to STROBE

t<sub>HS</sub> = Hold Time from STROBE

$0 \leq \delta_A \leq 1$  : Acquisition Data Delay (fraction of  $t_P)$

$t_{P} = \frac{1}{f}$  = Sample Clock Period

\*Note: When using an external Sample clock greater than 20 MHz, the duty cycle is corrected to 50%.

t<sub>DDCSC</sub> : Time Delay from DDC Connector to Internal Sample Clock

$0 \leq \delta_A \leq 1$  : Acquisition Data Delay (fraction of  $t_P)$

$t_{\rm P} = \frac{1}{c}$  = Period of Sample Clock

t<sub>SUSC</sub> = Set-Up Time to Sample Clock

t<sub>HSC</sub> = Hold Time to Sample Clock

#### CLK IN (SMA Jack Connector)

| Specification       | Value                                                                                   | Comments |

|---------------------|-----------------------------------------------------------------------------------------|----------|

| Direction           | Input to device                                                                         | —        |

| Destinations        | <ol> <li>Reference clock—for the phase lock loop (PLL)</li> <li>Sample clock</li> </ol> | _        |

| Input coupling      | AC                                                                                      | —        |

| Input<br>protection | ±10 VDC                                                                                 | Nominal. |

| Specification                        |                                                                                                    |                                                | Value                                         |                                               |                                               | Comments                                  |

|--------------------------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------|-----------------------------------------------|-----------------------------------------------|-------------------------------------------|

| Input<br>impedance                   | 50 $\Omega$ (default) or 1 k $\Omega$                                                              |                                                |                                               |                                               |                                               | Software-<br>selectable;<br>Nominal.      |

| Minimum<br>detectable<br>pulse width | 2 ns                                                                                               |                                                |                                               |                                               |                                               | Nominal.                                  |

| Clock<br>requirements                | Clock must                                                                                         | Clock must be continuous and free-running.     |                                               |                                               |                                               |                                           |

| Voltage ranges                       |                                                                                                    | 5                                              | Square Wave                                   | s                                             |                                               | —                                         |

|                                      | 0.65 V <sub>pp</sub> to :                                                                          | 5.0 V <sub>pp</sub>                            |                                               |                                               |                                               |                                           |

|                                      |                                                                                                    |                                                | Sine Waves                                    | i                                             |                                               | —                                         |

|                                      | Voltage<br>range                                                                                   | 0.65 V <sub>pp</sub><br>to 5.0 V <sub>pp</sub> | 1.0 V <sub>pp</sub> to<br>5.0 V <sub>pp</sub> | 1.3 V <sub>pp</sub> to<br>5.0 V <sub>pp</sub> | 2.6 V <sub>pp</sub> to<br>5.0 V <sub>pp</sub> |                                           |

|                                      | Frequency<br>range20 MHz13 MHz10 MHz5 MHz to<br>100 MHztotototo100 MHz100 MHz100 MHz100 MHz100 MHz |                                                |                                               |                                               |                                               | Supported by<br>NI 6544 and<br>6547 only. |

|                                      |                                                                                                    | 20 MHz<br>to<br>200 MHz                        | 13 MHz<br>to<br>200 MHz                       | 10 MHz<br>to<br>200 MHz                       | 5 MHz to<br>200 MHz                           | Supported by<br>NI 6545 and<br>6548 only. |

| Specification                               | Value                                                                            | Comments                                                                                        |

|---------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

|                                             | As Sample Clock                                                                  |                                                                                                 |

| Frequency<br>range                          | NI 6544 and NI 6547: 20 kHz to 100 MHz<br>NI 6545 and NI 6548: 20 kHz to 200 MHz | Nominal<br>3 dB cutoff<br>point at<br>100 MHz<br>when using<br>1 k $\Omega$ input<br>impedance. |

| Duty cycle<br>range                         | f < 20  MHz:  25%  to  75%<br>$f \ge 20 \text{ MHz: } 40\% \text{ to } 60\%$     | —                                                                                               |

|                                             | As Reference Clock                                                               |                                                                                                 |

| Reference<br>clock<br>frequency<br>range    | 5 MHz to 100 MHz (Integer multiples of 1 MHz)                                    | _                                                                                               |

| Reference<br>clock<br>frequency<br>accuracy | ± 0.1%                                                                           | Required<br>accuracy of<br>the external<br>Reference<br>clock source.                           |

| Reference<br>clock duty<br>cycle            | 25% to 75%                                                                       | —                                                                                               |

### STROBE (DDC Connector)

| Specification              | Value                                                                                                                                                                               | Comments                                         |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Direction                  | Input to device                                                                                                                                                                     | —                                                |

| Destinations               | Sample clock (acquisition only)                                                                                                                                                     | —                                                |

| STROBE<br>frequency range  | NI 6544, NI 6547: 100 Hz to 100 MHz<br>NI 6545, NI 6548: 100 Hz to 200 MHz                                                                                                          | —                                                |

| STROBE duty<br>cycle range | 40% to 60% for clock frequencies $\ge$ 20 MHz<br>25% to 75% for clock frequencies $<$ 20 MHz<br><b>Note</b> : STROBE duty cycle is corrected to 50% at frequencies<br>$\ge$ 20 MHz. | Duty cycle<br>at the<br>programmed<br>threshold. |

| Specification                        | Value                                                                                                                                                      | Comments                                                         |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Minimum<br>detectable pulse<br>width | 2 ns                                                                                                                                                       | Nominal;<br>required at<br>acquisition<br>voltage<br>thresholds. |

| Voltage<br>thresholds                | Refer to the <i>Acquisition Timing (Data, STROBE, and PFI &lt; 03&gt;</i><br><i>Channels)</i> specifications in the <i>Channel Specifications</i> section. | —                                                                |

| Clock<br>requirements                | Clock must be continuous and free-running.                                                                                                                 | —                                                                |

| Input<br>impedance                   | 50 kΩ                                                                                                                                                      | Nominal.                                                         |

#### CLK OUT (SMA Jack Connector)

| Specification              | Value                                                                                                                                        | Comments |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Direction                  | Output from device                                                                                                                           | —        |

| Sources                    | <ol> <li>Sample clock (excluding STROBE)</li> <li>Reference clock (PLL)</li> </ol>                                                           | —        |

| Output<br>impedance        | 50 Ω                                                                                                                                         | Nominal. |

| Electrical characteristics | Refer to the <i>Generation Channels (Data, DDC CLK OUT, and PFI &lt;03&gt;)</i> specifications in the <i>Channel Specifications</i> section. | —        |

| Logic type                 | Matched with generation and acquisition sessions.                                                                                            | —        |

### DDC CLK OUT (DDC Connector)

| Specification              | Value                                                                                                                                        | Comments                                                                            |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| Direction                  | Output from device                                                                                                                           | —                                                                                   |

| Sources                    | Sample clock (generation only)                                                                                                               | STROBE and<br>acquisition<br>Sample clock<br>cannot be<br>routed to DDC<br>CLK OUT. |

| Electrical characteristics | Refer to the <i>Generation Channels (Data, DDC CLK OUT, and PFI &lt;03&gt;)</i> specifications in the <i>Channel Specifications</i> section. | —                                                                                   |

### Reference Clock (PLL)

| Specification                          | Value                                                                                                                                                           | Comments                                               |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|

| Reference<br>clock sources             | <ol> <li>PXI_CLK100 (PXI Express backplane)</li> <li>CLK IN (SMA jack connector)</li> <li>None (internal oscillator locked to an internal reference)</li> </ol> | Provides the<br>reference<br>frequency for<br>the PLL. |

| Lock time                              | 150 ms                                                                                                                                                          | Maximum,<br>not including<br>software<br>latency.      |

| Reference<br>clock<br>frequencies      | 5 MHz to 100 MHz (integer multiple of 1 MHz)                                                                                                                    | 0.1% required accuracy.                                |

| Reference<br>clock duty<br>cycle range | 25% to 75%                                                                                                                                                      | —                                                      |

| Reference<br>clock<br>destinations     | CLK OUT (SMA jack connector)                                                                                                                                    | —                                                      |

### Memory and Scripting

| Specification                                                |                                                                                                                                                                                                                                                                                                                                                | Value                                                                                                                                                                                                                                                                                                                                                        |                 | Comments                                                                                                                                    |  |

|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------|--|