#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE PXIe-7820R

# LabVIEW PDM Acquisitions Toolkit Specifications

# Contents

| PDM Acquisition Toolkit Specifications                         | 3  |

|----------------------------------------------------------------|----|

| PDM Acquisition Toolkit Specifications for PXIe-7820R/7821R    | 3  |

| PDM Acquisition Toolkit Specifications for USB-7845R/7846R     | 14 |

| Function Generator Specifications                              | 23 |

| Modulator Specifications                                       | 26 |

| Linear Chirp Specifications                                    | 26 |

| Logarithmic Chirp Specifications                               | 27 |

| Inter-IC Sound (I2S) Bus Specifications                        | 29 |

| I2S Acquisition and Generation Specifications                  | 29 |

| I2S Bank to Channel Mapping for PXIe-7820R/7821R               | 34 |

| I2S Bank to Channel Mapping for USB-7845R/7846R                | 35 |

| Connector Pin Assignments for PXIe-7820R/7821R I2S Acquisition | 35 |

| Connector Pin Assignments for PXIe-7820R/7821R I2S Generation  | 40 |

| Connector Pin Assignments for USB-7845R/7846R I2S Acquisition  | 43 |

| Connector Pin Assignments for USB-7845R/7846R I2S Generation   | 45 |

# PDM Acquisition Toolkit Specifications

The LabVIEW PDM Acquisition Toolkit supports the PXIe-7820R/7821R and USB-7845R/7846R. Refer to the product documentation for these hardware instruments on ni.com/manuals to view detailed specifications and getting started information.

# PDM Acquisition Toolkit Specifications for PXIe-7820R/7821R

Refer to these specifications when using the LabVIEW PDM Acquisition Toolkit with the PXIe-7820R/7821R.

|                                        | Acquisition                                                                   | Generation                                                        |  |  |

|----------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------------|--|--|

| Number of PDM<br>data lines            | 32, consisting of four banks of 8 data lines and 2 clock lines                | 16                                                                |  |  |

| Number of PDM channels                 | 64, consisting of four banks of 16 channels                                   | 32                                                                |  |  |

| Number of<br>timing engines            | 2                                                                             | 1                                                                 |  |  |

| Clock input/<br>output                 | Clock output—One master bit clock shared across 8 data<br>lines (16 channels) | Clock input—<br>One input<br>shared across all<br>output channels |  |  |

| Data, clock, and<br>GPIO logical level | Single-ended logic 1.2 V, 1.8 V, and 3.3 V                                    | Single-ended<br>logic 1.2 V, 1.8 V,<br>and 3.3 V                  |  |  |

| PDM clock rate                         | 10 to 4800 kb/s, master mode only                                             | 10 to 4800 kb/s,<br>slave mode only                               |  |  |

| Timebase<br>reference source           | PXI Express 100 MHz                                                           | N/A                                                               |  |  |

| Timebase accuracy error                |                                                                               |                                                                   |  |  |

| Divided clock                          | <2%, 250 ps peak-peak jitter                                                  | N/A                                                               |  |  |

| DDS clock                              | <100 ppm, 8.3 ns peak-peak jitter                                             | N/A                                                               |  |  |

### **Input Characteristics**

|                                       | Acquisition                                                                                                                                                                                          | Generation                                                                                                                                      |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Phase/<br>Synchronization             | All channels within a bank of 8 data lines are sampled<br>synchronously from a common clock. Phase relationship<br>between channels is fully maintained. Channels within a task<br>are synchronized. | All channels are<br>generated<br>synchronously<br>from the input<br>clock. Phase<br>relationship<br>between<br>channels is fully<br>maintained. |

| Generation<br>signal types            | N/A                                                                                                                                                                                                  | Sine, chirp<br>(linear or<br>logarithmic),<br>white noise, and<br>custom periodic<br>signals                                                    |

| General purpose<br>digital I/O (GPIO) | 24 static GPIO lines can be configured independently as input or output lines                                                                                                                        | 8 static GPIO<br>lines can be<br>configured<br>independently<br>as input or<br>output lines                                                     |

Refer to the **Bank to Channel Mapping for PXIe-7820R/7821R** section for the layout of banks, data lines, channels, and clock lines.

# **Decimation Filters**

| Decimation factor options | 24, 32, 48, 64, 96, and 128. Select the option by task. |

|---------------------------|---------------------------------------------------------|

|---------------------------|---------------------------------------------------------|

#### **Decimation Filter Specifications**

| Decimation Factor             | 24 and 48 | 32 and 64 | 96 and 128 |

|-------------------------------|-----------|-----------|------------|

| Normalized passband frequency | 0.4275    | 0.438     | 0.45       |

| Passband ripple (dB)          | ±0.0025   | ±0.001    | ±0.0004    |

| Normalized stopband frequency | 0.5725    | 0.562     | 0.55       |

| Stopband attenuation (dB)     | >110      | >120      | >123       |

| Decimation Factor             | 24 and 48 | 32 and 64 | 96 and 128 |

|-------------------------------|-----------|-----------|------------|

| Filter output delay (samples) | 23        | 30        | 38         |

# Acquisition and Generation Control

|                                   | Acquisition                                                     | Generation                               |

|-----------------------------------|-----------------------------------------------------------------|------------------------------------------|

| Acquisition options               | Raw PDM and/or PCM (decimated) data                             | N/A                                      |

| Acquisition/Generation mode       | Finite or Continuous                                            | Continuous                               |

| Trigger options                   | Immediate or PXI-Trigger. Independent triggering on each task   | Immediate or PXI-Trigger                 |

| Export signal options             | N/A                                                             | Start trigger to a PXI<br>trigger line   |

| PXI trigger                       | PXI-Trig [07]. Rising or Falling edge                           | PXI-Trig [07]. Rising or<br>Falling edge |

| Acquisition pre-delay             | Common pre-delay for each task applied to both PDM and PCM data | N/A                                      |

| Acquisition pre-delay resolution  | 1 PDM bitrate period                                            | N/A                                      |

| Acquisition pre-delay range       | 0 to 16383 bitrate periods                                      | N/A                                      |

| Acquisition post-delay            | Common post-delay for each task and applied to decimated data   | N/A                                      |

| Acquisition post-delay resolution | 1 decimated data period                                         | N/A                                      |

| Acquisition post-delay range      | 0 to 2 <sup>27</sup> -2 (134,217,726) decimated data periods    | N/A                                      |

# Simulation Mode

| PDM         | Sine tone with a PDM amplitude of ±0.7071 FS (0.500 RMS) |

|-------------|----------------------------------------------------------|

| simulation  |                                                          |

| signal type |                                                          |

| Tone<br>frequency   | Proportional to the selected PDM rate and repeats for every group of 16 PDM<br>channel inputs.<br>For a PDM rate of 3.072 MHz, tone frequency is 1 kHz for the first PDM channel input,<br>increments by 1 kHz for each PDM channel input, and repeats this sequence for<br>every 16 PDM channel inputs. The following table illustrates the tone frequencies at<br>3.072 MHz for all 64 PDM channel inputs. |        |  |

|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|

|                     | PDM Channel Input 0L                                                                                                                                                                                                                                                                                                                                                                                         | 1 kHz  |  |

|                     | PDM Channel Input 0R                                                                                                                                                                                                                                                                                                                                                                                         | 2 kHz  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                              |        |  |

|                     | PDM Channel Input 7L                                                                                                                                                                                                                                                                                                                                                                                         | 15 kHz |  |

|                     | PDM Channel Input 7R                                                                                                                                                                                                                                                                                                                                                                                         | 16 kHz |  |

|                     | PDM Channel Input 8L                                                                                                                                                                                                                                                                                                                                                                                         | 1 kHz  |  |

|                     | PDM Channel Input 8R                                                                                                                                                                                                                                                                                                                                                                                         | 2 kHz  |  |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                              |        |  |

|                     | PDM Channel Input 31L                                                                                                                                                                                                                                                                                                                                                                                        | 15 kHz |  |

|                     | PDM Channel Input 31R                                                                                                                                                                                                                                                                                                                                                                                        | 16 kHz |  |

|                     | Refer to the <b>Bank to Channel Mapping for PXIe-7820R/7821R</b> section for the layout of banks, data lines, channels, and clock lines.                                                                                                                                                                                                                                                                     |        |  |

| Tone start<br>phase | 0 degree for all tones when using the Configure PDM Trigger (None) VI                                                                                                                                                                                                                                                                                                                                        |        |  |

#### **Related information**

<u>Configure PDM Trigger VI</u>

# Bank to Channel Mapping for PXIe-7820R/7821R

The following table illustrates the bank to channel mapping for the PXIe-7820R/7821R.

| Bank 0 | Bank 0 PDM Data Input 0 PDM Channel Input 0L<br>PDM Channel Input 0R Bank | Bank 2 | 2 PDM Data Input<br>16 | PDM Channel Input<br>16L |   |

|--------|---------------------------------------------------------------------------|--------|------------------------|--------------------------|---|

|        |                                                                           |        |                        | PDM Channel Input<br>16R |   |

|        |                                                                           | •      |                        |                          | • |

|        |                                          | •                        |                      |                          |                          |

|--------|------------------------------------------|--------------------------|----------------------|--------------------------|--------------------------|

|        | PDM Data Input 7 PDM Channel Input<br>7L |                          | PDM Data Input<br>23 | PDM Channel Input<br>23L |                          |

|        |                                          | PDM Channel Input<br>7R  |                      |                          | PDM Channel Input<br>23R |

|        | Clock 0,1                                |                          |                      | Clock 4,5                |                          |

| Bank 1 | PDM Data Input 8                         | PDM Channel Input<br>8L  | Bank 3               | PDM Data Input<br>24     | PDM Channel Input<br>24L |

|        |                                          | PDM Channel Input<br>8R  |                      |                          | PDM Channel Input<br>24R |

|        |                                          | •                        |                      |                          | •                        |

|        |                                          | •                        |                      |                          | •                        |

|        |                                          |                          |                      |                          | •                        |

|        | PDM Data Input<br>15                     | PDM Channel Input<br>15L |                      | PDM Data Input<br>31     | PDM Channel Input<br>31L |

|        |                                          | PDM Channel Input<br>15R |                      |                          | PDM Channel Input<br>31R |

|        | Clock 2,3                                |                          |                      | Clock 6,7                |                          |

# Connector Pin Assignments for PXIe-7820R/7821R PDM Acquisition

Use the following connector pin assignments when you configure pin functions for PDM acquisition using the PXIe-7820R/7821R.

| Terminal | Function | Assignment   |

|----------|----------|--------------|

| 1        | DIO31    | PDM Input 15 |

| 2        | GND      |              |

| 3        | DIO29    | GPIO 11      |

| 4        | GND      |              |

| 5        | DIO27    | GPIO 9       |

| Terminal | Function | Assignment         |

|----------|----------|--------------------|

| 6        | GND      |                    |

| 7        | DIO25    | PDM Input 13       |

| 8        | GND      |                    |

| 9        | DIO23    | PDM Input 11       |

| 10       | GND      |                    |

| 11       | DIO21    | PDM Input 9        |

| 12       | GND      |                    |

| 13       | DIO19    | PDM Clock Output 3 |

| 14       | GND      |                    |

| 15       | DIO17    | GPIO 7             |

| 16       | GND      |                    |

| 17       | DIO15    | GPIO 5             |

| 18       | GND      |                    |

| 19       | DIO13    | PDM Clock Output 1 |

| 20       | GND      |                    |

| 21       | DIO11    | PDM Input 7        |

| 22       | GND      |                    |

| 23       | DIO9     | PDM Input 5        |

| 24       | GND      |                    |

| 25       | DIO7     | PDM Input 3        |

| 26       | GND      |                    |

| 27       | DIO5     | GPIO 3             |

| 28       | GND      |                    |

| 29       | DIO3     | GPIO 1             |

| 30       | GND      |                    |

| 31       | DIO1     | PDM Input 1        |

| 32       | GND      |                    |

| 33       | GND      |                    |

| 34       | GND      |                    |

| 35       | DIO30    | PDM Clock Output 2 |

| 36       | GND      |                    |

| Terminal | Function                  | Assignment         |

|----------|---------------------------|--------------------|

| 37       | DIO28                     | PDM Input 14       |

| 38       | GND                       |                    |

| 39       | DIO26                     | PDM Input 12       |

| 40       | GND                       |                    |

| 41       | DIO24                     | PDM Input 10       |

| 42       | GND                       |                    |

| 43       | DIO22                     | GPIO 10            |

| 44       | GND                       |                    |

| 45       | DIO20                     | GPIO 8             |

| 46       | GND                       |                    |

| 47       | DIO18                     | GPIO 6             |

| 48       | GND                       |                    |

| 49       | DIO16                     | PDM Input 8        |

| 50       | GND                       |                    |

| 51       | DIO14                     | PDM Input 6        |

| 52       | GND                       |                    |

| 53       | DIO12                     | GPIO 4             |

| 54       | GND                       |                    |

| 55       | DIO10                     | GPIO 2             |

| 56       | GND                       |                    |

| 57       | DIO8                      | GPIO 0             |

| 58       | GND                       |                    |

| 59       | DIO6                      | PDM Input 4        |

| 60       | GND                       |                    |

| 61       | DIO4                      | PDM Input 2        |

| 62       | GND                       |                    |

| 63       | DIO2                      | PDM Input 0        |

| 64       | GND                       |                    |

| 65       | DIO0                      | PDM Clock Output 0 |

| 66       | GND                       |                    |

| 67       | External Clock <b>x</b> * |                    |

| Terminal                                                                      | Function | Assignment |

|-------------------------------------------------------------------------------|----------|------------|

| 68                                                                            | GND      |            |

| * <b>x</b> is the connector number. External Clock <b>x</b> is an input only. |          |            |

| Terminal | Function | Assignment         |

|----------|----------|--------------------|

| 1        | DIO31    | PDM Input 31       |

| 2        | GND      |                    |

| 3        | DIO29    | GPIO 23            |

| 4        | GND      |                    |

| 5        | DIO27    | GPIO 21            |

| 6        | GND      |                    |

| 7        | DIO25    | PDM Input 29       |

| 8        | GND      |                    |

| 9        | DIO23    | PDM Input 27       |

| 10       | GND      |                    |

| 11       | DIO21    | PDM Input 25       |

| 12       | GND      |                    |

| 13       | DIO19    | PDM Clock Output 7 |

| 14       | GND      |                    |

| 15       | DIO17    | GPIO 19            |

| 16       | GND      |                    |

| 17       | DIO15    | GPIO 17            |

| 18       | GND      |                    |

| 19       | DIO13    | PDM Clock Output 5 |

| 20       | GND      |                    |

| 21       | DIO11    | PDM Input 23       |

| 22       | GND      |                    |

| 23       | DIO9     | PDM Input 21       |

| 24       | GND      |                    |

| 25       | DIO7     | PDM Input 19       |

| Terminal | Function | Assignment         |

|----------|----------|--------------------|

| 26       | GND      |                    |

| 27       | DIO5     | GPIO 15            |

| 28       | GND      |                    |

| 29       | DIO3     | GPIO 13            |

| 30       | GND      |                    |

| 31       | DIO1     | PDM Input 17       |

| 32       | GND      |                    |

| 33       | GND      |                    |

| 34       | GND      |                    |

| 35       | DIO30    | PDM Clock Output 6 |

| 36       | GND      |                    |

| 37       | DIO28    | PDM Input 30       |

| 38       | GND      |                    |

| 39       | DIO26    | PDM Input 28       |

| 40       | GND      |                    |

| 41       | DIO24    | PDM Input 26       |

| 42       | GND      |                    |

| 43       | DIO22    | GPIO 22            |

| 44       | GND      |                    |

| 45       | DIO20    | GPIO 20            |

| 46       | GND      |                    |

| 47       | DIO18    | GPIO 18            |

| 48       | GND      |                    |

| 49       | DIO16    | PDM Input 24       |

| 50       | GND      |                    |

| 51       | DIO14    | PDM Input 22       |

| 52       | GND      |                    |

| 53       | DIO12    | GPIO 16            |

| 54       | GND      |                    |

| 55       | DIO10    | GPIO 14            |

| 56       | GND      |                    |

| Terminal                                                                      | Function                  | Assignment         |

|-------------------------------------------------------------------------------|---------------------------|--------------------|

| 57                                                                            | DIO8                      | GPIO 12            |

| 58                                                                            | GND                       |                    |

| 59                                                                            | DIO6                      | PDM Input 20       |

| 60                                                                            | GND                       |                    |

| 61                                                                            | DIO4                      | PDM Input 18       |

| 62                                                                            | GND                       |                    |

| 63                                                                            | DIO2                      | PDM Input 16       |

| 64                                                                            | GND                       |                    |

| 65                                                                            | DIO0                      | PDM Clock Output 4 |

| 66                                                                            | GND                       |                    |

| 67                                                                            | External Clock <b>x</b> * |                    |

| 68                                                                            | GND                       |                    |

| * <b>x</b> is the connector number. External Clock <b>x</b> is an input only. |                           |                    |

# Connector Pin Assignments for PXIe-7820R/7821R PDM Generation

Use the following connector pin assignments when you configure pin functions for PDM generation using the PXIe-7820R/7821R.

| Terminal | Function | Assignment    |

|----------|----------|---------------|

| 1        | DIO31    | PDM Output 15 |

| 2        | GND      |               |

| 3        | DIO29    |               |

| 4        | GND      |               |

| 5        | DIO27    |               |

| 6        | GND      |               |

| 7        | DIO25    | PDM Output 13 |

| 8        | GND      |               |

| 9        | DIO23    | PDM Output 11 |

| Terminal | Function | Assignment    |

|----------|----------|---------------|

| 10       | GND      |               |

| 11       | DIO21    | PDM Output 9  |

| 12       | GND      |               |

| 13       | DIO19    |               |

| 14       | GND      |               |

| 15       | DIO17    | GPIO 7        |

| 16       | GND      |               |

| 17       | DIO15    | GPIO 5        |

| 18       | GND      |               |

| 19       | DIO13    |               |

| 20       | GND      |               |

| 21       | DIO11    | PDM Output 7  |

| 22       | GND      |               |

| 23       | DIO9     | PDM Output 5  |

| 24       | GND      |               |

| 25       | DIO7     | PDM Output 3  |

| 26       | GND      |               |

| 27       | DIO5     | GPIO 3        |

| 28       | GND      |               |

| 29       | DIO3     | GPIO 1        |

| 30       | GND      |               |

| 31       | DIO1     | PDM Output 1  |

| 32       | GND      |               |

| 33       | GND      |               |

| 34       | GND      |               |

| 35       | DIO30    |               |

| 36       | GND      |               |

| 37       | DIO28    | PDM Output 14 |

| 38       | GND      |               |

| 39       | DIO26    | PDM Output 12 |

| 40       | GND      |               |

| Terminal                  | Function                                     | Assignment    |

|---------------------------|----------------------------------------------|---------------|

| 41                        | DIO24                                        | PDM Output 10 |

| 42                        | GND                                          |               |

| 43                        | DIO22                                        |               |

| 44                        | GND                                          |               |

| 45                        | DIO20                                        |               |

| 46                        | GND                                          |               |

| 47                        | DIO18                                        | GPIO 6        |

| 48                        | GND                                          |               |

| 49                        | DIO16                                        | PDM Output 8  |

| 50                        | GND                                          |               |

| 51                        | DIO14                                        | PDM Output 6  |

| 52                        | GND                                          |               |

| 53                        | DIO12                                        | GPIO 4        |

| 54                        | GND                                          |               |

| 55                        | DIO10                                        | GPIO 2        |

| 56                        | GND                                          |               |

| 57                        | DIO8                                         | GPIO 0        |

| 58                        | GND                                          |               |

| 59                        | DIO6                                         | PDM Output 4  |

| 60                        | GND                                          |               |

| 61                        | DIO4                                         | PDM Output 2  |

| 62                        | GND                                          |               |

| 63                        | DIO2                                         | PDM Output 0  |

| 64                        | GND                                          |               |

| 65                        | DIOO                                         | PDM Clock 0   |

| 66                        | GND                                          |               |

| 67                        | External Clock <b>x</b> *                    |               |

| 68                        | GND                                          |               |

| * <b>x</b> is the connect | tor number. External Clock <b>x</b> is an in | put only.     |

# PDM Acquisition Toolkit Specifications for USB-7845R/7846R

Refer to these specifications when using the LabVIEW PDM Acquisition Toolkit with the USB-7845R/7846R.

### Input Characteristics

|                                        | Acquisition                                                                                                                                                                                          | Generation                                                                                                                                      |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Number of PDM<br>data lines            | 8, consisting of one bank of 8 data lines and 2 clock lines                                                                                                                                          | 8                                                                                                                                               |

| Number of PDM channels                 | 16                                                                                                                                                                                                   | 16                                                                                                                                              |

| Number of timing engines               | 1                                                                                                                                                                                                    | 1                                                                                                                                               |

| Clock input/<br>output                 | Clock output—One master bit clock shared across 8 data<br>lines (16 channels)                                                                                                                        | Clock input—One<br>input shared<br>across all output<br>channels                                                                                |

| Data, clock, and<br>GPIO logical level | Single-ended logic 1.2 V, 1.8 V, and 3.3 V                                                                                                                                                           | Single-ended<br>logic 1.2 V, 1.8 V,<br>and 3.3 V                                                                                                |

| PDM clock rate                         | 10 to 4800 kb/s, master mode only                                                                                                                                                                    | 10 to 4800 kb/s,<br>slave mode only                                                                                                             |

| Timebase<br>reference source           | PXI Express 100 MHz                                                                                                                                                                                  | N/A                                                                                                                                             |

| Timebase accurac                       | y error                                                                                                                                                                                              |                                                                                                                                                 |

| Divided clock                          | <2%, 250 ps peak-peak jitter                                                                                                                                                                         | N/A                                                                                                                                             |

| DDS clock                              | <100 ppm, 8.3 ns peak-peak jitter                                                                                                                                                                    | N/A                                                                                                                                             |

| Phase/<br>Synchronization              | All channels within a bank of 8 data lines are sampled<br>synchronously from a common clock. Phase relationship<br>between channels is fully maintained. Channels within a<br>task are synchronized. | All channels are<br>generated<br>synchronously<br>from the input<br>clock. Phase<br>relationship<br>between<br>channels is fully<br>maintained. |

|                                       | Acquisition                                                                  | Generation                                                                                  |

|---------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| Generation signal<br>types            | N/A                                                                          | Sine, chirp (linear<br>or logarithmic),<br>white noise, and<br>custom periodic<br>signals   |

| General purpose<br>digital I/O (GPIO) | 8 static GPIO lines can be configured independently as input or output lines | 8 static GPIO<br>lines can be<br>configured<br>independently as<br>input or output<br>lines |

Refer to the **Bank to Channel Mapping for USB-7845R/7846R** section for the layout of banks, data lines, channels, and clock lines.

#### **Decimation Filters**

| Decimation factor options | 24, 32, 48, 64, 96, and 128. Select the option by task. |

|---------------------------|---------------------------------------------------------|

|---------------------------|---------------------------------------------------------|

#### **Decimation Filter Specifications**

| Decimation Factor             | 24 and 48 | 32 and 64 | 96 and 128 |

|-------------------------------|-----------|-----------|------------|

| Normalized passband frequency | 0.4275    | 0.438     | 0.45       |

| Passband ripple (dB)          | ±0.0025   | ±0.001    | ±0.0004    |

| Normalized stopband frequency | 0.5725    | 0.562     | 0.55       |

| Stopband attenuation (dB)     | >110      | >120      | >123       |

| Filter output delay (samples) | 23        | 30        | 38         |

### Acquisition and Generation Control

|                             | Acquisition                         | Generation |

|-----------------------------|-------------------------------------|------------|

| Acquisition options         | Raw PDM and/or PCM (decimated) data | N/A        |

| Acquisition/Generation mode | Finite or Continuous                | Continuous |

|                                   | Acquisition                                                     | Generation     |

|-----------------------------------|-----------------------------------------------------------------|----------------|

| Trigger options                   | Immediate only                                                  | Immediate only |

| Export signal options             | N/A                                                             | None           |

| Acquisition pre-delay             | Common pre-delay for each task applied to both PDM and PCM data | N/A            |

| Acquisition pre-delay resolution  | 1 PDM bitrate period                                            | N/A            |

| Acquisition pre-delay range       | 0 to 16383 bitrate periods                                      | N/A            |

| Acquisition post-delay            | Common post-delay for each task and applied to decimated data   | N/A            |

| Acquisition post-delay resolution | 1 decimated data period                                         | N/A            |

| Acquisition post-delay range      | 0 to 2 <sup>27</sup> -2 (134,217,726) decimated data periods    | N/A            |

# Simulation Mode

| PDM<br>simulation<br>signal type | Sine tone with a PDM amplitude of ±0.7071 FS (0.500 RMS)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |        |  |  |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--|--|

| Tone<br>frequency                | Proportional to the selected PDM rate.<br>For a PDM rate of 3.072 MHz, tone frequency is 1 kHz for the first PDM channel input<br>and increments by 1 kHz for each PDM channel input. The following table illustrates<br>the tone frequencies at 3.072 MHz for all 16 PDM channel inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |        |  |  |

|                                  | PDM Channel Input 0L 1 kHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |  |  |

|                                  | PDM Channel Input 0R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 2 kHz  |  |  |

|                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |  |  |

|                                  | PDM Channel Input 7L                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 15 kHz |  |  |

|                                  | PDM Channel Input 7R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 16 kHz |  |  |

| Tone start                       | Refer to the <b>Bank to Channel Mapping for USB-7</b><br>layout of banks, data lines, channels, and clock line of banks, data lines, channels, and clock line of banks, data lines when using the Configure Plance of the configure of the configure Plance of the configure of | nes.   |  |  |

| phase                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        |  |  |

#### **Related information**

<u>Configure PDM Trigger VI</u>

#### Bank to Channel Mapping for USB-7845R/7846R

The following table illustrates the bank to channel mapping for the USB-7845R/7846R.

| Bank 0 PDM Data Input 0 | PDM Channel Input 0L |                      |

|-------------------------|----------------------|----------------------|

|                         |                      | PDM Channel Input 0R |

|                         |                      | •                    |

|                         |                      |                      |

|                         |                      |                      |

|                         | PDM Data Input 7     | PDM Channel Input 7L |

|                         |                      | PDM Channel Input 7R |

|                         | Clock 0,1            |                      |

# Connector Pin Assignments for USB-7845R/7846R PDM Acquisition

Use the following connector pin assignments when you configure pin functions for PDM acquisition using the USB-7845R/7846R.

| Terminal | Function | Assignment |

|----------|----------|------------|

| 1        | DIO31    |            |

| 2        | GND      |            |

| 3        | DIO29    |            |

| 4        | GND      |            |

| 5        | DIO27    |            |

| 6        | GND      |            |

| 7        | DIO25    |            |

| 8        | GND      |            |

| Terminal | Function | Assignment         |

|----------|----------|--------------------|

| 9        | DIO23    |                    |

| 10       | GND      |                    |

| 11       | DIO21    |                    |

| 12       | GND      |                    |

| 13       | DIO19    |                    |

| 14       | GND      |                    |

| 15       | DIO17    | GPIO 7             |

| 16       | GND      |                    |

| 17       | DIO15    | GPIO 5             |

| 18       | GND      |                    |

| 19       | DIO13    | PDM Clock Output 1 |

| 20       | GND      |                    |

| 21       | DIO11    | PDM Input 7        |

| 22       | GND      |                    |

| 23       | DIO9     | PDM Input 5        |

| 24       | GND      |                    |

| 25       | DIO7     | PDM Input 3        |

| 26       | GND      |                    |

| 27       | DIO5     | GPIO 3             |

| 28       | GND      |                    |

| 29       | DIO3     | GPIO 1             |

| 30       | GND      |                    |

| 31       | DIO1     | PDM Input 1        |

| 32       | GND      |                    |

| 33       | GND      |                    |

| 34       | GND      |                    |

| 35       | DIO30    |                    |

| 36       | GND      |                    |

| 37       | DIO28    |                    |

| 38       | GND      |                    |

| 39       | DIO26    |                    |

| Terminal                  | Function                                 | Assignment         |

|---------------------------|------------------------------------------|--------------------|

| 40                        | GND                                      |                    |

| 41                        | DIO24                                    |                    |

| 42                        | GND                                      |                    |

| 43                        | DIO22                                    |                    |

| 44                        | GND                                      |                    |

| 45                        | DIO20                                    |                    |

| 46                        | GND                                      |                    |

| 47                        | DIO18                                    | GPIO 6             |

| 48                        | GND                                      |                    |

| 49                        | DIO16                                    |                    |

| 50                        | GND                                      |                    |

| 51                        | DIO14                                    | PDM Input 6        |

| 52                        | GND                                      |                    |

| 53                        | DIO12                                    | GPIO 4             |

| 54                        | GND                                      |                    |

| 55                        | DIO10                                    | GPIO 2             |

| 56                        | GND                                      |                    |

| 57                        | DIO8                                     | GPIO 0             |

| 58                        | GND                                      |                    |

| 59                        | DIO6                                     | PDM Input 4        |

| 60                        | GND                                      |                    |

| 61                        | DIO4                                     | PDM Input 2        |

| 62                        | GND                                      |                    |

| 63                        | DIO2                                     | PDM Input 0        |

| 64                        | GND                                      |                    |

| 65                        | DIO0                                     | PDM Clock Output 0 |

| 66                        | GND                                      |                    |

| 67                        | External Clock <b>x</b> *                |                    |

| 68                        | GND                                      |                    |

| * <b>x</b> is the connect | tor number. External Clock <b>x</b> is a | n input only.      |

# Connector Pin Assignments for USB-7845R/7846R PDM Generation

Use the following connector pin assignments when you configure pin functions for PDM generation using the USB-7845R/7846R.

| Terminal | Function | Assignment   |

|----------|----------|--------------|

| 1        | DIO31    |              |

| 2        | GND      |              |

| 3        | DIO29    |              |

| 4        | GND      |              |

| 5        | DIO27    |              |

| 6        | GND      |              |

| 7        | DIO25    |              |

| 8        | GND      |              |

| 9        | DIO23    |              |

| 10       | GND      |              |

| 11       | DIO21    |              |

| 12       | GND      |              |

| 13       | DIO19    |              |

| 14       | GND      |              |

| 15       | DIO17    | GPIO 7       |

| 16       | GND      |              |

| 17       | DIO15    | GPIO 5       |

| 18       | GND      |              |

| 19       | DIO13    |              |

| 20       | GND      |              |

| 21       | DIO11    | PDM Output 7 |

| 22       | GND      |              |

| 23       | DIO9     | PDM Output 5 |

| 24       | GND      |              |

| Terminal | Function | Assignment   |

|----------|----------|--------------|

| 25       | DIO7     | PDM Output 3 |

| 26       | GND      |              |

| 27       | DIO5     | GPIO 3       |

| 28       | GND      |              |

| 29       | DIO3     | GPIO 1       |

| 30       | GND      |              |

| 31       | DIO1     | PDM Output 1 |

| 32       | GND      |              |

| 33       | GND      |              |

| 34       | GND      |              |

| 35       | DIO30    |              |

| 36       | GND      |              |

| 37       | DIO28    |              |

| 38       | GND      |              |

| 39       | DIO26    |              |

| 40       | GND      |              |

| 41       | DIO24    |              |

| 42       | GND      |              |

| 43       | DIO22    |              |

| 44       | GND      |              |

| 45       | DIO20    |              |

| 46       | GND      |              |

| 47       | DIO18    | GPIO 6       |

| 48       | GND      |              |

| 49       | DIO16    |              |

| 50       | GND      |              |

| 51       | DIO14    | PDM Output 6 |

| 52       | GND      |              |

| 53       | DIO12    | GPIO 4       |

| 54       | GND      |              |

| 55       | DIO10    | GPIO 2       |

| Terminal                                                                      | Function                  | Assignment         |

|-------------------------------------------------------------------------------|---------------------------|--------------------|

| 56                                                                            | GND                       |                    |

| 57                                                                            | DIO8                      | GPIO 0             |

| 58                                                                            | GND                       |                    |

| 59                                                                            | DIO6                      | PDM Output 4       |

| 60                                                                            | GND                       |                    |

| 61                                                                            | DIO4                      | PDM Output 2       |

| 62                                                                            | GND                       |                    |

| 63                                                                            | DIO2                      | PDM Output 0       |

| 64                                                                            | GND                       |                    |

| 65                                                                            | DIO0                      | PDM Clock Output 0 |

| 66                                                                            | GND                       |                    |

| 67                                                                            | External Clock <b>x</b> * |                    |

| 68                                                                            | GND                       |                    |

| * <b>x</b> is the connector number. External Clock <b>x</b> is an input only. |                           |                    |

#### Function Generator Specifications

Refer to the following specifications and examples when generating signals using the LabVIEW PDM Acquisition Toolkit.

# Dynamic Range and Distortion Specifications

| SINAD, where test amplitude is 0.5 relative digital full scale                                                                                            |         |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--|

| Fourth order modulator                                                                                                                                    | >98 dB  |  |

| Fifth order modulator                                                                                                                                     | >124 dB |  |

| Dynamic Range, where test amplitude is 0.0005 relative digital full scale                                                                                 |         |  |

| Fourth order modulator >100 dB                                                                                                                            |         |  |

| Fifth order modulator >126 dB                                                                                                                             |         |  |

| * Measurement Conditions: PDM rate = 3.072 MHz; Modulator bandwidth = 20 kHz; Test signal = 1 kHz sine wave; Measurement bandwidth = Modulator bandwidth. |         |  |

#### Modulator Bandwidth

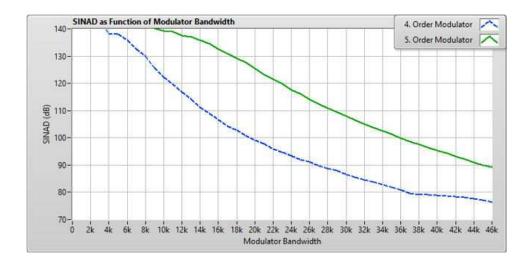

#### SINAD as a Function of Modulator Bandwidth

The following figure demonstrates the signal-to-noise and distortion ratio (SINAD) as a function of modulator bandwidth when the modulator order is 4 and 5.

\* Measurement Conditions: PDM rate = 3.072 MHz; Modulator bandwidth = 3 kHz to 46 kHz; Test frequency = 1 kHz; Test amplitude = 0.5 FS.

#### Modulator Flatness as a Function of Modulator Bandwidth

| Fourth Order Modulator                                                                |                                               |  |

|---------------------------------------------------------------------------------------|-----------------------------------------------|--|

| Modulator bandwidth ≤40 kHz                                                           | Ripple DC to modulation bandwidth < ±0.004 dB |  |

| Modulator bandwidth >40 kHz and ≤46 kHz                                               | Ripple DC to modulation bandwidth < ±0.01 dB  |  |

| Fifth Order Modulator                                                                 |                                               |  |

| Modulator bandwidth ≤40 kHz                                                           | Ripple DC to modulation bandwidth < ±0.001 dB |  |

| Modulator bandwidth >40 kHz and ≤46 kHz Ripple DC to modulation bandwidth < ±0.002 dB |                                               |  |

| * Measurement Conditions: PDM rate = 3.072 MHz                                        |                                               |  |

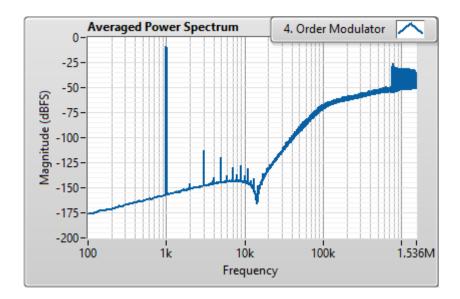

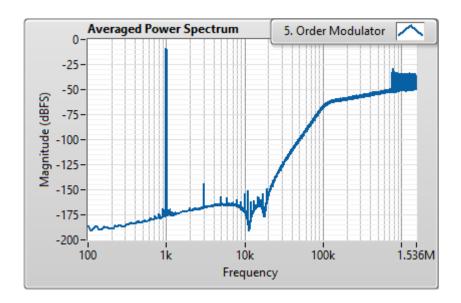

# **Spectral Characteristics**

The following figures demonstrate the averaged power spectrum when the modulator order is 4 and 5, respectively.

\* Measurement Conditions: PDM rate = 3.072 MHz; Modulator bandwidth = 20 kHz; Test frequency = 1 kHz; Test amplitude = 0.5 FS; Spectral resolution = 10 Hz; Window type = Hanning; Number of RMS averaging = 64.

### Modulator Specifications

| PDM<br>modulator<br>order                            | 4 and 5. Use the Configure Modulator VI to select the modulator order.                                                                                                                                                                                                                  |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PDM<br>modulator<br>bandwidth                        | DC to 0.015 * PCM rate. The bandwidth is DC to 46 kHz for PDM rate of 3.072 MHz. The default is                                                                                                                                                                                         |

| Recommended<br>maximum<br>output signal<br>amplitude | <ul> <li>The recommended maximum output signal amplitude depends on the modulator order.</li> <li>For the fourth order modulator, the recommended maximum output signal amplitude</li> <li>For the fifth order modulator, the recommended maximum output signal amplitude is</li> </ul> |

#### **Related information**

<u>Configure Modulator VI</u>

#### Linear Chirp Specifications

The following specifications apply to the Configure Chirp (N Ch) VI when configuring a linear chirp signal.