#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

# **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

PXIe-8135

### **GETTING STARTED GUIDE**

# MIMO Prototyping System

This document explains how to use the MIMO Application Framework with a modular hardware system consisting of multiple universal software radio peripheral (USRP) devices in a multiple input, multiple output (MIMO) configuration.

# Contents

| System Requirements                                 | 2  |

|-----------------------------------------------------|----|

| Software Requirements                               | 2  |

| Hardware Requirements                               | 3  |

| Hardware Setup                                      | 4  |

| Electromagnetic Compatibility Guidelines            | 4  |

| About the Hardware                                  | 4  |

| Base Station                                        | 4  |

| Mobile Station                                      | 6  |

| System Configurations                               | 7  |

| Hardware Setup                                      | 8  |

| Rack Assembly Diagrams                              | 8  |

| Installing PXIe Modules                             | 13 |

| Cable Connections                                   | 13 |

| Installing the Software                             | 15 |

| Powering on the Hardware                            | 15 |

| Base Station                                        | 15 |

| Mobile Station                                      | 15 |

| Connection Diagrams                                 | 16 |

| Software                                            | 19 |

| Hardware Naming                                     | 19 |

| Understanding the Components of this Sample Project | 20 |

| Create a New Project Instance                       |    |

| Folder Structure                                    | 20 |

| System Overview                                     | 22 |

| System Features                                     |    |

| System Components                                   |    |

| Running the LabVIEW Host Code                                     | 26 |

|-------------------------------------------------------------------|----|

| On the BS Host Computer                                           | 26 |

| On the MS Host Computer                                           | 27 |

| Running Video Streaming                                           | 29 |

| Start Video Stream at the Transmitter (MS)                        | 29 |

| Start Video Stream of the Receiver (BS)                           | 30 |

| Description of Controls and Indicators                            | 31 |

| Description of Controls and Indicators on the BS Host Front Panel | 31 |

| Description of Controls and Indicators on the MS Host Front Panel | 44 |

| Troubleshooting                                                   | 51 |

| Related Information                                               | 52 |

| Appendix                                                          | 53 |

| Cable Connection Mapping and Labeling                             | 53 |

| Equipment Labeling Rules                                          | 53 |

| Other Labeling Rules                                              | 53 |

| End-User License Agreements and Third-Party Legal Notices         | 69 |

| Worldwide Support and Services                                    | 69 |

|                                                                   |    |

# System Requirements

# Software Requirements

- Microsoft Windows 8/7 (64-bit) preinstalled on the PXI controller

- NI-USRP 15.5

- LabVIEW Communication System Design Suite 2.0

- MIMO Application Framework 1.0

The installation of NI software is started by running setup.exe from the provided installation media. Follow the installer prompts to complete the installation process.

# Hardware Requirements

Depending on the configuration, the main system hardware components are listed in the following table.

Table 1. MIMO Base Station (BS) Parts List<sup>1</sup>

|                             | Quantity needed for each configuration |                |                |               |  |

|-----------------------------|----------------------------------------|----------------|----------------|---------------|--|

|                             | 128 antennas                           | 64 antennas    | 32 antennas    | 16 antennas   |  |

| Description                 | (8 subsystems)                         | (4 subsystems) | (2 subsystems) | (1 subsystem) |  |

| USRP RIO Software Defined   | 64                                     | 32             | 16             | 8             |  |

| Radio (SDR) <sup>2</sup>    |                                        |                |                |               |  |

| x4 MXI-Express Cable        | 64                                     | 32             | 16             | 8             |  |

| PXIe-1085 Chassis (18-Slot, | 1                                      | 1              | 1              | 1             |  |

| 24 GB/s Sys Bandwidth       |                                        |                |                |               |  |

| (BW))                       |                                        |                |                |               |  |

| PXIe-8135 Controller        | 1                                      | 1              | 1              | 1             |  |

| PXIe-7976R FPGA Module      | 5                                      | 3              | 2              | 2             |  |

| for FlexRIO                 |                                        |                |                |               |  |

| PXIe-6674T Synchronization  | 1                                      | 1              | 1              | 1             |  |

| Module                      |                                        |                |                |               |  |

| 2.4 GHz and 5 GHz Dual Band | 128                                    | 64             | 32             | 16            |  |

| Vertical Antenna            |                                        |                |                |               |  |

| CDA-2990 Clock Distribution | 9                                      | 5              | 3              | 1             |  |

| Device <sup>3</sup>         |                                        |                |                |               |  |

| 8 GB RAM Upgrade for PXIe-  | 1                                      | 1              | 1              | 1             |  |

| 8135                        |                                        |                |                |               |  |

| PXIe-8384 Remote Control    | 8                                      | 4              | 2              | 1             |  |

| Module (x8 Gen2 MXI-        |                                        |                |                |               |  |

| Express)                    |                                        |                |                |               |  |

| x8 MXI-Express Cable        | 8                                      | 4              | 2              | 1             |  |

| SMA to SMA Cable            | 19                                     | 11             | 7              | 3             |  |

| CPS-8910 Switch Device for  | 8                                      | 4              | 2              | 1             |  |

| PCI Express <sup>4</sup>    |                                        |                |                |               |  |

<sup>&</sup>lt;sup>1</sup> This is not a complete list of required hardware. For a complete list please contact your local sales representative.

<sup>&</sup>lt;sup>2</sup> USRP-2940R/2942R/2943R/2944R/2950R/2952R/2953R/2954R.

<sup>&</sup>lt;sup>3</sup> Also referred to as a Clock Distribution Accessory (CDA).

<sup>&</sup>lt;sup>4</sup> Also referred to as a Cabled PXI Express Switch Box (CPS).

# Hardware Setup

# Electromagnetic Compatibility Guidelines

The individual components of this product were tested and comply with the regulatory requirements and limits for electromagnetic compatibility (EMC) stated in their respective specifications. These requirements and limits provide reasonable protection against harmful interference when the product is operated in the intended operational electromagnetic environment. However, the system as a whole has not been through EMC testing as a unit and the users are expected to use it in a way that complies to all regulations in their region.

To minimize interference with radio and television reception and prevent unacceptable performance degradation, install and use this product in strict accordance with the instructions in the product documentation.

Furthermore, any changes or modifications to the product not expressly approved by National Instruments could void your authority to operate it under your local regulatory rules.

**Note** In the United States (per FCC 47 CFR), Class A equipment is intended for use in commercial, light-industrial, and heavy-industrial locations. In Europe, Canada, Australia, and New Zealand (per CISPR 11), Class A equipment is intended for use only in heavy-industrial locations.

**Caution** The MIMO System is intended for use only indoors test environment as test and measurement equipment. This product is intended for professional use only.

**Caution** To ensure the specified EMC performance, operate this product only with shielded cables and accessories.

**Caution** To ensure the specified EMC performance, operate this product only with cables less than 3 meters in length.

### About the Hardware

The system consists of the BS and Mobile Station (MS).

**Base Station**

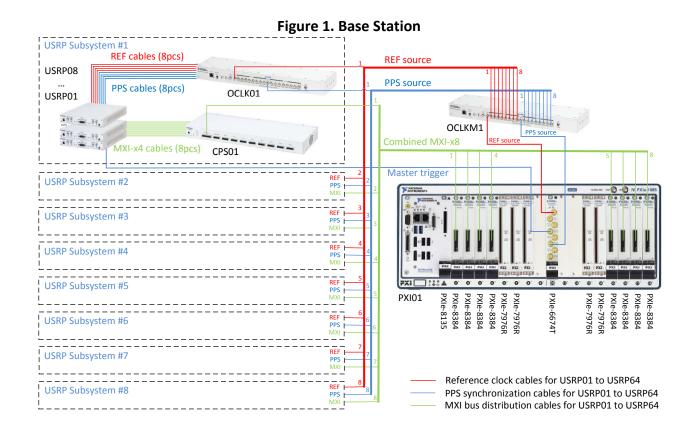

The BS consists of the PXIe-8135 controller, one to eight PXIe-8384 MXI-Express modules for communication with the USRP RIO devices (through the CPS-8910), up to five PXIe-7976R modules (depending on the number of USRP subsystems), and a PXIe-6674T module, installed on the PXIe-1085 chassis.

Clock and synchronization signals are distributed to up to eight USRP subsystems through the CDA-2990 (OCLKM1)<sup>5</sup>. It provides both clock and time synchronization by amplifying and splitting a 10 MHz reference signal, generated by the PXIe-6674T and the pulse per second (PPS) signal from master USRP, eight ways through matched-length traces.

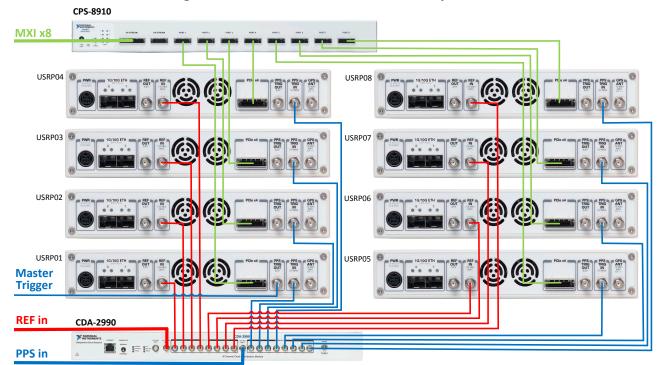

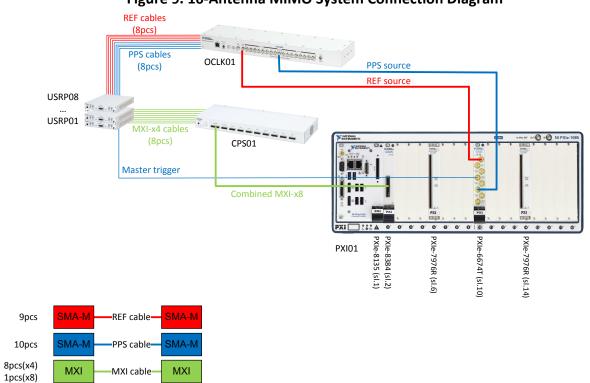

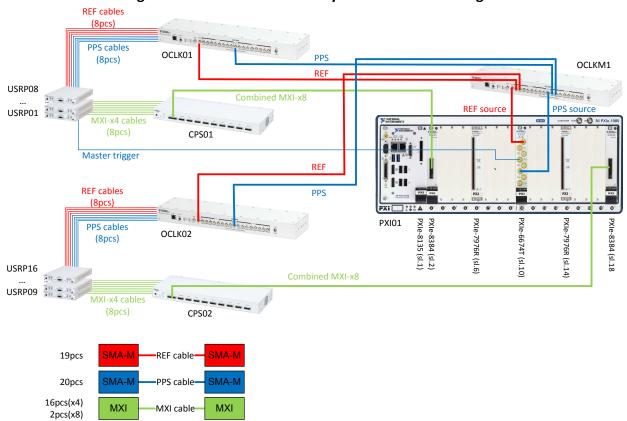

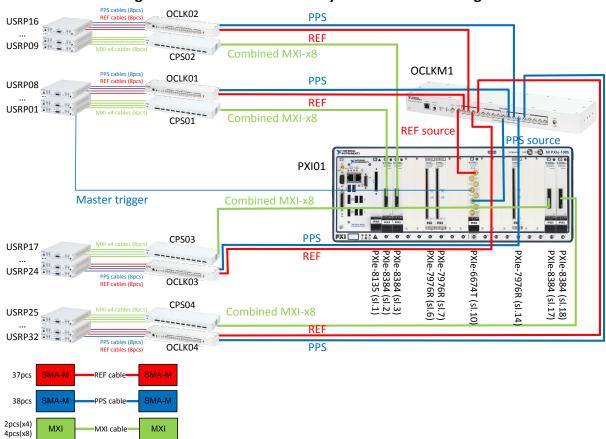

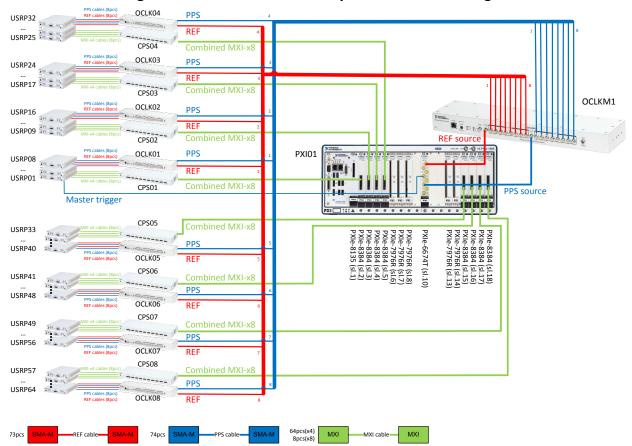

The system can control up to eight USRP subsystems. Each subsystem consists of eight USRP RIO devices, connected to the CPS-8910 device (CPS01 to CPS08). The clock and synchronization signals received by the USRP subsystem are distributed among the eight USRP RIO devices in the subsystem through the CDA-2990 (OCLK01 to OCLK08). A detailed connections diagram for each USRP subsystem is given in Figure 2.

Note The lengths of used cables are critical for timing. The signal path (the sum of the lengths of all cables from the PXIe-6674T module to each USRP RIO) must be equal for each channel.

<sup>&</sup>lt;sup>5</sup> Not required for the single subsystem configuration (up to 16 antennas), in which both clock and PPS are provided directly from the PXIe-6674T module.

Figure 2. Connections in Each USRP Subsystem

#### **Mobile Station**

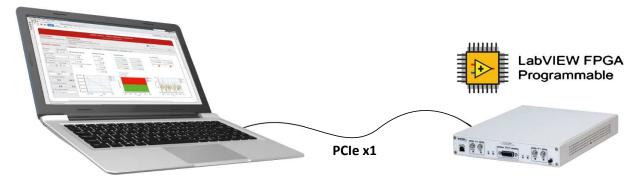

The MIMO Application Framework supports up to 12 simultaneous MSs. An MS represents a handset or other wireless device with single input, single output (SISO) wireless capabilities. The MS prototype uses a USRP RIO with an integrated GPS disciplined oscillator<sup>6</sup> (GPSDO)<sup>7</sup>, connected to a PC (typically a laptop) or PXI chassis using a cabled PCI Express to an ExpressCard. A typical testbed implementation includes multiple MSs where each USRP RIO might represent one or two MS devices. Software on the MS is implemented as a single antenna system, placing the physical layer (PHY) in the FPGA of the USRP RIO while the basic media access control (MAC) layer functionality (data piping) is split between the FPGA and host.

<sup>&</sup>lt;sup>6</sup> The GPSDO is important because it provides improved clock accuracy and enables synchronization and geo-location capability if needed in future system expansion.

<sup>&</sup>lt;sup>7</sup> USRP-2950R/2952R/2953R/2954R (USRP-295x)

Figure 3. Typical MS Setup with Laptop and USRP RIO

Table 2 provides a quick reference of parts used in a single MS system. It includes hardware devices and cables used to connect the devices as shown in Figure 3. Alternatively, a PCI Express connection can be used if a desktop or PXI chassis is chosen for the MS controller.

**Table 2. Mobile Station Equipment**

| Description                                              |   |  |  |  |  |

|----------------------------------------------------------|---|--|--|--|--|

| USRP-295x device                                         | 1 |  |  |  |  |

| USRP RIO Laptop Connectivity Kit (ExpressCard and Cable) |   |  |  |  |  |

| Laptop with ExpressCard Slot                             | 1 |  |  |  |  |

### **System Configurations**

The software can be configured to use four to 128 antennas, and the BS is typically used in one of the following configurations:

- 16 antenna MIMO (1 USRP subsystem)

- 32 antenna MIMO (2 USRP subsystems)

- 64 antenna MIMO (4 USRP subsystems)

- 128 antenna MIMO (8 USRP subsystems)

Refer to the Connection Diagrams section for detailed connection diagrams for BS systems based on each configuration.

# Hardware Setup

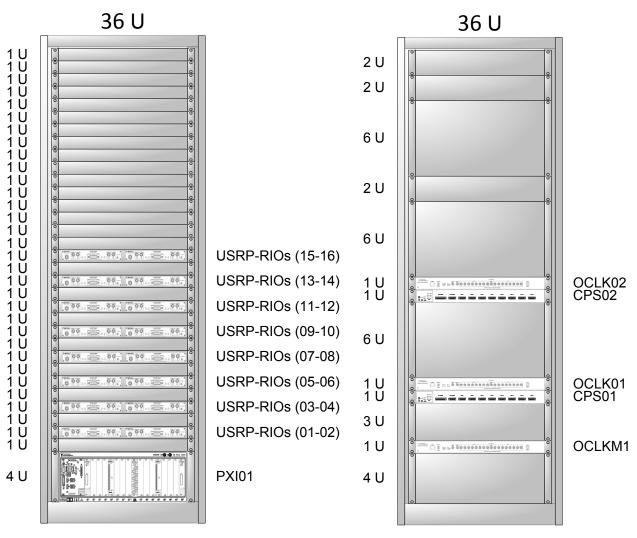

# Rack Assembly Diagrams

36 U 36 U 2 U 2 U 6 U 2 U 6 U 2 U 6 U USRP-RIOs (07-08) OCLK01 CPS01 USRP-RIOs (05-06) 1 U 1 U USRP-RIOs (03-04) 3 U USRP-RIOs (01-02) 1 U PXI01 4 U 4 U

Figure 4. 16-Antenna System

Rear view Front view

Front view Rear view

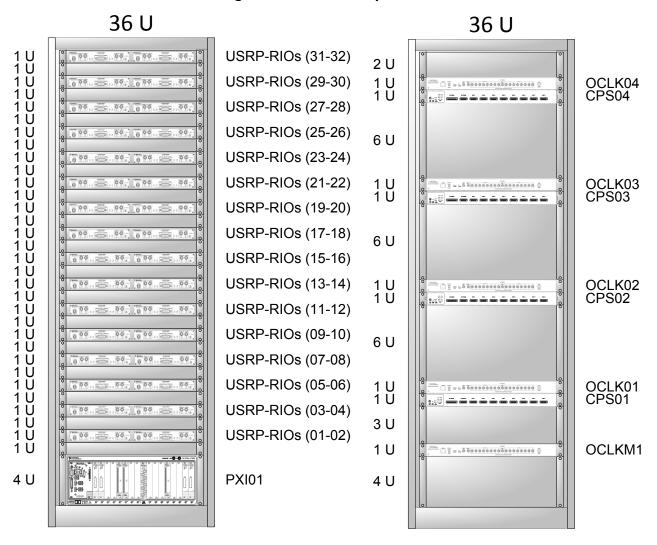

Figure 6. 64-Antenna System

Front view Rear view

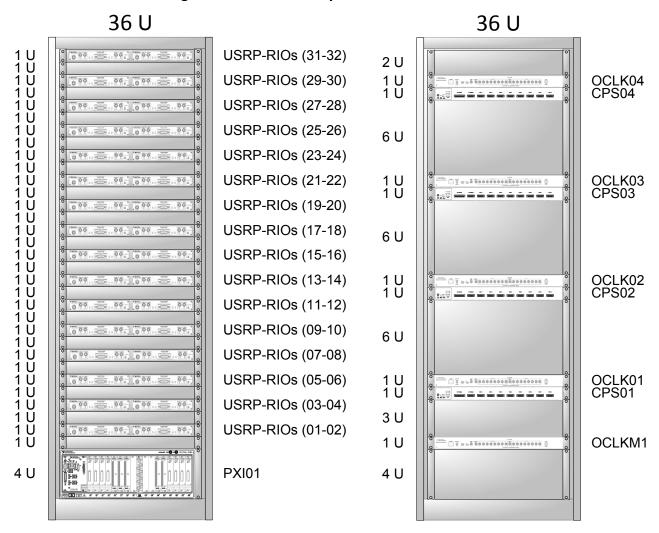

Figure 7. 128-Antenna System: Subrack 1 of 2

Front view Rear view

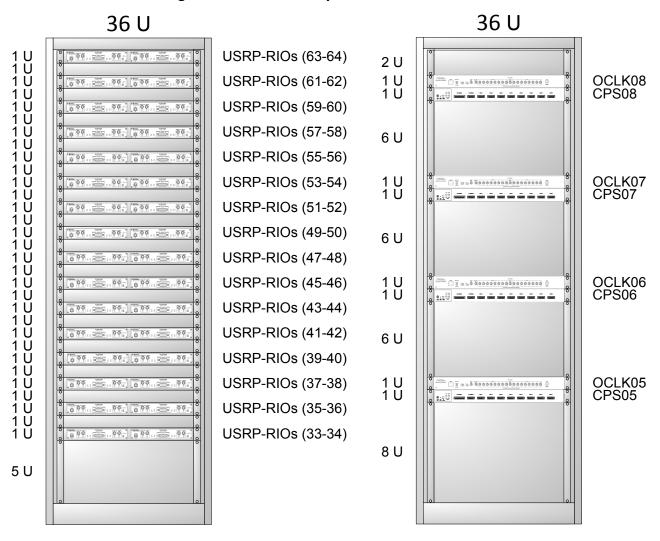

Figure 8. 128-Antenna System: Subrack 2 of 2

Front view Rear view

### Installing PXIe Modules

Install the PXIe modules on the chassis in accordance with the hardware configuration as shown in the following table.

**Table 3. MIMO BS Parts**

| PXIe-1085 | Number of Antennas (USRP subsystems) |            |            |            |  |  |

|-----------|--------------------------------------|------------|------------|------------|--|--|

| slot #    | 128 (8)                              | 64 (4)     | 32 (2)     | 16 (1)     |  |  |

| 1         | PXIe-8135                            | PXIe-8135  | PXIe-8135  | PXIe-8135  |  |  |

| 2         | PXIe-8384                            | PXIe-8384  | PXIe-8384  | PXIe-8384  |  |  |

| 3         | PXIe-8384                            | PXIe-8384  | _          | _          |  |  |

| 4         | PXIe-8384                            | _          | _          | _          |  |  |

| 5         | PXIe-8384                            | _          | _          | _          |  |  |

| 6         | PXIe-7976R                           | PXIe-7976R | PXIe-7976R | PXIe-7976R |  |  |

| 7         | PXIe-7976R                           | PXIe-7976R | _          | _          |  |  |

| 8         | PXIe-7976R                           | _          | _          | _          |  |  |

| 9         | _                                    | _          | _          | _          |  |  |

| 10        | PXIe-6674T                           | PXIe-6674T | PXIe-6674T | PXIe-6674T |  |  |

| 11        | _                                    | _          | _          | _          |  |  |

| 12        | _                                    | _          | _          | _          |  |  |

| 13        | PXIe-7976R                           | _          | _          | -          |  |  |

| 14        | PXIe-7976R                           | PXIe-7976R | PXIe-7976R | PXIe-7976R |  |  |

| 15        | PXIe-8384                            | _          | _          | _          |  |  |

| 16        | PXIe-8384                            | _          | _          | _          |  |  |

| 17        | PXIe-8384                            | PXIe-8384  | _          | _          |  |  |

| 18        | PXIe-8384                            | PXIe-8384  | PXIe-8384  | _          |  |  |

Refer to the **Connection Diagrams** section for detailed connection diagrams and interconnections tables.

### **Cable Connections**

Cabled connections between various hardware components of the system are listed in Tables 4 through 9 below.

**Table 4. Cable Connections within USRP Subsystems**

|                  |                |           |                   | Cable type<br>and |                          |

|------------------|----------------|-----------|-------------------|-------------------|--------------------------|

| Device #1        | Port           | Device #2 | Port              | quantity          | Description              |

| USRP01 to USRP08 | REF IN         | CDA       | 10 MHz OUT 1 to 8 | RF_coax (x8)      | Reference clock for USRP |

| USRP01 to USRP08 | PPS TRIG<br>IN | CDA       | PPS OUT 1 to 8    | RF_coax (x8)      | PPS trigger for USRP     |

| USRP01 to USRP08 | PCle x4        | CPS       | PORT 1 to PORT 8  | MXI (x8)          | MXI for USRP             |

Table 5. Cable Connections between the Master CDA and the CDAs in USRP Subsystems

|             |                | Port in MIMO |         |                     |     | ber of a |     |     |

|-------------|----------------|--------------|---------|---------------------|-----|----------|-----|-----|

| USRP        | Port in Master | subsystem    | Cable   |                     | 128 | 64       | 32  | 16  |

| subsystem # | CDA            | CDA          | type    | Description         | (8) | (4)      | (2) | (1) |

| 01          | 10 MHz OUT 1   | EXT 10       | RF_coax | Reference clock for | х   | х        | х   | Х   |

|             |                | MHz INPUT    |         | subsystem #1        | ^   | ^        | ^   | ^   |

| 02          | 10 MHz OUT 2   | EXT 10       | RF_coax | Reference clock for | х   | Х        | Х   |     |

|             |                | MHz INPUT    |         | subsystem #2        | ^   | ^        | ^   |     |

| 03          | 10 MHz OUT 3   | EXT 10       | RF_coax | Reference clock for | х   | Х        |     |     |

|             |                | MHz INPUT    |         | subsystem #3        | ^   | ^        |     |     |

| 04          | 10 MHz OUT 4   | EXT 10       | RF_coax | Reference clock for | х   | Х        |     |     |

|             |                | MHz INPUT    |         | subsystem #4        | ^   | ^        |     |     |

| 05          | 10 MHz OUT 5   | EXT 10       | RF_coax | Reference clock for | x   |          |     |     |

|             |                | MHz INPUT    |         | subsystem #5        | ^   |          |     |     |

| 06          | 10 MHz OUT 6   | EXT 10       | RF_coax | Reference clock for | х   |          |     |     |

|             |                | MHz INPUT    |         | subsystem #6        | ^   |          |     |     |

| 07          | 10 MHz OUT 7   | EXT 10       | RF_coax | Reference clock for | х   |          |     |     |

|             |                | MHz INPUT    |         | subsystem #7        | ^   |          |     |     |

| 08          | 10 MHz OUT 8   | EXT 10       | RF_coax | Reference clock for | х   |          |     |     |

|             |                | MHz INPUT    |         | subsystem #8        | ^   |          |     |     |

| 01          | PPS OUT 1      | EXT PPS      | RF_coax | PPS trigger for     | х   | Х        | х   | х   |

|             |                | INPUT        |         | subsystem #1        | ^   | ^        | ^   | ^   |

| 02          | PPS OUT 2      | EXT PPS      | RF_coax | PPS TRIGGER for     | х   | Х        | Х   |     |

|             |                | INPUT        |         | subsystem #2        | ^   | ^        | ^   |     |

| 03          | PPS OUT 3      | EXT PPS      | RF_coax | PPS TRIGGER for     | х   | Х        |     |     |

|             |                | INPUT        |         | subsystem #3        | ^   | ^        |     |     |

| 04          | PPS OUT 4      | EXT PPS      | RF_coax | PPS TRIGGER for     | х   | Х        |     |     |

|             |                | INPUT        |         | subsystem #4        | ^   | ^        |     |     |

| 05          | PPS OUT 5      | EXT PPS      | RF_coax | PPS TRIGGER for     | х   |          |     |     |

|             |                | INPUT        |         | subsystem #5        | ^   |          |     |     |

| 06          | PPS OUT 6      | EXT PPS      | RF_coax | PPS TRIGGER for     |     |          |     |     |

|             |                | INPUT        |         | subsystem #6        | Х   |          |     |     |

| 07          | PPS OUT 7      | EXT PPS      | RF_coax | PPS TRIGGER for     | v   |          |     |     |

|             |                | INPUT        |         | subsystem #7        | Х   |          |     |     |

| 08          | PPS OUT 8      | EXT PPS      | RF_coax | PPS TRIGGER for     | V   |          |     |     |

|             |                | INPUT        |         | subsystem #8        | Х   |          |     |     |

Table 6. Cable Connections between the PXI and the CPS in USRP subsystems

| PXIe-8384 | 128<br>(8) | 64<br>(4) | 32<br>(2) | 16<br>(1) |           |            |                      |

|-----------|------------|-----------|-----------|-----------|-----------|------------|----------------------|

| in slot # |            | JSRP sub  |           | •         | CPS port  | Cable type | Description          |

| 02        | 1          | 1         | 1         | 1         | UP STREAM | MXI        | MXI for subsystem #1 |

| 03        | 2          | 2         |           |           | UP STREAM | MXI        | MXI for subsystem #2 |

| 04        | 3          |           |           |           | UP STREAM | MXI        | MXI for subsystem #3 |

| 05        | 4          |           |           |           | UP STREAM | MXI        | MXI for subsystem #4 |

| 15        | 5          |           |           |           | UP STREAM | MXI        | MXI for subsystem #5 |

| 16        | 6          |           |           |           | UP STREAM | MXI        | MXI for subsystem #6 |

| 17        | 7          | 3         |           |           | UP STREAM | MXI        | MXI for subsystem #7 |

| 18        | 8          | 4         | 2         |           | UP STREAM | MXI        | MXI for subsystem #8 |

Table 7. Cable Connections between PXIe-6674T and Master CDA

| Output Port on PXIe-6674T | Input Port on CDA | Cable type | Description          |

|---------------------------|-------------------|------------|----------------------|

| CLK OUT                   | EXT 10 MHz INPUT  | RF_coax    | Reference clock from |

|                           |                   |            | PXI                  |

| PFI3                      | EXT PPS INPUT     | RF_coax    | PPS trigger from PXI |

Table 8. Cable Connection between USRP Subsystem #1 and the PXIe-6674T (Master Trigger)

| Port on USRP01  | Port on    |            |                    |

|-----------------|------------|------------|--------------------|

| in subsystem #1 | PXIe-6674T | Cable type | Description        |

| PPS TRIG OUT    | PFI1       | RF_coax    | Master PPS trigger |

## Installing the Software

You must be an Administrator to install NI software on your computer.

- 1. Install LabVIEW Communication System Design Suite 2.0.

- 2. Install NI-USRP 15.5.

- 3. Install MIMO Application Framework.

- 4. When the installers complete the installation, select **Restart** in the dialog box.

# Powering on the Hardware

**Caution** Ensure that all SMA connectors are properly tightened. Poor connections may result in a delay in signal propagation, resulting in poor system operation.

Caution Ensure that the PRIMARY REF flip switches on all CDA-2990 devices are in the EXTERNAL position.

#### **Base Station**

- 1. Power on all the USRP subsystems.

- 2. Power on the PXI controller.

#### Mobile Station

- 1. Power on the USRP RIO.

- 2. Power on the computer (laptop, PC, or PXI chassis) to which the USRP RIO is connected.

# Connection Diagrams

Figure 9. 16-Antenna MIMO System Connection Diagram

Figure 10. 32-Antenna MIMO System Connection Diagram

Figure 11. 64-Antenna MIMO System Connection Diagram

Figure 12. 128-Antenna MIMO System Connection Diagram

### Software

# Hardware Naming

Use MAX, or System Diagram in LabVIEW Communications, to change the hardware aliases. The MIMO Application Framework is designed to work with the hardware aliases in the following table.

**Table 9. Hardware Aliases**

| Device     | Configuration | Alias                                                                                 |

|------------|---------------|---------------------------------------------------------------------------------------|

| PXIe-6674T | All           | TIME                                                                                  |

| PXIe-7976  | All           | FLEXO, FLEX1,,FLEX4                                                                   |

| USRP RIO   | CPS switch    | CPS1Port1Dev1, CPS1Port2Dev1,,CPS1Port8Dev1,                                          |

|            | box           | CPS2Port1Dev1, CPS2Port2Dev1,,CPS2Port8Dev1, and so                                   |

|            |               | on.                                                                                   |

|            |               | You can keep the default names if you set USRP Naming Scheme to CPS(1-8)Port(1-8)Dev1 |

|            |               | Naming Scheme to CPS(1-8)Port(1-8)Dev1.                                               |

|            | PXI chassis   | PXI2Slot2Port1Dev1, PXI2Slot3Port1Dev1,,                                              |

|            |               | PXI2Slot18Port1Dev1, PXI3Slot2Port1Dev1,                                              |

|     | PXI3Slot2Port1Dev1,,PXI3Slot18Port1Dev1.                |

|-----|---------------------------------------------------------|

|     | You can keep the default names if you set USRP Naming   |

|     | Scheme to PXI(2-5)Slot(2-18)Port1Dev1.                  |

| All | Rename the USRP RIO devices to USRP01, USRP02,          |

|     | USRP03, and so on, and set <b>USRP Naming Scheme</b> to |

|     | USRP (01-64).                                           |

### Understanding the Components of this Sample Project

The development project is comprised of LabVIEW host code and LabVIEW FPGA code. The related folder structure and components of the project are described in the following subsections. The description covers the Development project, which comprises all FPGA and Host software parts. There is a Deployment project limited to the Mobile Station Host code only and does not include all contents listed below.

### Create a New Project Instance

To create a new instance of the MIMO Application Framework, launch LabVIEW Communications System Design Suite 2.0 by selecting LabVIEW Communications 2.0 from the Start menu. From the Project Templates on the launched Project tab, select Application Frameworks » MIMO Application Framework Development v1.0 to launch the project.

#### Folder Structure

The following files and folders are created inside the specified folder:

#### MIMO Development v1.0.lvproject

This project file contains reference to all VIs and targets.

#### **Base Station Host.gvi**

This is the top-level host VI of the BS, also called the Evolved Node B (eNodeB). It implements a downlink (DL) transmitter (TX) and an uplink (UL) receiver (RX) and can communicate with up to twelve MSs.

The host interfaces with multiple FlexRIO FPGA modules which serve as processors and multiple USRP RIOs which serve as remote radio heads (RRHs). The bitfiles are built from the following corresponding FPGA top-levels:

- Base Station MIMO Processor FPGA.gvi: This is the MIMO Processor top-level where the largest part of the in-phase/quadrature (I/Q) baseband signal processing is executed. A MIMO Processor bitfile can be configured to work for up to 32, 64 or 128 antennas. Each bitfile handles either all, the half or a fourth of all subcarriers per OFDM symbol. Refer to the "System Overview" section for more details.

- Base Station Bit Processor FPGA.gvi: This is the Bit Processor top-level where the TX and RX bit processing are executed. The TX packet generator as well as the RX packet validator are executed in the bit processor.

• Base Station RRH FPGA.gvi: This is the RRH top-level where the OFDM modulation and demodulation as well the interfacing with the RF is performed. Refer to the "System Overview" section for more details.

### **Mobile Station Host.gvi**

This is the top-level host VI of the MS, also called User Equipment (UE). Each host configures two MSs. The host interfaces with the bitfile built from the following corresponding FPGA top-level:

• Mobile Station FPGA.gvi: This is the MS top-level. It implements two MSs ("UE 0" and "UE 1"), each with a DL RX and UL TX.

#### **Builds**

This folder contains the precompiled bitfiles. The FlexRIO modules are loaded with MIMO Processor bitfiles. Which bitfile is used specifically depends on which of the following system configurations is used:

- MIMO Processor 32 Antennas.lvbitx: Used for BSs that are configured for up to 32 antennas.

- MIMO Processor 64 Antennas.lvbitx: Used for BSs that are configured for up to 64 antennas.

- MIMO Processor 128 Antennas.lvbitx: Used for BSs that are configured for up to 128 antennas.

For bit processing, a single FlexRIO module is loaded with Bit Processor bitfile:

Bit Processor.lvbitx: Used for BS bit processing. It works with all BS configurations.

The USRP RIOs that serve as RRHs are loaded with the following bitfiles:

- RRH Combiner.lvbitx: Used for all RRHs in a subsystem except the last one. Applicable for USRP RIO devices with 120 or 160 MHz bandwidth.

- RRH Splitter.lvbitx: Used for the last RRH in a subsystem. Applicable for USRP RIO devices with 120 or 160 MHz bandwidth.

- RRH Combiner 40 MHz.lvbitx: Used for all RRHs in a subsystem except the last one. Applicable for USRP RIO devices with 40 MHz bandwidth.

- RRH Splitter 40 MHz.lvbitx: Used for the last RRH in a subsystem. Applicable for USRP RIO devices with 40 MHz bandwidth.

The USRP RIO devices that serve as MSs are loaded with the following bitfiles:

- Mobile Station.lvbitx: Used for USRO RIO devices with 120 MHz or 160 MHz bandwidth.

- Mobile Station 40 MHz.lybitx: Used for USRO RIO devices with 40 MHz bandwidth.

#### Common

The common folder contains generic nodes for host and FPGA that are shared between different Application Frameworks, such as mathematical functions, type conversions, and so on.

#### **Link Simulator**

This folder contains the Link Simulator which simulates the UL and DL transmission chain on the host.

#### **MIMO v1.0**

This folder contains host and FPGA nodes, which were specifically designed for the MIMO Application Framework. It has three subfolders: FPGA, Host, and Types. The Types subfolder contains type definitions that are required in the system.

#### Resources

This folder contains the FPGA resources which are needed for the bitfiles to compile.

#### **USRP RIO 120 MHz BW**

This directory was taken from the NI USRP RIO Multi-Device Streaming project.

#### **Testbenches**

Host simulation test benches for all parts of the design.

# System Overview

The MIMO Application framework provides the functional elements of the PHY as well as the basic MAC of both BS and MSs. It includes the following elements:

- MIMO DL data transmission and reception

- MIMO UL data transmission and reception

- Synchronization of BSs and MSs, either over a common trigger signal, or over-the-air using the primary synchronization sequence (PSS)

- Basic MAC functionality provided for packet-based user data transmission in DL and UL to enable user data streaming applications

#### System Features

The MIMO Application Framework is presented on a flexible platform. It supports the following features:

- Scalable number of antennas from four to 128 at the BSs. Data rates and interfaces scale automatically.

- One to 12 MSs.

- 20 MHz bandwidth with a frame structure based on long-term evolution (LTE).

- Fully reconfigurable frame schedule.

- Multi-user MIMO precoding and equalization on FPGA including  $128 \times 12$  minimum mean squared error (MMSE), zero-forcing (ZF), and maximum-ratio combining (MRC).

- Bidirectional Time Division Duplex (TDD) with fully reconfigurable UL and DL.

- Channel reciprocity calibration per RF channel.

- Aggregates all data to the processing units.

- Time and frequency synchronization over-the-air, all using commercial off-the-shelf components.

- Support for different modulation schemes for modulating the data subcarriers: quadrature phase shift keying (QPSK), 16-quadrature amplitude modulation (QAM), 64-QAM, and 256-QAM.

Visit ni.com/info and enter the Info Code exrukz to access the MIMO Application Framework White Paper for more information about the MIMO Application Framework design.

### System Components

#### Base Station

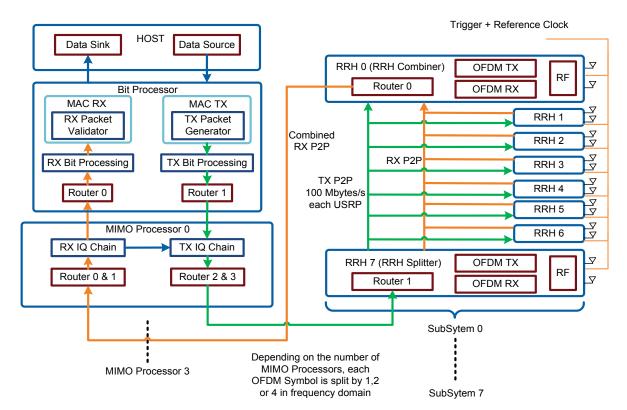

The following figure shows the block diagram of the BS in the UL and DL. The components perform the following tasks:

Host: Configures the system and displays the system status. Interfaces with multiple processor bitfiles loaded to the FlexRIO modules and multiple RRH bitfiles loaded to the USRP RIO devices. It also receives and transmits payload data using the user datagram protocol (UDP).

- Data Source: Data source for the DL payload data. If configured as "UDP," data is read from the configured UDP ports.

- Data Sink: Data sink for the received UL payload data. If configured as "Off," the received data is discarded. If configured as "UDP," the received data is sent as UDP packets to the configured remote address and ports.

Bit Processor: The central processing unit for TX and RX bit Processing. The main components of this module are:

- **TX Packet Generator:** Generates the packets based on the MAC packet structure.

- RX Packet Validator: Performs frame validation by means of frame check sequence (FCS), which contains an IEEE 32-bit cyclic redundancy code (CRC).

- TX Bit Processing: It is responsible for TX bit processing including data scrambling, TX bit grouping, modulation and data reordering.

- RX Bit Processing: It is responsible for RX bit processing including data reordering, demapping, packing, and descrambling.

- Router 0 & 1: Used for dynamically routing data. Every router has its own routing program which is written from the host depending on the given system configuration. Router 0 is used to route the receive data from MIMO processors to the RX bit processing chain. Router 1 is used to route the transmit data from the TX bit processing chain to the MIMO processors.

MIMO Processors: The central processing units for TX and RX I/Q Processing. Depending on the system configuration, a MIMO processor process all, one half or one fourth of the subcarriers per orthogonal frequency division multiplexing (OFDM) symbol.

- TX I/Q Chain: Includes modules such as Precoding, Stream Combiner, and so on.

- Routers: Used for dynamically routing data. Every router has its own routing program which is written from the host depending on the given system configuration.

- o Router 0 & 1: Used to route receive data from RRH subsystems to the MIMO processor.

- Router 2 & 3: Used to route transmit data from the MIMO processor to the RRH subsystems.

- RX I/Q Chain: Estimates the channel towards the MS from the received data and equalizes the received signals.

RRH Subsystem: The RRHs contain the analog-to-digital converters (ADC) and digital-to-analog converters (DAC). They handle the transformation from time domain to frequency domain and vice versa. Multiple RRHs (two to eight) build a subsystem. A base station can consist of one to eight subsystems.

- RRH Splitter (last RRH in subsystem): Receives the transmit data from the MIMO processors, distributes it to the TX chains of all other RRHs in the subsystem, one after the other, and finally to its own TX chain.

- RRH Combiner (remaining RRHs): Accumulates the received data from its own RX chain, followed by the RX chains of all other RRHs in a subsystem, one after the other, and sends it to the MIMO processors.

- OFDM TX and OFDM RX: Each RRH contains OFDM modulation and OFDM demodulation.

- RF: In the transmit path, it performs DUC, RF impairments correction, and writes the transmit data to the RF. In the receive path, it reads the receive data from the RF, performs DDC and performs RF impairments correction.

Figure 13. Block Diagram of the BS (TX and RX Chain)

#### **Mobile Station**

The following figure shows the block diagram of the MS system in the UL and DL.

Digital Payload Baseband UDP Data **UDP** Read Stream in MAC UE TX **UL TX PHY** Conversion PN Source TDD Switching RF UDP LIDP Data Down Stream MAC UE RX DL RX PHY Handling Write Conversion out Payload Data Host Trigger Source **FPGA**

Figure 14. Block Diagram of the MS (TX and RX Chains)

The components shown in Figure 14 perform the following tasks:

- Host: Configures the FPGA and displays the system status. Interfaces with the MS bitfile.

- **UDP read:** Reads data, provided by an external application, from a UDP socket. The data is used as a payload data in the UL Data field of each slot, which is then encoded and modulated as an UL signal by the UL TX (UL TX PHY).

- PN Source: Generates a pseudo noise (PN) sequence, a sequence of pseudorandom numbers.

- **UDP write:** Writes the payload data that was received and decoded from the DL signal by the DL RX (DL RX PHY) to an UDP socket. The data can then be read by an external application.

- Data Handling: Reads received data from FPGA, checks packets validation, and stores received payload to queues.

- FPGA: Contains the MAC and PHY modules for the UL and the DL.

- MAC TX: A simple MAC implementation which adds a header containing the number of payload bytes. The header is followed by the payload in bytes and the remaining bytes are filled with padding bytes. The 32-bit CRC is then added.

- **MAC RX:** Packets validator and payload extraction.

- UL TX PHY: The physical layer of the UL TX creates the UL signal based on the configured frame structure as digital baseband I/Q data. This includes resource mapping, pilot generation, and OFDM modulation.

- DL RX PHY: The physical layer of the DL RX demodulates the downlink signal. This includes PSS-based synchronization, OFDM demodulation, channel estimation and equalization.

- **Up Conversion:** Performs digital up conversion (from the LTE sampling rate of 30.72 MS/s to 120 MS/s or 200 MS/s, depending on the USRP RIO model), performs RF impairments correction, and writes the resulting TX samples to the RF interface.

- **Down Conversion:** Reads RX samples from the RF interface, performs digital down conversion (from 120 MS/s or 200 MS/s, depending on the USRP RIO model, to the LTE sampling rate of 30.72 MS/s), and performs RF impairments correction.

- Trigger Source: The MS can be synchronized to the BS using the PSS over-the-air or by using an external trigger signal which is provided from the BS.

- TDD Switching: The TDD Switching module is responsible for TX and RX activation based on the frame schedule.

# Running the LabVIEW Host Code

**Caution** Ensure you meet the hardware and software requirements before trying to run the host code.

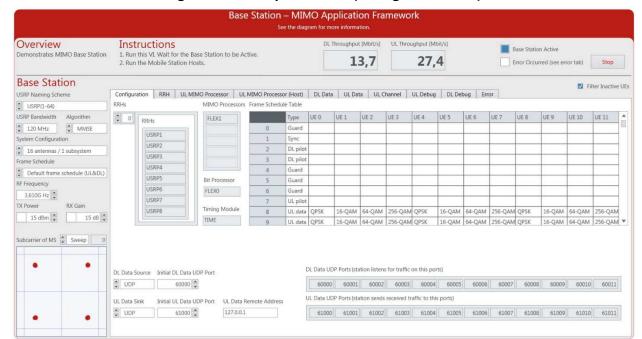

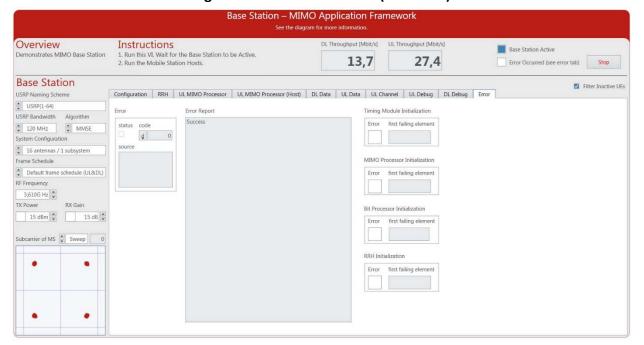

#### On the BS Host Computer

- 1. Launch LabVIEW Communications System Design Suite 2.0 by selecting LabVIEW Communications 2.0 from the Start menu.

- 2. From the Project Templates on the launched **Project** tab, select **Application Frameworks**, then select MIMO Development to launch the project.

- 3. Within that project, open Base Station Host.gvi. The front panel of this VI is shown in Figure 15.

- 4. Set the following configurations in **Base Station Host.gvi**:

- a. Set the USRP Naming Scheme depending on the hardware aliases that you configured using MAX (see Table 9 for details)

- b. Set the USRP Bandwidth Model depending on the hardware model of your USRP RIO devices.

- c. Set the **System Configuration** control to the required configuration

- d. Set the RF Frequency to a frequency supported by your USRP RIO devices.<sup>8</sup>

- e. Set the **TX power** in dBm and **RX gain** in dB or keep the default values.

- 5. Run the **Base Station Host.gvi** by clicking the run button ( ).

- If successful, the Base Station Active indicator lights.

- o If an error is indicated, go to the Error tab to check the error message. Here you will also see if an error occurred during the initialization of the timing module, the MIMO Processors, the Bit processor or the RRHs. The first failing element tells which module could not be initialized correctly. Use MAX to check if the failing module is configured with the correct hardware alias.

<sup>&</sup>lt;sup>8</sup> Consider local laws if you are transmitting over-the-air. The USRP-29xx is not approved or licensed for transmission over-the-air using an antenna.

Figure 15. Front panel of BS (Configuration Tab)

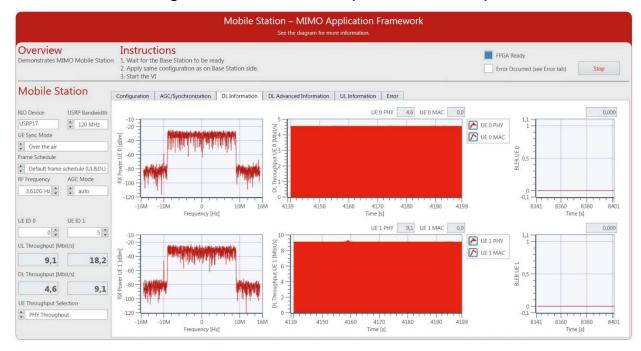

#### On the MS Host Computer

- 1. Launch LabVIEW Communications System Design Suite 2.0 by selecting LabVIEW **Communications 2.0** from the Start menu.

- 2. From the Project Templates on the launched **Project** tab, select **Application Frameworks**, then select MIMO Development to launch the project.

- 3. Within that project, open Mobile Station Host.gvi. The front panel of this VI is shown in Figure 16.

- 4. Set the following configurations in Mobile Station Host.gvi:

- a. Configure the RIO identifier in the RIO Device control. Use MAX to configure the hardware alias of the USRP RIO that you want to use as MS.

- b. Set the USRP Bandwidth Model depending on the hardware model of your USRP RIO

- c. Select the **UE Synchronization Mode** using the **UE Sync Mode** control (over-the-air or using external trigger).

- d. Set the **RF Frequency** according to the base station.<sup>9</sup>

- e. Set the automatic gain control (AGC) mode to auto or manual. If the AGC is configured to manual, set the TX power in dBm and RX gain in dB that are available in the AGC Settings and Status tab.

- f. Set the MS ID of both MSs (UE ID 0 and UE ID 1). Each MS ID has its modulation scheme as shown in Figure 15.

- Run Mobile Station Host.gvi by clicking the run button ( ).

- If successful, the FPGA Ready indicator lights.

<sup>&</sup>lt;sup>9</sup> Consider local laws if you are transmitting over-the-air. The USRP-29xx is not approved or licensed for transmission over-the-air using an antenna.

If an error is indicated, go to the **Error** tab to check the error message. Use MAX to check if the USRP RIO is configured with the correct hardware alias.

Mobile Station – MIMO Application Framework Overview Instructions FPGA Ready onstrates MIMO Mobile Station 1. Wait for the Base Station to be ready 2. Apply same configuration as on Base Station side. Error Occurred (see Error tab) Stop Mobile Station | Configuration | AGC/Synchronization | DL Information | DL Advanced Information | UL Information | Error USRP Bandwidth UE TX Delay [clock cycles] Frame Schedule Table RIO Device USRP17 120 MHz 30 1 UL Sync Mode UL Sync Mode Type UE 0 UE 1 UE 2 UE 3 auto Over the air Frame Schedule DL pilot Default frame schedule (UL&DL) RF Frequency 3,610G Hz 🛊 auto 16-QAM 64-QAM 256-QAM QPSK UL data QPSK 16-QAM 64-QAM 256-QAM QPSK 16-QAM 64-QAM 256-QAN UE ID 1 UL data QPSK 16-QAM 64-QAM 256-QAM QPSK 16-QAM 64-QAM 256-QAM QPSK 16-QAM 64-QAM 256-QAM ▼ 0 × 5 × UL Throughput [Mbit/s] 9,3 18,2 DL Throughput [Mbit/s] UL Data Source Initial UL Data UDP Port UL Data UDP Ports (station listens for traffic on this ports) 4,6 9,1 UDP 50000 W DL Data UDP Ports (station sends received traffic to this ports) UE Throughput Selection DL Data Sink Initial DL Data UDP Port DL Data Remote Address 51000 51001 ▼ UDP 51000 ▼ 127.0.0.1 PHY Throughput

Figure 16. Front Panel of MS (Configuration Tab)

For initial verification that the system is running:

- 1. Select the Frame Schedule Table in the Configuration tab on the Base Station Host.gvi to find the modulation scheme of the selected MSs.

- 2. For UL investigation, select the UL MIMO Processor tab on the Base Station Host.gvi, and verify that the presented RX constellations match the corresponding modulation schemes according to the Frame Schedule Table. When using the default frame schedule UE 0 should have QPSK modulation and UE 1 should have 16 QAM modulation. Furthermore, select the UL Data tab and verify the UL throughput.

- For DL investigation, select the DL Advanced Information tab on the Mobile Station Host.gvi, and verify that the presented RX constellations match the corresponding modulation schemes according to the Frame Schedule Table. Furthermore, select the DL Information tab and verify the DL throughput.

If you want to transmit and receive with more than two MSs (one MS host), you have two options:

- 1. Use different host computers. For example, use one laptop with one USRP RIO connected to it per MS Host.

- 2. Use the same host computer (for example, a PXI chassis) with multiple USRP RIOs connected to it. For running multiple MS Hosts, you have to duplicate Mobile Station Host.gvi.

When using multiple MS hosts, the above configurations should be repeated for each MS host. Please make sure to select the correct RIO Device each time and to choose unique UE IDs. When using the same UE ID twice the BS will not be able to decode the UL because it receives a mixed signal with the same UL pilots and the same UL data scrambling sequence.

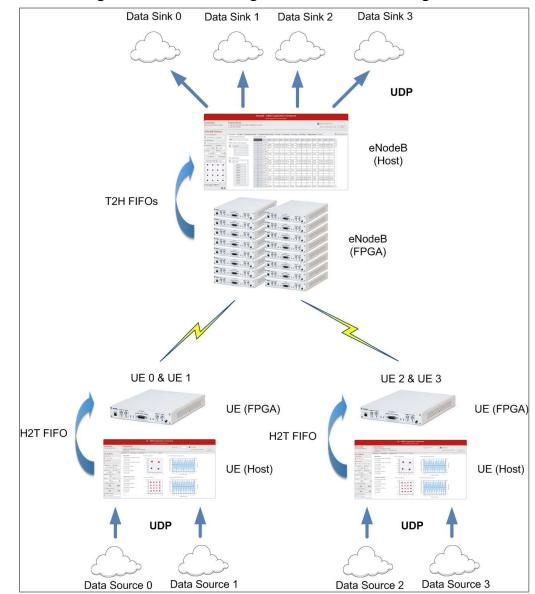

### Running Video Streaming

The MIMO Application Framework implements a basic MAC functionality which allows for packet-based data exchange of user-defined payload data. Figure 17 shows an example where user-defined data is transferred in the uplink. The user-data is received at the MS from a data source in form of UDP packets and send out at the BS to a data sink also in form of UDP packets. Any program capable of transmitting UDP data can serve as a data source. Similarly, any program capable of receiving UDP data can serve as a data sink.

If you use a video streaming application as a data source and a video player as a data sink, the MIMO Application Framework can be used for video streaming. The following section describes video streaming using the VLC media player that is available at www.videolan.org.

#### Start Video Stream at the Transmitter (MS)

The MS host acting as an UL transmitter receives UDP packets from the video streaming application and utilizes the MIMO Application Framework to transmit the data frames.

- 1. Create a new project as described in **Running the LabVIEW Host Code**.

- 2. Open the top-level host VI of the MS, Mobile Station Host.gvi, set the correct RIO identifier in the RIO device parameter, and then set UL Data Source on the Configuration tab to UDP

- 3. Run the LabVIEW host VI by clicking the run button ( ).

- 4. Start cmd.exe and change the directory to the VLC installation directory.

- 5. Start the VLC application as a streaming client with the following command:

```

vlc.exe --repeat "PATH TO VIDEO FILE"

:sout=#std{access=udp{ttl=1}, mux=ts, dst=@:UDP PORT TX}

where PATH TO VIDEO FILE should be replaced with the location of the video that should

be used. The value of UDP PORT TX is 50.000, which is the default UDP Receive Port for MS ID

0. The default UDP receive port can be changed using the Initial UL Data UDP Port control on

the Configuration tab.

```

When using multiple MSs, the value of UDP PORT TX has to be adapted. Each MS Host opens two UDP ports for the two RF chains. See **UL UDP Data Ports** indicator for the used ports.

Figure 17. Data Streaming from MSs to the BS Using UDP

### Start Video Stream of the Receiver (BS)

The BS host acting as a receiver utilizes the MIMO Application Framework to validate the received data frames and pass them via UDP to the video player.

- 1. Create a new project as described in **Running the LabVIEW Host Code section**.

- 2. Open the top-level host VI of the BS, **Base Station Host.gvi**, and then switch to **Configuration** tab and set **UL Data Sink** to **UDP**.

- 3. Run the LabVIEW host VI by clicking the run button (▶).

- 4. Start cmd.exe and change the directory to the VLC installation directory.

- 5. Start the VLC application as a streaming client with the following command: vlc.exe udp://@: $UDP\_PORT\_RX$

The value of UDP PORT RX is 61.000, which is the default UDP Transmit Port. The default value of UDP PORT RX can be changed using the Initial UL Data UDP Port control on Configuration tab. The UDP PORT RX values must be derived as Initial UL Data UDP Port + UE-ID.

# Description of Controls and Indicators

#### Description of Controls and Indicators on the BS Host Front Panel

This section describes all controls, graphs and indicators which are placed on the BS Host front panel.

#### BS Basic Controls and Indicators

Several controls and indicators are placed outside the main tab control of Base Station Host.gvi as shown in Figure 15. The following table lists the corresponding controls. Table 11 lists the corresponding indicators.

**Table 10. BS Basic Configuration - Controls**

| Control              | Description                                                                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USRP Naming Scheme   | Determines the naming scheme of the USRP RIO devices which are loaded with the RRH bitfiles. The enumeration contains the following values:  • CPS(1-8)Port(1-8)Dev1 • PXI(2-5)Slot(2-18)Port1Dev1 |

|                      | • USRP(01-64)                                                                                                                                                                                      |

| USRP Bandwidth       | Determines the bandwidth of the used USRP RIO devices. The enumeration contains the following values:  • 120 or 160 MHz  • 40 MHz                                                                  |

| Algorithm            | Configures the algorithm that is used for precoding. The enumeration contains the following values:  • MMSE • MRC • ZF                                                                             |

| System Configuration | Determines the system configuration. The number of antennas and subsystems is based on this configuration.                                                                                         |

| Frame Schedule       | Determines the frame schedule to use.                                                                                                                                                              |

| RF Frequency        | The center frequency for radio transmission and reception. 10      |

|---------------------|--------------------------------------------------------------------|

| TX Power            | Sets the BS RF transmit power in dBm.                              |

| RX Gain             | Sets the BS RF receive gain in dB.                                 |

| Subcarrier of MS    | Selects the MS ID for the constellation plot below. Set to "sweep" |

|                     | to sweep through the MSs over time. If the Filter Inactive UEs     |

|                     | control is active, the sweeping will include only the active MSs.  |

| Filter Inactive UEs | Filters inactive MSs in several graphs, for example in the         |

|                     | constellation plots.                                               |

Table 11. BS Basic Configurations - Indicators and Graphs

| Indicator                    | Description                                                            |

|------------------------------|------------------------------------------------------------------------|

| TX Clipping                  | Indicates a numeric overflow at the output of DAC. It is located       |

|                              | beside <b>TX Power</b> control                                         |

| RX Clipping                  | Indicates a numeric overflow at the output of ADC. It is located       |

|                              | beside <b>RX Gain</b> control.                                         |

| <b>Equalized Subcarriers</b> | Shows the constellations of the selected MS using <b>Subcarrier of</b> |

|                              | MS control or of all MSs in sweep.                                     |

| <b>UL Throughput</b>         | Numerical display showing the total UL throughput in Mbit/s            |

| [MBit/s]                     |                                                                        |

| DL Throughput                | Numerical display showing the total DL throughput in Mbit/s            |

| [MBit/s]                     |                                                                        |

| <b>Base Station Active</b>   | A Boolean indicator that indicates the BS is ready.                    |

| Error Occurred (see          | A Boolean indicator that lights up if an error occurred.               |

| error tab)                   |                                                                        |

BS Indicators on Configuration Tab

The following two tables list the controls and indicators, respectively, which are placed on the Configuration tab of Base Station Host.gvi as shown in Figure 16.

Table 12. BS Host - Controls on Configuration Tab

| Control        | Description                                                                                     |

|----------------|-------------------------------------------------------------------------------------------------|

| DL Data Source | It has three options:                                                                           |

|                | <ul> <li>Off: Data source is inactive.</li> <li>UDP: To read data from an UDP socket</li> </ul> |

|                | PN Data: Generate data from a PN Source.                                                        |

| UL Data Sink   | If it is set to UDP, received frames are forwarded to the configured                            |

| OL Data SIIIK  | UDP address and port.                                                                           |

$<sup>^{10}</sup>$  Consider local laws if you are transmitting over-the-air. The USRP-29xx is not approved or licensed for transmission over-the-air using an antenna.

| Initial DL Data UDP Port | An offset to start opening UDP ports for UDP packet reception.    |

|--------------------------|-------------------------------------------------------------------|

|                          | The default UDP Transmit Port is 60.000. For each extra MS, the   |

|                          | corresponding UDP port value is 60.000 plus the MS identity.      |

| Initial UL Data UDP Port | An offset to start opening UDP ports for UDP packet transmission. |

|                          | The default UDP Receiver Port is 61.000. For each extra MS, the   |

|                          | corresponding UDP port value is 61.000 plus the MS identity.      |

| UL Data Remote           | The IP address that the UDP packets received from MS are sent to. |

| Address                  |                                                                   |

Table 13. BS Host - Indicators on Configuration Tab

| Indicator            | Description                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RRHs                 | Shows the RIO aliases of active USRP RIO devices per subsystem.                                                                                                                                                                                                                                                                                                                                                      |

| MIMO Processors      | Shows the addresses of active FlexRIO modules for I/Q Processing.                                                                                                                                                                                                                                                                                                                                                    |

| Bit Processor        | Shows the address of active FlexRIO module for bit processing.                                                                                                                                                                                                                                                                                                                                                       |

| Timing Module        | Shows the address of Timing Module RIO card.                                                                                                                                                                                                                                                                                                                                                                         |

| Frame Schedule Table | Shows the OFDM Frame Schedule of all 12 MSs. The OFDM symbol types of each MS frame (140 OFDM Symbols) are presented. The OFDM symbol type could be Guard, Sync, DL pilot, DL data, UL pilot, and UL data. In addition, the modulation schemes of all MSs are presented, which could be QPSK, 16-QAM, 64-QAM, and 256-QAM. The <b>Frame Schedule Table</b> indicator is controlled by <b>Frame Schedule</b> control. |

| DL Data UDP Ports    | Shows the UDP ports to forward traffic to the MSs.                                                                                                                                                                                                                                                                                                                                                                   |

| UL Data UDP Ports    | Shows the UDP ports to forward traffic from the MSs.                                                                                                                                                                                                                                                                                                                                                                 |

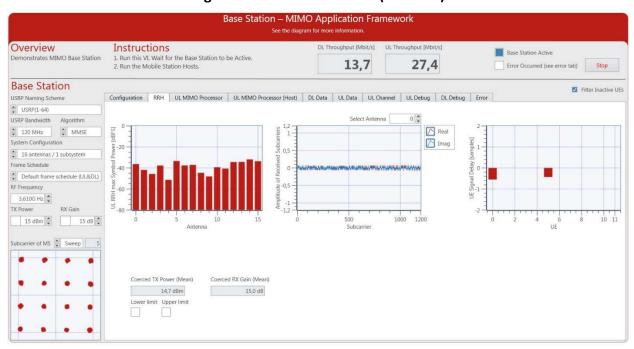

### BS Control and Indicators on RRH Tab

The following table lists the control which is placed on the RRH tab of Base Station Host.gvi as shown in Figure 19. Table 15 lists the corresponding indicators.

Table 14. BS Host - Control on RRH Tab

| Control        | Description                                                   |

|----------------|---------------------------------------------------------------|

| Select Antenna | Determines the antenna for which the received subcarriers are |

|                | shown on this tab.                                            |

Table 15. BS Host - Graphs and Indicators on RRH Tab

| Indicator        | Description                                                                       |

|------------------|-----------------------------------------------------------------------------------|

| Coerced TX Power | Numerical indication shows the actual used analog TX RF power of                  |

| (Mean)           | all antennas as the mean value, which is set by <b>TX Power</b> control in [dBm]. |

| Lower limit      | Boolean indicator shows if the configured <b>TX Power</b> value is                |

|                  | coerced to the allowed range.                                                     |

| Upper limit            | Boolean indicator shows if the configured <b>TX Power</b> value is         |

|------------------------|----------------------------------------------------------------------------|

|                        | coerced to the allowed range.                                              |

| Coerced RX Gain        | Numerical indication shows the actual used analog RX RF gain of            |

| (Mean)                 | all antennas as the mean value, which is set by <b>RX Gain</b> control in  |

|                        | [dB]. The gain value is coerced by the capabilities of the device.         |

| UL RRH max Symbol      | Graphical indication shows the maximum signal strength of a radio          |

| Power [dBFS]           | frame (calculated on OFDM symbol basis) over all antennas.                 |

| Amplitude of Received  | Graphical indication shows the received subcarriers of the                 |

| Subcarriers            | selected antenna. The antenna can be selected using <b>Select</b>          |

|                        | Antenna control that is located on the above side of the figure.           |

| <b>UE Signal Delay</b> | Graphical indication shows the estimated time delay of all MSs in          |

| [Samples]              | LTE samples. This graphical representation can be used to                  |

|                        | calibrate the time delay of each MS manually by using the <b>UE TX</b>     |

|                        | <b>Delay</b> control on the <b>Configuration</b> tab of MS host top-level. |

Figure 18. Front Panel of BS (RRH Tab)

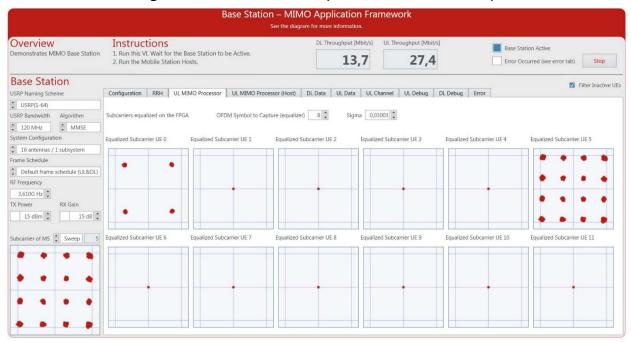

BS Controls and Indicators on UL MIMO Processor Tab

The following table lists the controls that are placed on the **UL MIMO Processor** tab of **Base Station** Host.gvi as shown in Figure 20. Table 17 lists the corresponding indicators.

Table 16. BS Host - Controls on UL MIMO Processor Tab

| Control             | Description                                                         |

|---------------------|---------------------------------------------------------------------|

| OFDM Symbol to      | This control is used to show the constellation of RX I/Q samples of |

| Capture (equalizer) | the selected OFDM symbol number after equalization. The same        |

|                     | OFDM symbol number is selected for all MSs.                         |

| Sigma               | Selects the scaling factor that is used in the modified Gram-       |

|                     | Schmidt QR decomposition (MGS-QRD) algorithm of the MMSE            |

|                     | channel estimator.                                                  |

Table 17. BS Host - Indicators on UL MIMO Processor Tab

| Indicator                      | Description                                                          |

|--------------------------------|----------------------------------------------------------------------|

| <b>Equalized Subcarrier UE</b> | Those 12 graphical representations show the constellation of RX      |

| 0 to Equalized                 | I/Q samples of all MSs. If the number of active MSs is less than 12, |

| Subcarrier UE 11               | it is recommended to filter the inactive MSs using the Filter        |

|                                | Inactive UEs control located on the right side under the Stop        |

|                                | button.                                                              |

Figure 19. Front Panel of BS (UL MIMO Processor Tab)

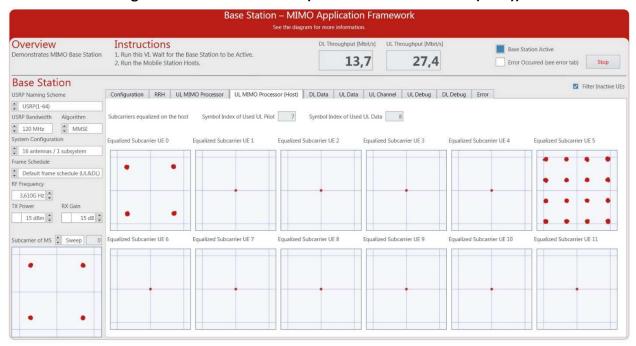

BS Indicators on UL MIMO Processor (Host) Tab

This tab contains the same graphical indicators as on the previous tab as shown on **Figure** 20. However, the channel estimation and equalization is performed on the host and not on the FPGA. The following table shows the corresponding numerical indicators.

Table 18. BS Host - Indicators on UL MIMO Processor (Host) Tab

| Indicator            | Description                                             |

|----------------------|---------------------------------------------------------|

| Symbol index of Used | OFDM symbol index of the UL pilot to derive the channel |

| UL Pilot             | estimation from.                                        |

| Symbol index of Used | OFDM symbol index of the UL data to apply the channel   |

| UL Data              | equalization and display the constellations.            |

Figure 20. Front Panel of BS (UL MIMO Processor Tab (Host))

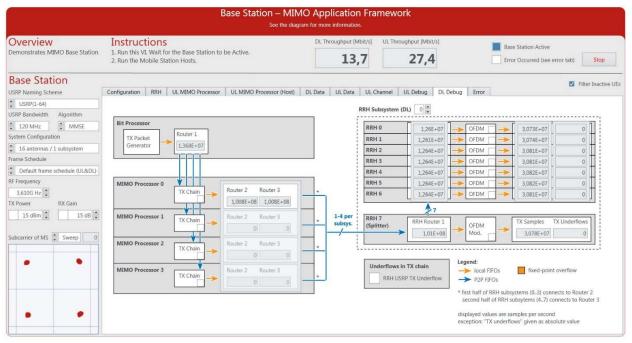

### BS Indicators on DL Data Tab

The following table lists the indicators which are placed on the DL Data tab of Base Station Host.gvi as shown in Figure 21.

Table 19. BS Host - Indicators on DL Data Tab

| Indicator        | Description                                                       |

|------------------|-------------------------------------------------------------------|

| Throughput Graph | Graphical indication showing the DL throughput of all MSs in Mbit |

|                  | per second with respect to time.                                  |

| Throughput Table | Numerical indication of the DL throughput of all MSs in Mbit per  |

|                  | second.                                                           |

Base Station – MIMO Application Framework DL Throughput [Mbit/s] UL Throughput [Mbit/s] Overview Instructions Base Station Active Run this VI. Wait for the Base Station to be Active.

Run the Mobile Station Hosts. ates MIMO Base Station 13,7 27,4 Error Occurred (see error tab) Stop **Base Station** Filter Inactive UEs Configuration RRH UL MIMO Processor UL MIMO Processor (Host) DL Data UL Data UL Channel UL Debug DL Debug Error USRP Naming Scheme USRP Bandwidth DL Throughput per UE [Mbit/s] ME 0 PHY ♣ 120 MHz MMSE 13 -4.6 12 -System Configuration 16 antennas / 1 subsystem 11 -10 -Default frame schedule (UL&DL) 3,610G Hz TX Power 15 dBm 15 dB Subcarrier of MS Sweep

Figure 21. Front Panel of BS (DL Data Tab)

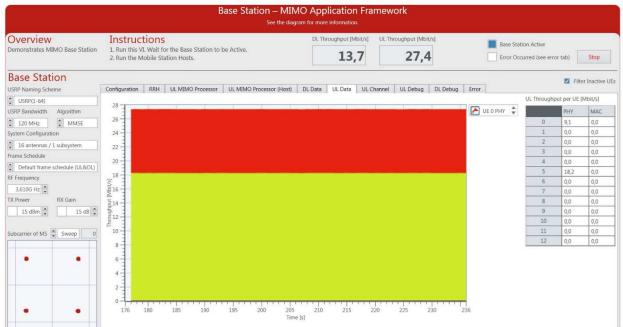

## BS Indicators on UL Data Tab

The following table lists the indicators which are placed on the UL Data tab of Base Station Host.gvi as shown in Figure 22.

Table 20. BS Host - Indicators on UL Data Tab

| Indicator        | Description                                                      |

|------------------|------------------------------------------------------------------|

| Throughput Graph | Graphical indication showing the actual throughput of all MSs in |

|                  | Mbit per second.                                                 |

| Throughput Table | Numerical indication of the throughput of all MSs in Mbit per    |

|                  | second.                                                          |

Figure 22. Front Panel of BS (UL Data Tab)

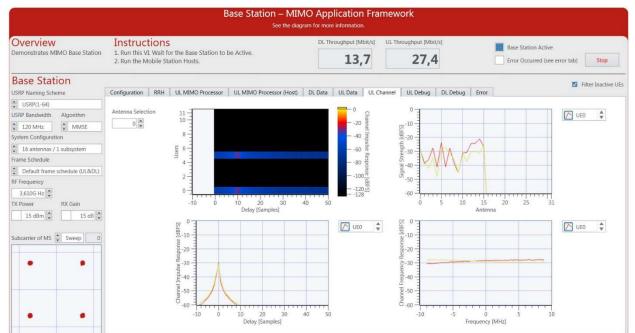

BS Indicators and Controls on UL Channel Tab

Table 21 lists the control which is placed on the **UL Channel** tab of **Base Station Host.gvi** as shown in Figure 23. Table 22 lists the corresponding indicators.

Table 21. BS Host - Control on UL Channel Tab

| Control           | Description                                                       |

|-------------------|-------------------------------------------------------------------|

| Antenna Selection | Numerical control selects the BS antenna to calculate the Channel |

|                   | Frequency Responses, Channel Impulse Responses, and the Users     |

|                   | intensity.                                                        |

Table 22. BS Host - Indicators on UL Channel Tab

| Indicator                | Description                                                              |

|--------------------------|--------------------------------------------------------------------------|

| Signal Strength          | Graphical indication located on top-right side showing the               |

|                          | received signal strength for all MSs versus all antennas of BS.          |

| <b>Channel Frequency</b> | Graphical indication located on bottom-right showing the channel         |

| Response                 | frequency responses of all MSs in dBFS.                                  |

| Channel Impulse          | Graphical indication located on bottom-left showing the channel          |

| Response                 | impulse responses of all MSs. The amplitude of the channel               |

|                          | impulse responses is in dBFS while the time delay is in terms of         |

|                          | LTE samples.                                                             |

| Intensity Graph          | Graphical indication located on top-left side showing the <b>Channel</b> |

|                          | Impulse Response of MSs as an intensity figure.                          |

Figure 23. Front Panel of BS (UL Channel Tab)

### BS Control and Indicators on UL Debug Tab

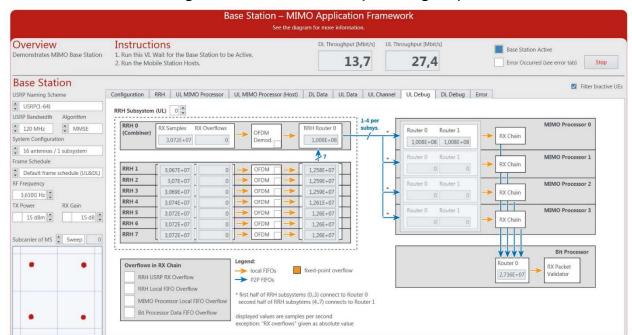

Figure 24 shows the screenshot of the UL Debug tab of Base Station Host.gvi. This tab contains a block diagram of the uplink part of the system overlaid with numeric and Boolean indicators which indicate the number of samples processed per second and fixed-point overflows. The control and indicators are listed in Table 23 and Table 24.

Table 23. BS Host - Control on UL Debug Tab

| Control            | Description                                                 |

|--------------------|-------------------------------------------------------------|

| RRH Subsystem (UL) | Numerical control selects the subsystem number based on the |

|                    | MIMO system configuration. The maximum number of subsystems |

|                    | is 8, hence the control ranges from 0 to 7.                 |

Table 24. BS Host - Indicators on UL Debug Tab

| Indicator          | Description                                                                                                                                                                                     |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| For RRH 0 to RRH 7 |                                                                                                                                                                                                 |

| RX Samples         | Numerical indicator displaying the number of RX samples in the time domain processed per second. Because the LTE sampling frequency is 30.72 MHz, the values should equal $3.072 \times 10^7$ . |

| RX Overflows                             | Numerical indicator that indicates overflows in the FIFO which connects the USRP RX loop (which reads from the ADC and performs digital down-conversion) and the RX I/Q processing loop (which performs OFDM demodulation). Overflows can occur when the samples are not processed fast enough either in the RX I/Q processing chain or on the MIMO Processors. Another possibility is too high traffic on the PCI-Express bus which stalls the P2P streams. The values should be zero if the system is in normal operation. |

|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed-point<br>overflow                  | Boolean indicator that indicates fixed-point overflows in the I/Q processing chain. The TX power levels and RX gains should be configured so that no fixed-point overflows occur.                                                                                                                                                                                                                                                                                                                                            |

| RRH Router 0                             | Number of samples processed per second by RRH Router 0. The number should be $1.26\times10^7$ multiplied by the number of RRHs in the subsystem for the first RRH in a subsystem (RRH Combiner).                                                                                                                                                                                                                                                                                                                             |

| For MIMO Processor 0 to MIMO Processor 3 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Router 0 and                             | Numeric indicators displaying the number of samples processed                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Router 1                                 | by router 0 and router 1 per second. The value should be $1.008 \times 10^8$ .                                                                                                                                                                                                                                                                                                                                                                                                                                               |