#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### **SELL YOUR SURPLUS**

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs.

## **OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

**Bridging the gap** between the manufacturer and your legacy test system.

0

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote

SCXI-1200

# DIO 6533 User Manual

High-Speed Digital I/O Boards for PCI, PXI, CompactPCI, AT, EISA, or PCMCIA Bus Systems

July 1997 Edition Part Number 321464B-01

#### **Internet Support**

support@natinst.com

E-mail: info@natinst.com

FTP Site: ftp.natinst.com

Web Address: http://www.natinst.com

#### **Bulletin Board Support**

BBS United States: (512) 794-5422 BBS United Kingdom: 01635 551422

BBS France: 01 48 65 15 59

**Fax-on-Demand Support**

(512) 418-1111

Telephone Support (U.S.)

Tel: (512) 795-8248 Fax: (512) 794-5678

#### **International Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 5734815, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, United Kingdom 01635 523545

#### **National Instruments Corporate Headquarters**

6504 Bridge Point Parkway Austin, TX 78730-5039 Tel: (512) 794-0100

# **Important Information**

#### Warranty

The PCI-DIO-32HS, PXI-6533, AT-DIO-32HS, and DAQCard-6533 devices are warranted against defects in materials and workmanship for a period of one year from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICIAL PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### Trademarks

$LabVIEW^@, NI-DAQ^@, RTSI^@, ComponentWorks^{TM}, CVI^{TM}, DAQCard^{TM}, MITE^{TM}, SCXI^{TM}, and \ VirtualBench^{TM} are trademarks of National Instruments Corporation.$

Product and company names listed are trademarks or trade names of their respective companies.

#### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

# Table of Contents

| <b>About</b> | This Manual                                  |

|--------------|----------------------------------------------|

|              | Organization of This Manualxi                |

|              | Conventions Used in This Manualxii           |

|              | National Instruments Documentationxii        |

|              | Related Documentationxiii                    |

|              | Customer Communication xiv                   |

| Chapt        | er 1                                         |

| Introd       | luction                                      |

|              | About the DIO 6533 Devices1-1                |

|              | Using PXI with CompactPCI1-2                 |

|              | What You Need to Get Started1-3              |

|              | Software Programming Choices                 |

|              | National Instruments Application Software1-4 |

|              | NI-DAQ Driver Software                       |

|              | Register-Level Programming1-6                |

|              | Optional Equipment                           |

|              | Unpacking1-8                                 |

| Chapt        | er 2                                         |

| Instal       | lation and Configuration                     |

|              | Software Installation                        |

|              | Hardware Installation2-1                     |

|              | Installing the PCI-DIO-32HS2-1               |

|              | Installing the PXI-65332-2                   |

|              | Installing the AT-DIO-32HS2-3                |

|              | Installing the DAQCard-65332-3               |

|              | PCI. PXI. and DAOCard Device Configuration   |

| A       | AT Device Configuration                       | 2-5  |

|---------|-----------------------------------------------|------|

|         | Bus Interface                                 |      |

|         | Plug and Play Mode                            |      |

|         | Switchless Data Acquisition                   |      |

|         | Base I/O Address Selection                    |      |

|         | DMA Channel Selection                         |      |

|         | Interrupt Channel Selection                   | 2-6  |

| Chaptei | r 3                                           |      |

| -       | are Overview                                  |      |

|         | Justrobed I/O                                 | 3_4  |

|         | trobed I/O—Pattern Generation and Handshaking |      |

| Б       | Pattern and Change Detection                  |      |

|         | Pattern-Detection Triggers                    |      |

|         | Change Detection                              |      |

|         | Message Generation                            |      |

|         | Handshaking Protocols                         |      |

|         | 8255 Emulation                                |      |

|         | Level ACK                                     |      |

|         | Leading-Edge Pulse                            |      |

|         | Long Pulse                                    |      |

|         | Trailing-Edge Pulse                           |      |

|         | Burst Mode                                    |      |

|         | Comparing Protocols                           |      |

|         | Starting a Handshaking Transfer               |      |

|         | Controlling the Startup Sequence              |      |

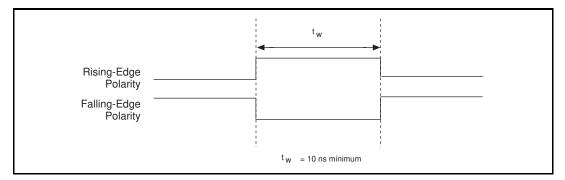

|         | Controlling Line Polarities                   |      |

| T       | ransfer Rates                                 | 3-13 |

| Chaptei | r 4                                           |      |

| •       | Connections                                   |      |

| •       |                                               |      |

| 1/      | O Connector                                   |      |

|         | Signal Descriptions                           |      |

|         | Signal Characteristics                        |      |

|         | Control Signal Summary                        |      |

|         | RTSI Bus Interface                            |      |

|         | Board and RTSI Clocks                         |      |

| ъ       | RTSI Triggers                                 |      |

| D       | Oata Signal Connections                       |      |

|         | Unstrobed I/OStrobed I/O                      |      |

|         | SUVDCU 1/V                                    | 4-I2 |

|       | Timing Connections                        | 4-13 |

|-------|-------------------------------------------|------|

|       | Pull-Up and Pull-Down Connections         | 4-13 |

|       | Power Connections                         | 4-14 |

|       | Field Wiring and Termination              | 4-14 |

| Chan  | iter 5                                    |      |

|       |                                           |      |

| Signa | al Timing                                 |      |

|       | Pattern-Generation Timing                 | 5-1  |

|       | Request Timing                            |      |

|       | Internal Requests                         | 5-2  |

|       | External Requests                         | 5-2  |

|       | Trigger Timing                            | 5-3  |

|       | Handshake Timing                          | 5-4  |

|       | 8255 Emulation                            | 5-4  |

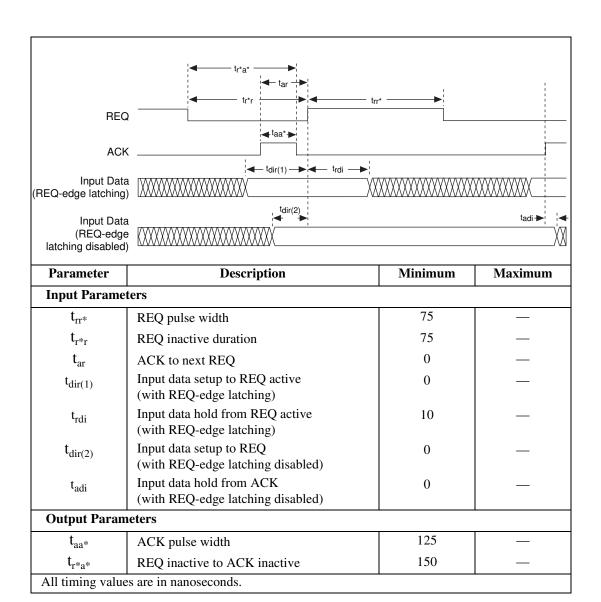

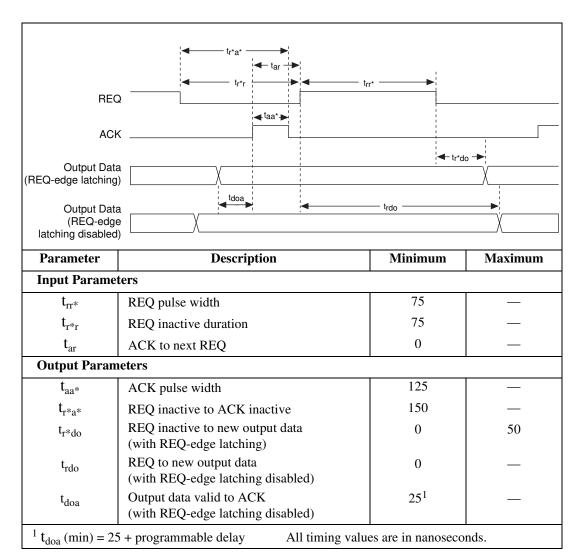

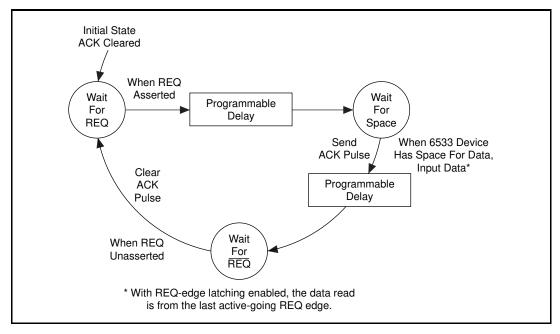

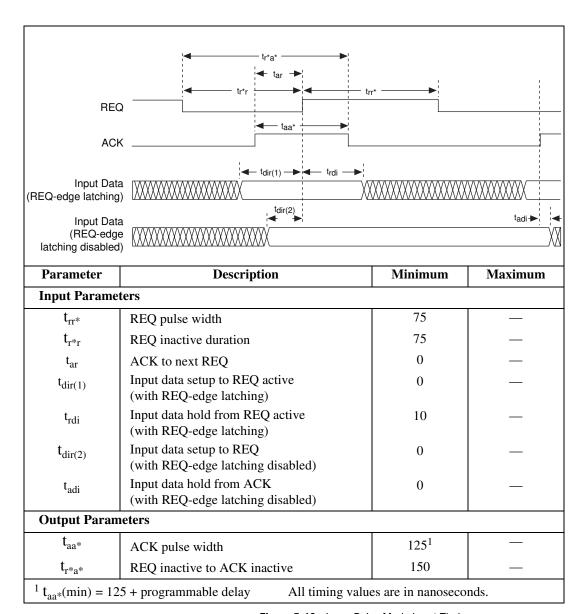

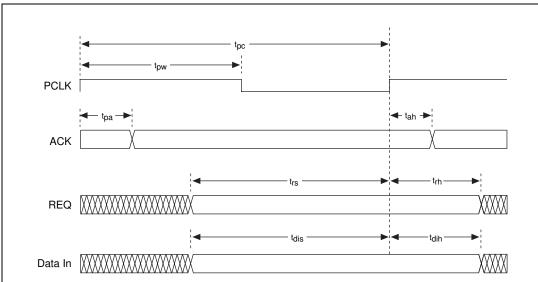

|       | Input                                     | 5-5  |

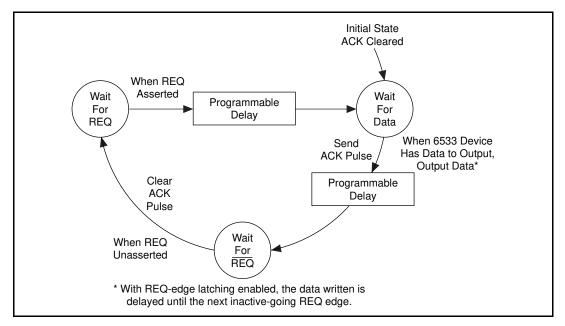

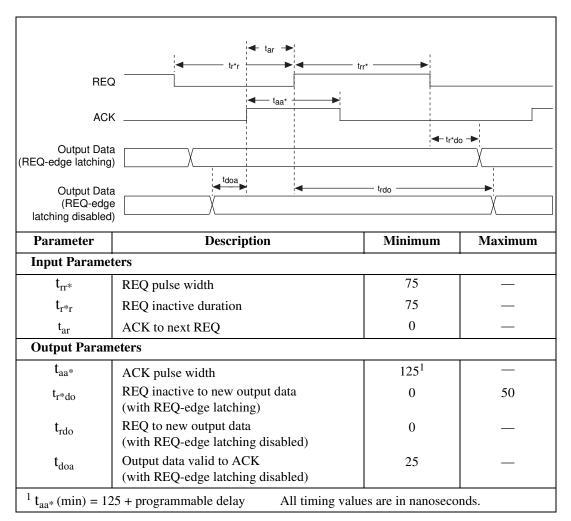

|       | Output                                    | 5-6  |

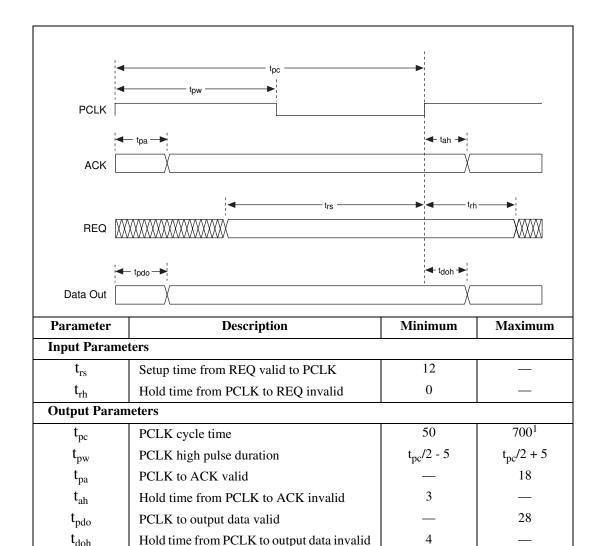

|       | 8255 Emulation Mode Timing Specifications | 5-8  |

|       | Other Asynchronous Modes                  | 5-9  |

|       | Level-ACK Mode                            | 5-9  |

|       | Input                                     | 5-9  |

|       | Output                                    | 5-10 |

|       | Level-ACK Mode Timing Specifications      | 5-11 |

|       | Leading-Edge Mode                         | 5-14 |

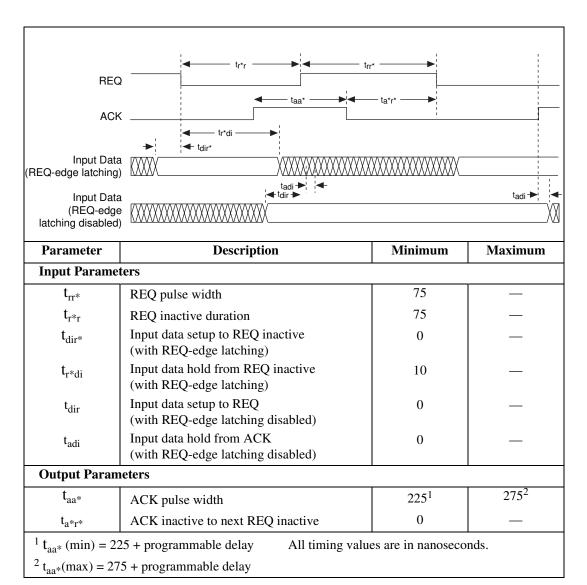

|       | Input                                     | 5-14 |

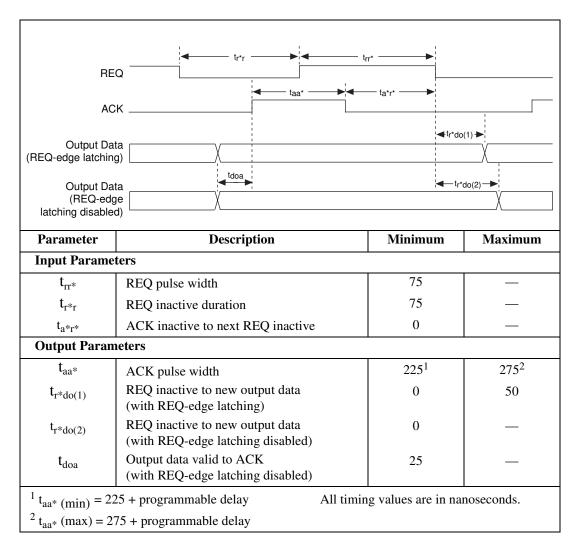

|       | Output                                    |      |

|       | Leading-Edge Mode Timing Specifications   | 5-16 |

|       | Long-Pulse Mode                           |      |

|       | Long-Pulse Mode Timing Specifications     |      |

|       | Trailing-Edge Mode                        |      |

|       | Input                                     |      |

|       | Output                                    |      |

|       | Trailing-Edge Mode Timing Specifications  |      |

|       | Burst Mode                                |      |

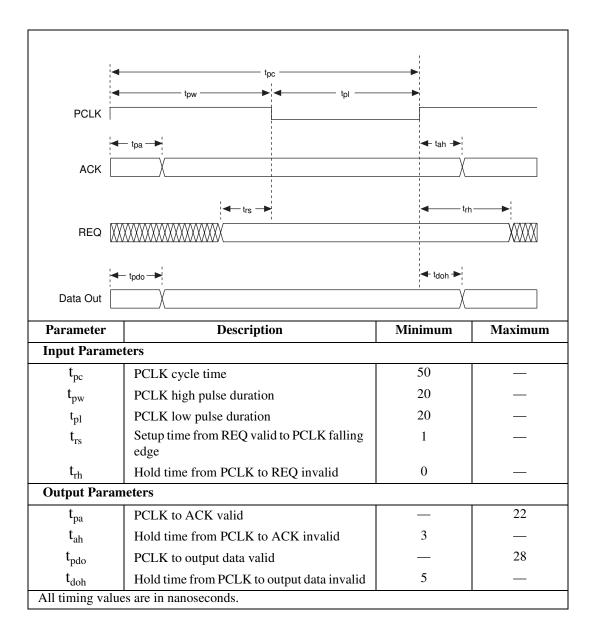

|       | Burst Mode Timing Specifications          | 5-28 |

|       |                                           |      |

# Appendix A Specifications

# Appendix B Optional Adapter Description

# Appendix C Customer Communication

## Glossary

#### Index

#### **Figures**

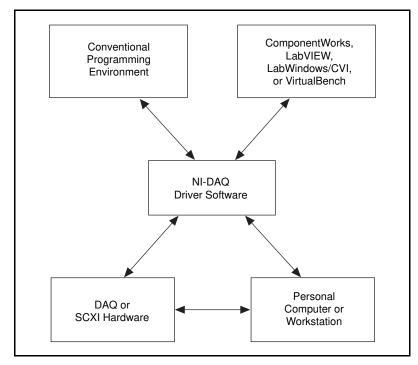

| Figure 1-1.  | The Relationship Between the Programming Environment, NI-DAQ, and Your Hardware | 1-6  |

|--------------|---------------------------------------------------------------------------------|------|

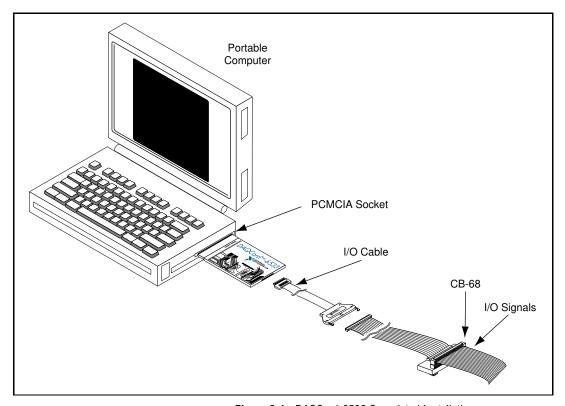

| Figure 2-1.  | DAQCard-6533 Completed Installation                                             | 2-4  |

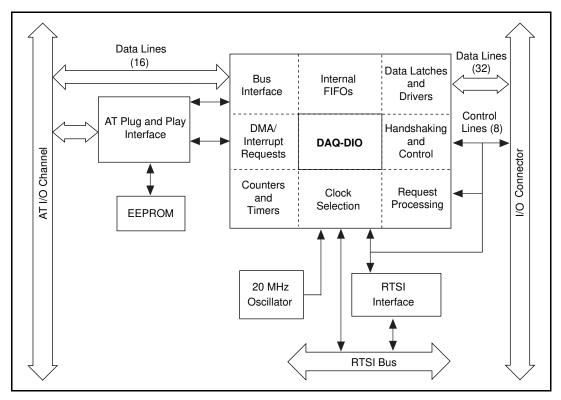

| Figure 3-1.  | PCI-DIO-32HS/PXI-6533 Block Diagram                                             | 3-2  |

| Figure 3-2.  | AT-DIO-32HS Block Diagram                                                       | 3-3  |

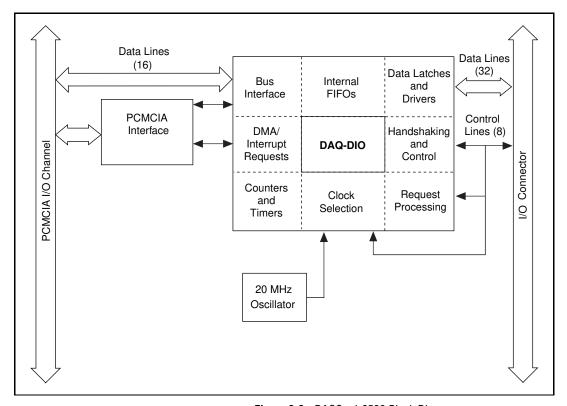

| Figure 3-3.  | DAQCard-6533 Block Diagram                                                      | 3-4  |

| Figure 3-4.  | Pattern Detection Example                                                       | 3-7  |

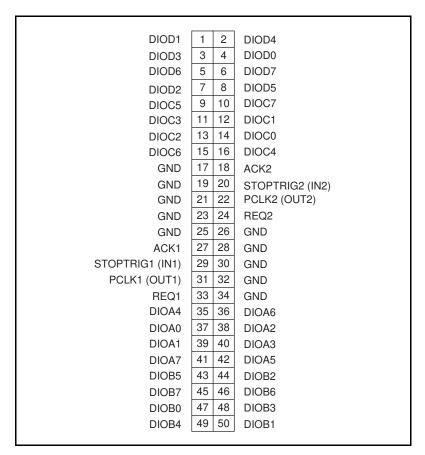

| Figure 4-1.  | 6533 Device I/O Connector Pin Assignments                                       | 4-2  |

| Figure 4-2.  | RTSI Bus Signal Connection                                                      | 4-9  |

| Figure 4-3.  | Example of Data Signal Connections                                              | 4-11 |

| Figure 4-4.  | Transmission Line Terminations                                                  | 4-16 |

| Figure 5-1.  | Pattern-Generation Timing                                                       | 5-1  |

| Figure 5-2.  | Internal Request Timing                                                         | 5-2  |

| Figure 5-3.  | External Request Timing                                                         | 5-3  |

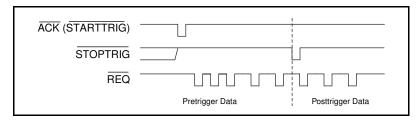

| Figure 5-4.  | Trigger Input Signal Timing                                                     | 5-4  |

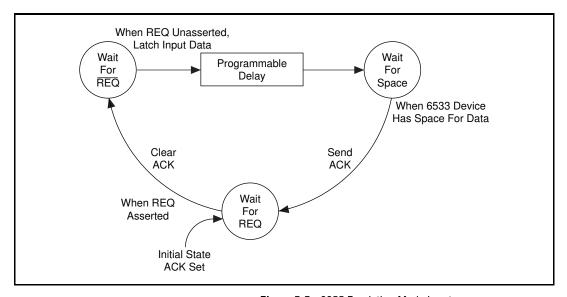

| Figure 5-5.  | 8255 Emulation Mode Input                                                       | 5-6  |

| Figure 5-6.  | 8255 Emulation Mode Output                                                      | 5-7  |

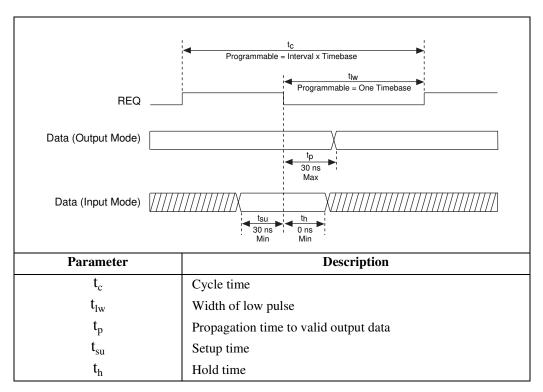

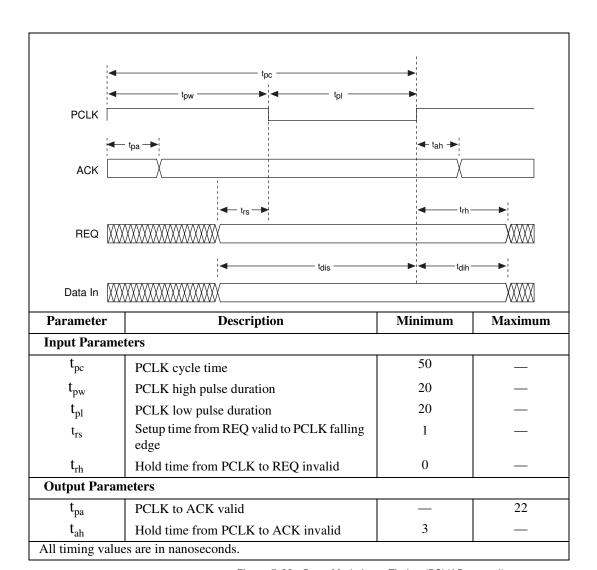

| Figure 5-7.  | 8255 Emulation Timing                                                           | 5-8  |

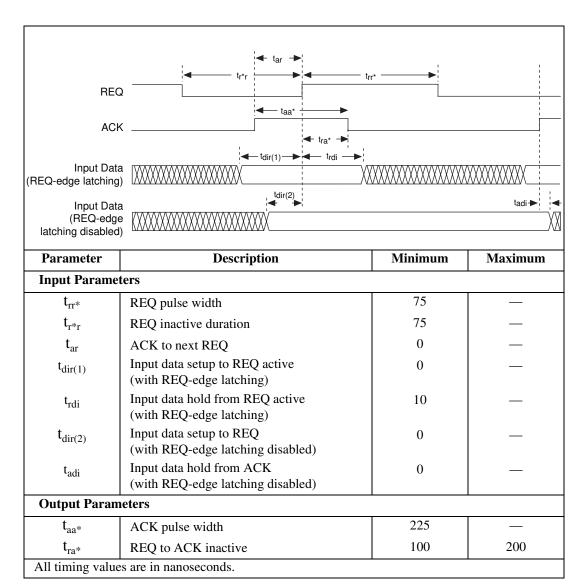

| Figure 5-8.  | Level-ACK Mode Input                                                            | 5-10 |

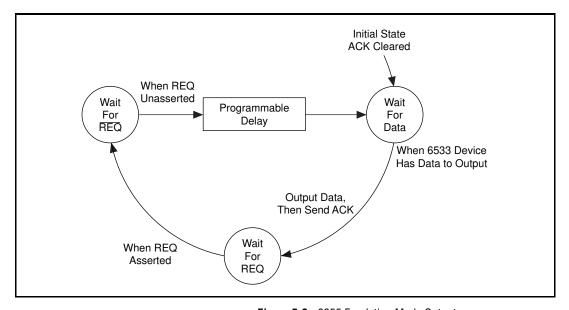

| Figure 5-9.  | Level-ACK Mode Output                                                           | 5-11 |

| Figure 5-10. | Level-ACK Mode Input Timing                                                     | 5-12 |

|              |                                                                                 |      |

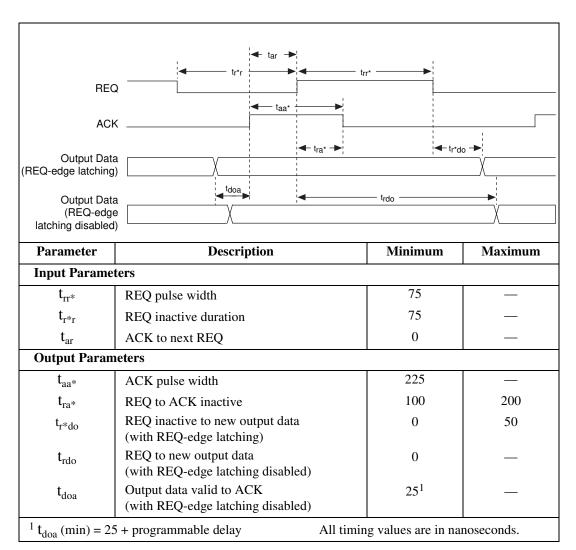

|       | Figure 5-11. | Level-ACK Mode Output Timing             | 5-13 |

|-------|--------------|------------------------------------------|------|

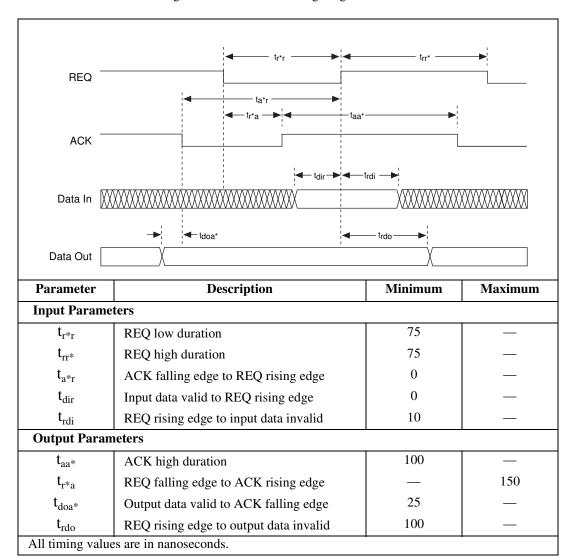

|       | Figure 5-12. | Leading-Edge Mode Input                  | 5-15 |

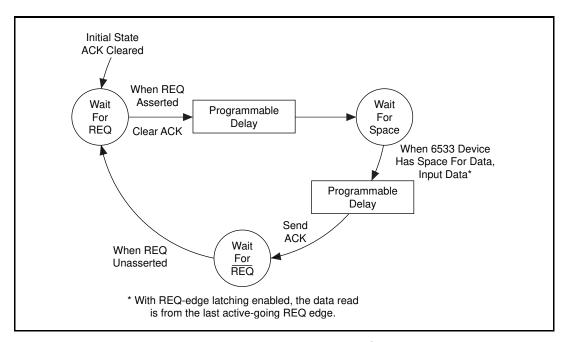

|       | Figure 5-13. | Leading-Edge Mode Output                 | 5-16 |

|       | Figure 5-14. | Leading-Edge Mode Input Timing           | 5-17 |

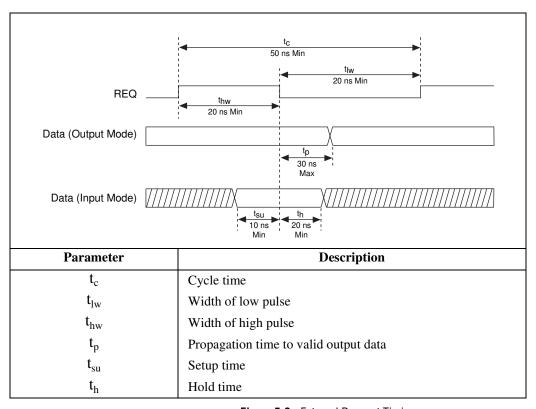

|       | Figure 5-15. | Leading-Edge Mode Output Timing          | 5-18 |

|       | Figure 5-16. | Long-Pulse Mode Input                    |      |

|       | Figure 5-17. | Long-Pulse Mode Output                   | 5-20 |

|       | Figure 5-18. | Long-Pulse Mode Input Timing             | 5-21 |

|       | Figure 5-19. | Long-Pulse Mode Output Timing            | 5-22 |

|       | Figure 5-20. | Trailing-Edge Mode Input                 | 5-24 |

|       | Figure 5-21. | Trailing-Edge Mode Output                | 5-25 |

|       | Figure 5-22. | Trailing-Edge Mode Input Timing          | 5-26 |

|       | Figure 5-23. | Trailing-Edge Mode Output Timing         | 5-27 |

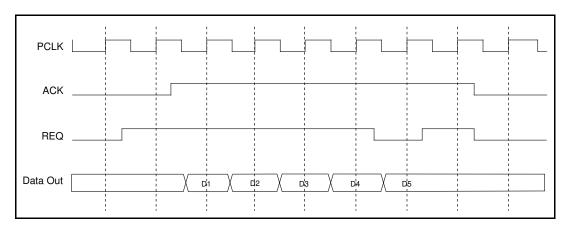

|       | Figure 5-24. | Input Burst Mode Transfer Example        | 5-28 |

|       | Figure 5-25. | Output Burst Mode Transfer Example       | 5-29 |

|       | Figure 5-26. | Burst Mode Output Timing (Default)       | 5-30 |

|       | Figure 5-27. | Burst Mode Input Timing (Default)        | 5-31 |

|       | Figure 5-28. | Burst Mode Output Timing (PCLK Reversed) | 5-32 |

|       | Figure 5-29. | Burst Mode Input Timing (PCLK Reversed)  | 5-33 |

|       | Figure B-1.  | 68-to-50-Pin Adapter Pin Assignments     | B-2  |

| Table |              |                                          |      |

|       | Table 1-1.   | Pins Used by the PXI-6533 Device         | 1-3  |

|       | Table 2-1.   | PC AT I/O Address Map                    |      |

|       | Table 2-2.   | PC AT Interrupt Assignment Map           |      |

|       | Table 2-3.   | PC AT 16-Bit DMA Channel Assignment Map  | 2-9  |

|       | Table 3-1.   | 6533 Handshaking Protocols               | 3-11 |

|       | Table 4-1.   | Signal Descriptions                      | 4-3  |

|       | Table 4-2.   | Control Signal Summary                   | 4-7  |

About This Manual

This manual describes the electrical and mechanical aspects of the DIO 6533 (formerly called *DIO-32HS*) family of devices, and contains information concerning their operation and programming. Unless otherwise noted, text applies to all devices in the DIO 6533 family. The devices named *DIO-32HS* and 6533 are the same in functionality; their primary difference is the bus interface.

The DIO 6533 family includes the following devices:

- PCI-DIO-32HS

- PXI-6533

- AT-DIO-32HS

- DAQCard-6533

# **Organization of This Manual**

The DIO 6533 User Manual is organized as follows:

- Chapter 1, *Introduction*, describes the DIO 6533 (DIO-32HS) devices, lists what you need to get started, describes optional equipment, and explains how to unpack your device.

- Chapter 2, *Installation and Configuration*, explains how to install and configure your DIO 6533 device.

- Chapter 3, *Hardware Overview*, provides an overview of the hardware functions of your DIO 6533 device.

- Chapter 4, *Signal Connections*, describes how to make input and output signal connections to your DIO 6533 device via the device I/O connector and RTSI connector.

- Chapter 5, *Signal Timing*, provides detailed timing specifications for DIO 6533 pattern generation and for the various full, two-way handshaking modes.

- Appendix A, Specifications, lists the specifications for the DIO 6533 devices.

- Appendix B, *Optional Adapter Description*, describes the optional 68-to-50-pin DIO 6533 device adapter.

- Appendix C, Customer Communication, contains forms you can

use to request help from National Instruments or to comment on our

products.

- The Glossary contains an alphabetical list and descriptions of terms used in this manual, including acronyms, abbreviations, definitions, metric prefixes, mnemonics, and symbols.

- The *Index* alphabetically lists topics covered in this manual, including the page where you can find the topic.

## **Conventions Used in This Manual**

The following conventions are used in this manual:

Angle brackets containing numbers separated by an ellipsis represent a

range of values associated with a bit or signal name (for example,

DIOB<3..0>).

♦ The ♦ symbol indicates that the text following it applies only to a

specific DIO 6533 device.

bold italic Bold italic text denotes a note, caution, or warning.

6533 device 6533 device refers to the PCI-DIO-32HS, PXI-6533, AT-DIO-32HS,

and DAQCard-6533 devices, unless otherwise noted.

italic Italic text denotes emphasis, a cross reference, or an introduction to a

key concept.

SCXI SCXI stands for Signal Conditioning eXtensions for Instrumentation

and is a National Instruments product line designed to perform front-end signal conditioning for National Instruments plug-in DAQ

boards.

The *Glossary* lists abbreviations, acronyms, definitions, metric prefixes, mnemonics, symbols, and terms.

## **National Instruments Documentation**

The DIO 6533 User Manual is one piece of the documentation set for your DAQ system. You could have any of several types of documents, depending on the hardware and software in your system. Use the documentation you have as follows:

- Getting Started with SCXI—If you are using SCXI, this is the first

manual you should read. It gives an overview of the SCXI system

and contains the most commonly needed information for the

modules, chassis, and software.

- Your SCXI hardware user manuals—If you are using SCXI, read

these manuals next for detailed information about signal

connections and module configuration. They also explain in greater

detail how the module works and contain application hints.

- Your DAQ hardware documentation—This documentation has

detailed information about the DAQ hardware that plugs into or is

connected to your computer. Use this documentation for hardware

installation and configuration instructions, specification

information about your DAQ hardware, and application hints.

- Software documentation—You may have both application software and NI-DAQ software documentation. National Instruments application software includes LabVIEW, LabWindows®/CVI, ComponentWorks, and VirtualBench. After you set up your hardware system, use either your application software documentation or the NI-DAQ documentation to help you write your application. If you have a large, complicated system, it is worthwhile to look through the software documentation before you configure your hardware.

- Accessory installation guides or manuals—If you are using

accessory products, read the terminal block and cable assembly

installation guides. They explain how to physically connect the

relevant pieces of the system. Consult these guides when you are

making your connections.

- SCXI Chassis Manual—If you are using SCXI, read this manual for maintenance information on the chassis and installation instructions.

#### **Related Documentation**

The following documents contain information that you may find helpful as you read this manual:

- Your computer's technical reference manual

- National Instruments *PXI Specification*, rev. 1.0

- PICMG CompactPCI 2.0 R2.1

# **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix C, *Customer Communication*, at the end of this manual.

Introduction

This chapter describes the DIO 6533 (DIO-32HS) devices, lists what you need to get started, describes optional equipment, and explains how to unpack your device.

#### About the DIO 6533 Devices

Thank you for buying a National Instruments DIO 6533 device. The 6533 devices are 32-bit, parallel digital I/O interfaces for PC-compatible computers, or PXI or CompactPCI chassis. The 6533 devices offer digital data acquisition, digital waveform generation, and high-speed, flexible handshaking.

The PCI-DIO-32HS and PXI-6533 are completely switchless, jumperless DAQ devices for PCI buses and PXI or CompactPCI chassis, respectively. Both contain the National Instruments MITE PCI interface. The MITE offers bus-master operation, PCI burst transfers, and high-speed DMA controllers for continuous, scatter-gather DMA without requiring DMA resources from your computer. See the *Using PXI with CompactPCI* section in this chapter for more information on your PXI-6533 device.

The AT-DIO-32HS is a completely switchless, jumperless DAQ device for AT (16-bit ISA) buses. The AT-DIO-32HS implements the Plug and Play ISA Specification so that your operating system can configure all DMA channels, interrupts, and base I/O addresses. You can easily change device configurations without removing the device from your computer. The AT-DIO-32HS offers dual DMA with channel switching for uninterrupted, high-speed data transfer.

The DAQCard-6533 is a general-purpose digital I/O card for computers equipped with Type II PCMCIA slots. The small size and weight of the DAQCard-6533, coupled with low power consumption, make this card ideal for use in portable computers, making remote digital data acquisition practical. The card requires very little operating power and has a standby mode that uses even less power, thus extending the life of your computer batteries.

Each 6533 device contains the National Instruments DAQ-DIO chip, providing two independent channels of digital input and output, pattern generation, and handshaking. Each channel offers the following functions:

- Selectable data path width (8, 16, or 32 bits)

- 16-sample-deep FIFO buffer

- 16-bit and 32-bit counters for timebase and interval generation, with a maximum timing resolution of 50 ns

- A handshaking controller implementing six flexible timing protocols

- Start and stop trigger detection and digital pattern detection

- 24 mA outputs

- Hysteresis and diode-based line termination on all inputs

With 6533 devices, you can use your computer or chassis as a digital I/O tester, logic analyzer, or system controller for laboratory testing, production testing, and industrial process monitoring and control.

For detailed 6533 device specifications, see Appendix A, *Specifications*.

# Using PXI with CompactPCI

Using PXI-compatible products with standard CompactPCI products is an important feature provided by the *PXI Specification*, rev. 1.0. If you use a PXI compatible plug-in device in a standard CompactPCI chassis, you will be unable to use PXI-specific functions, but you can still use the basic plug-in device functions. For example, the RTSI bus on your PXI-6533 device is available in a PXI chassis, but not in a CompactPCI chassis.

The CompactPCI specification permits vendors to develop sub-buses that coexist with the basic PCI interface on the CompactPCI bus. Compatible operation is not guaranteed between CompactPCI devices with different sub-buses nor between CompactPCI devices with sub-buses and PXI. The standard implementation for CompactPCI does not include these sub-buses. Your PXI-6533 device will work in any standard CompactPCI chassis adhering to the *PICMG CompactPCI 2.0 R2.1* document.

PXI specific features are implemented on the J2 connector of the CompactPCI bus. Table 1-1 lists the J2 pins used by your PXI-6533 device. Your PXI device is compatible with any CompactPCI chassis with a sub-bus that does not drive these lines. Even if the sub-bus is capable of driving these lines, the PXI device is still compatible as long as those pins on the sub-bus are disabled by default and not ever enabled. Damage may result if these lines are driven by the sub-bus.

PXI-6533 **PXI Pin Name** PXI J2 Pin Number Signal **RTSI** PXI Trigger (0..6) B16, A16, A17, A18, B18, Trigger C18, E18 (0..6)Reserved PXI Star D17 RTSI Clock E16 PXI Trigger (7) Reserved LBR (7, 8, 10, 11, A3, C3, E3, A2, B2 12)

Table 1-1. Pins Used by the PXI-6533 Device

## What You Need to Get Started

To set up and use your DIO 6533 device, you will need the following:

One of the following devices:

PCI-DIO-32HS

PXI-6533

AT-DIO-32HS

DAQCard-6533

□ DIO 6533 User Manual

| One of the following software packages and documentation                                     |  |  |

|----------------------------------------------------------------------------------------------|--|--|

| NI-DAQ for PC compatibles                                                                    |  |  |

| LabVIEW for Windows                                                                          |  |  |

| LabWindows/CVI                                                                               |  |  |

| ComponentWorks                                                                               |  |  |

| VirtualBench                                                                                 |  |  |

| Appropriate cable: PSHR68-68M (DAQCard-6533 only) Shielded or ribbon cable (for all devices) |  |  |

| Your computer PXI or CompactPCI chassis and controller                                       |  |  |

# **Software Programming Choices**

There are several options to choose from when programming your National Instruments DAQ hardware. You can use LabVIEW, LabWindows/CVI, ComponentWorks, VirtualBench, or NI-DAQ.

#### **National Instruments Application Software**

LabVIEW features interactive graphics, a state-of-the art user interface, and a powerful graphical programming language. The LabVIEW Data Acquisition VI Library, a series of VIs for using LabVIEW with National Instruments DAQ hardware, is included with LabVIEW. The LabVIEW Data Acquisition VI Library is functionally equivalent to the NI-DAQ software.

LabWindows/CVI features interactive graphics and a state-of-the-art user interface, and uses the ANSI standard C programming language. The LabWindows/CVI Data Acquisition Library, a series of functions for using National Instruments DAQ hardware, is included with LabWindows/CVI. The LabWindows/CVI Data Acquisition Library is functionally equivalent to the NI-DAQ software.

ComponentWorks contains tools for data acquisition and instrument control built on NI-DAQ driver software. ComponentWorks provides a higher-level programming interface for building virtual instruments through standard OLE controls and DLLs. With ComponentWorks, you can use all of the configuration tools, resource management utilities, and interactive control utilities included with NI-DAQ.

Chapter 1

VirtualBench features virtual instruments that combine DAQ products, software, and your computer to create a stand-alone instrument with the added benefit of the processing, display, and storage capabilities of your computer. VirtualBench instruments load and save waveform data to disk in the same forms that can be used in popular spreadsheet programs and word processors.

Using LabVIEW, LabWindows/CVI, ComponentWorks, or VirtualBench software will greatly reduce the development time for your data acquisition and control application.

#### NI-DAQ Driver Software

The NI-DAQ driver software is included at no charge with all National Instruments DAQ hardware. NI-DAQ is not packaged with SCXI or accessory products, except for the SCXI-1200. NI-DAQ has an extensive library of functions that you can call from your application programming environment. These functions include routines for analog input (A/D conversion), buffered data acquisition (high-speed A/D conversion), analog output (D/A conversion), waveform generation (timed D/A conversion), digital I/O, counter/timer operations, SCXI, RTSI, calibration, messaging, and acquiring data to extended memory.

NI-DAQ has both high-level DAQ I/O functions for maximum ease of use and low-level DAQ I/O functions for maximum flexibility and performance. Examples for high-level functions are streaming data to disk or acquiring a certain number of data points. An example of a low-level function is writing directly to registers on the DAQ device. NI-DAQ does not sacrifice performance of National Instruments DAQ devices because it lets multiple devices operate at their peak performance, even simultaneously.

NI-DAQ also internally addresses many of the complex issues between the computer and the DAQ hardware such as programming interrupts and DMA controllers. NI-DAQ maintains a consistent software interface so that you can change platforms with minimal modifications to your code. Whether you are using conventional programming languages or NI-DAQ software, your application uses the NI-DAQ driver software, as illustrated in Figure 1-1.

Figure 1-1. The Relationship Between the Programming Environment, NI-DAQ, and Your Hardware

You can use your 6533 device, together with other AT (16-bit ISA), PCI, PC, EISA, DAQCard, and DAQPad Series DAQ hardware, with NI-DAQ software for PC compatibles. The PCI-DIO-32HS or AT-DIO-32HS requires version 5.0 or later. The PXI-6533 or DAQCard-6533 requires version 5.1 or later.

#### **Register-Level Programming**

The final option for programming any National Instruments DAQ hardware is to write register-level software. Writing register-level programming software can be very time-consuming and inefficient and is not recommended for most users.

Even if you are an experienced register-level programmer, consider using NI-DAQ or National Instruments application software to program your National Instruments DAQ hardware. Using National Instruments application software is as easy and as flexible as register-level programming and can save weeks of development time.

# **Optional Equipment**

National Instruments offers a variety of products to use with your 6533 device, including cables, connector blocks, and other accessories, as follows:

- Cables and cable assemblies, shielded and ribbon

- Connector blocks, shielded and unshielded 50 and 68-pin screw terminals

- Real Time System Integration (RTSI) bus cables

- SCXI modules and accessories for isolating digital signals, controlling relays, and creating isolated analog outputs

- Low channel-count signal conditioning modules, devices, and accessories, including relays and optical isolation

Some cables and accessories require use of the 68 to 50-pin DIO 6533 device adaptor, detailed in Appendix B, *Optional Adapter Description*.

For more specific information about these products, refer to your National Instruments catalogue or web site, or call the office nearest you.

# Unpacking

Your 6533 device is shipped in an antistatic package to prevent electrostatic damage to the device. Electrostatic discharge can damage several components on the device. To avoid such damage in handling the device, take the following precautions:

- Ground yourself via a grounding strap or by holding a grounded object.

- Touch the antistatic package to a metal part of your computer chassis before removing the device from the package.

- Remove the device from the package and inspect the device for loose components or any sign of damage. Notify National Instruments if the device appears damaged in any way. *Do not* install a damaged device into your computer.

- *Never* touch the exposed pins of connectors.

- Store your 6533 device in the antistatic envelope when not in use.

# Installation and Configuration

This chapter explains how to install and configure your DIO 6533 device.

#### **Software Installation**

Install your software before you install your 6533 device. Refer to the appropriate release notes indicated below for specific instructions on the software installation sequence.

If you are using NI-DAQ, refer to your NI-DAQ release notes. Find the installation section for your operating system and follow the instructions given there.

If you are using LabVIEW, LabWindows/CVI, or other National Instruments application software packages, refer to the appropriate release notes. After you have installed your application software, refer to your NI-DAQ release notes and follow the instructions given there for your operating system and application software package.

#### **Hardware Installation**

Following are general installation instructions for each device. Consult your computer or chassis user manual or technical reference manual for specific instructions about installing new devices in your computer or chassis.

#### Installing the PCI-DIO-32HS

You can install a PCI-DIO-32HS in any available 5 V PCI expansion slot in your computer.

- 1. Turn off and unplug your computer.

- 2. Remove the top cover or access port to the expansion slots.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Touch the metal part inside your computer to discharge any static electricity that might be on your clothes or body.

- 5. Insert the PCI-DIO-32HS into a 5 V PCI slot. It may be a tight fit, but *do not force* the device into place.

- 6. Screw the mounting bracket of the PCI-DIO-32HS to the back panel rail of the computer.

- 7. Visually verify the installation.

- 8. Replace the top cover of your computer.

- 9. Plug in and turn on your computer.

#### Installing the PXI-6533

You can install a PXI-6533 in any available 5 V peripheral slot in your PXI or CompactPCI chassis.

The PXI-6533 has connections to several reserved lines on the CompactPCI J2 connector. Before installing a PXI-6533 in a CompactPCI system that uses J2 connector lines for purposes other than PXI, see Using PXI with CompactPCI in Chapter 1, Introduction, of this manual.

- 1. Turn off and unplug your PXI or CompactPCI chassis.

- 2. Choose an unused PXI or CompactPCI 5 V peripheral slot. For maximum performance, install the PXI-6533 in a slot that supports bus arbitration, or bus-master cards. The PXI-6533 contains onboard bus-master DMA logic that can operate only in such a slot. If you choose a slot that does not support bus masters, you will have to disable the onboard DMA controller using your software. PXI-compliant chassis must have bus arbitration for all slots.

- 3. Remove the filler panel for the peripheral slot you have chosen.

- 4. Touch a metal part on your chassis to discharge any static electricity that might be on your clothes or body.

- 5. Insert the PXI-6533 in the selected 5 V slot. Use the injector/ejector handle to fully inject the device into place.

- 6. Screw the front panel of the PXI-6533 to the front panel mounting rails of the PXI or CompactPCI chassis.

- 7. Visually verify the installation.

- 8. Plug in and turn on the PXI or CompactPCI chassis.

#### Installing the AT-DIO-32HS

You can install an AT-DIO-32HS in any available AT (16-bit ISA) or EISA expansion slot in your computer.

- 1. Turn off and unplug your computer.

- 2. Remove the top cover or access port to the expansion slots.

- 3. Remove the expansion slot cover on the back panel of the computer.

- 4. Touch the metal part inside your computer to discharge any static electricity that might be on your clothes or body.

- 5. Insert the AT-DIO-32HS into an AT (16-bit ISA) or EISA slot. It may be a tight fit, but *do not force* the device into place.

- 6. Screw the mounting bracket of the AT-DIO-32HS to the back panel rail of the computer.

- 7. Visually verify the installation.

- 8. Replace the top cover of the computer.

- 9. Plug in and turn on your computer.

#### **Installing the DAQCard-6533**

You can install your DAQCard-6533 in any available Type II PCMCIA slot in your computer. See Figure 2-1 for the completed installation.

- 1. Turn off your computer. If your computer supports hot insertion, you may insert or remove the DAQCard-6533 at any time, whether the computer is powered on or off.

- 2. Remove the PCMCIA slot cover on your computer, if any.

- 3. Insert the PCMCIA bus connector of the DAQCard-6533 into the PCMCIA slot. The card is keyed so that you can insert it only one way.

- 4. Attach the I/O cable. Be very careful not to put strain on the I/O cable when inserting it into and removing it from the DAQCard-6533. When plugging and unplugging the cable, always grasp the cable by the connector. *Never* pull directly on the I/O cable to unplug it from the DAQCard-6533.

Figure 2-1. DAQCard-6533 Completed Installation

Your 6533 device is installed. The device is now ready for software configuration.

# PCI, PXI, and DAQCard Device Configuration

The PCI-DIO-32HS, PXI-6533, and DAQCard-6533 are completely software configurable. The system software automatically allocates all device resources, including base memory address and interrupt level. These devices do not require DMA controller resources from your computer.

# **AT Device Configuration**

The plug and play feature of the AT-DIO-32HS makes it completely software configurable. You can use software to configure the base I/O address, DMA channels, and interrupt levels.

#### **Bus Interface**

The AT-DIO-32HS works in either a Plug and Play mode or a switchless mode. These modes dictate how system resources are determined and assigned to the device.

#### **Plug and Play Mode**

The AT-DIO-32HS is fully compatible with the industry-standard Intel/Microsoft Plug and Play Specification version 1.0a. A Plug and Play system arbitrates and assigns system resources through software, freeing you from manually setting switches and jumpers. These resources include the device base I/O address, DMA channels, and interrupt channels. The AT-DIO-32HS is configured at the factory to request these resources from the Plug and Play Configuration Manager.

The Configuration Manager receives all of the resource requests at startup, compares the available resources to those requested, and assigns the available resources as efficiently as possible to the Plug and Play devices. Application software can query the Configuration Manager to determine the resources assigned to each device without your involvement. The Plug and Play software is installed as a device driver or as an integral component of the computer BIOS.

#### **Switchless Data Acquisition**

You can use your AT-DIO-32HS device in a non-Plug and Play system as a switchless DAQ device. A non-Plug and Play system is a system in which the Configuration Manager has not been installed and which does not contain any non-National Instruments Plug and Play products. Use a configuration utility, such as the NI-PnP or Intel configuration utilities, to enter the base address, DMA, and interrupt selections, and the application software assigns them to the device.

Note:

Avoid resource conflicts with non-National Instruments devices. For example, do not configure two devices to have the same base address.

#### **Base I/O Address Selection**

The AT-DIO-32HS device can be configured to use a base address in the range of 100 to 3E0 hex. The AT-DIO-32HS occupies 16 bytes of address space and must be located on a 16-byte boundary. Therefore, valid addresses include 100, 110, 120, ..., 3D0, 3E0 hex. This selection is software configured and does not require you to manually change any settings on the device.

#### **DMA Channel Selection**

The AT-DIO-32HS can achieve high transfer rates by using up to two 16-bit DMA channels. The AT-DIO-32HS can use only 16-bit DMA channels, which correspond to channels 5, 6, and 7 in an AT (16-bit ISA) computer and channels 0, 1, 2, 3, 5, 6, and 7 in an EISA computer. These selections are all software configured and do not require you to manually change any settings on the device.

#### **Interrupt Channel Selection**

The AT-DIO-32HS increases bus efficiency by using an interrupt channel for event notification. The AT-DIO-32HS can use interrupt channel 3, 4, 5, 6, 7, 9, 10, 11, 12, 14, or 15. This selection is software-configured and does not require you to manually change any settings on the device.

Tables 2-1, 2-2, and 2-3 provide information concerning possible conflicts in base address, DMA channel, and interrupt channel assignment when configuring your AT-DIO-32HS device.

| I/O Address Range (Hex) | Device                                         |

|-------------------------|------------------------------------------------|

| 100 to 1EF              |                                                |

| 1F0 to 1F8              | IBM PC AT Fixed Disk                           |

| 200 to 20F              | PC and PC AT Game Controller, reserved         |

| 210 to 213              | PC-DIO-24 – default                            |

| 218 to 21F              |                                                |

| 220 to 23F              | Previous generation of AT-MIO boards – default |

Table 2-1. PC AT I/O Address Map

Table 2-1. PC AT I/O Address Map (Continued)

Chapter 2

| I/O Address Range (Hex) | Device                                         |

|-------------------------|------------------------------------------------|

| 240 to 25F              | AT-DIO-32F – default                           |

| 260 to 27F              | Lab-PC/PC+ – default                           |

| 278 to 28F              | AT Parallel Printer Port 2 (LPT2)              |

| 279                     | Reserved for Plug and Play operation           |

| 280 to 29F              | WD EtherCard+ – default                        |

| 2A0 to 2BF              | -                                              |

| 2E2 to 2F7              | _                                              |

| 2F8 to 2FF              | PC, AT Serial Port 2 (COM2)                    |

| 300 to 30F              | 3Com EtherLink – default                       |

| 310 to 31F              | -                                              |

| 320 to 32F              | IBM PC/XT Fixed Disk Controller                |

| 330 to 35F              | _                                              |

| 360 to 363              | PC Network (low address)                       |

| 364 to 367              | Reserved                                       |

| 368 to 36B              | PC Network (high address)                      |

| 36C to 36F              | Reserved                                       |

| 370 to 366              | PC, AT Parallel Printer Port 1 (LPT1)          |

| 380 to 38C              | SDLC Communications                            |

| 380 to 389              | Bisynchronous (BSC) Communications (alternate) |

| 390 to 393              | Cluster Adapter 0                              |

| 394 to 39F              | _                                              |

| 3A0 to 3A9              | BSC Communications (primary)                   |

| 3AA to 3AF              | _                                              |

| 3B0 to 3BF              | Monochrome Display/Parallel Printer Adapter 0  |

Table 2-1. PC AT I/O Address Map (Continued)

| I/O Address Range (Hex) | Device                               |

|-------------------------|--------------------------------------|

| 3C0 to 3CF              | Enhanced Graphics Adapter, VGA       |

| 3D0 to 3DF              | Color/Graphics Monitor Adapter, VGA  |

| 3E0 to 3EF              |                                      |

| 3F0 to 3F7              | Diskette Controller                  |

| 3F8 to 3FF              | Serial Port 1 (COM1)                 |

| A79                     | Reserved for Plug and Play operation |

Table 2-2 shows the PC AT interrupt assignments.

Table 2-2. PC AT Interrupt Assignment Map

| IRQ | Device                                                                |

|-----|-----------------------------------------------------------------------|

| 15  | Available                                                             |

| 14  | Fixed Disk Controller                                                 |

| 13  | Coprocessor                                                           |

| 12  | AT-DIO-32F – default                                                  |

| 11  | AT-DIO-32F – default                                                  |

| 10  | AT-MIO-16 – default                                                   |

| 9   | PC Network – default<br>PC Network Alternate – default                |

| 8   | Real-Time Clock                                                       |

| 7   | Parallel Port 1 (LPT1)                                                |

| 6   | Diskette Drive Controller<br>Fixed Disk and Diskette Drive Controller |

| 5   | Parallel Port 2 (LPT2) PC-DIO-24 – default Lab-PC/PC+ – default       |

| 4   | Serial Port 1 (COM1)<br>BSC, BSC Alternate                            |

Table 2-2. PC AT Interrupt Assignment Map (Continued)

| IRQ | Device                                                                                                                                      |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | Serial Port 2 (COM2) BSC, BSC Alternate Cluster (primary) PC Network, PC Network Alternate WD EtherCard+ – default 3Com EtherLink – default |

| 2   | IRQ 8-15 Chain (from interrupt controller 2)                                                                                                |

| 1   | Keyboard Controller Output Buffer Full                                                                                                      |

| 0   | Timer Channel 0 Output                                                                                                                      |

Table 2-3 shows the PC AT 16-bit DMA channel assignments.

Table 2-3. PC AT 16-Bit DMA Channel Assignment Map

| Channel | Device                                             |

|---------|----------------------------------------------------|

| 7       | AT-MIO-16 Series – default                         |

| 6       | AT-MIO-16 Series – default<br>AT-DIO-32F – default |

| 5       | AT-DIO-32F – default                               |

| 4       | Cascade for DMA Controller #1 (channels<03>)       |

Note: EISA computers also have channels < 0..3 > available as 16-bit DMA channels.

This chapter provides an overview of the hardware functions of your DIO 6533 device.

Each 6533 device contains the National Instruments DAQ-DIO chip, a 32-bit general-purpose digital I/O interface. The DAQ-DIO chip enables the 6533 device to perform single-line and single-point input and output, digital data acquisition, digital waveform generation, and high-speed data transfer using a wide range of handshaking protocols.

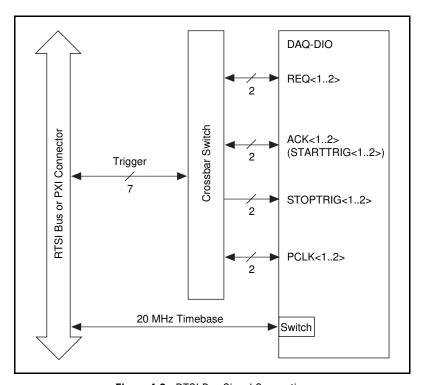

Figures 3-1, 3-2, and 3-3 show the block diagrams for the 6533 devices.

Figure 3-1. PCI-DIO-32HS/PXI-6533 Block Diagram

Figure 3-2. AT-DIO-32HS Block Diagram

Figure 3-3. DAQCard-6533 Block Diagram

## **Unstrobed I/O**

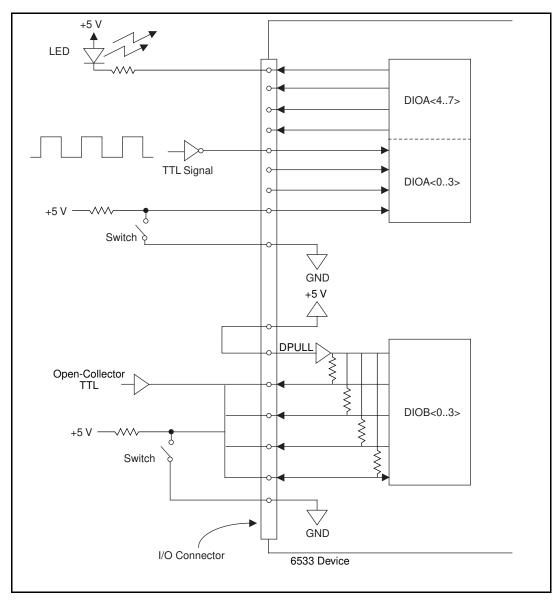

The 6533 devices can perform unstrobed I/O, which is basic digital I/O that employs no handshaking or hardware-controlled timing. You can write or read data directly to or from the four digital I/O ports of the 6533 devices. The I/O ports contain eight lines each and are labeled *A*, *B*, *C*, and *D*. You can configure each line individually for either input or output.

When you perform only unstrobed I/O, the 6533 device does not require its handshaking control and status signals to carry timing information. Therefore, you can use the REQ and STOPTRIG lines as extra data inputs, and the ACK and PCLK lines as extra data outputs.

Chapter 3

# Strobed I/O—Pattern Generation and Handshaking

The 6533 devices can also perform strobed I/O. Strobed I/O is data transfer in which the 6533 hardware regulates timing or performs handshaking functions. The 6533 devices have two handshaking controllers and can perform up to two strobed operations simultaneously. The operations can be input transfers, output transfers, or one of each.

You select the width of each transfer by allocating the digital I/O ports into two groups for the two controllers. For example, by allocating ports A and B to group 1, you can perform a 16-bit strobed transfer using the group 1 controller. Any port that you do not allocate to a group, you can use for unstrobed I/O.

LabVIEW users should note that the LabVIEW documentation uses the term group in another context. LabVIEW groups do not correspond directly to hardware groups.

Each hardware group has its own, independent set of timing control lines—ACK (STARTTRIG), REQ, PCLK, and STOPTRIG—to carry control, status, clocking, and trigger information.

Any external device that the 6533 devices control, monitor, test, or communicate with is referred to as a peripheral device.

Strobed operations fall into two categories—pattern generation and full, or two-way, handshaking transfer.

In pattern generation, data acquisition applications typically require sampling input data at a predetermined frequency. Similarly, waveform-generation applications require driving output data to specific output patterns at a predetermined frequency. You can regulate the frequency by supplying a timing signal to the REQ line; this signal is an external request. The 6533 devices can also generate their own REQ pulses, or internal requests. Each group has a 32-bit counter to regulate the period between transfers.

In pattern generation, you can also supply start and stop triggers to begin and end an operation. You can select either a rising edge or a falling edge as a trigger signal. You can also trigger when the 6533 device detects a specified digital pattern on its data lines.

A variant of pattern generation is *change detection*. In change detection, the 6533 device generates an internal request only when the input data changes. This feature allows you to monitor activity on the input lines efficiently, without capturing multiple copies of the same input pattern. See the *Pattern and Change Detection* section for more information.

In *full*, or *two-way*, *handshaking transfer*, control information passes both to and from the peripheral device. The 6533 device and the peripheral device each provides the other with strobe signals as data becomes available or is acquired. By withholding strobe signals, either the 6533 device or the peripheral device can slow down the transfer, if necessary. Because of this capability, and because fixed rates are not critical, you can run full-handshaking operations at the highest possible speeds.

#### **Pattern and Change Detection**

You can configure the 6533 device to do several types of pattern and change detection. These modes add additional monitoring capabilities to strobed input operation.

#### **Pattern-Detection Triggers**

You can configure the 6533 device to search for a particular pattern in the input data. When the pattern occurs, the 6533 device can:

- Generate a start trigger to begin a digital data acquisition operation

- Generate a stop trigger to end a digital data acquisition operation

To use a start or stop trigger, you must configure the 6533 device for pattern-generation mode. See Chapter 5, *Signal Timing*, for more information on start and stop triggers.

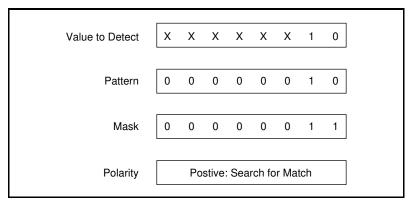

You can specify the following three parameters to the pattern-detection circuit:

- A mask, declaring which data bits you wish to examine

- The pattern value you wish to search for

- Polarity (whether to search for data that matches or that mismatches the specified pattern)

Figure 3-4 shows a pattern-detection example.

Figure 3-4. Pattern Detection Example

The 6533 device provides the following two types of pattern detection timing:

- Compare all data to the input pattern immediately, without waiting for a request pulse (typically used for start triggers).

- Compare acquired data to the pattern, after a request pulse strobes the data in (typically used for stop triggers).

In immediate, unstrobed pattern-detection, the 6533 device detects any occurrence of the pattern, with or without a request strobe. However, the 6533 device filters out very short pattern matches, to ensure that a transient data value that occurs during line switching does not falsely cause a match. A glitch must be present for no more than 20 ns to guarantee rejection. A valid pattern must be present for at least 60 ns to guarantee detection.

In strobed, request-based pattern detection, data is checked as it is strobed in by request pulses. Strobed pattern detection is typically used to generate triggers. You can use strobed pattern detection to generate start triggers too, but only when using an external request source. See the *Request Timing* section in Chapter 5, *Signal Timing*, for the timing of the request pulses that strobe in data.

# **Change Detection**

You can configure the 6533 device to search for transitions on one or more input lines. Whenever a change occurs, the 6533 device generates an internal request, capturing the new input pattern.

The pattern mask, which selects the bits that are significant for pattern detection, also applies to change detection. The 6533 device monitors only the significant bits for changes. After detecting a change, however, the 6533 device captures the values of all bits.

Change detection can increase CPU and bus efficiency for control applications. You can monitor activity on input lines without continuously polling, and without transferring unnecessary data during periods of inactivity.

After a change occurs, the 6533 device takes from 50 to 150 ns to clock in the new data. Therefore, the resolution of change detection is 150 ns. Repeatedly changing data is also subject to the usual pattern generation rate limits; see the *Transfer Rates* section in this chapter for more information.

You can use change detection in conjunction with pattern detection. Within a single group, the change and pattern detection masks are the same; input lines that are significant for pattern detection are also significant for change detection.

# **Message Generation**

Some software environments, such as LabVIEW and LabWindows/CVI, support message generation. Messages allow you to run a user-specified routine when a particular data acquisition event occurs. For example:

- Generate a message upon acquisition of a specified input pattern

- Generate a message every time the 6533 device transfers a data point. You can apply this option to change-detection mode to generate a message every time the input data changes.

These message-generation options can extend your pattern and change-detection capabilities. Some message-generation options require that you select interrupt-driven rather than DMA transfers. See your software documentation for further information about messages.

### **Handshaking Protocols**

When you perform full, two-way handshaking operations, you can select among several timing protocols offered by the 6533 devices. The protocol you select determines the timing of the ACK signals that the 6533 device sends to the peripheral device and of the REQ signals

expected from the peripheral device. One protocol, burst mode, also uses PCLK signals.

The following sections describe the handshaking protocols offered by the 6533 devices. Refer to Table 3-1 for further information on these protocols. For timing details, see Chapter 5, *Signal Timing*.

#### 8255 Emulation

The 8255 emulation protocol emulates the strobed protocols obeyed by the 8255 and 82C55 PPI chips—chips that are used, for example, on the National Instruments PC-DIO-24 and PC-DIO-96/PnP. Because of faster response times, a wider data path, and FIFO buffering, 8255 emulation mode offers much higher data transfer rates than an actual 8255 chip. The 8255 emulation protocol offers the highest peak transfer rate of any protocol except burst mode.

#### Level ACK

After each transfer, the 6533 device asserts the ACK signal to the peripheral device. Holding the ACK line at the asserted level, the 6533 device does not begin a new transfer until a false-to-true transition on the REQ line from the peripheral device occurs.

### **Leading-Edge Pulse**

After each transfer, the 6533 device sends a pulse on the ACK line to the peripheral device. The 6533 device then waits for a false-to-true transition on the REQ line, the start of a REQ pulse, before starting a new transfer. You can specify an ACK pulse delay.

### Long Pulse

Long-pulse mode is the same as leading-edge pulse mode, except that you can specify a minimum pulse width, instead of an ACK pulse delay.

### **Trailing-Edge Pulse**

After each transfer, the 6533 device sends a pulse on the ACK line to the peripheral device. The 6533 device waits for a true-to-false transition on the REQ line, the end of a REQ pulse, before starting a new transfer.

#### **Burst Mode**

The 6533 device sends or receives a clock signal to or from the peripheral device over the PCLK line. Every cycle, the 6533 device asserts an ACK signal if ready for a transfer, and the peripheral device, likewise, asserts a REQ signal if ready for a transfer. Each cycle during which both the 6533 device and the peripheral device indicate that they are ready for a transfer, one data point is latched. Burst mode can transfer data at high rates, particularly over short cables.

# **Comparing Protocols**

Table 3-1 shows similarities and differences among the 6533 device handshaking modes. Asynchronous protocols use only the ACK and REQ signals. Burst mode, a synchronous protocol, uses the ACK, REQ, and PCLK signals. The PCLK line shares a clock signal between the 6533 device and the peripheral device.

Table 3-1 shows peak handshaking rates for typical cable lengths. The peak rates give an upper limit, deriving from the pulse widths and other timing specifications of the handshaking protocol. Your actual maximum rate depends on many factors; see the *Transfer Rates* section in this chapter.

Table 3-1 also shows whether the ACK and REQ signals are active high, active low, or programmable polarity. The table shows whether the leading or trailing edge of a REQ pulse initiates a data transfer. The table also describes the effect on each protocol of setting a programmable delay. See Chapter 5, *Signal Timing*, for timing details.

The table also shows complementary protocols with which the protocol can communicate, assuming that you choose complementary settings for any options the two protocols offer. For example, a 6533 device in 8255 emulation mode can communicate with a 6533 device in long pulse mode, if you select ACK and REQ to be active low.

Table 3-1. 6533 Handshaking Protocols

| Protocol                | Peak Rates (MS/s)<br>at Various Cable<br>Lengths |          | REQ and ACK<br>Polarity | REQ Edge<br>That Requests<br>Transfer | Programmable<br>Delay Location              | Complementary<br>Protocols                                                        |

|-------------------------|--------------------------------------------------|----------|-------------------------|---------------------------------------|---------------------------------------------|-----------------------------------------------------------------------------------|

|                         | 1 m                                              | 2 or 5 m |                         |                                       |                                             |                                                                                   |

| Asynchronous Protocols  |                                                  |          |                         |                                       |                                             |                                                                                   |

| 8255<br>Emulation       | 5                                                | 2.67     | Active-low              | Trailing                              | Between<br>transfers                        | Leading-Edge<br>Pulse                                                             |

| Level<br>ACK            | 3.33                                             | 2.5      | Programmable            | Leading                               | Before ACK<br>and between<br>transfers      | Level ACK                                                                         |

| Leading-<br>Edge Pulse  | 3.33                                             | 2.5      | Programmable            | Leading                               | Before ACK<br>and between<br>transfers      | Leading-Edge<br>Pulse                                                             |

| Long Pulse              | 3.33                                             | 2.5      | Programmable            | Leading                               | For pulse width<br>and between<br>transfers | Long Pulse,<br>8255<br>Emula-tion,<br>PC-DIO-24,<br>PC-DIO-96/PnP,<br>8255, 82C55 |

| Trailing-<br>Edge Pulse | 1.8                                              | 1.5      | Programmable            | Trailing                              | For pulse width<br>and between<br>transfers | Trailing-Edge<br>Pulse                                                            |

| Synchronous Protocol    |                                                  |          |                         |                                       |                                             |                                                                                   |

| Burst                   | 20                                               | 10*      | Programmable            | Neither<br>(level REQ)                | For clock speed                             | Burst                                                                             |

<sup>\*</sup> Although asynchronous modes can adjust automatically to cable length, for synchronous modes, you must select an appropriate speed for your cable at configuration time. Select a delay of at least the following: 0 for a typical cable up to 1 m, 1 (100 ns) for a typical cable up to 5 m, and 2 (200 ns) for a typical cable up to 15 m long.

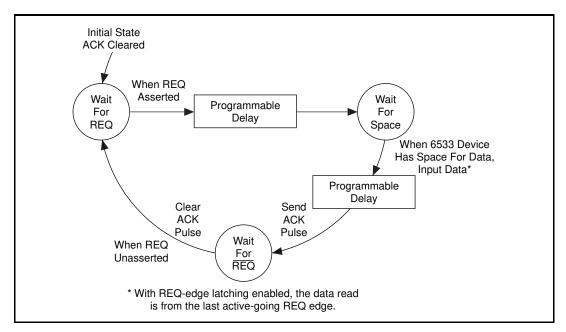

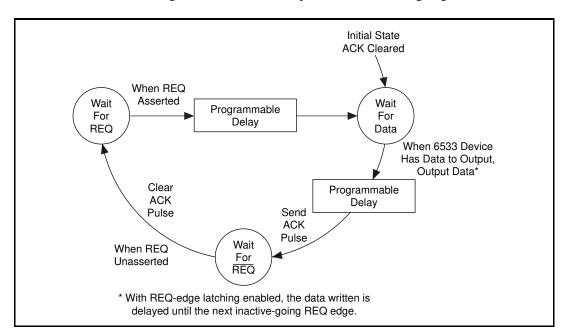

# Starting a Handshaking Transfer

Starting a handshaking transfer correctly protects against incorrect or missed data when the ACK and REQ lines are changing polarity to active-high or active-low. This is particularly important in burst mode because of the potential to miss a lot of data. You can use either of the following two startup methods:

- Control the configuration and startup sequence.

- Select compatible line polarities and default line levels.

# **Controlling the Startup Sequence**

One startup method is to follow a prescribed initialization order in which you can make sure the 6533 device is configured and is driving a valid ACK value before you enable the transfer on the peripheral device. Similarly, you can make sure the peripheral device is configured and is driving a valid REQ value before you enable the transfer on the 6533 device.

To use a prescribed initialization order, perform the following steps:

- 1. Configure the 6533 device for a protocol compatible with your peripheral device.

- 2. Configure and reset the peripheral device, if appropriate.

- 3. Enable the input device (6533 device or peripheral device) and begin a transfer.

- 4. Enable the output device (6533 device or peripheral device) and begin a transfer.

To control the startup order, you must be able to enable and disable the peripheral device, and you must control the order in which the 6533 device and the peripheral device are enabled. The 6533 device extra input and output lines can be helpful for these purposes.

Controlling the startup sequence does not apply to buffered (block) operations. In a buffered operation, the NI-DAQ software configures and enables the 6533 device at the same time, when you start the actual data transfer. For buffered operations, therefore, use the second startup method, controlling the line polarities.

# **Controlling Line Polarities**

If you cannot control the initialization order of the 6533 device and peripheral device, you can still start a transfer reliably if you select the polarities of the ACK and REQ lines so that the power-up, undriven states of the control lines are the inactive states.

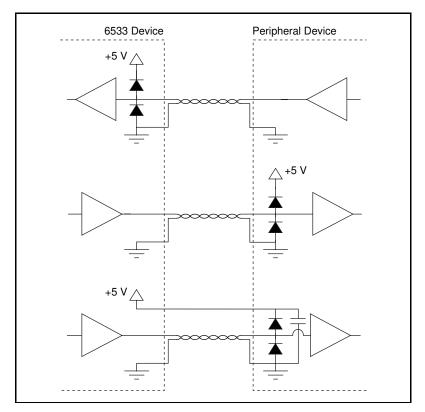

By default, the power-up, undriven state of the REQ and ACK lines is low, due to the onboard  $2.2\,\mathrm{k}\Omega$  pull-down resistors. Therefore, you should either select a protocol with active-high REQ and ACK signals or use the CPULL bias-selection line or your own pull-up resistors to change the power-up, undriven control-line state to high. See Chapter 4, *Signal Connections*, for information on using the CPULL line to control the 6533 device pull-up and pull-down resistors.

# **Transfer Rates**

The maximum average transfer rate that the 6533 device can achieve for two-way handshaking applications is the lower of the following two rates:

- The peak handshaking rate from Table 3-1, which can be lowered by the handshaking speed of your peripheral device

- The average available bus bandwidth, based on your computer system, the number of other devices generating bus cycles, and your application software

The maximum sustainable transfer rate the 6533 device can achieve for pattern generation application is the *minimum* available bus bandwidth, based on your computer system, the number of other devices generating bus cycles, and your application software (this rate is always lower than the peak pattern generation rate).

To achieve the highest possible rates, consider the following information:

- Full, two-way handshaking is faster than pattern generation, because two-way handshaking uses the average rather than the minimum bus bandwidth.

- Burst mode is the fastest handshaking protocol, especially for short cables.

- Your system bus should be as free as possible from unrelated activity. Minimize the number of other I/O cards active in the system.

- Direct-memory access (DMA) transfers are faster than interrupt-driven transfers, especially for pattern generation. By default, the software uses DMA if available.

- ♦ The PCI-DIO-32HS always supports DMA transfers.

- ♦ The PXI-6533 supports DMA if inserted into a peripheral slot that allows bus arbitration (bus mastering). When using a slot that does not allow bus arbitration, use software to select interrupt-driven transfers.

- ♦ The AT-DIO-32HS supports DMA, if system DMA resources are available. If a second DMA channel is available, you can minimize channel reprogramming time by allocating two DMA channels to a single transfer. By allocating two channels, you allow the AT-DIO-32HS software to reprogram one channel while continuing transfers on the other channel. This is particularly important for pattern generation.

- ◆ The DAQCard-6533 cannot be programmed for DMA.

- The average bus bandwidth is higher for the PCI-DIO-32HS or PXI-6533 than for the AT-DIO-32HS, and higher for the AT-DIO-32HS than for the DAQCard-6533.

# **Signal Connections**

This chapter describes how to make input and output signal connections to your DIO 6533 device via the device I/O connector and RTSI connector.

The I/O connector for the 6533 device has 68 pins. You can connect the 6533 device to 68-pin accessories through an SH68-68-D1 shielded cable or an R6868 ribbon cable. Using an optional 68-to-50 pin 6533 device adapter, you can also connect your 6533 device to 50-pin accessories through an NB1 ribbon cable.

# I/O Connector

Figure 4-1 shows the pin assignments for the 68-pin 6533 device I/O connector. Refer to Appendix B, *Optional Adapter Description*, for the pin assignments for the 68-to-50 pin adapter.

Caution:

Connections that exceed any of the maximum input or output ratings on the 6533 may damage your device and your computer. See Appendix A, Specifications, for maximum ratings. This warning includes connecting any power signals to ground and vice versa. National Instruments is NOT liable for any damages resulting from any such signal connections.

Figure 4-1. 6533 Device I/O Connector Pin Assignments

Note:

In Figure 4-1, the \* indicates that you can reverse the pin assignments of the ACK1 (STARTTIG1) and REQ1 pins, or the ACK2 (STARTTIG2) and REQ2 pins, with software. This can be useful when performing two-way ACK/REQ handshaking between two 6533 devices over an SH68-68-D1 or similar cable, because it allows you to connect one device's ACK pin to the

other device's REQ pin. When you exchange two signals on the I/O connector, you also exchange them for RTSI purposes.

# **Signal Descriptions**

Table 4-1 provides signal descriptions. Each signal on the 6533 device is referenced to the GND lines.

Table 4-1. Signal Descriptions

| Pins | Signal Name | Signal Type | Description                                                                                                                                                                                                                           |

|------|-------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2,9  | REQ<12>     | Control     | Group 1 and group 2 request lines—In handshaking mode, a group's REQ line carries handshaking status information from the peripheral.                                                                                                 |

|      |             |             | In pattern generation mode, REQ carries timing pulses either to or from the peripheral to strobe data into or out of the 6533 device. These strobe signals are comparable to the CONVERT* or UPDATE* signals of an analog DAQ device. |

|      |             |             | When not configuring the 6533 device for group operations, you can use the REQ<12> lines as extra, general-purpose input lines (IN<34>).                                                                                              |

| 3, 8 | ACK<12>     | Control     | Group 1 and group 2 acknowledge lines—In handshaking mode, a group's ACK line carries handshaking control information to the peripheral.                                                                                              |

|      |             |             | In pattern generation mode, the ACK lines can function as STARTTRIG<12> lines. You can use rising or falling edges on these lines to start pattern generation operations.                                                             |

|      |             |             | When not configuring the 6533 device for group operations, you can use the ACK<12> lines as extra, general-purpose output lines (OUT<34>).                                                                                            |

Table 4-1. Signal Descriptions (Continued)

| Pins                              | Signal Name      | Signal Type | Description                                                                                                                                                                                                                             |

|-----------------------------------|------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4, 7                              | STOPTRIG<br><12> | Control     | Group 1 and group 2 stop triggers—You can use rising or falling edges on these lines to end pattern generation operations.                                                                                                              |

|                                   |                  |             | When not configuring the 6533 device for group operations, you can use the STOPTRIG<12> lines as extra, general-purpose input lines (IN<12>).                                                                                           |

| 5–6                               | PCLK<12>         | Control     | Group 1 and group 2 peripheral clock lines—In handshaking mode, if you select the burst protocol, these lines carry clock signals to the peripheral (during output operations) or from the peripheral device (during input operations). |