#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs. We Sell For Cash We Get Credit We Receive a Trade-In Deal

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

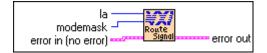

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote CLICK HERE VXIpc-850

# **VXI VI Reference Manual**

January 1998 Edition Part Number 320557D-01

#### **Internet Support**

E-mail: support@natinst.com FTP Site: ftp.natinst.com Web Address: http://www.natinst.com

#### **Bulletin Board Support**

BBS United States: 512 794 5422 BBS United Kingdom: 01635 551422 BBS France: 01 48 65 15 59

Fax-on-Demand Support

512 418 1111

**Telephone Support (USA)** Tel: 512 795 8248 Fax: 512 794 5678

#### **International Offices**

Australia 03 9879 5166, Austria 0662 45 79 90 0, Belgium 02 757 00 20, Brazil 011 288 3336, Canada (Ontario) 905 785 0085, Canada (Québec) 514 694 8521, Denmark 45 76 26 00, Finland 09 725 725 11, France 01 48 14 24 24, Germany 089 741 31 30, Hong Kong 2645 3186, Israel 03 6120092, Italy 02 413091, Japan 03 5472 2970, Korea 02 596 7456, Mexico 5 520 2635, Netherlands 0348 433466, Norway 32 84 84 00, Singapore 2265886, Spain 91 640 0085, Sweden 08 730 49 70, Switzerland 056 200 51 51, Taiwan 02 377 1200, United Kingdom 01635 523545

#### National Instruments Corporate Headquarters

6504 Bridge Point Parkway Austin, Texas 78730-5039 USA Tel: 512 794 0100

© Copyright 1990, 1998 National Instruments Corporation. All rights reserved.

# **Important Information**

#### Warranty

The media on which you receive National Instruments software are warranted against defects in materials and workmanship for a period of 90 days from the date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace equipment that proves to be defective during the warranty period. This warranty includes parts and labor.

The media on which you receive National Instruments software are warranted not to fail to execute programming instructions, due to defects in materials and workmanship, for a period of 90 days from date of shipment, as evidenced by receipts or other documentation. National Instruments will, at its option, repair or replace software media that do not execute programming instructions if National Instruments receives notice of such defects during the warranty period. National Instruments does not warrant that the operation of the software shall be uninterrupted or error free.

A Return Material Authorization (RMA) number must be obtained from the factory and clearly marked on the outside of the package before any equipment will be accepted for warranty work. National Instruments will pay the shipping costs of returning to the owner parts which are covered by warranty.

National Instruments believes that the information in this manual is accurate. The document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, National Instruments reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition. The reader should consult National Instruments if errors are suspected. In no event shall National Instruments be liable for any damages arising out of or related to this document or the information contained in it.

EXCEPT AS SPECIFIED HEREIN, NATIONAL INSTRUMENTS MAKES NO WARRANTIES, EXPRESS OR IMPLIED, AND SPECIFICALLY DISCLAIMS ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR A PARTICULAR PURPOSE. CUSTOMER'S RIGHT TO RECOVER DAMAGES CAUSED BY FAULT OR NEGLIGENCE ON THE PART OF NATIONAL INSTRUMENTS SHALL BE LIMITED TO THE AMOUNT THERETOFORE PAID BY THE CUSTOMER. NATIONAL INSTRUMENTS WILL NOT BE LIABLE FOR DAMAGES RESULTING FROM LOSS OF DATA, PROFITS, USE OF PRODUCTS, OR INCIDENTAL OR CONSEQUENTIAL DAMAGES, EVEN IF ADVISED OF THE POSSIBILITY THEREOF. This limitation of the liability of National Instruments will apply regardless of the form of action, whether in contract or tort, including negligence. Any action against National Instruments must be brought within one year after the cause of action accrues. National Instruments shall not be liable for any delay in performance due to causes beyond its reasonable control. The warranty provided herein does not cover damages, defects, malfunctions, or service failures caused by owner's failure to follow the National Instruments installation, operation, or maintenance instructions; owner's modification of the product; owner's abuse, misuse, or negligent acts; and power failure or surges, fire, flood, accident, actions of third parties, or other events outside reasonable control.

#### Copyright

Under the copyright laws, this publication may not be reproduced or transmitted in any form, electronic or mechanical, including photocopying, recording, storing in an information retrieval system, or translating, in whole or in part, without the prior written consent of National Instruments Corporation.

#### Trademarks

LabVIEW<sup>TM</sup>, natinst.com<sup>TM</sup>, National Instruments<sup>TM</sup>, and NI-VXI<sup>TM</sup> are trademarks of National Instruments Corporation. Product and company names listed are trademarks or trade names of their respective companies.

#### WARNING REGARDING MEDICAL AND CLINICAL USE OF NATIONAL INSTRUMENTS PRODUCTS

National Instruments products are not designed with components and testing intended to ensure a level of reliability suitable for use in treatment and diagnosis of humans. Applications of National Instruments products involving medical or clinical treatment can create a potential for accidental injury caused by product failure, or by errors on the part of the user or application designer. Any use or application of National Instruments products for or involving medical or clinical treatment must be performed by properly trained and qualified medical personnel, and all traditional medical safeguards, equipment, and procedures that are appropriate in the particular situation to prevent serious injury or death should always continue to be used when National Instruments products are being used. National Instruments products are NOT intended to be a substitute for any form of established process, procedure, or equipment used to monitor or safeguard human health and safety in medical or clinical treatment.

#### **About This Manual**

| Organization of This Manual     | ix  |

|---------------------------------|-----|

| Conventions Used in This Manual | х   |

| Related Documentation           | xi  |

| Customer Communication          | xii |

#### Chapter 1 Introduction

| VXIbus Overview                        | 1-1 |

|----------------------------------------|-----|

| VXI Devices                            | 1-1 |

| Register-Based Devices                 | 1-2 |

| Message-Based Devices                  | 1-2 |

| Word Serial Protocol                   |     |

| Commander/Servant Hierarchies          | 1-3 |

| Interrupts and Asynchronous Events     | 1-4 |

| VXI Handler VIs Overview               | 1-4 |

| VXI VI Library Overview                | 1-5 |

| Multiple Mainframe Support             | 1-7 |

| Controllers                            | 1-7 |

| The Extender and Controller Parameters | 1-9 |

| Error Handling Parameter               |     |

| Converting Old Applications            |     |

|                                        |     |

### Chapter 2 System Configuration and VXI Library Initialization VIs

| Locating System Configuration VIs in LabVIEW     | 2-1 |

|--------------------------------------------------|-----|

| Finding Help Online for System Configuration VIs | 2-1 |

| Handling Errors                                  |     |

| System Configuration VI Descriptions             |     |

| System Comgutation vi Descriptions               |     |

### Chapter 3 Word Serial Commander Protocol VIs

| Locating Word Serial Commander VIs in LabVIEW     | 3-1 |

|---------------------------------------------------|-----|

| Finding Help Online for Word Serial Commander VIs | 3-1 |

| Handling Errors                                   | 3-1 |

| Word Serial Commander VI Descriptions             |     |

### Chapter 4 Word Serial Servant Protocol VIs

| Locating Word Serial Servant Protocol VIs in LabVIEW |  |

|------------------------------------------------------|--|

| Finding Help Online for                              |  |

| Word Serial Servant Protocol VIs                     |  |

| Handling Errors                                      |  |

| Word Serial Servant Protocol VI Descriptions         |  |

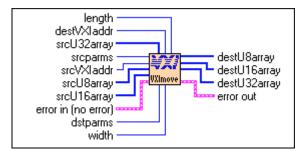

### Chapter 5 Low-Level VXIbus Access VIs

| Multiple Accessors for a Window                     |  |

|-----------------------------------------------------|--|

| Owner Privilege                                     |  |

| Access Only Privilege                               |  |

| Locating Low-Level VXIbus Access VIs in LabVIEW     |  |

| Finding Help Online for Low-Level VXIbus Access VIs |  |

| Handling Errors                                     |  |

| Low-Level VXIbus Access VI Descriptions             |  |

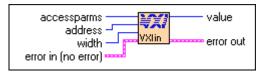

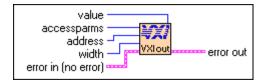

#### Chapter 6 High-Level VXIbus Access VIs

| Locating High-Level VXIbus Access VIs in LabVIEW     | . 6-2 |

|------------------------------------------------------|-------|

| Finding Help Online for High-Level VXIbus Access VIs | . 6-2 |

| Handling Errors                                      | . 6-2 |

| High-Level VXIbus Access VI Descriptions             | . 6-3 |

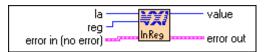

#### Chapter 7 Local Resource Access VIs

| Locating Local Resource Access VIs in LabVIEW     | 7-1 |

|---------------------------------------------------|-----|

| Finding Help Online for Local Resource Access VIs |     |

| Handling Errors                                   | 7-1 |

| Local Resource Access VI Descriptions             | 7-2 |

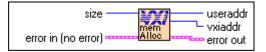

#### Chapter 8 Shared Memory Access VIs

| Locating Shared Memory Access VIs in LabVIEW     | 8-1 |

|--------------------------------------------------|-----|

| Finding Help Online for Shared Memory Access VIs | 8-1 |

| Handling Errors                                  |     |

| Shared Memory Resource VI Descriptions           | 8-2 |

### Chapter 9 VXI Signal VIs

| Locating VXI Signal VIs in LabVIEW     | 9-2 |

|----------------------------------------|-----|

| Finding Help Online for VXI Signal VIs |     |

| Handling Errors                        |     |

| VXI Signal VI Descriptions             | 9-3 |

### Chapter 10 VXI Interrupt VIs

| Locating VXI Interrupt VIs in LabVIEW     |  |

|-------------------------------------------|--|

| Finding Help Online for VXI Interrupt VIs |  |

| Handling Errors                           |  |

| VXI Interrupt VI Descriptions             |  |

|                                           |  |

### Chapter 11 VXI Trigger VIs

| Locating VXI Trigger VIs in LabVIEW     |  |

|-----------------------------------------|--|

| Finding Help Online for VXI Trigger VIs |  |

| Handling Errors                         |  |

| VXI Trigger VI Descriptions             |  |

|                                         |  |

### Chapter 12 System Interrupt Handler VIs

| Locating System Interrupt Handler VIs in LabVIEW     |  |

|------------------------------------------------------|--|

| Finding Help Online for System Interrupt Handler VIs |  |

| Handling Errors                                      |  |

| System Interrupt Handler VI Descriptions             |  |

### Chapter 13 VXIbus Extender VIs

| Locating VXIbus Extender VIs in LabVIEW     | 13-1 |

|---------------------------------------------|------|

| Finding Help Online for VXIbus Extender VIs |      |

| Handling Errors                             |      |

| VXIbus Extender VI Descriptions             |      |

### Appendix A Error Codes

| Error Cluster Descriptions                              | A-2 |

|---------------------------------------------------------|-----|

| System Configuration and VXI Library Initialization VIs | A-2 |

| Word Serial Commander Protocol VIs                      | A-3 |

| Word Serial Servant Protocol VIs                        | A-4 |

| Low-Level VXIbus Access VIs                             | A-4 |

| High-Level VXIbus Access VIs                            | A-5 |

| Local Resource Access VIs                               | A-5 |

| Shared Memory Access VIs                                | A-5 |

| VXI Signal VIs                                          |     |

| VXI Interrupt VIs                                       |     |

| VXI Trigger VIs                                         | A-6 |

| System Interrupt Handler VIs                            | A-7 |

| VXIbus Extender VIs                                     |     |

|                                                         |     |

### Appendix B Customer Communication

### Glossary

### Figures

| 1-5 |

|-----|

|     |

|     |

|     |

| 1-9 |

|     |

The *LabVIEW VXI VI Reference Manual* describes the VXI virtual instruments (VIs) for LabVIEW.

This manual supplements your *LabVIEW User Manual*, and you should be familiar with the material in that manual. You also should be familiar with the operation of LabVIEW, your computer, and your computer's operating system.

## **Organization of This Manual**

The LabVIEW VXI VI Reference Manual is organized as follows:

- Chapter 1, *Introduction*, describes how this manual corresponds with the *NI-VXI Programmer Reference Manual*.

- Chapter 2, *System Configuration and VXI Library Initialization VIs*, describes the System Configuration VIs.

- Chapter 3, *Word Serial Commander Protocol VIs*, describes the VXI Word Serial Commander Protocol VIs.

- Chapter 4, *Word Serial Servant Protocol VIs*, describes the VXI Word Serial Servant Protocol VIs.

- Chapter 5, *Low-Level VXIbus Access VIs*, describes how to use the VIs that give you the fastest access method for directly reading from or writing to any of the VXIbus address spaces.

- Chapter 6, *High-Level VXIbus Access VIs*, describes the VIs with which you have direct access to the VXIbus address spaces.

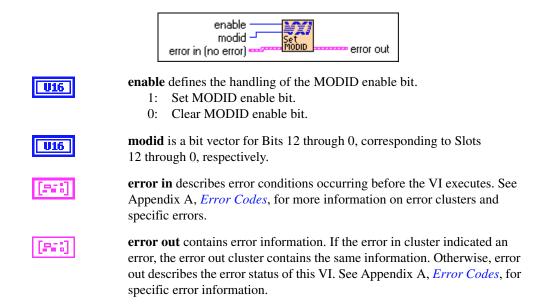

- Chapter 7, *Local Resource Access VIs*, describes the VIs you use to access miscellaneous local resources such as the local CPU VXI register set and Slot 0 MODID operations.

- Chapter 8, *Shared Memory Access VIs*, describes the VIs you use to perform shared memory operations.

- Chapter 9, *VXI Signal VIs*, describes the VIs you use to specify signal routing, manipulate the global signal queue, and wait for a particular VXI signal to be received.

- Chapter 10, *VXI Interrupt VIs*, describes the VIs that control VXI interrupts.

- Chapter 11, *VXI Trigger VIs*, describes the VIs that control triggers, a backplane feature that VXI adds to the VME standard.

- Chapter 12, *System Interrupt Handler VIs*, describes the System Interrupt Handler VIs.

- Chapter 13, VXIbus Extender VIs, describes the VXIbus Extender VIs.

- Appendix A, *Error Codes*, describes the error codes returned by LabVIEW VXI VIs.

- Appendix B, *Customer Communication*, contains forms you can use to request help from National Instruments or to comment on our products and manuals.

- The *Glossary* contains an alphabetical list and description of terms used in this manual, including abbreviations, acronyms, metric prefixes, mnemonics, and symbols.

## **Conventions Used in This Manual**

|                     | The following conventions are used in this manual:                                                                                                                                                                                                                                                                                                                            |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <>                  | Angle brackets enclose the name of a key on the keyboard—for example, <shift>.</shift>                                                                                                                                                                                                                                                                                        |

| -                   | A hyphen between two or more key names enclosed in angle brackets denotes that you should simultaneously press the named keys—for example, <control-alt-delete>.</control-alt-delete>                                                                                                                                                                                         |

| »                   | The » symbol leads you through nested menu items and dialog box options to a final action. The sequence <b>File</b> » <b>Page Setup</b> » <b>Options</b> » <b>Substitute Fonts</b> directs you to pull down the <b>File</b> menu, select the <b>Page Setup</b> item, select <b>Options</b> , and finally select the <b>Substitute Fonts</b> options from the last dialog box. |

|                     | This icon to the left of bold italicized text denotes a note, which alerts you to important information.                                                                                                                                                                                                                                                                      |

| bold                | Bold text denotes the names of menus, menu items, parameters, dialog boxes, dialog box buttons or options, icons, windows, Windows 95 tabs, or LEDs.                                                                                                                                                                                                                          |

| bold italic         | Bold italic text denotes an activity objective, note, caution, or warning.                                                                                                                                                                                                                                                                                                    |

| <control></control> | Key names are lowercase.                                                                                                                                                                                                                                                                                                                                                      |

| italic              | Italic text denotes variables, emphasis, a cross reference, or an introduction to a key concept. This font also denotes text from which you supply the appropriate word or value, as in Windows $3.x$ .                                                                                                                                                                       |

paths Paths in this manual are denoted using backslashes (\) to separate drive names, directories, folders, and files.

Each VXI VI description in this manual displays an icon before the parameter name to designate its data type. These icons are illustrated and defined in the following table.

| Control    | Indicator  | Data Type                      |

|------------|------------|--------------------------------|

| 116        | 116        | Integer                        |

| 132        | 132        | Long Integer                   |

| U16        | <b>U16</b> | Unsigned Integer               |

| <b>U32</b> | <b>U32</b> | Unsigned Long Integer          |

| abc        | <u>abc</u> | String                         |

| TF         | TF         | Boolean                        |

| [032]      | [032]      | Array of Unsigned Long Integer |

| [U16]      | [016]      | Array of Unsigned Integer      |

| [ 80 ]     | [ U8]      | Array of Unsigned Character    |

| [116]      | [116]      | Array of Integer               |

| [TF]       | [TF]       | Array of Boolean               |

|            |            | Cluster                        |

## **Related Documentation**

The following documents contain information that you may find helpful as you read this manual:

- G Programming Reference Manual

- LabVIEW Data Acquisition Basics Manual

- LabVIEW Function and VI Reference Manual

- LabVIEW QuickStart Guide

- LabVIEW *Online Reference*, available by selecting **Help»Online Reference**

- *LabVIEW Online Tutorial* (Windows only), which you launch from the LabVIEW dialog box

- G Programming Quick Reference Card

- LabVIEW Getting Started Card

- LabVIEW Release Notes

- LabVIEW Upgrade Notes

- The getting started or user manuals for the VXI boards you use

- *IEEE Standard for a Versatile Backplane Bus: VMEbus,* ANSI/IEEE Standard 1014-1987

- VXI-1, VXIbus System Specification, Rev. 1.4, VXIbus Consortium

- VXI-6, *VXIbus Mainframe Extender Specification*, Rev. 1.0, VXIbus Consortium

- NI-VXI Programmer Reference Manual

- NI-VXI User Manual

## **Customer Communication**

National Instruments wants to receive your comments on our products and manuals. We are interested in the applications you develop with our products, and we want to help if you have problems with them. To make it easy for you to contact us, this manual contains comment and configuration forms for you to complete. These forms are in Appendix B, *Customer Communication*, at the end of this manual.

# Introduction

This manual is a companion guide to the *NI-VXI Programmer Reference Manual* that came with your VXI hardware. With the exception of the LabVIEW Handler VIs, which correspond to the SetHandler and DefaultHandler functions, every VI in this manual corresponds directly with the function of the same name in the *NI-VXI Programmer Reference Manual*.

National Instruments recommends that you begin by reading the *NI-VXI User Manual*, as well as this chapter, to give you an overview of the VXIbus and NI-VXI. Once you are familiar with this material, you can begin to write your program. Notice that the beginning of each function chapter in this book contains a general overview of the operations of the class of functions in the chapter, as well as a brief description of each function. You should become familiar with the entire class of functions you are using, so that you know which ones are necessary to perform your tasks most efficiently.

Refer to the README.TXT file in your NI-VXI directory to obtain the latest information about your software, as well as platform specific information regarding your hardware.

### **VXIbus Overview**

This section introduces some of the concepts from the VXIbus specification.

#### **VXI** Devices

A VXI device has a unique logical address, which you use to find or access the device in the VXI system. This logical address can be compared to a GPIB device address. Because VXI uses an 8-bit logical address, you can have up to 256 VXI devices in a VXI system.

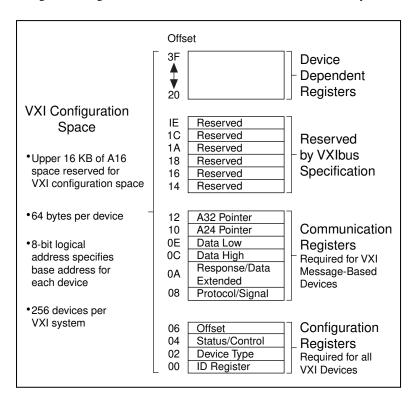

Each VXI device must have a specific set of registers, called *configuration registers*. These registers are located in the upper 16 KB of the 64-KB A16 VXI address space, as shown in Figure 1-1, *VXI Configuration Registers*.

The logical address of a VXI device determines the location of the configuration registers of the device in the 16-KB area reserved by VXI.

Figure 1-1. VXI Configuration Registers

#### **Register-Based Devices**

VXI configuration registers, which are required for all VXI devices, help the system identify each VXI device, its type, model and manufacturer, address space, and memory requirements. A VXIbus device with only this minimum level of capability is called a *Register-Based device*. With this common set of configuration registers, the centralized Resource Manager (RM), which is essentially a software module, can perform automatic system and memory configuration when the system is initialized.

#### **Message-Based Devices**

In addition to Register-Based devices, the VXIbus specification also defines *Message-Based devices*, which must have *communication registers* in addition to the configuration registers. All Message-Based VXIbus

devices, regardless of the manufacturer, can communicate at a minimum level using the VXI-specified Word Serial Protocol. At this minimum level, you can establish higher-performance communication channels, such as shared-memory channels to take advantage of the VXIbus bandwidth capabilities.

#### **Word Serial Protocol**

The VXIbus Word Serial Protocol is a standardized message-passing protocol. This protocol functions much like the IEEE 488 protocol, which transfers data messages to and from devices one byte (or word) at a time. Thus, VXI Message-Based devices communicate in a fashion very similar to IEEE 488 instruments. In general, Message-Based devices typically contain some level of local intelligence that uses or requires a high level of communication.

All VXI Message-Based devices must use Word Serial Protocol and communicate in a standard way. Use the Word Serial Commander VIs to communicate with message-based devices.

In this manual, italics also are used to denote Word Serial commands and queries.

#### **Commander/Servant Hierarchies**

The VXIbus specification defines a Commander/Servant communication protocol so that you can construct hierarchical systems using conceptual layers of VXI devices. This structure can be compared to an inverted tree. A *Commander* is any device in the hierarchy with one or more associated lower level devices, or Servants. A *Servant* is any device in the subtree of a Commander. A device can be both a Commander and a Servant in a multiple-level hierarchy.

A Commander has exclusive control of the communication registers of its immediate Servants (one or more). Any VXI module has only one Commander. Commanders communicate with Servants through the communication registers of the Servants using the Word Serial Protocol. Servants communicate with their Commander, responding to the Word Serial commands and queries from their Commander through the Word Serial Protocol. Servants can also communicate asynchronous status and events to their Commander through hardware interrupts, or by writing specific signals directly to the Signal register of their Commander.

Although the Word Serial Protocol is reserved for Commander/Servant communications, two VXI devices can establish peer-to-peer

communication through a specified shared-memory protocol or by writing specific messages directly to the Signal register of the device.

#### Interrupts and Asynchronous Events

Servants can communicate asynchronous status and events to their Commander through hardware interrupts or by writing specific messages (signals) directly to the hardware Signal register of their Commander. Devices that are not bus masters always transmit such information through interrupts, whereas devices that have bus master capability either can use interrupts or send signals. Some devices can receive only signals, but others might be only interrupt handlers.

The VXIbus specification defines Word Serial commands so that a Commander can understand the capabilities of its Servants and configure them to generate interrupts or signals in a particular way. For example, a Commander can instruct its Servants to use a particular interrupt line, send signals rather than generate interrupts, or configure the reporting of only certain status or error conditions.

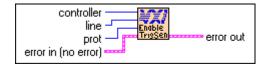

## **VXI Handler VIs Overview**

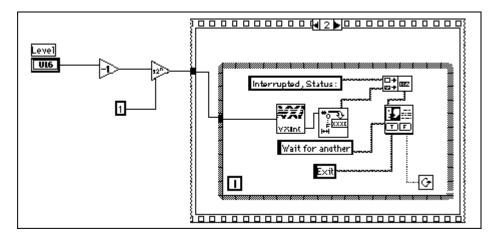

A VXI handler is a user routine that is executed when some event occurs in the VXI interface. For example, you can set a VXI interrupt handler to execute when an interrupt is asserted.

You can use VXI VIs to create a handler as part of your LabVIEW diagram. The handler can use any LabVIEW VI, including other VXI VIs. The VIs you use to create these handlers are called the Handler VIs.

The Handler VIs are analogous to the SetHandler and DefaultHandler calls in the *NI-VXI Programmer Reference Manual*. The inputs to the Handler VIs are the same as the parameters to the SetHandler functions. The outputs to the Handler VIs are the same as the parameters to the DefaultHandler functions.

The Handler VIs are implemented using LabVIEW occurrences. Because an occurrence is a *one-shot* event (the dependent VIs are executed only once), you must put the Handler VI and your handler in a while loop structure.

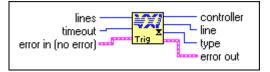

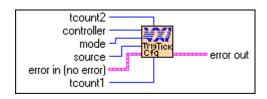

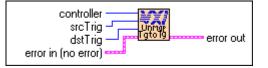

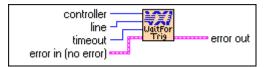

Figure 1-2, *Example of an Interrupt Handler*, shows an example of a LabVIEW interrupt handler, which displays the dialog box whenever an

interrupt of a certain level is asserted. The VXI VIs store the pending interrupts so that the handler executes once for each handler.

Figure 1-2. Example of an Interrupt Handler

Passing the value 3 to a Set Handler VI tells the VXI VI library to begin queueing occurrences for later handling by a Handler VI.

```

🇊 Note

```

Even on platforms where VXI user handlers normally are executed at interrupt time (such as Macintosh and Windows), the LabVIEW user handler diagram is not executed at interrupt time.

## **VXI VI Library Overview**

The *NI-VXI Programmer Reference Manual* gives explanations of the NI-VXI functions. The material found in that manual applies equally to the NI-VXI LabVIEW VXI VIs, and you can use it as a reference in conjunction with this document. The VIs are divided into the following groups:

- System Configuration VIs initialize the NI-VXI interface at the lowest level. In addition, the System Configuration VIs can retrieve or modify device configuration information.

- Word Serial Commander Protocol VIs are used by Word Serial Commanders to communicate with a Message-Based Servant device using the Word Serial, Longword Serial, or Extended Longword Serial protocols. Word Serial is the minimal mode of communication between VXI Message-Based devices. These VIs can perform command/query sending and buffer reads/writes.

- *Word Serial Servant Protocol VIs* give Message-Based Servant devices all of the necessary capabilities to communicate with the Message-Based Commander of the local CPU (the device on which the NI-VXI interface resides) using the Word Serial, Longword Serial, or Extended Longword Serial protocols. These capabilities include command/query handling and buffer read/writes.

- *Low-Level VXIbus Access VIs* offer the fastest access method for directly reading from or writing to any of the VXIbus address spaces. Use them when execution speed is critical.

- *High-Level VXIbus Access VIs* are similar to the Low-Level VXIbus Access VIs, but these VIs give you direct access to the VXIbus address spaces. You can use these VIs to read, write, and move blocks of data between any of the VXIbus address spaces. You can specify any VXIbus privilege mode or byte order. The VIs trap and report Bus Errors. The High-Level VXIbus Access VIs are easy-to-use. You should use them when execution speed is not crucial.

- Local Resource Access VIs offer access to miscellaneous local resources such as the VXI register set of local CPU, Slot 0 MODID operations (when the local device is configured for Slot 0 operation), and the VXI shared RAM of the local CPU. These VIs are useful for shared memory type communication, for non-Resource Manager operation (when the local CPU is not the Resource Manager), and for debugging purposes.

- Shared Memory Access VIs offer access to local CPU-shared RAM.

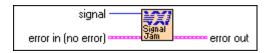

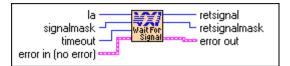

- *VXI Signal VIs* are used by VXI bus masters to interrupt another device. The value written to a Signal register of a device has the same format as the status/ID value returned during a VXI interrupt acknowledge cycle. You can route VXI signals to the default interrupt service routine or place them into a global signal queue. VXI signal VIs can specify the signal routing, manipulate the global signal queue, and wait for a particular signal value (or set of values) to be received.

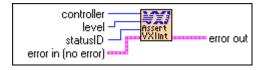

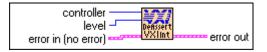

- *VXI Interrupt VIs* let you process individual VXI interrupt status/IDs as VME status/IDs, VXI status/IDs, or VXI signals. By default, status/IDs are processed as VXI signals. VXI interrupt VIs can specify the status/ID processing method and can assert specified VXI interrupt lines with a specified status/ID value.

- *VXI Trigger VIs* are a standard interface to source and accept any of the VXIbus TTL or ECL trigger lines. These VIs can also detect acknowledgements from the accepting device and send the acknowledgements back to the sourcing device. You can use these VIs as configuration tools for signal conditioning and routing trigger lines,

and for configuring the settings of the trigger inputs and outputs as well as the National Instruments Trigger Interface Chip (TIC) counter and tick timers. VXI trigger VIs support all VXI-defined trigger protocols; the actual capabilities depend on the specific hardware platform.

- *System Interrupt Handler VIs* let you handle the system interrupt conditions. These conditions include Sysfail, ACfail, Sysreset, BusError, and SoftReset interrupts.

- *VXIbus Extender VIs* allow you to dynamically reconfigure multiple-mainframe transparent mapping of the VXI interrupt lines, TTL triggers, ECL triggers, and utility bus signals. The National Instruments Resource Manager configures the mainframe extenders with settings based on user-modifiable configuration files.

LabVIEW 5.0 includes new VXI VI examples. See these examples in \labview\examples\instr\smplvxi.llb

## **Multiple Mainframe Support**

The NI-VXI functions described in this manual support multiple mainframes both in external CPU configurations and embedded CPU configurations. The Startup Resource Manager supports one or more mainframe extenders and configures a single- or multiple-mainframe VXI/VME system. Refer to the *VXIbus Mainframe Extender Specification*, Revision 1.3 or later, for more details on multiple mainframe systems.

### Controllers

A *controller* is a device that is capable of controlling other devices. A desktop computer with a MXI interface board, an embedded computer in a VXI/VME chassis, a VXI-MXI, and a VME-MXI may all be controllers depending on the configuration of the system.

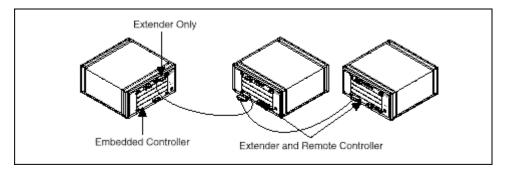

There are several types of controllers that may exist in a VXI/VME system: embedded, external, and remote.

- embedded controller—A computer plugged directly into the VXI/VME backplane. An example is the National Instruments VXIpc-850. All of the required VXI/VME interface capabilities are built directly onto the computer itself. An embedded computer has direct access to the VXI/VMEbus backplane in which it is installed.

- remote controller—A device in the VXI/VME system that has the capability to control the VXI/VMEbus, but has no intelligent CPU installed. An example is the VXI-MXI-2. In NI-VXI, the parent-side

VXI-MXI-2 (that is, the VXI-MXI-2 with a MXI-2 cable connected towards the root frame) in the frame acts as a remote controller. An embedded or external controller may use a remote controller to control the remote mainframe.

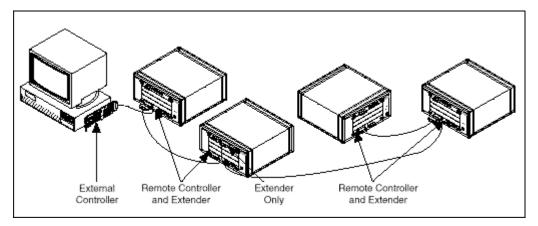

• *external controller*—A desktop computer or workstation connected to the VXI/VME system via a MXI interface board. An example is a standard personal computer with a PCI-MXI-2 installed.

In general, a multiple mainframe VXI/VME system will have one of the following controller configurations:

• An embedded controller in one frame that is connected to other frames via mainframe extenders using MXI-2. VXI-MXI-2 or VME-MXI-2 boards in the other frames can also be used as remote controllers. See Figure 1-3.

Figure 1-3. An Embedded Controller Connected to Other Frames via Mainframe Extenders Using MXI-2

• An external controller connected using MXI-2 to a number of remote controllers, each in a separate frame. The external controller can use the remote controllers for control of the VXI/VME system, or it can use its own controller capabilities. See Figure 1-4, An External Controller Connected Using MXI-2 to a Number of Remote Controllers.

Figure 1-4. An External Controller Connected Using MXI-2 to a Number of Remote Controllers

#### **The Extender and Controller Parameters**

In NI-VXI, some functions require a parameter named **extender** or **controller**. Since some extenders act as controllers, there is often confusion concerning what logical addresses should be passed to these functions.

The **extender** parameter is the logical address of a mainframe extender on which the function should be performed. Usually, functions with an **extender** parameter involve the mapping of interrupt lines or trigger lines into or out of a frame. The **controller** parameter is the logical address of an embedded, external, extending, or remote controller. Usually, functions with a **controller** parameter involve sourcing or sensing particular interrupts or triggers in a frame. According to the definitions of the different types of controllers, the only valid logical addresses for the **controller** parameter are:

- The external or embedded controller on which the program is running.

- A parent-side VXI-MXI-2 or VME-MXI-2 in a frame.

Most functions that take a **controller** parameter will allow you to pass (-1) as the logical address. This selects the default controller for the system. Notice that the default controller is determined by the following factors:

- If the program is running on an embedded controller, the default controller is the embedded controller.

- If the program is running on an external controller, you can configure whether the default controller is the external controller or the remote controller with the lowest numbered logical address. With this behavior, if you write a program on an embedded controller referring to the controller as logical address –1, you can swap the embedded controller configuration with an external controller configuration without changing your source code.

Notice that -1 is never a valid value for the **extender** parameter. In addition, the logical addresses of embedded and external controllers also are never valid values for the **extender** parameter. The **extender** parameter refers only to devices that can map interrupt lines, trigger lines, or other signals into or out of a frame.

## **Error Handling Parameter**

Each of the NI-VXI VIs contains error in and error out clusters that keep track of error information as the VIs execute. If the error in cluster passed to a VI already contains an error the VI will not execute. Instead it will only pass on the same error information. Otherwise, it will execute and pass the status of its execution out the error out terminal. More information on the error codes used by the VIs and how they relate to the status codes used by older versions of the NI-VXI VIs can be found in Appendix A, *Error Codes*.

## **Converting Old Applications**

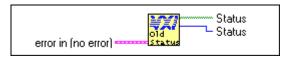

Existing programs automatically load the previous versions of the NI-VXI VIs. These VIs have the word "Old" on the icon and have \_old added to their names to distinguish them from the new VIs. The new NI-VXI VIs are supported only in LabVIEW 5.0 and later. You can combine Old and new VIs when you convert or add on to existing applications. However, only the new VIs use error clusters. The Old VIs are located in \labview\Vi.lib\Instr\VXI\old.

# System Configuration and VXI Library Initialization VIs

This chapter describes the System Configuration VIs. Your application program can use these VIs to copy all of the Resource Manager (RM) table information into data structures at startup so that you can find device names or logical addresses by specifying certain attributes of the device for identification purposes.

## Locating System Configuration VIs in LabVIEW

Select **Windows**»**Show Diagram** to go to the block diagram in LabVIEW. From the **Functions** palette, choose **Instrument I/O**»**VXI**»**System Configuration** to locate the System Configuration VIs in LabVIEW.

## Finding Help Online for System Configuration VIs

You can find helpful information about individual VIs online by using the LabVIEW Help window. Open the Help window by choosing **Help**»**Show Help** in LabVIEW. When you place the cursor on a VI icon, the wiring diagram and parameter names for that VI appear in the Help window.

You also can double-click the VI to open the front panel. When the Help window is open, you can get more information on each parameter by placing the cursor over the corresponding control or indicator on the VI front panel.

#### **Handling Errors**

The NI-VXI VIs use the LabVIEW error cluster method for handling errors. Each VI has error in and error out terminals. See Appendix A, *Error Codes*, for information on how the error codes relate to the previous status codes used by the NI-VXI VIs and a description of **error in** and **error out** parameters.

### System Configuration VI Descriptions

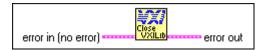

#### **CloseVXIIibrary**

Disables interrupts and frees dynamic memory allocated for the internal device information table. You should call this VI before exiting your application.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**error out** contains error information. If the error in cluster indicated an error, the error out cluster contains the same information. Otherwise, error out describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

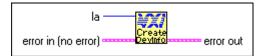

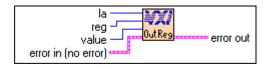

#### CreateDevInfo

Allocates space in the device information table for a new entry with logical address **la**. The fields in the device information table for the entry are set to default values (null or unasserted values).

**la** is the logical address of the device for which to create an entry in the device information table.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

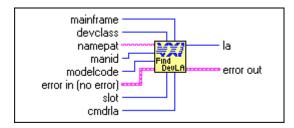

#### FindDevLA

Finds a VXI device with the specified attributes in the RM table and returns its logical address. You can use any combination of attributes to specify a device. In this manner, you can acquire unknown device names or logical addresses. If **namepat** is "" or any other attribute is -1, or not connected, that attribute is not used in the matching algorithm. If two or more devices match, **la** contains the logical address of the first device found.

**I16**

**mainframe** is the mainframe location of the device (logical address of mainframe extender).

devclass is the device class of the device.

- 0: Memory Class Device.

- 1: Extended Class Device.

- 2: Message-Based Device.

- 3: Register-Based Device.

abc

**namepat** is the name pattern. A partial name is acceptable (for example, for GPIB-VXI, it will accept GP).

manid is the VXI manufacturer identification number.

modelcode is the 12-bit or 16-bit model number of the VXI manufacturer.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| <b>I16</b> |

|------------|

| <b>I16</b> |

| <b>I16</b> |

| [set]      |

**slot** is the slot location of the device.

cmdrla is the logical address of the Commander.

la is the logical address of the device found.

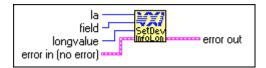

#### GetDevInfoLong

Gets information about a specified device from the device information table. The information is contained in a 32-bit unsigned integer.

la is the logical address of the device to get information about.

**field** is the field identification number.

- 12: Base of A24/A32 memory.

- 13: Size of A24/A32 memory.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| <b>U32</b> |  |

|------------|--|

| [243]      |  |

longvalue is the information for that field.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

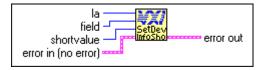

#### GetDevInfoShort

Gets information about a specified device from the device information table. The information is contained in a 16-bit unsigned integer.

la is the logical address of the device to get information about.

**field** is the field identification number.

- 2: Logical address of the Commander.

- 3: Mainframe.

- 4: Slot.

- 5: Manufacturer identification number.

- 7: Model code.

- 9: Device class.

- 10: Extended subclass (if extended class device).

- 11: Address space used.

- 14: Memory type and access time.

- 15: Bit vector list of VXI interrupter lines.

- 16: Bit vector list of VXI interrupt handler lines.

- 17: Mainframe extender, controller information.

| Bits      | Description                                                          |

|-----------|----------------------------------------------------------------------|

| 15 and 14 | Reserved                                                             |

| 13        | <ol> <li>Remote controller</li> <li>Not remote controller</li> </ol> |

| 12        | 1: Child side extender<br>0: Parent side extender                    |

| 11        | 1: Frame extender<br>0: Not frame extender                           |

| 10        | 1: Extended controller                                               |

| 9         | 1: Embedded controller                                               |

| 8         | 1: External controller                                               |

| 7 to 0    | Frame extender towards root frame                                    |

- 18: Asynchronous mode control state.

- 19: Response enable state.

- 20: Protocols supported.

- 21: Capability/status flags.

- 22: Status state (Pass/Fail, Ready/Not Ready).

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

shortvalue is the information for that field.

#### GetDevInfoStr

Gets information about a specified device from the device information table. The information is contained in **stringvalue**.

la is the logical address of the device to get information about.

field is the field identification number.

- 1: Device name.

- 6: Manufacturer name.

- 8: Model name.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| abc   |  |

|-------|--|

| [553] |  |

stringvalue is the information for that field.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### InitVXIIibrary

Allocates and initializes the data structures required by the VXI library VIs in the driver. This VI reads the RM table file and copies all of the RM information into data structures in local memory. It also performs other initialization operations, such as installing the default interrupt handlers.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

#### SetDevInfoLong

Sets information about a specified device in the device information table. The value being set is a 32-bit unsigned integer.

I16

la is the logical address of the device to set information for.

field is the field identification number.

12: Base of A24/A32 memory.

13: Size of A24/A32 memory.

longvalue is the information for that field.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

[26]

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### SetDevInfoShort

Sets information about a specified device in the device information table. The value being set is a 16-bit unsigned integer.

la is the logical address of the device to set information for.

**field** is the field identification number.

- 2: Logical address of the Commander.

- 3: Mainframe.

- 4: Slot.

- 5: Manufacturer identification number.

- 7: Model code.

- 9: Device class.

- 10: Extended subclass (if extended class device).

- 11: Address space used.

- 14: Memory type and access time.

- 15: Bit vector list of VXI interrupter lines.

- 16: Bit vector list of VXI interrupt handler lines.

- 17: Mainframe extender, controller information.

| Bits      | Description                                                          |

|-----------|----------------------------------------------------------------------|

| 15 and 14 | Reserved                                                             |

| 13        | <ol> <li>Remote controller</li> <li>Not remote controller</li> </ol> |

| 12        | 1: Child side extender<br>0: Parent side extender                    |

| 11        | 1: Frame extender<br>0: Not frame extender                           |

| 10        | 1: Extended controller                                               |

| 9         | 1: Embedded controller                                               |

| 15 to 13  | Reserved                                                             |

| 12        | 1: Child side extender<br>0: Parent side extender                    |

- 18: Asynchronous mode control state.

- 19: Response enable state.

- 20: Protocols supported.

- 21: Capability/status flags.

- 22: Status state (Pass/Fail, Ready/Not Ready).

shortvalue is the information for that field.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

#### SetDevInfoStr

Sets information about a specified device in the device information table. The information being set is contained in a string.

116 U16 la is the logical address of the device to set information for.

field is the field identification number.

- 1: Device name.

- 6: Manufacturer name.

- 8: Model name.

stringvalue is the buffer to receive information for that field.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

3

# Word Serial Commander Protocol VIs

This chapter describes the VXI Word Serial Commander Protocol VIs. Word Serial communication is the minimal mode of communication between VXI Message-Based devices within the VXI Commander/Servant hierarchy.

## Locating Word Serial Commander VIs in LabVIEW

Select **Windows»Show Diagram** to go to the block diagram in LabVIEW. From the **Functions** palette, choose **Instrument I/O»VXI»Word Serial Commander Protocol** to locate the Word Serial Commander Protocol VIs in LabVIEW.

## Finding Help Online for Word Serial Commander VIs

You can find helpful information about individual VIs online by using the LabVIEW Help window. Open the Help window by choosing **Help**»**Show Help** in LabVIEW. When you place the cursor on a VI icon, the wiring diagram and parameter names for that VI appear in the Help window.

You also can double-click on the VI to open the front panel. When the Help window is open, you can get more information on each parameter by placing the cursor over the corresponding control or indicator on the VI front panel.

#### **Handling Errors**

The NI-VXI VIs use the LabVIEW error cluster method for handling errors. Each VI has error in and error out terminals. See Appendix A, *Error Codes*, for information on how the error codes relate to the previous status codes used by the NI-VXI VIs and a description of **error in** and **error out** parameters.

### Word Serial Commander VI Descriptions

#### WSabort

Performs a Forced or Unrecognized (Unsupported) Command abort of a Word Serial operation(s) in progress.

**la** is the logical address of the Message-Based device.

**abortop** is the operation to abort.

- 1: Forced Abort: aborts WSwrt, WSrd, and WStrg.

- 2: UnSupCom: aborts WScmd, WSLcmd, and WSEcmd.

- 3: Forced Abort: aborts WScmd, WSLcmd, and WSEcmd.

- 4: Forced Abort: aborts all Word Serial operations.

- 5: Async Abort: aborts all Word Serial operations immediately. Be careful when using this option. During a Word Serial query, the Servant may be left in an invalid state if the operation is aborted after writing the query and before reading the response register. When using this option, the Word Serial operation is aborted immediately as compared to using options 1, 3, and 4, where the operation is not aborted until the response is read in that situation.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

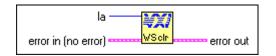

#### WSclr

Sends the Word Serial Clear command to a Message-Based device.

la is the logical address of the Message-Based device.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

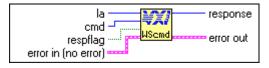

#### WScmd

Sends a Word Serial command or query to a Message-Based device.

la is the logical address of the Message-Based device.

**cmd** is the Word Serial command value.

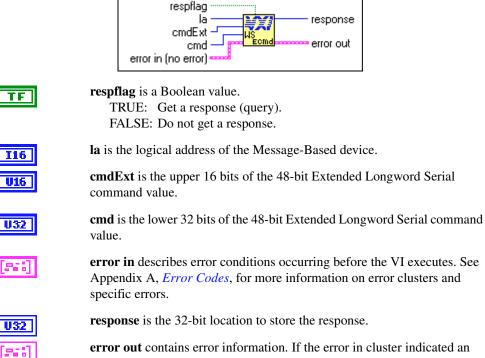

**respflag** is a Boolean value. TRUE: Get a response (query). FALSE: Do not get a response.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

response is the 16-bit response.

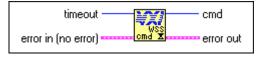

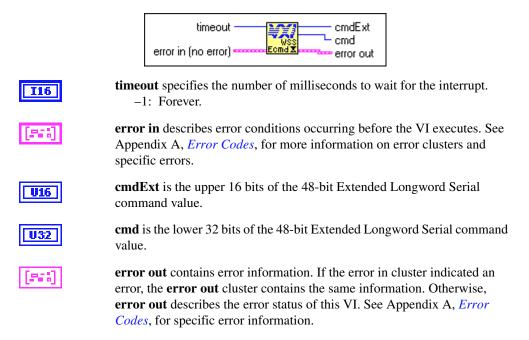

#### WSEcmd

Sends an Extended Longword Serial command or query to a Message-Based device.

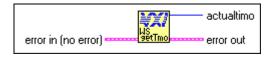

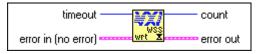

#### WSgetTmo

Gets the actual time period to wait before aborting a Word Serial, Longword Serial, or Extended Longword Serial Protocol transfer.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

actualtimo is the timeout period (in milliseconds).

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

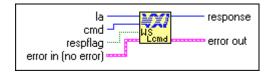

#### WSLcmd

Sends a Longword Serial command or query to a Message-Based device.

la is the logical address of the Message-Based device.

**cmd** is the Longword Serial command value.

**respflag** is a Boolean value. TRUE: Get a response (query). FALSE: Do not get a response.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

response is the 32-bit location to store the response.

#### **WSLresp**

Retrieves a response to a previously sent Longword Serial Protocol query from a VXI Message-Based device.

WSLcmd can send a query and automatically read a response. However, if you must break up the sending of the query and the reading of the response, you can use WSLcmd to send the query without reading the response and WSLresp to read the response.

L F

This VI is intended for debugging purposes only.

Note

la is the logical address of the Message-Based device.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| <b>U32</b> |

|------------|

| [201]      |

response is the 32-bit response.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

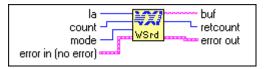

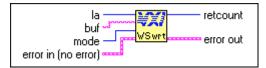

#### WSrd

Transfers the specified number of data bytes from a Message-Based device into a specified local memory buffer, using the VXIbus Byte Transfer Protocol.

**la** is the logical address of the Message-Based device from which the buffer is read.

count is the maximum number of bytes to transfer.

**mode** is the transfer mode bit vector. The following table describes the mode bit vector corresponding to bits 15 through 0.

| Bit     | Event Signal                                                                                                                                 |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 15 to 8 | EOS character (valid if EOS termination)                                                                                                     |

| 4       | <ul><li>EOS character termination</li><li>1: Terminate transfer on EOS bit.</li><li>0: Do not terminate transfer on EOS bit.</li></ul>       |

| 3       | <ul><li>CR character termination</li><li>1: Terminate transfer on CR bit.</li><li>0: Do not terminate transfer on CR bit</li></ul>           |

| 2       | <ul><li>LF character termination</li><li>1: Terminate transfer on LF bit.</li><li>0: Do not terminate transfer on LF bit</li></ul>           |

| 1       | <ul><li>END bit termination suppression</li><li>0: Terminate transfer on END bit.</li><li>1: Do not terminate transfer on END bit.</li></ul> |

| 0       | Not DOR<br>0: Abort if not DOR.<br>1: Poll until DOR                                                                                         |

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**buf** is the data read.

retcount is the number of bytes actually transferred.

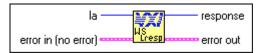

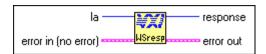

#### WSresp

Retrieves a response for a previously sent Word Serial Protocol query from a VXI Message-Based device.

The WScmd VI can send a query and automatically read a response. However, if it is necessary to break up the sending of the query and the reading of the response, you can use the WScmd VI to send the query without reading the response and use the WSresp VI to read the response.

This VI is intended for debugging purposes only.

Note

la is the logical address of the Message-Based device.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| <b>U16</b> |  |

|------------|--|

| [26]       |  |

response is the 16-bit response.

**error out** contains error information. If the error in cluster indicated an error, the error out cluster contains the same information. Otherwise, error out describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

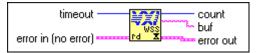

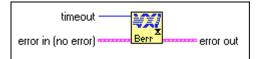

#### WSsetTmo

Sets the time period to wait before aborting a Word Serial, Longword Serial, or Extended Longword Serial Protocol transfer. It returns the actual timeout value set (the nearest timeout period possible greater than or equal to the timeout period specified).

| 132  |

|------|

| [55] |

timeout is the timeout period (in milliseconds).

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

actual timo is the actual timeout period set (in milliseconds).

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### WStrg

Sends the Word Serial *Trigger* command to a Message-Based device.

la is the logical address of the Message-Based device.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

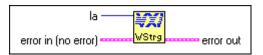

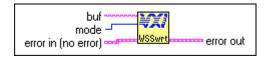

#### WSwrt

Transfers the specified number of data bytes from a memory buffer to a Message-Based device, using the VXIbus Byte Transfer Protocol.

**la** is the logical address of the Message-Based device to which the buffer is written.

| abc        |  |

|------------|--|

| <b>U16</b> |  |

buf is the write buffer.

mode is the transfer mode bit vector,

for Bit 0

- 1: Poll until device is DIR.

- 0: Abort if device is not DIR.

for Bit 1

- 1: Set the END bit on the last byte of the transfer.

- 0: Clear the END bit on the last byte of the transfer.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

retcount is the number of bytes actually transferred.

4

# Word Serial Servant Protocol VIs

This chapter describes the VXI Word Serial Servant Protocol VIs. Word Serial communication is the minimal mode of communication between VXI Message-Based devices within the VXI Commander/Servant hierarchy. The local CPU (the CPU on which the NI-VXI functions are running) uses the Word Serial Servant VIs to perform VXI Message-Based Word Serial Servant communication with its Commander.

You use these VIs only in the case where the local CPU is not a Top-Level Commander (probably not the Resource Manager), such as in a multiple CPU situation. In a multiple CPU situation, the local CPU must allow the Resource Manager device to configure the local CPU and can optionally implement some basic message-transfer Word Serial communication with its Commander. The four basic types of Word Serial Servant VIs are as follows:

- Command reception

- Query reception and responding

- Buffer sending

- Buffer receiving

Word Serial Protocol is a simple 16-bit transfer protocol between a Commander and its Servants. The Commander polls specific bits in the VXI Response register of the Servant to determine when a command can be written, when a response can be read from the Data Low register, and when a Word Serial protocol error occurs. Before a Commander can send a Word Serial command to a Servant, it must first poll the Write Ready (WR) bit until it is asserted (set to 1). The Commander can then write the command to the Data Low register.

If the Commander is sending a query, it first sends the query in the same manner as sending a command, but then continues by polling the Read Ready (RR) bit until it is asserted. It then reads the response from the Data Low register. A buffer write is a series of Byte Available Word Serial commands sent to the Servant, with the additional constraint that the Data In Ready (DIR) bit as well as the WR bit must be asserted before the *Byte Available* is sent. The lower 8 bits (bits 0 to 7) of the 16-bit command contains a single byte of data (bit 8 is the END bit). Therefore, one *Byte Available* is sent for each data byte in the buffer written.

A buffer read is a series of *Byte Request* Word Serial queries sent to the Servant, with the additional constraint that the Data Out Ready (DOR) bit, as well as the WR bit, must be asserted before the *Byte Request* is sent. The lower 8 bits (bits 0 to 7) of the 16-bit response contain a single byte of data (bit 8 is the END bit). Therefore, one *Byte Request* is sent for each data byte in the buffer read.

In addition to the WR, RR, DIR, and DOR bits that get polled during various Word Serial transfers, the ERR\* bit is also checked. The ERR\* bit indicates that a Word Serial Protocol error has occurred. The Word Serial Protocol error can be Unsupported Command, Multiple Query Error (MQE), DIR Violation, DOR Violation, RR Violation, or WR Violation. The Word Serial Servant Protocol VIs allow the local CPU to generate any of the Word Serial Protocol errors and to respond to the *Read Protocol Error* Word Serial query with the corresponding protocol error. The ERR\* bit assertion and unassertion are handled automatically.

The Longword Serial and Extended Longword Serial Protocols are similar to the Word Serial Protocol, but involve 32-bit and 48-bit command transfers, respectively, instead of the 16-bit transfers of the Word Serial Protocol. The VXI specification, however, provides no common command usages for these protocols. The commands are either VXI Reserved or User-Defined. The NI-VXI interface gives you the ability to receive and process any one of these commands.

## Locating Word Serial Servant Protocol VIs in LabVIEW

Select **Windows»Show Diagram** to go to the block diagram in LabVIEW. From the **Functions** palette, choose **Instrument I/O»VXI»Word Serial Servant Protocol** to locate the Word Serial Servant Protocol VIs in LabVIEW.

## Finding Help Online for Word Serial Servant Protocol VIs

You can find helpful information about individual VIs online by using the LabVIEW Help window. Open the Help window by choosing **Help**»**Show Help** in LabVIEW. When you place the cursor on a VI icon, the wiring diagram and parameter names for that VI appear in the Help window.

You can also double-click on the VI to open the front panel. When the Help window is open, you can get more information on each parameter by placing the cursor over the corresponding control or indicator on the VI front panel.

#### **Handling Errors**

The NI-VXI VIs use the LabVIEW error cluster method for handling errors. Each VI has error in and error out terminals. See Appendix A, *Error Codes*, for information on how the error codes relate to the previous status codes used by the NI-VXI VIs and a description of **error in** and **error out** parameters.

#### Word Serial Servant Protocol VI Descriptions

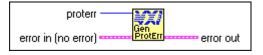

#### GenProtError

Generates a Word Serial protocol error if one is not already pending. The Response register bit ERR\* is asserted if the value of the protocol error, **proterr**, is not FFFF. If **proterr** is FFFF, ERR\* is unasserted. If no previous error existed, the **proterr** value is saved for response to a future *Read Protocol Error* query via the VI RespProtError.

**U16**

**proterr** is the protocol error to generate an error.

- FFFF: Clear any protocol error condition.

- FFFD: Multiple Query Error (MQE).

- FFFC: Unsupported Command (UnSupCom).

- FFFB: Data In Ready violation (DIRviol).

- FFFA: Data Out Ready violation (DORviol).

- FFF9: Read Ready violation (RRviol).

- FFF8: Write Ready violation (WRviol).

Other values are reserved.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| (See a) |

|---------|

|---------|

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

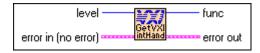

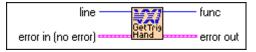

#### GetWSScmdHandler

Returns the address of the current WSScmd interrupt handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

| <b>U32</b> |

|------------|

|------------|

func is the address of the current WSScmd interrupt handler.0: Word Serial Servant VIs not supported.

| [24] |

|------|

|------|

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### GetWSSEcmdHandler

Returns the address of the current WSSEcmd interrupt handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

func is the address of the current WSSEcmd interrupt handler.0: Word Serial Servant VIs not supported.

LabVIFW VXI VI Reference Manual

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### GetWSSLcmdHandler

Returns the address of the current WSSLcmd interrupt handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

func is the address of the current WSSLcmd interrupt handler.0: Word Serial Servant VIs not supported.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### GetWSSrdHandler

Returns the address of the current WSSrd done notification interrupt handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**func** is the address of the current WSSrd done notification interrupt handler.

0: Word Serial Servant VIs not supported.

#### GetWSSwrtHandler

Returns the address of the current WSSwrt done notification interrupt handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**func** is the address of the current WSSwrt done notification interrupt handler.

0: Word Serial Servant VIs not supported.

| [244] |

|-------|

|-------|

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### RespProtError

Responds to the Word Serial *Read Protocol Error* query with the last protocol error generated via the GenProtError VI. The ERR\* bit is unasserted.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

[553]

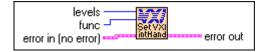

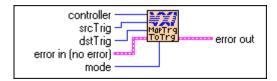

#### SetWSScmdHandler

Replaces the current WSScmd interrupt handler with a specified handler.

| 032 |

|-----|

|-----|

**func** is the address of the new WSScmd interrupt handler obtained from the GetWSScmdHandler VI.

- 0: Set to DefaultWSScmdHandler.

- 3: LabVIEW Occurrence Handler.

| [***] |

|-------|

|-------|

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

#### SetWSSEcmdHandler

Replaces the current WSSEcmd interrupt handler with a specified handler.

**func** is the address of the new WSSEcmd interrupt handler obtained from the GetWSScmdHandler VI.

- 0: Set to DefaultWSSEcmdHandler.

- 3: LabVIEW Occurrence Handler.

**U32**

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

[253]

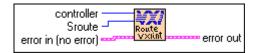

#### **SetWSSLcmdHandler**

Replaces the current WSSLcmd interrupt handler with a specified handler.

| • | 112-3 |

|---|-------|

|   | UJL.  |

**func** is the address of the new WSSLcmd interrupt handler obtained from the GetWSScmdHandler VI.

- 0: Set to DefaultWSSLcmdHandler.

- 3: LabVIEW Occurrence Handler.

error in describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

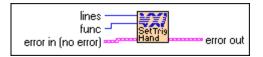

#### SetWSSrdHandler

**2** - 2

Replaces the current WSSrd done notification interrupt handler with a specified handler.

| 11.0-0 |

|--------|

| UJZ.   |

| <br>   |

**func** is the address of the new WSSrd done notification handler obtained from the GetWSScmdHandler VI.

- 0: Set to DefaultWSSrdHandler.

- 3: LabVIEW Occurrence Handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

[243]

#### SetWSSwrtHandler

Replaces the current WSSwrt done notification interrupt handler with a specified handler.

| 11227 |

|-------|

|       |

**func** is the address of the new WSSwrt done notification handler obtained from the GetWSScmdHandler VI.

- 0: Set to DefaultWSSwrtHandler.

- 3: LabVIEW Occurrence Handler.

**error in** describes error conditions occurring before the VI executes. See Appendix A, *Error Codes*, for more information on error clusters and specific errors.

**error out** contains error information. If the error in cluster indicated an error, the **error out** cluster contains the same information. Otherwise, **error out** describes the error status of this VI. See Appendix A, *Error Codes*, for specific error information.

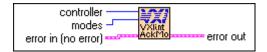

#### WSSabort

Aborts the Word Serial Servant operation(s) in progress.

| I16 |

|-----|

|-----|

**abortop** is the operation to abort, bit vector.

| Bit | Description                                                                                                                                                                                                  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Abort WSSwrt                                                                                                                                                                                                 |