#### **COMPREHENSIVE SERVICES**

We offer competitive repair and calibration services, as well as easily accessible documentation and free downloadable resources.

#### SELL YOUR SURPLUS

We buy new, used, decommissioned, and surplus parts from every NI series. We work out the best solution to suit your individual needs. We Sell For Cash We Get Credit We Receive a Trade-In Deal

**OBSOLETE NI HARDWARE IN STOCK & READY TO SHIP**

We stock New, New Surplus, Refurbished, and Reconditioned NI Hardware.

APEX WAVES

**Bridging the gap** between the manufacturer and your legacy test system.

1-800-915-6216

www.apexwaves.com

sales@apexwaves.com

$\bigtriangledown$

All trademarks, brands, and brand names are the property of their respective owners.

Request a Quote Sclick HERE CRIO-9057

**USER MANUAL**

# cRIO-905x

# Embedded CompactRIO Controller with Real-Time Processor and Reconfigurable FPGA

This document describes the features of the cRIO-905x and contains information about mounting and operating the device.

In this document, the cRIO-9053, cRIO-9054, cRIO-9055, cRIO-9056, cRIO-9057, cRIO-9058 are referred to collectively as cRIO-905*x*.

# Contents

| Configuring the cRIO-905x                                               | 2    |

|-------------------------------------------------------------------------|------|

| Connecting the cRIO-905x to the Host Computer Using USB                 | 3    |

| Connecting the cRIO-905x to the Host Computer or Network Using Ethernet |      |

| Configuring Startup Options                                             | 4    |

| cRIO-905x Features                                                      | 6    |

| Ports and Connectors                                                    | 6    |

| Buttons                                                                 | . 10 |

| LEDs                                                                    | 11   |

| Chassis Grounding Screw                                                 | . 14 |

| Internal Real-Time Clock                                                | 14   |

| Digital Routing                                                         | 14   |

| Clock Routing                                                           |      |

| Synchronization Across a Network                                        |      |

| Battery                                                                 | . 18 |

| File System                                                             | 18   |

| Mounting the Controller                                                 | 19   |

| Alternative Mounting Configurations                                     | 20   |

| Mounting Requirements                                                   | 20   |

| Dimensions                                                              | 21   |

| Rear Mounting on a Flat Surface                                         | . 23 |

| Front Mounting on a Flat Surface                                        | . 25 |

| Mounting the Controller on a Panel                                      | 27   |

| Mounting on a DIN Rail                                                  | . 30 |

| Mounting on a Rack                                                      | 32   |

| Mounting the Device on a Desktop                                        | 32   |

| Choosing Your Programming Mode                                          | . 36 |

| Analog Input with NI-DAQmx                                              | . 37 |

| Analog Output with NI-DAQmx                                             | . 43 |

| Digital Input/Output with NI-DAQmx                                      | . 49 |

| PFI with NI-DAQmx                                                       | . 61 |

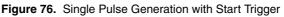

| Counters with NI-DAQmx                                                  | 62   |

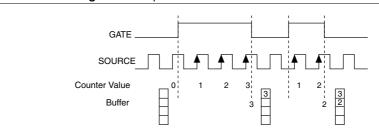

| Counter Input Applications                                              | . 67 |

| Counter Output Applications                                             | . 86 |

| Counter Timing Signals                                                  | . 94 |

| Worldwide Support and Services                                          | . 99 |

# Configuring the cRIO-905x

You can connect the cRIO-905*x* to a host computer or network and configure the startup options using the USB 2.0 Type-C Device Port with Console Out or the RJ-45 Gigabit Ethernet port 0.

**Tip** Refer to the *cRIO-905x Getting Started Guide* for basic configuration instructions and information about connecting to a host computer using the USB 2.0

Type-C Device Port with Console Out. NI recommends using the USB 2.0 Type-C Device Port with Console Out for configuration, debugging, and maintenance.

# Connecting the cRIO-905*x* to the Host Computer Using USB

Complete the following steps to connect the cRIO-905x to the host computer using the USB 2.0 Type-C Device Port with Console Out.

- 1. Power on the host computer.

- 2. Connect the cRIO-905*x* to the host computer using the USB Type C to Type A cable (included in kit), inserting the USB Type-C connector into the USB 2.0 Type-C Device Port with Console Out.

- 3. Connect the other end of the USB cable (Type-A) to the host computer.

**Note** The device driver software automatically detects the cRIO-905*x*. If the device driver software does not detect the cRIO-905*x*, verify that you installed the appropriate NI software in the correct order on the host computer as described in *Installing Software on the Host Computer* in the *cRIO-905x Getting Started Guide*.

4. Select Configure and install software to this device.

# Connecting the cRIO-905x to the Host Computer or Network Using Ethernet

Complete the following steps to connect the cRIO-905x to a host computer or Ethernet network using the RJ-45 Gigabit Ethernet port 0. NI recommends using the RJ-45 Gigabit Ethernet port 0 for communication with deployed systems.

**Note** If your controller has the RJ-45 Gigabit Ethernet port 1, you can configure that port in Measurement & Automation Explorer (MAX) under the **Network Settings** tab.

- 1. Power on the host computer or Ethernet hub.

- Connect the RJ-45 Gigabit Ethernet port 0 on the cRIO-905x to the host computer or Ethernet hub using a standard Category 5 (CAT-5) or better shielded, twisted-pair Ethernet cable.

**Notice** To prevent data loss and to maintain the integrity of your Ethernet installation, do not use a cable longer than 100 m (328 ft).

The cRIO-905x attempts to initiate a DHCP network connection the first time you connect using Ethernet. The cRIO-905x connects to the network with a link-local IP address with the form 169.254.x.x if it is unable to initiate a DHCP connection.

## Finding the cRIO-905x on the Network (DHCP)

Complete the following steps to find the cRIO-905x on a network using DHCP.

- 1. Disable secondary network interfaces on the host computer, such as a wireless access card on a laptop.

- 2. Ensure that any anti-virus and firewall software running on the host computer allows connections to the host computer.

**Note** MAX uses UDP on port 44525. Refer to the documentation of your firewall software for information about configuring the firewall to allow communication through this port.

- 3. Launch MAX on the host computer.

- 4. Expand Remote Systems in the configuration tree and locate your system.

**Tip** MAX lists the system under the model number followed by the serial number, such as NI-cRIO-905x-1856AAA.

**Tip** If you do not see the cRIO-905x under **Remote Systems**, use the **Troubleshoot Remote System Discovery** utility to walk through troubleshooting steps.

# **Configuring Startup Options**

Complete the following steps to configure the cRIO-905x startup options in MAX.

- 1. In MAX, expand your system under Remote Systems.

- 2. Select the **Startup Settings** tab to configure the startup settings.

## cRIO-905x Startup Options

You can configure the following cRIO-905x startup options.

| Startup Option                         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Force Safe Mode                        | Rebooting the cRIO-905x with this setting on starts the cRIO-905x without launching LabVIEW Real-Time or any startup applications. In safe mode, the cRIO-905x launches only the services necessary for updating configuration and installing software.                                                                                                                                                                                                                                       |

| Enable Console<br>Out                  | <ul> <li>Rebooting the cRIO-905<i>x</i> with this setting on redirects the console output to the USB 2.0 Type-C Device Port with Console Out. You can use a serial-port terminal program to read the IP address and firmware version of the cRIO-905<i>x</i>. Make sure that the serial-port terminal program is configured to the following settings:</li> <li>115,200 bits per second</li> <li>Eight data bits</li> <li>No parity</li> <li>One stop bit</li> <li>No flow control</li> </ul> |

| Disable RT<br>Startup App              | Rebooting the cRIO-905 $x$ with this setting on prevents any LabVIEW startup applications from running.                                                                                                                                                                                                                                                                                                                                                                                       |

| Disable FPGA<br>Startup App            | Rebooting the cRIO-905 $x$ with this setting on prevents autoloading of any FPGA application.                                                                                                                                                                                                                                                                                                                                                                                                 |

| Enable Secure<br>Shell (SSH)<br>Logins | Rebooting the cRIO-905x with this setting on starts sshd on the cRIO-905x. Starting sshd enables logins over SSH, an encrypted communication protocol.         Note       Visit <i>ni.com/info</i> and enter the Info Code openssh for more information about SSH.                                                                                                                                                                                                                            |

| LabVIEW Project<br>Access              | Rebooting the cRIO-905 $x$ with this setting on enables you to add the target to a LabVIEW project.                                                                                                                                                                                                                                                                                                                                                                                           |

#### Table 1. cRIO-905x Startup Options

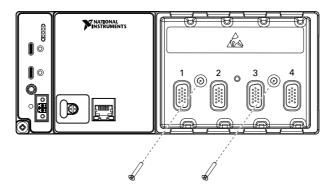

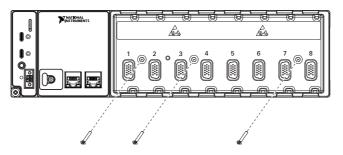

# cRIO-905x Features

## Ports and Connectors

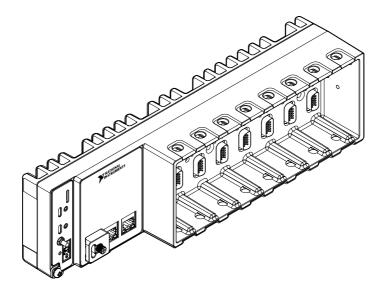

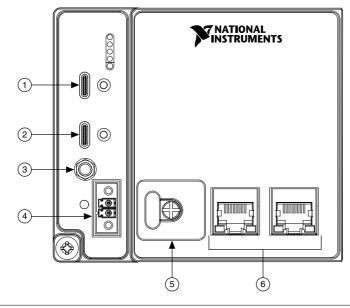

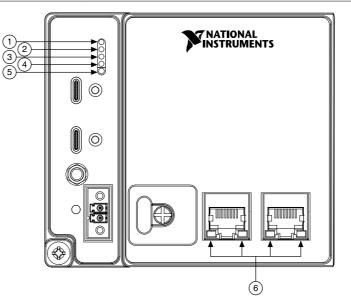

Figure 1. cRIO-905x Ports and Connectors

- 1. USB 2.0 Type-C Device Port with Console Out

- 2. USB 3.1 Type-C Host Port

- 3. PFI 0

- 4. Power Connector

- 5. SD Association MicroSD Card Removable Storage

- 6. RJ-45 Gigabit Ethernet Ports (one or two, depending on the model)

## USB 2.0 Type-C Device Port with Console Out

When operating a device, use this port to connect the cRIO-905x to a host PC. The USB device functionality provides an alternate method to connect the controller to a host PC for configuration, application deployment, debugging, and maintenance.

Console Out over USB requires a virtual COM port driver on the host PC. This driver installs with CompactRIO 18.1 or later.

You must enable Console Out on the cRIO-905x in Measurement & Automation Explorer (MAX) or by booting the controller into Safe Mode.

**Note** This port cannot be accessed by the user application when the Console Out startup option is enabled.

## USB 3.1 Type-C Host Port

The USB host port on the cRIO-905x support common USB mass-storage devices such as USB Flash drives, USB-to-IDE adapters, keyboards, mice, and USB cameras.

The following NI USB Type-C adapters are available for the cRIO-905x.

| Cable                                                               | Length | Part Number |  |

|---------------------------------------------------------------------|--------|-------------|--|

| USB Cable with Retention, Type-C Male to Type-A Female, USB 3.1, 3A | 0.5 m  | 143555-0R5  |  |

The following NI cables with retention are available for use with the cRIO-905x.

| Cable                                                             | Length | Part Number |

|-------------------------------------------------------------------|--------|-------------|

| USB Cable with Retention, Type-C Male to Type-C Male, USB 3.1, 3A | 0.3 m  | 143556-0R3  |

|                                                                   | 1 m    | 143556-01   |

|                                                                   | 2 m    | 143556-02   |

#### Table 3. NI USB Cables with Retention

## PFI 0

The Programmable Function Interface (PFI) terminal is a SMB connector. You can configure the PFI terminal as a timing input or timing output signal for AI, AO, DI, DO, or counter/timer functions.

**Note** The PFI 0 terminal can only be used while the module is in the Real Time programmatic mode. For more information about programming modes, refer to *Choosing Your Programming Mode*.

## **Power Connector**

The cRIO-905x has a power connector to which you can connect a power supply.

| Pinout      | Pin | Description |

|-------------|-----|-------------|

| $\square$   | V   | Power input |

| v<br>C<br>C | С   | Common      |

Table 4. Power Connector Pinout

The cRIO-905x has reverse-voltage protection.

The following NI power supplies and accessories are available for use with the cRIO-905x.

| Accessory                                                                  | Part Number |  |  |

|----------------------------------------------------------------------------|-------------|--|--|

| NI PS-10 Desktop Power Supply, 24 V DC, 5 A, 100-120/200-240 V AC<br>Input | 782698-01   |  |  |

| NI PS-14 Industrial Power Supply, 24 to 28 V DC, 3.3 A, 100-240 V AC Input | 783167-01   |  |  |

| NI PS-15 Industrial Power Supply, 24 to 28 V DC, 5 A, 100/230 V AC Input   | 781093-01   |  |  |

| NI PS-16 Industrial Power Supply, 24 to 28 V DC, 10 A, 115/230 V AC Input  | 781094-01   |  |  |

| NI PS-17 Industrial Power Supply, 24 to 28 V DC, 20 A, 85-276 V AC Input   | 781095-01   |  |  |

#### Table 5. Power Supplies

#### Table 6. Power Accessories

| Accessory                                                       | Part Number |

|-----------------------------------------------------------------|-------------|

| 2-Position Screw Terminal Power Connector for cRIO-905x (Qty 4) | 786902-01   |

| NI 9971 Backshell for 2-Position Connector Block (Qty 4)        | 196375-01   |

#### MicroSD Card Removable Storage

The cRIO-905*x* has a microSD card slot that reads from and writes to microSD cards. The slot supports microSD card interface speeds up to UHS-I DDR50.

**Notice** Using microSD cards that are not approved by NI might invalidate specifications and result in unreliable performance.

The following accessories are available for use with the cRIO-905x.

| Accessory                                       | Capacity | Part Number |

|-------------------------------------------------|----------|-------------|

| Industrial microSD card, -40 °C to 85 °C, UHS-I | 16 GB    | 786913-01   |

| MicroSD card slot cover (x3)                    | _        | 786901-01   |

#### Table 7. MicroSD Storage Accessories

#### MicroSD Card Slot Cover

You must use the microSD card slot cover to protect the microSD card in hazardous locations. Do not remove a microSD card while the SD IN USE LED is flashing or solid because file corruption may result.

**Note** Screw the slot cover closed completely. Tighten the captive screws to a maximum torque of  $0.75 \text{ N} \cdot \text{m} (6.7 \text{ lb} \cdot \text{in.})$  using a #1 Phillips screwdriver. Do not overtighten.

## **RJ-45 Gigabit Ethernet Port**

The cRIO-905x will have one or two tri-speed RJ-45 Gigabit Ethernet ports. By default, the Ethernet port is enabled and configured to obtain an IP address automatically. The Ethernet port can be configured in MAX.

| Fast Ethernet Signal | Gigabit Ethernet Signal | Pin | Pinout |

|----------------------|-------------------------|-----|--------|

| TX+                  | TX_A+                   | 1   |        |

| TX-                  | TX_A-                   | 2   |        |

| RX+                  | RX_B+                   | 3   |        |

| No Connect           | TX_C+                   | 4   |        |

| No Connect           | TX_C-                   | 5   |        |

| RX-                  | RX_B-                   | 6   |        |

| No Connect           | RX_D+                   | 7   |        |

| No Connect           | RX_D-                   | 8   |        |

#### Table 8. RJ-45 Gigabit Ethernet Port Pinout

**Note** The Ethernet port performs automatic crossover configuration so you do not need to use a crossover cable to connect to a host computer.

The following NI Ethernet cables are available for use with the cRIO-905x.

| Table 9. RJ-45 Gigabit Ethernet Cable | es |

|---------------------------------------|----|

|---------------------------------------|----|

| · · · · · · · · · · · · · · · · · · · |        |             |  |

|---------------------------------------|--------|-------------|--|

| Cables                                | Length | Part Number |  |

|                                       | 2 m    | 151733-02   |  |

| CAT-5E Ethernet Cable, shielded       | 5 m    | 151733-05   |  |

|                                       | 10 m   | 151733-10   |  |

# **Buttons**

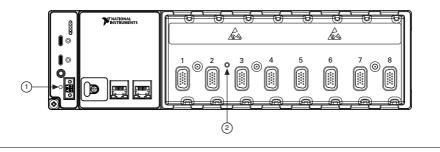

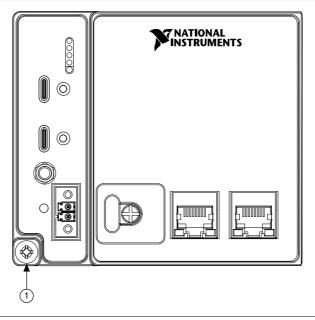

Figure 2. cRIO-905x Buttons

- 1. RESET Button

- 2. CMOS Reset Button

## **RESET Button**

Press the RESET button to reset the processor in the same manner as cycling power.

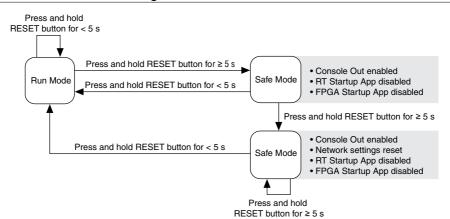

Figure 3. Reset Button Behavior

For more information about using the RESET button for network troubleshooting, see *Troubleshooting Network Connectivity*.

#### Troubleshooting Network Connectivity

You can use the RESET button to troubleshoot network connectivity.

Complete the following steps to reset the network adapters to default settings.

- 1. Hold the RESET button for 5 seconds, and then release it to boot the controller in safe mode and enable Console Out.

- 2. Hold the RESET button again for 5 seconds to boot the controller into safe mode, enable Console Out, and reset network adapters to default settings.

## **CMOS Reset Button**

The cRIO-905x has a CMOS reset button that you can use to reset the CMOS and the BIOS.

# LEDs

Figure 4. cRIO-905x Front Panel LEDs

- 1. POWER LED

- 2. STATUS LED

- 3. SD IN USE LED

- 4. USER1 LED

- 5. USER FPGA1 LED

- 6. Gigabit Ethernet LEDs

## **POWER LED Indicators**

#### Table 10. POWER LED Indicators

| LED Pattern | Indication                       |

|-------------|----------------------------------|

| Solid       | The cRIO-905 $x$ is powered on.  |

| Off         | The cRIO-905 $x$ is powered off. |

## STATUS LED Indicators

| LED Pattern                      | Indication                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Blinks twice and<br>pauses       | The cRIO-905 <i>x</i> is in safe mode. Software is not installed, which is the factory default state, or software has been improperly installed on the cRIO-905 <i>x</i> . An error can occur when an attempt to upgrade the software is interrupted. Reinstall software on the cRIO-905 <i>x</i> . Refer to the <i>Measurement &amp; Automation Explorer (MAX) Help</i> for information about installing software on the cRIO-905 <i>x</i> .                  |

| Blinks three times<br>and pauses | The cRIO-905 <i>x</i> is in user-directed safe mode, or the cRIO-905 <i>x</i> is in install mode to indicate that software is currently being installed. This pattern may also indicate that the user has forced the cRIO-905 <i>x</i> to boot into safe mode by pressing the reset button for longer than five seconds or by enabling safe mode in MAX. Refer to the <i>Measurement &amp; Automation Explorer (MAX) Help</i> for information about safe mode. |

| Blinks four times<br>and pauses  | The cRIO-905 $x$ is in safe mode. The software has crashed twice without rebooting or cycling power between crashes.                                                                                                                                                                                                                                                                                                                                           |

| Continuously blinks              | The cRIO-905 <i>x</i> has not booted into NI Linux Real-Time. The cRIO-905 <i>x</i> either booted into an unsupported operating system, was interrupted during the boot process, or detected an unrecoverable software error. If the problem persists, contact NI for support.                                                                                                                                                                                 |

| On momentarily                   | The cRIO-905 $x$ is booting. No action required.                                                                                                                                                                                                                                                                                                                                                                                                               |

| Off                              | The cRIO-905 $x$ is in run mode. Software is installed and the operating system is running.                                                                                                                                                                                                                                                                                                                                                                    |

#### Table 11. STATUS LED Indicators

## User LEDs

You can define the behavior of the USER1 LED and the USER FPGA1 LED to meet the needs of your application.

| LED           | LED Color | Description                                                                                                                                                                                                                                                                 |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USER1         | Green     | Use LabVIEW Real-Time to define the USER1 LED with the RT LEDs VI. For more information about the RT LEDs VI, refer to the <i>LabVIEW Help</i> .                                                                                                                            |

| USER<br>FPGA1 | Green     | Use the LabVIEW FPGA Module and NI-RIO Device Drivers<br>software to define the USER FPGA1 LED. Use the USER<br>FPGA1 LED to help debug your application or retrieve<br>application status. Refer to the <i>LabVIEW Help</i> for information<br>about programming this LED. |

Table 12. User LEDs

## SD IN USE LED Indicators

| Table 13. SD IN USE LED Indicato | rs |

|----------------------------------|----|

|----------------------------------|----|

| LED Pattern | Indication                             |

|-------------|----------------------------------------|

| Solid       | A microSD card is present and mounted. |

| Off         | No microSD card is present.            |

## Ethernet LED Indicators

#### Table 14. Ethernet LED Indicators

| LED         | LED Color | LED Pattern | Indication                    |  |

|-------------|-----------|-------------|-------------------------------|--|

| ACT/LINK    |           | Off         | LAN link not established      |  |

|             | Green     | Solid       | LAN link established          |  |

|             |           | Flashing    | Activity on LAN               |  |

| 10/100/1000 | Yellow    | Solid       | 1,000 Mb/s data rate selected |  |

|             | Green     | Solid       | 100 Mb/s data rate selected   |  |

|             |           | Off         | 10 Mb/s data rate selected    |  |

## **Chassis Grounding Screw**

Figure 5. cRIO-905x Chassis Grounding Screw

1. Chassis Grounding Screw

**Note** For information about grounding the cRIO-905x, see *Grounding the Controller* in the *cRIO-905x Getting Started Guide*.

**Note** For more information about ground connections, visit *ni.com/info* and enter the Info Code emcground.

## Internal Real-Time Clock

The cRIO-905*x* contains an internal real-time clock that maintains system time when the cRIO-905*x* is powered off. The system clock of the cRIO-905*x* is synchronized with the internal real-time clock at startup. You can set the real-time clock using the BIOS setup utility or MAX, or you can set the real-time clock programmatically using LabVIEW.

Refer to the model specifications on *ni.com/manuals* for the real-time clock accuracy specifications.

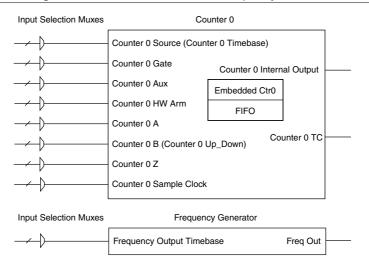

# **Digital Routing**

The digital routing circuitry of the cRIO-905x manages the flow of data between the bus interface and the acquisition and generation sub-systems when programming C Series modules in Real-Time (NI-DAQmx) mode. The subsystems include analog input, analog output, digital

I/O, and counters. The digital routing circuitry uses FIFOs (if present) in each sub-system to ensure efficient data movement.

**Note** When programming C Series modules in FPGA mode, the flow of data between the modules and the bus interface is programmed using LabVIEW FPGA.

The digital routing circuitry also routes timing and control signals. The acquisition and generation sub-systems use these signals to manage and synchronize acquisitions and generations. These signals can come from the following sources:

- C Series modules programmed in Real-Time (NI-DAQmx) mode

- User input through the PFI terminals using parallel digital C Series modules or the cRIO-905x PFI 0 terminal

- FPGA or DAQ ASIC using the cRIO trigger bus to share hardware triggers and signals between the LabVIEW FPGA and DAQmx applications

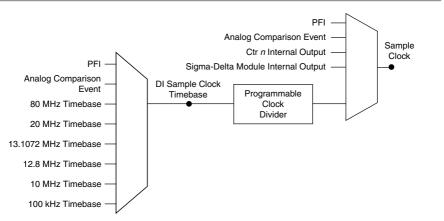

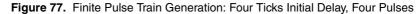

# **Clock Routing**

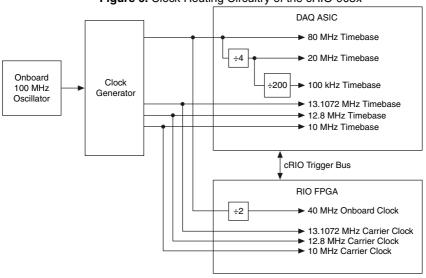

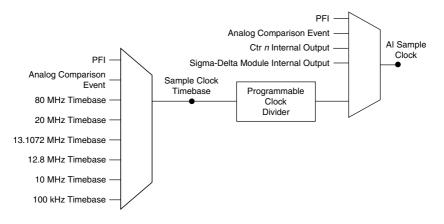

The following figure shows the clock routing circuitry of the cRIO-905x.

Figure 6. Clock Routing Circuitry of the cRIO-905x

**Note** When switching between programming modes, you may notice the terms timebase and clock used interchangeably. This is due to the DAQ ASIC and the RIO FPGA using different terminology for timing and clock mechanisms. The documentation will use the term based on the programming mode discussed.

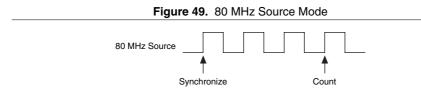

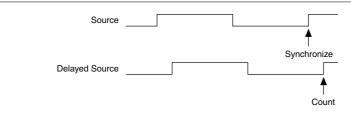

## 80 MHz Timebase

When programming C Series modules in Real-Time (NI-DAQmx) mode, the 80 MHz timebase can function as the source input to the 32-bit general-purpose counter/timers. The 80 MHz timebase is generated from the onboard oscillator.

## 20 MHz and 100 kHz Timebases

When programming C Series modules in Real-Time (NI-DAQmx) mode, the 20 MHz and 100 kHz timebases can be used to generate many of the analog input and analog output timing signals. These timebases can also function as the source input to the 32-bit general-purpose counter/timers. The 20 MHz and 100 kHz timebases are generated by dividing down the 80 MHz timebase, as shown in the previous figure.

## 40 MHz Onboard Clock

When programming C Series modules in FPGA mode, the 40 MHz onboard clock is used as the top-level clock for your LabVIEW FPGA application and C Series module IO nodes. The 40 MHz onboard clock can be used to clock single-cycle timed loops. Derived clocks of varying frequency can be generated from the 40 MHz onboard clock. The 40 MHz onboard clock is phase aligned with the incoming 80 MHz clock.

# 13.1072 MHz, 12.8 MHz, and 10 MHz Timebases and Carrier Clocks

When programming C Series modules in Real-Time (NI-DAQmx) mode, the 13.1072 MHz, 12.8 MHz, and 10 MHz timebases can be used to generate many of the analog input and analog output timing signals. These timebases can also function as the source input to the 32-bit general-purpose counter/timers. The 13.1072 MHz, 12.8 MHz, and 10 MHz timebases are generated directly from the onboard clock generator.

When programming C Series modules in FPGA mode, the 13.1072 MHz, 12.8 MHz, and 10 MHz carrier clocks can be used as the master clock for C Series analog input and analog output modules. The 13.1072 MHz, 12.8 MHz, and 10 MHz carrier clocks are available as IO Nodes in LabVIEW FPGA applications and can be used to correlate the onboard clocks with self-timed C Series modules containing free-running clocks.

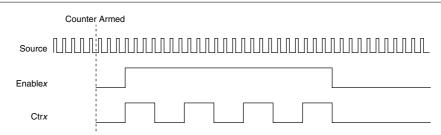

# Synchronization Across a Network

## Internal Timebase

The onboard 100 MHz oscillator automatically synchronizes to other network-synchronized devices that are part of the local IEEE 802.1AS or IEEE 1588-2008 subnet, depending on the active time reference that is being used on the controller.

The 80 MHz, 40 MHz, 20 MHz, 100 kHz, 13.1072 MHz, 12.8 MHz, and 10 MHz timebases are derived from the onboard oscillator and are synchronized to it. Therefore, the timebases are also synchronized to other network-synchronized timebases on the IEEE 802.1AS or IEEE 1588-2008 subnet. This enables analog input, analog output, digital I/O, and counter/ timers to be synchronized to other chassis across a distributed network.

When programming C Series modules in FPGA mode, the Time Synchronization IO Nodes can be used to synchronize the LabVIEW FPGA application to other network-synchronized devices.

## Network-based Synchronization

IEEE 1588, also known as the precision time protocol (PTP), is an Ethernet-based synchronization method designed for cabled, local networks. The PTP protocol provides a fault tolerant method of synchronizing all participating clocks to the highest quality clock in the network. This method of synchronization between networked devices uses packet-based communication and is possible over the long distances allowed for each Ethernet link, without signal propagation impact. IEEE 1588 has many different profiles, such as IEEE 802.1AS-2011, each of which use different features. Because the profiles are not interoperable with each other, make sure it is known which profile is implemented on the device. For devices on the network to synchronize with each other using IEEE 1588, all devices must be compatible with the desired IEEE 1588 profile and must all be connected within the selected IEEE 1588 profile-compliant network infrastructure.

The cRIO-905*x* controllers are compatible with both the IEEE 802.1AS-2011 profile and the IEEE 1588-2008 (1588v2) Delay Request-Response profile. However, each network port must be configured individually to the specific profile required for the network.

#### Differences Between IEEE 802.1AS-2011 and IEEE 1588-2008

IEEE 802.1AS-2011, also known as the generalized precision time protocol (gPTP), is a profile of IEEE 1588. A cRIO-905*x* controller can be configured to use either the IEEE 802.1AS-2011 profile or the IEEE 1588-2008 profile by configuring the port's time reference. If a user does not explicitly specify which time reference to use a cRIO-905*x* controller will default to use the IEEE 802.1AS-2011 profile. There are some differences between the IEEE 802.1AS-2011 profile and the IEEE 1588-2008 profile which are called out below:

- IEEE 802.1AS-2011 assumes all communication between devices is done on the OSI layer 2, while IEEE 1588-2008 can support various layer 2 and layer 3-4 communication methods. The IEEE 1588-2008 profile National Instruments implements on the cRIO-905x only supports layer 3-4 communication methods. Operating on the layer 2 yields better performance for the IEEE 802.1AS-2011.

- IEEE 802.1AS-2011 only communicates gPTP information directly with other IEEE 802.1AS devices within a system. Therefore, there must be IEEE 802.1AS-2011 support along the entire path from one IEEE 802.1AS-2011 device to another. With IEEE 1588-2008, it is possible to use non-IEEE 1588-2008 switches between two IEEE 1588-2008 devices. The benefit of having IEEE 802.1AS-2011 support along the entire path is a faster performance and lower jitter compared to IEEE 1588-2008.

- With IEEE 802.1AS-2011 there are only two types of time-aware systems: time-aware end stations and time-aware bridges. Whereas with IEEE 1588-2008, there are the following: ordinary clock, boundary clock, end-to-end transparent clock and a time-aware bridges. Based on these factors, IEEE 802.1AS-2011 can reduce complexity and configuration challenges compared to IEEE 1588-2008. A cRIO-905x controller acts as a time-aware end station for both protocols.

#### IEEE 1588 External Switch Requirements

To take advantage of the network synchronization features of the cRIO-905*x* controllers, ensure that your network infrastructure meets certain requirements depending on which IEEE 1588 profile is implemented for your application:

- IEEE 802.1AS-2011 support—Automatically enables timebase synchronization and enables the use of time-based triggers and timestamping between devices across the network. Synchronization performance will meet NI product specifications.

- IEEE 1588-2008 support—Enables timebase synchronization and enables the use of timebased triggers and timestamping between devices across the network. Synchronization performance will vary and may not meet NI product specifications. As a default configuration for IEEE 1588-2008, NI supports the IEEE 1588 Delay Request-Response profile, using the UDP over IP transport (layer 3-4).

# Battery

The cRIO-905*x* contains a lithium cell battery that stores the system clock information when the cRIO-905*x* is powered off. There is only a slight drain on the battery when power is applied to the cRIO-905*x* power connector. The rate at which the battery drains when power is disconnected depends on the ambient storage temperature. For longer battery life, store the cRIO-905*x* at a cooler temperature and apply power to the power connector. Refer to the specifications on *ni.com/manuals* for the expected battery lifetime.

The battery is not user-replaceable. If you need to replace the battery, contact NI. Refer to the controller specifications on *ni.com/manuals* for information about battery disposal.

# File System

LabVIEW mounts USB devices and microSD cards to the media/sdx1 directory and creates symbolic links /u, /v, /w, or /x to the media mount point, starting with /u if it is available. To prevent any file corruption to external storage devices, verify that any file IO operations with the specific drive finish before removing the device. Refer to the *LabVIEW Help* for more information.

The file system of the cRIO-905*x* follows conventions established for UNIX-style operating systems. Other LabVIEW Real-Time targets follow Microsoft Windows-style conventions. In order to facilitate the porting of applications from those targets, this target supports the Windows-style /C home directory. This path is bound to the UNIX-style directory /home/lvuser.

Various LabVIEW Real-Time system files which would be accessible from C: (or /C) on other LabVIEW Real-Time targets are found in different locations on this target.

UNIX-style file systems support the concept of a symbolic link, which allows access to a file using an alternative file path. For example, it is possible to link /C/ni-rt/system, where dynamic libraries are deployed on other LabVIEW Real-Time targets, to /usr/local/lib, where they are stored on the cRIO-905*x*, if the application requires this.

For more information, visit *ni.com/info* and enter the Info Code RT\_Paths.

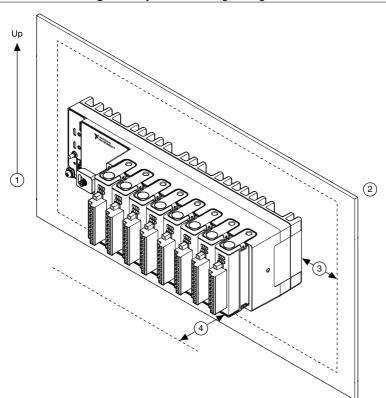

# Mounting the Controller

To obtain the maximum ambient temperature, you must mount the cRIO-905x in the reference mounting configuration shown in the following image. Mounting the cRIO-905x in the reference mounting configuration ensures that your system will operate correctly across the full operating temperature range and provide optimal C Series module accuracy. Observe the following guidelines to mount the cRIO-905x in the reference mounting configuration.

| 1          | Horizontal mounting orientation.                                                                                                                                                                                                                                                                                                                                                                                                        |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2          | <ul> <li>Mounting substrate options:</li> <li>Mount the cRIO-905x directly to a metallic surface that is at least 1.6 mm (0.062 in.) thick and extends a minimum of 101.6 mm (4 in.) beyond all edges of the device.</li> <li>Use the NI Panel Mounting Kit to mount the cRIO-905x to a metallic surface that is at least 1.6 mm (0.062 in.) thick and extends a minimum of 101.6 mm (4 in.) beyond all edges of the device.</li> </ul> |

| 3          | Observe the minimum spacing dimensions in the Mounting Requirements section.                                                                                                                                                                                                                                                                                                                                                            |

| 4          | Allow space for cabling clearance according to the <i>Mounting Requirements</i> section.                                                                                                                                                                                                                                                                                                                                                |

| $\bigcirc$ | <b>Tip</b> Before mounting the controller, record the serial number from the side of the $cRIO-905x$ so that you can identify the $cRIO-905x$ in MAX. You will be unable to                                                                                                                                                                                                                                                             |

troller, record the serial number from the side cRIO-905x so that you can identify the cRIO-905x in MAX. You will be unable to read the serial number after you mount the controller.

# Alternative Mounting Configurations

The maximum operating temperature may be reduced for any mounting configuration other than the reference mounting configuration. A 10 °C (18 °F) reduction in maximum operating temperature is sufficient for most alternate mounting configurations. Follow the guidelines above for all mounting configurations. The published accuracy specifications, although not guaranteed for alternate mounting configurations, may be met depending on the system power and the thermal performance of the alternate mounting configuration. Contact NI for further details regarding the impact of common alternate mounting configurations on maximum operating temperature and module accuracy.

Contact NI for further details regarding the system impact of common alternative mounting configurations.

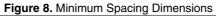

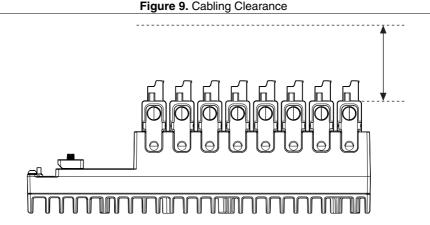

# Mounting Requirements

**Note** The various connector types on C Series modules require different cabling clearances. For a complete list of cabling clearances for C Series modules, visit *ni.com/info* and enter the Info Code crioconn.

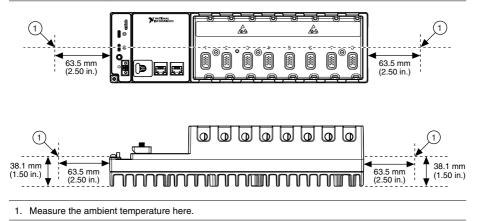

Figure 10. Ambient Temperature Measurement Location

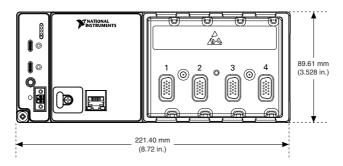

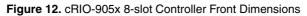

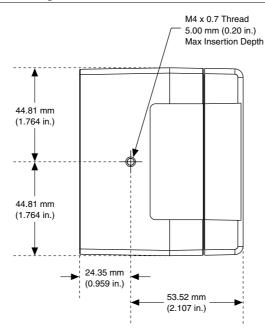

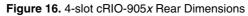

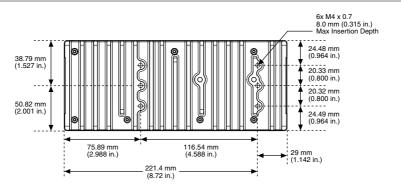

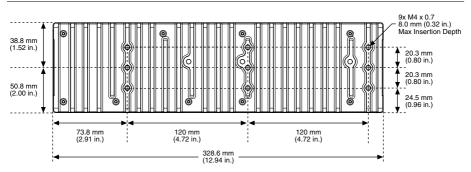

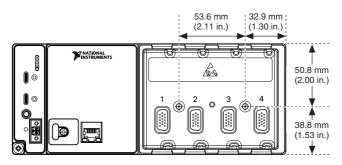

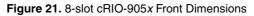

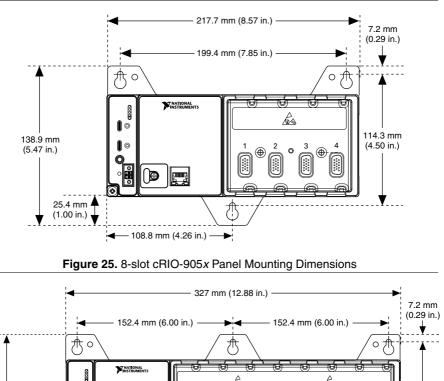

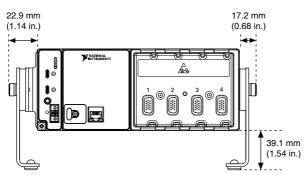

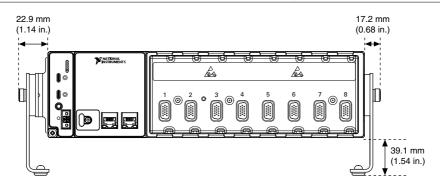

# Dimensions

The following dimensional drawings apply to all cRIO-905x controllers. For detailed dimensional drawings and 3D models, visit *ni.com/dimensions* and search for the model number.

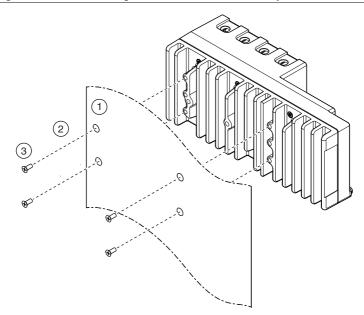

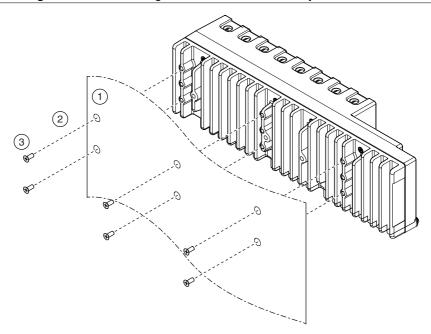

## Rear Mounting on a Flat Surface

#### What to Use

- cRIO-905*x*

- M4 screws, user provided, which must not exceed 8 mm of insertion into the cRIO-905x

- x4 for 4-slot models

- x6 for 8-slot models

#### What to Do

Complete the following steps to rear mount the cRIO-905x directly on a flat, rigid surface using the mounting holes.

**Note** NI recommends rear mounting your system on a flat surface in environments with high shock and vibration.

Figure 14. Rear Mounting the 4-slot cRIO-905x Directly on a Flat Surface

Figure 15. Rear Mounting the 8-slot cRIO-905x Directly on a Flat Surface

- 1. Prepare the surface for mounting the cRIO-905x using the Surface Mounting Dimensions.

- 2. Align the cRIO-905x on the surface.

- 3. Fasten the cRIO-905x to the surface using the M4 screws appropriate for the surface.

**Note** Screws must not exceed 8 mm of insertion into the cRIO-905x. Tighten the screws to a torque of  $1.3 \text{ N} \cdot \text{m}$  (11.5 lb · in.).

## Surface Mounting Rear Dimensions

Figure 17. 8-slot cRIO-905x Rear Dimensions

## Front Mounting on a Flat Surface

#### What to Use

- cRIO-905*x*

- M4 screws, user-provided, length dependent on application

- x2 for 4-slot models

- x3 for 8-slot models

#### What to Do

Complete the following steps to front mount the cRIO-905x directly on a flat, rigid surface using the mounting holes.

**Note** NI recommends rear mounting your system on a flat surface in environments with high shock and vibration.

Figure 18. Front Mounting the 4-slot cRIO-905x Directly on a Flat Surface

Figure 19. Front Mounting the 8-slot cRIO-905x Directly on a Flat Surface

- 1. Prepare the surface for mounting the cRIO-905x using the *Surface Mounting Dimensions*.

- 2. Align the cRIO-905x on the surface.

- 3. Fasten the cRIO-905x to the surface using the M4 screws appropriate for the surface.

## Surface Mounting Front Dimensions Figure 20. 4-slot cRIO-905x Front Dimensions

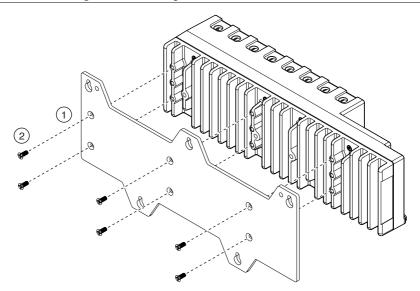

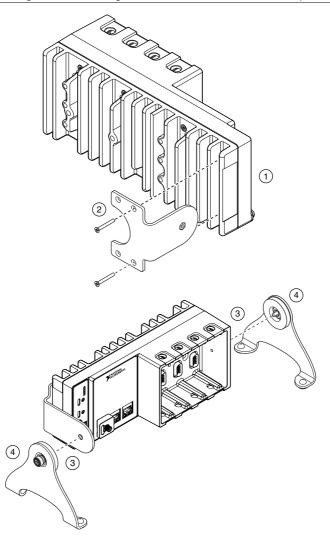

## Mounting the Controller on a Panel

#### What to Use

- cRIO-905*x*

- Screwdriver, Phillips #2

- NI panel mounting kit for 4-slot controllers, 157253-01

- Panel mounting plate

- M4 x 10 screws (x4)

- NI panel mounting kit for 8-slot controllers, 157267-01

- Panel mounting plate

- M4 x 10 screws (x6)

#### What to Do

Complete the following steps to mount the cRIO-905x on a panel.

Figure 23. Mounting the 8-slot cRIO-905x on a Panel

1. Align the cRIO-905x and the panel mounting plate.

2. Fasten the panel mounting plate to the cRIO-905*x* using the screwdriver and M4 x 10 screws.

**Note** You must use the screws provided with the NI panel mounting kit because they are the correct depth and thread for the panel mounting plate. Tighten the screws to a torque of  $1.3 \text{ N} \cdot \text{m}$  (11.5 lb  $\cdot$  in.).

3. Fasten the panel mounting plate to the surface using the screwdriver and screws that are appropriate for the surface. The maximum screw size is M5 or number 10.

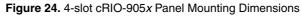

## Panel Mounting Dimensions

10

0

138.9 mm

(5.47 in.)

25.4 mm 4

(1.00 in.)

Â

0

— 147.3 mm (5.80 in.) -

୲୕

₼

🗲 89.9 mm (3.54 in.) 🗲

3

4

0

5

ſ

Â

6

7 8

$\odot$

114.3 mm

(4.50 in.)

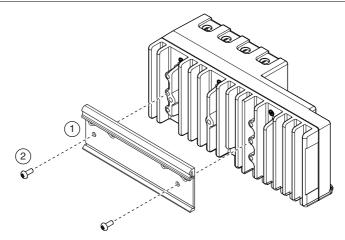

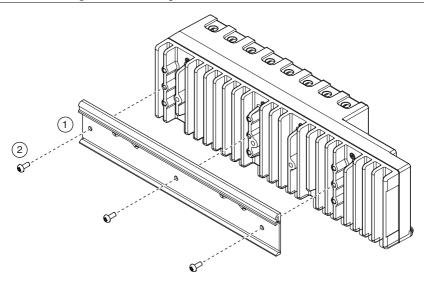

# Mounting on a DIN Rail

#### What to Use

- cRIO-905*x*

- Screwdriver, Phillips #2

- NI DIN rail mounting kit

- 4-slot models 157254-01

- DIN rail clip

- M4 x 10 screws (x2)

- 8-slot models 157268-01

- DIN rail clip

- M4 x 10 screws (x3)

#### What to Do

Complete the following steps to mount the cRIO-905x on a standard 35-mm DIN rail.

#### Figure 26. Mounting the 4-slot cRIO-905x on a DIN Rail

- 1. Align the DIN rail clip with the mounting holes on the rear of the cRIO-905x.

- 2. Fasten the DIN rail clip to the cRIO-905x using the screwdriver and M4 x 10 screws.

**Note** You must use the screws provided with the NI DIN rail kit because they are the correct depth and thread for the DIN rail clip. Tighten the screws to a torque of  $1.3 \text{ N} \cdot \text{m} (11.5 \text{ lb} \cdot \text{in.})$ .

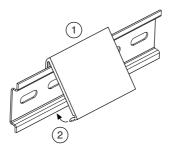

## Clipping the Controller on a DIN Rail

Figure 28. Clipping the Controller on a DIN Rail

- 1. Latch the spring side (top) of the DIN clip onto the top edge of the DIN rail.

- 2. Press down firmly to compress the spring until the clip locks in place on the DIN rail.

**Note** Ensure that no C Series modules are in the controller before removing it from the DIN rail.

# Mounting on a Rack

You can use the following rack mount kits to mount the controller and other DIN railmountable equipment on a standard 482.6 mm (19 in.) rack.

- Industrial Rack Mount Kit, 786411-01

- NI Rack-Mounting Kit, 781989-01

**Note** You must use the appropriate NI DIN rail mounting kit for your model in addition to a rack-mounting kit.

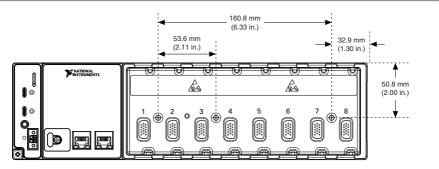

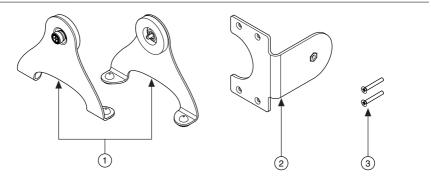

## Mounting the Device on a Desktop

#### What to Use

- cRIO-905x

- Screwdriver, Phillips #1

- Screwdriver, Phillips #2

- Screwdriver, Torx T10

- NI desktop mounting kit, 779473-01

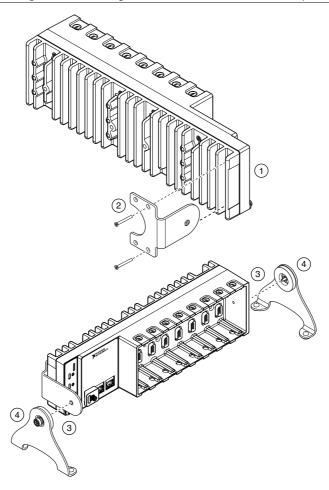

#### Figure 29. Components of the NI Desktop Mount Kit

- 1. Desktop mounting brackets (x2)

- 2. Adapter bracket

- 3. M3 x 35 screws (x2)

#### What to Do

Complete the following steps to mount the cRIO-905x on a desktop.

- 1. Use the Torx T10 screwdriver to remove the two screws from the back of the chassis on the controller side.

- 2. Use the #1 Phillips screwdriver and the two M3 x 35 screws to attach the adapter bracket to the chassis.

- 3. Align the desktop mounting brackets with the mounting holes at the end of the chassis and on the adapter bracket.

- 4. Use a #2 Phillips screwdriver to tighten the captive screw on the end bracket.

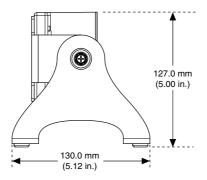

### **Desktop Mounting Dimensions**

Figure 32. 4 Slot cRIO-905x Desktop Mounting Front Dimensions

Figure 33. 8 Slot cRIO-905x Desktop Mounting Front Dimensions

Figure 34. cRIO-905x Desktop Mounting Side Dimensions

# Choosing Your Programming Mode

| J          | Real-<br>Time | Enables you to use C Series modules directly from LabVIEW Real-Time, using NI DAQmx.                                                                                                                                                                                                                                                                                                                                                              |

|------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |               | C Series modules appear under the Real-Time Resources item in the MAX<br>Project Explorer window and I/O channels appear as I/O variables under<br>the modules. To use I/O variables, you drag and drop them from the<br>Project Explorer window to LabVIEW Real-Time VIs.                                                                                                                                                                        |

|            |               | Use this mode to make the C Series module behave like it is in a CompactDAQ controller, using the Real-Time NI-DAQmx and NI-XNET drivers to communicate, and access the four counter/timers and the PFI trigger connector on the controller.                                                                                                                                                                                                      |

| 2          | Real-<br>Time | Enables you to use C Series modules directly from LabVIEW Real-Time, using I/O variables.                                                                                                                                                                                                                                                                                                                                                         |

|            | Scan          | C Series modules that you use in Scan Interface mode appear under the Real-Time Scan Resources item in the MAX Project Explorer window and I/O channels appear as I/O variables under the modules. To use I/O variables, you drag and drop them from the Project Explorer window to LabVIEW Real-Time VIs.                                                                                                                                        |

|            |               | In this mode, you do not need to do any LabVIEW FPGA development.<br>LabVIEW programs the FPGA for you with a fixed FPGA bitfile that<br>communicates with all the C Series modules that RT Scan mode supports.<br>LabVIEW also sends C Series data to the Real-Time host to be displayed<br>in I/O variables. Real-Time Scan mode also enables you to dynamically<br>detect which types of C Series modules are plugged into chassis slots.      |

| <b>111</b> | FPGA          | Enables you to use C Series modules from LabVIEW FPGA VIs.                                                                                                                                                                                                                                                                                                                                                                                        |

| ₽          |               | C Series modules appear directly under the FPGA Target item in the MAX Project Explorer window and I/O channels appear as FPGA I/O items under the FPGA Target. To access the I/O channels, you either configure FPGA I/O Nodes in a LabVIEW FPGA VI or drag and drop the I/O channels from the Project Explorer window to a LabVIEW FPGA VI block diagram.                                                                                       |

|            |               | Use this mode to add more flexibility, customization, timing, and<br>synchronization to your applications. To use the CompactRIO system in<br>FPGA mode, you must either have the LabVIEW FPGA Module installed<br>on the host computer, or have access to a compiled bitfile that you can<br>download to the FPGA. In either case, you use the Open FPGA VI<br>Reference function in a LabVIEW Real-Time VI to access the FPGA VI<br>or bitfile. |

The cRIO-905x supports three programming modes on a per slot basis.

| Task                                                               | Real-Time | Real-Time Scan | FPGA |

|--------------------------------------------------------------------|-----------|----------------|------|

| Control rates up to 1 kHz                                          |           |                |      |

| Control rates between 1 kHz and 2.5 kHz<br>(application dependent) |           | •              |      |

| Control rates over 2.5 kHz                                         |           |                |      |

| High-speed waveform acquisition                                    |           |                |      |

Table 15. Supported Programming Modes for Popular Tasks

**Note** Some C Series modules can only be used in certain programming modes. For module-specific software support information, visit *ni.com/info* and enter the Info Code swsupport.

To learn more about using the cRIO-905x in Real-Time mode, refer to the following sections:

- Analog Input with NI-DAQmx

- Analog Output with NI-DAQmx

- Digital Input/Output with NI-DAQmx

- PFI with NI-DAQmx

- Counters with NI-DAQmx

# Analog Input with NI-DAQmx

To perform analog input measurements, install a supported analog input C Series module into any slot on the cRIO controller and set the programming mode to Real-Time (NI-DAQmx) mode. The measurement specifications, such as number of channels, channel configuration, sample rate, and gain, are determined by the type of C Series module used. For more information and wiring diagrams, refer to the documentation included with your C Series modules.

The cRIO controller has eight input timing engines, which means that up to eight hardwaretimed analog input tasks can be running at a time on the controller. An analog input task can include channels from multiple analog input modules. However, channels from a single module cannot be used in multiple tasks.

Multiple timing engines allow the cRIO controller to run up to eight analog input tasks simultaneously, each using independent timing and triggering configurations. The eight timing engines are it0, it1,...it7.

## Hardware-Timed Single Point (HWTSP) Mode

In HWTSP mode, samples are acquired or generated continuously using hardware timing and no buffer. You must use the sample clock or change detection timing types. No other timing types are supported.

Use HWTSP mode if you need to know if a loop executes in a given amount of time, such as in a control application. Because there is no buffer, if you use HWTSP mode, ensure that reads

or writes execute fast enough to keep up with hardware timing. If a read or write executes late, it returns a warning.

Note DSA modules do not support HWTSP mode.

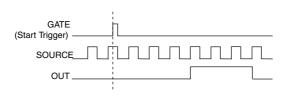

## Analog Input Triggering Signal

A trigger is a signal that causes an action, such as starting or stopping the acquisition of data. When you configure a trigger, you must decide how you want to produce the trigger and the action you want the trigger to cause. The cRIO controller supports internal software triggering, external digital triggering, analog triggering, and internal time triggering.

Three triggers are available: Start Trigger, Reference Trigger, and Pause Trigger. An analog or digital signal can initiate these three trigger actions. C Series Parallel digital input modules and the controller's integrated PFI trigger line can be used in any controller slot to supply a digital trigger. To find your module triggering options, refer to the documentation included with your C Series modules. For more information about using digital modules for triggering, refer to the *Digital Input/Output with NI-DAQmx* section.

Refer to the *AI Start Trigger Signal*, *AI Reference Trigger Signal*, and *AI Pause Trigger Signal* sections for more information about the analog input trigger signals.

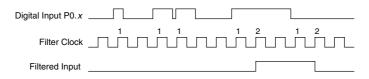

## Analog Input Timing Signals

The cRIO controller features the following analog input timing signals:

- AI Sample Clock Signal\*

- AI Sample Clock Timebase Signal

- AI Start Trigger Signal\*

- AI Reference Trigger Signal\*

- AI Pause Trigger Signal\*

Signals with an \* support digital filtering. Refer to the *PFI Filters* section for more information.

Refer to the *AI Convert Clock Signal Behavior For Analog Input Modules* section for more information about AI Convert Clock signals and the cRIO controller.

### AI Sample Clock Signal

A sample consists of one reading from each channel in the AI task. Sample Clock signals the start of a sample of all analog input channels in the task. The sample clock can be generated from external or internal sources as shown in the figure below.

#### Routing the Sample Clock to an Output Terminal

You can route Sample Clock to any output PFI terminal. Sample Clock is an active high pulse by default.

#### Al Sample Clock Timebase Signal

The AI Sample Clock Timebase signal is divided down to provide a source for Sample Clock. AI Sample Clock Timebase can be generated from external or internal sources. AI Sample Clock Timebase is not available as an output from the controller.

#### Al Start Trigger Signal

Use the Start Trigger signal to begin a measurement acquisition which consists of one or more samples. Once the acquisition begins, configure the acquisition to stop in one of the following ways:

- When a certain number of points has been sampled (in finite mode)

- After a hardware reference trigger (in finite mode)

- With a software command (in continuous mode)

An acquisition that uses a start trigger (but not a reference trigger) is sometimes referred to as a posttriggered acquisition. That is, samples are measured only after the trigger.

When you are using an internal sample clock, you can specify a default delay from the start trigger to the first sample.

#### Using a Digital Source

To use the Start Trigger signal with a digital source, specify a source and a rising or falling edge. Use the following signals as the source:

- Any PFI terminal

- Counter n Internal Output

The source also can be one of several other internal signals on your cRIO controller. Refer to the "Device Routing in MAX" topic in the *NI-DAQmx Help* or the *LabVIEW Help* for more information.

#### Using an Analog Source

Some C Series modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event. When you use an analog trigger source for Start Trigger, the acquisition begins on the first rising edge of the Analog Comparison Event signal.

#### Routing AI Start Trigger to an Output Terminal

You can route the Start Trigger signal to any output PFI terminal. The output is an active high pulse.

#### Using a Time Source

To use the Start Trigger signal with a time source, configure a specific time in NI-DAQmx. Refer to the "Timestamps" and "Time Triggering" topics in the *NI-DAQmx Help* for more information on accessing time-based features in the NI-DAQmx API.

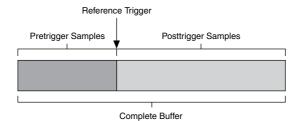

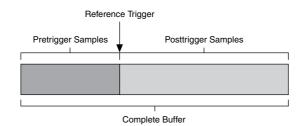

### AI Reference Trigger Signal

Use a reference trigger to stop a measurement acquisition. To use a reference trigger, specify a buffer of finite size and a number of pretrigger samples (samples that occur before the reference trigger). The number of posttrigger samples (samples that occur after the reference trigger) desired is the buffer size minus the number of pretrigger samples.

Once the acquisition begins, the cRIO controller writes samples to the buffer. After the cRIO controller captures the specified number of pretrigger samples, the cRIO controller begins to look for the reference trigger condition. If the reference trigger condition occurs before the cRIO controller captures the specified number of pretrigger samples, the controller ignores the condition.

If the buffer becomes full, the cRIO controller continuously discards the oldest samples in the buffer to make space for the next sample. This data can be accessed (with some limitations) before the cRIO controller discards it. Refer to the *Can a Pretriggered Acquisition be Continuous*? document for more information. To access this document, go to *ni.com/info* and enter the Info Code rdcanq.

When the reference trigger occurs, the cRIO controller continues to write samples to the buffer until the buffer contains the number of posttrigger samples desired. The figure below shows the final buffer.

#### Using a Digital Source

To use a reference trigger with a digital source, specify a source and a rising or falling edge. Either PFI or one of several internal signals on the cRIO controller can provide the source. Refer to the "Device Routing in MAX" topic in the *NI-DAQmx Help* or the *LabVIEW Help* for more information.

#### Using an Analog Source

Some C Series modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event.

When you use an analog trigger source, the acquisition stops on the first rising or falling edge of the Analog Comparison Event signal, depending on the trigger properties.

#### Routing the Reference Trigger Signal to an Output Terminal

You can route a reference trigger to any output PFI terminal. Reference Trigger is active high by default.

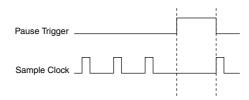

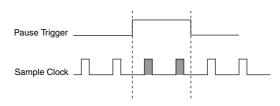

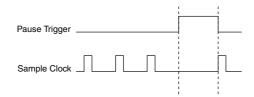

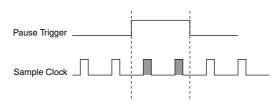

#### Al Pause Trigger Signal

You can use the Pause Trigger to pause and resume a measurement acquisition. The internal sample clock pauses while the external trigger signal is active and resumes when the signal is inactive. You can program the active level of the pause trigger to be high or low.

#### Using a Digital Source

To use the Pause Trigger, specify a source and a polarity. The source can be either from PFI or one of several other internal signals on your cRIO controller. Refer to the "Device Routing in MAX" topic in the *NI-DAQmx Help* or the *LabVIEW Help* for more information.

#### Using an Analog Source

Some C Series modules can generate a trigger based on an analog signal. In NI-DAQmx, this is called the Analog Comparison Event.

When you use an analog trigger source, the internal sample clock pauses when the Analog Comparison Event signal is low and resumes when the signal goes high (or vice versa).

**Note** Pause triggers are only sensitive to the level of the source, not the edge.

### Al Convert Clock Signal Behavior For Analog Input Modules

Refer to the Scanned Modules, Simultaneous Sample-and-Hold Modules, Delta-Sigma Modules, and Slow Sample Rate Modules sections for information about the AI Convert Clock signal and C Series analog input modules.

#### Scanned Modules

Scanned C Series analog input modules contain a single A/D converter and a multiplexer to select between multiple input channels. When the module interface receives a Sample Clock pulse, it begins generating a Convert Clock for each scanned module in the current task. Each Convert Clock signals the acquisition of a single channel from that module. The Convert Clock rate depends on the module being used, the number of channels used on that module, and the system Sample Clock rate.

The driver chooses the fastest conversion rate possible based on the speed of the A/D converter for each module and adds 10  $\mu$ s of padding between each channel to allow for adequate settling time. This scheme enables the channels to approximate simultaneous sampling. If the AI Sample Clock rate is too fast to allow for 10  $\mu$ s of padding, NI-DAQmx selects a conversion rate that spaces the AI Convert Clock pulses evenly throughout the sample. NI-DAQmx uses the same amount of padding for all the modules in the task. To explicitly specify the conversion rate, use the ActiveDevs and AI Convert Clock Rate properties using the DAQmx Timing property node or functions.

#### Simultaneous Sample-and-Hold Modules

Simultaneous sample-and-hold (SSH) C Series analog input modules contain multiple A/D converters or circuitry that allows all the input channels to be sampled at the same time. These modules sample their inputs on every Sample Clock pulse.

#### Delta-Sigma Modules

Delta-sigma C Series analog input modules function much like SSH modules, but use A/D converters that require a high-frequency oversample clock to produce accurate, synchronized data. Some delta-sigma modules in the cRIO controller automatically share a single oversample clock to synchronize data from all the modules that support an external oversample clock timebase when they all share the same task. (DSA modules are an example).

The oversample clock is used as the AI Sample Clock Timebase. The cRIO controller supplies 10 MHz, 12.8 MHz, and 13.1072 MHz timebases from which software automatically selects based on the modules in the task. When delta-sigma modules with different oversample clock frequencies are used in an analog input task, the AI Sample Clock Timebase can use any of the

available frequencies; by default, the fastest available is used. The sample rate of all modules in the task is an integer divisor of the frequency of the AI Sample Clock Timebase.

When one or more delta-sigma modules are in an analog input task, the delta-sigma modules also provide the signal used as the AI Sample Clock. This signal is used to cause A/D conversion for other modules in the system, just as the AI Sample Clock does when a delta-sigma module is not being used.

When delta-sigma modules are in an AI task, the controller automatically issues a synchronization pulse to each delta-sigma module so that their ADCs are reset at the same time. Because of the filtering used in delta-sigma A/D converters, these modules usually exhibit a fixed input delay relative to non-delta-sigma modules in the system. This input delay is specified in the C Series module documentation.

When channels from delta-sigma C Series modules are included in a multi-chassis task, please ensure that the first channel in your channel list is from a delta-sigma module.

Note DSA modules do not support HWTSP mode.

#### Slow Sample Rate Modules

Some C Series analog input modules are specifically designed for measuring signals that vary slowly, such as temperature. Because of their slow rate, it is not appropriate for these modules to constrain the AI Sample Clock to operate at or slower than their maximum rate. When using such a module in the cRIO controller mixed with a non-slow sample module in the same task, exceeding the maximum sampling rate of the slow sample module results in the most recently acquired sample being read multiple times. In this scenario, the first sample of a hardware-timed acquisition with a slow sampled C Series module is sampled when the task is committed.

For more information about which C Series modules are compatible with the cRIO controller, go to *ni.com/info* and enter the Info Code rdcdaq.

## Getting Started with AI Applications in Software

You can use the cRIO controller in the following analog input applications:

- Single-point acquisition

- Hardware-Timed Single Point acquisition

- Finite acquisition

- Continuous acquisition

For more information about programming analog input applications and triggers in software, refer to the *NI-DAQmx Help* or the *LabVIEW Help* for more information.

# Analog Output with NI-DAQmx

To generate analog output, install an analog output C Series module in any slot on the cRIO controller. The generation specifications, such as the number of channels, channel

configuration, update rate, and output range, are determined by the type of C Series module used. For more information, refer to the documentation included with your C Series module(s).

The cRIO controller has eight output timing engines, which means that up to eight hardwaretimed analog output tasks can be running at a time on the controller. On a single analog output C Series module, you can assign any number of channels to either a hardware-timed task or a software-timed (single-point) task. However, you cannot assign some channels to a hardwaretimed task and other channels (on the same module) to a software-timed task.

Multiple timing engines allow the cRIO controller to run up to eight analog output tasks simultaneously, each using independent timing and triggering configurations. The eight timing engines are ot0, ot1,... ot7.

## Analog Output Data Generation Methods

When performing an analog output operation, you either can perform software-timed generations or hardware-timed generations.

### Software-Timed Generations

With a software-timed generation, software controls the rate at which data is generated. Software sends a separate command to the hardware to initiate each DAC conversion. In NI-DAQmx, software-timed generations are referred to as on-demand timing. Software-timed generations are also referred to as immediate or static operations. They are typically used for writing out a single value, such as a constant DC voltage.

The following considerations apply to software-timed generations:

- If any AO channel on a module is used in a hardware-timed (waveform) task, no channels on that module can be used in a software-timed task

- You can configure software-timed generations to simultaneously update

- Only one simultaneous update task can run at a time

- A hardware-timed AO task and a simultaneous update AO task cannot run at the same time

#### Hardware-Timed Generations

With a hardware-timed generation, a digital hardware signal controls the rate of the generation. This signal can be generated internally on the controller or provided externally.

Hardware-timed generations have several advantages over software-timed acquisitions:

- The time between samples can be much shorter

- The timing between samples is deterministic

- Hardware-timed acquisitions can use hardware triggering

#### Hardware-Timed Single Point (HWTSP) Mode

In HWTSP mode, samples are acquired or generated continuously using hardware timing and no buffer. You must use the sample clock or change detection timing types. No other timing types are supported.

Use HWTSP mode if you need to know if a loop executes in a given amount of time, such as in a control application. Because there is no buffer, if you use HWTSP mode, ensure that reads or writes execute fast enough to keep up with hardware timing. If a read or write executes late, it returns a warning.

Note DSA modules do not support HWTSP mode.

#### **Buffered Analog Input**

A buffer is a temporary storage in computer memory for generated samples. In a buffered generation, data is moved from a host buffer to the cRIO controller onboard FIFO before it is written to the C Series modules.

One property of buffered I/O operations is sample mode. The sample mode can be either finite or continuous:

- *Finite*—Finite sample mode generation refers to the generation of a specific, predetermined number of data samples. After the specified number of samples is written out, the generation stops.

- *Continuous*—Continuous generation refers to the generation of an unspecified number of samples. Instead of generating a set number of data samples and stopping, a continuous generation continues until you stop the operation. There are three different continuous generation modes that control how the data is written. These modes are regeneration, onboard regeneration, and non-regeneration:

- In regeneration mode, you define a buffer in host memory. The data from the buffer is continually downloaded to the FIFO to be written out. New data can be written to the host buffer at any time without disrupting the output. There is no limitation on the number of waveform channels supported by regeneration mode.

- With onboard regeneration, the entire buffer is downloaded to the FIFO and regenerated from there. After the data is downloaded, new data cannot be written to the FIFO. To use onboard regeneration, the entire buffer must fit within the FIFO size. The advantage of using onboard regeneration is that it does not require communication with the main host memory once the operation is started, which prevents problems that may occur due to excessive bus traffic or operating system latency. There is a limit of 16 waveform channels for onboard regeneration.

- With non-regeneration, old data is not repeated. New data must continually be written to the buffer. If the program does not write new data to the buffer at a fast enough rate to keep up with the generation, the buffer underflows and causes an error. There is no limitation on the number of waveform channels supported by nonregeneration.

## Analog Output Triggering Signals

A trigger is a signal that causes an action, such as starting or stopping the acquisition of data. When you configure a trigger, you must decide how you want to produce the trigger and the action you want the trigger to cause. The cRIO controller supports internal software triggering, external digital triggering, analog triggering, and internal time triggering.

Analog output supports two different triggering actions: AO Start Trigger and AO Pause Trigger. An analog or digital signal can initiate these actions. C Series parallel digital input modules and the controller's integrated PFI trigger line can be used in any controller slot to supply a digital trigger. An analog trigger can be supplied by some C Series analog modules.

Refer to the *AO Start Trigger Signal* and *AO Pause Trigger Signal* sections for more information about the analog output trigger signals.

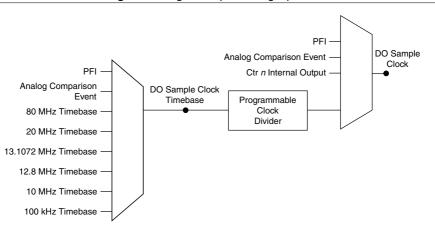

## Analog Output Timing Signals

The cRIO controller features the following AO (waveform generation) timing signals:

- AO Sample Clock Signal\*

- AO Sample Clock Timebase Signal

- AO Start Trigger Signal\*

- AO Pause Trigger Signal\*

Signals with an \* support digital filtering. Refer to the *PFI Filters* section for more information.

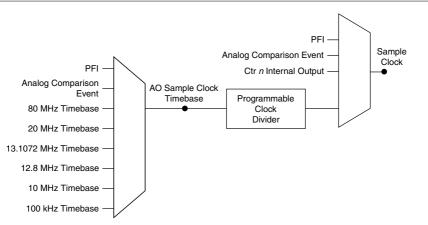

#### AO Sample Clock Signal

The AO sample clock signals when all the analog output channels in the task update. AO Sample Clock can be generated from external or internal sources as shown in the figure below.

#### Figure 37. Analog Output Timing Options

#### Routing AO Sample Clock to an Output Terminal

You can route AO Sample Clock to any output PFI terminal. AO Sample Clock is active high by default.

### AO Sample Clock Timebase Signal

The AO Sample Clock Timebase signal is divided down to provide a source for AO Sample Clock. AO Sample Clock Timebase can be generated from external or internal sources, and is not available as an output from the controller.

#### **Delta-Sigma Modules**

The oversample clock is used as the AO Sample Clock Timebase. The cRIO controller supplies 10 MHz, 12.8 MHz, and 13.1072 MHz timebases. When delta-sigma modules with different oversample clock frequencies are used in an analog output task, the AO Sample Clock Timebase can use any of the available frequencies; by default, the fastest available is used. The update rate of all modules in the task is an integer divisor of the frequency of the AO Sample Clock Timebase.

Note DSA modules do not support HWTSP mode.

### AO Start Trigger Signal

Use the AO Start Trigger signal to initiate a waveform generation. If you do not use triggers, you can begin a generation with a software command. If you are using an internal sample clock, you can specify a delay from the start trigger to the first sample. For more information, refer to the *NI-DAQmx Help*.

#### Using a Digital Source

To use AO Start Trigger, specify a source and a rising or falling edge. The source can be one of the following signals:

- A pulse initiated by host software

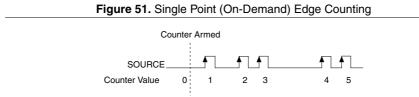

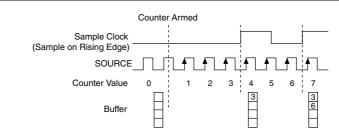

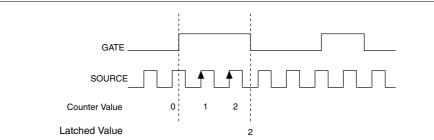

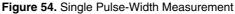

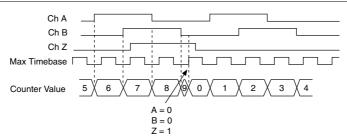

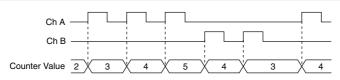

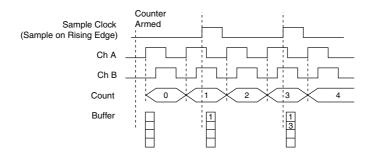

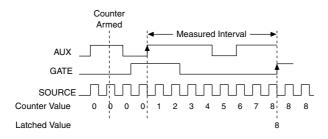

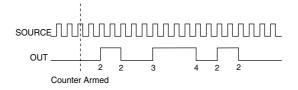

- Any PFI terminal