Modular Systems > National Instruments > CompactRIO Controllers

Pictures shown are a representation. Actual item may vary if no part number is provided on quote request.

✔ Same Day Calibration Available

✔ 2-3 Year Warranty Included

✔ Free Ground Shipping

Or speak to a sales representative for additional information:

Phone:

1-800-915-6216Email:

sales@apexwaves.comcRIO-9113 In Stock | Ships in 5-10 Days

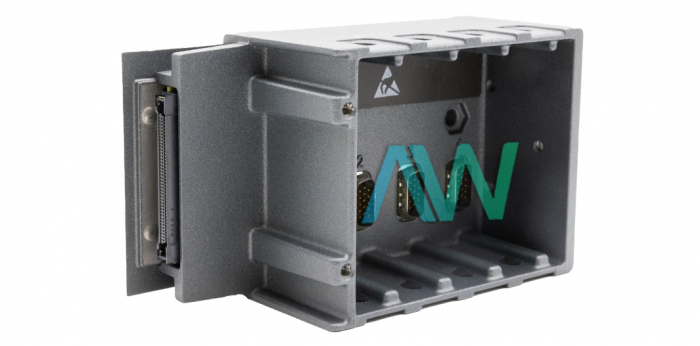

cRIO-9113, 4-Slot, FPGA CompactRIO Chassis

National Instruments cRIO-9113 CompactRIO Chassis

The cRIO‑9113 (Part Numbers: 780917-01 and 780917-02) comes with a Virtex-5 FPGA that utilizes the same interconnect and a similar access to the worldwide directing lattice. Timing models are shared, incredibly enhancing the consistency of the execution for high-speed plans. FPGAs are an imperative building hinder in high accessibility/unwavering quality framework. The Virtex-5 family System Monitor encourages simpler checking of the FPGA and its outside condition.

Each FPGA from the Virtex-5 family contains a System Monitor square, which is worked around a 10-bit 200k SPS ADC (Analog-to-Digital Converter). This ADC is utilized to digitize various on-chip sensors to give data about the physical condition inside the FPGA. On-chip sensors incorporate a temperature sensor and power supply sensors. Access to the outer condition is given by means of various outside simple input channels. These simple sources of input are broadly useful and can be utilized to digitize a wide assortment of voltage signal composes. Support for unipolar, bipolar, and genuine differential information plans is given.

The Virtex-5 FPGA on the NI cRIO-9113 utilizes input LUTs for up to 64 mixes, expanding the measure of rationale that the user can execute per cut. Also, the cuts themselves are set in nearer closeness to each other to decrease the proliferation deferral of electrons and increment by and large execution rates. The single-cycle Timed Loop structure in LabVIEW FPGA takes a full favorable position of six-input LUTs for generously enhanced asset use. This allows the user to utilize more LabVIEW FPGA code to fit inside the Virtex-5 FPGA and perform more activities per clock cycle.

| Model | cRIO-9113 |

|---|---|

| Manufacturer | National Instruments |

| Part Numbers | 780917-01, 780917-02 |

| Type | CompactRIO Chassis |

| Slots | 4 |

| FPGA | Virtex-5 LX50 |

| Number of Flip-flops | 28,800 |

| Embedded RAM | 1,728 kbits |

| Weight | 20 oz. |

| Warranty | 2-3 Year Warranty |

| cRIO-9113 Manual | User Manual and Maintenance Manual Available for Download |

| Price | Contact a sales representative for a quote. |

Associated part numbers for cRIO-9113:

National Instruments cRIO-9113 Frequently Asked Questions

Question: Is the cRIO-9113 a good module to use in a high movement environment?

Answer: The cRIO-9113 is a rugged FPGA chassis that is designed to be used in environments with high vibration or movement.

Question: What is the FPGA block RAM on the cRIO 9113?

Answer: The FPGA block RAM on the cRIO 9113 is 1,728.

Question: Can I creating timing or triggering schemes with the NI cRIO-9113?

Answer: Yes, you can create any local or timing, triggering, and synchronization scheme with 25 ns resolution with the NI cRIO-9113.

Delivery:

Warranty:

All of our products are covered by our Apex Waves Warranty.

✓ 3 Year Warranty - New Surplus Parts

✓ 2 Year Warranty - Refurbished Parts

Returns:

No hassle return policy.

Dedicated customer service team.

Quick Quotes:

Receive Price & Availability Today!

Calibration:

Ask About Our Tiered Calibration Levels

Option & Modules:

Confirm Your Requirements or Versions

Repair:

Cost & Lead Time Available Upon Request for Service

Repair Evaluation: $150

Common Typos: